本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19:38 1665

1665

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

2012-05-07 11:37:30 2668

2668

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 14342

14342

-Si539x时钟提升频率灵活性和抖动性能--Si56x Ultra Series™ XO/VCXO提供最大可达3GHz的任意频率时钟-。

2018-06-26 15:19:41 7075

7075 今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 645

645 时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 503

503

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

Silicon Labs日前扩展了Si539x抖动衰减器系列产品,其新器件型号具有完全集成的参考时钟、增强了系统可靠性和性能,同时简化了高速网络设计中的PCB布局布线。

2019-06-20 16:16:56 4682

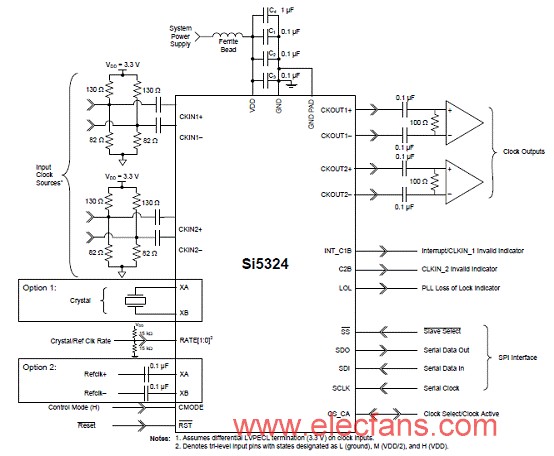

4682 的148.35 MHz进入收发器的gtxe2_i(GTXE2_CHANNEL)。这适用于SDI。 LMH1983的27 MHZ时钟进入控制I2C总线的过程,并从Si5324产生156.25 MHz时钟

2020-05-11 08:09:08

BOARD EVALUATION SI5324

2023-03-29 22:53:25

SI5324-EVB,SI5324评估板,0.002至710 MHz时钟发生器。 SI5324-EVB为评估SI5316任意速率精度时钟提供平台。 SI5316直接使用器件上的配置引脚进行控制

2019-02-22 09:30:51

Si5324 - Pin-Controlled 1_710 MHz Jitter Cleaning Clock - Silicon Laboratories

2022-11-04 17:22:44

嗨,Si5324已用于Xilinx参考设计(KC705评估板),可为10 gig SFP生成时钟。https://www.xilinx.com/support/documentation

2020-05-12 09:20:29

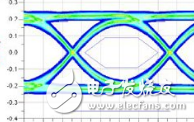

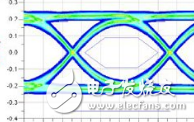

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

如题,目前项目要做一个100m16bit的数据采集卡,看了下贵公司的AD9460,但是差分参考时钟无法选择?

需不需要加一个时钟综合芯片比如Si5324?但类似的这种芯片市场上很不好买到。

如果用elcosc能否推荐个厂家和芯片?还有ad9460能否申请样品?谢谢

2023-12-25 07:44:39

如题,目前项目要做一个100m16bit的数据采集卡,看了下贵公司的AD9460,但是差分参考时钟无法选择?需不需要加一个时钟综合芯片比如Si5324?但类似的这种芯片市场上很不好买到。如果用elcosc能否推荐个厂家和芯片?还有ad9460能否申请样品?谢谢

2018-11-28 09:24:25

ZC706开发板上的SI5324需要通过I2C配置,官网找了一圈,只有VC709和KC705的例程,都是基于MICROBLAZE的,改到ZC706上问题也不大,准备动手这际,转念一想,何不

2019-07-05 08:22:37

C138和C141之后测量信号的差异。不幸的是,我没有在Si5324的引脚29和28上看到任何时钟输出,在衰减抖动之后,应该将我的125 MHz反馈回FPGA和SFP IP。我的设计很简单。它由1G eth

2019-09-27 09:21:26

MHz的双时钟输入,并产生两个相等的倍频时钟输出,范围为8 kHz至644.53 MHz。输入时钟频率和时钟倍频比可从流行的SyncE和T1 / E1速率表中选择。 Si5315基于第三代DSPLL技术,可在高度集成的PLL解决方案中提供任意速率频率合成和抖动衰减,无需外部VCXO和环路滤波器组件

2019-02-26 09:34:20

各种抖动技术规范是什么抖动的影响有哪些

2021-04-06 09:22:00

Si5328-EVB,评估套件为评估Si5328任意频率精密时钟定时IC提供了一个平台。 Si5328由微处理器或MCU(微控制器单元)通过I2C或SPI接口控制。 Si5328是一款抖动衰减器

2019-01-30 15:30:20

SI5340-D-EVB,评估板用于评估Si5340任意频率,任意输出,抖动衰减时钟倍频器版本D.器件版本以白色1英寸x 0.187英寸标签与文本SI5340-D区分-EB安装在主板的左下角。 (仅用于订购目的,术语EB和EVB分别指板和套件

2019-02-26 09:33:59

SI5340-EVB,评估板用于评估Si5340低抖动任意频率时钟发生器。 Si5340采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-26 09:28:56

SI5341-D-EVB,评估板用于评估Si5341任意频率,任意输出,抖动衰减时钟倍频器版本D.器件版本以白色1英寸x 0.187英寸标签与文本SI5341-D区分-EB安装在主板的左下角。 (仅用于订购目的,术语EB和EVB分别指板和套件

2019-02-26 09:41:06

SI5341-EVB,评估板用于评估Si5341低抖动任意频率时钟发生器。 Si5341采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-25 07:03:01

SI5342-D-EVB,评估板用于评估Si5342任意频率,任意输出,抖动衰减时钟倍频器版本D.器件版本以白色1英寸x 0.187英寸标签与文本SI5342-D区分-EB安装在主板的左下角。 (仅用于订购目的,术语EB和EVB分别指板和套件

2019-02-25 09:42:36

SI5344-D-EVB,基于Si5344任意频率,任意输出,抖动衰减时钟倍频器Rev.D的评估板

2019-02-25 06:21:54

SI5344-EVB,评估板用于评估Si5344任意频率,任意输出,抖动衰减时钟倍频器。 Si5344结合了第四代DSPLL和Multisynth技术,可为需要最高抖动性能的应用提供任意频率时钟

2019-02-26 09:36:27

SI5345-D-EVB,评估板用于评估Si5345任意频率,任意输出,抖动衰减时钟倍频器版本D.器件版本以白色1英寸x 0.187英寸标签与文本SI5345-D区分-EB安装在主板的左下角。 (仅用于订购目的,术语EB和EVB分别指板和套件

2019-02-25 09:46:14

SI5345-EVB,评估板用于评估Si5345任意频率,任意输出,抖动衰减时钟倍频器。 Si5345结合了第四代DSPLL和Multisynth技术,可为需要最高抖动性能的应用生成任意频率时钟

2019-02-26 07:34:30

SI5346-D-EVB,评估板用于评估Si5346任意频率,任意输出,抖动衰减时钟倍频器版本D.器件版本以白色1英寸x 0.187英寸标签与文本SI5346-D区分-EB安装在主板的左下角。 (仅用于订购目的,术语EB和EVB分别指板和套件

2019-02-25 09:51:02

具有可编程的抖动衰减带宽。 SI5348-D-EVB通过板载SMA连接器支持三个独立的差分输入时钟,两个独立的CMOS输入时钟和七个独立的输出时钟。 Si5348-D-EVB可以通过USB连接控制

2019-02-25 09:56:55

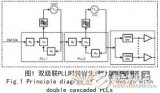

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

板上没有此频率的输入。我主要看两个选择: - 通过FPGA内的MMCM生成这个时钟(我读过它不是个好主意) - 使用电路板上的SI5324抖动衰减器产生312.5MHZ频率在kc705的原理图中,我

2019-09-27 09:51:28

。振荡器连接到引脚AK34和AL34(振荡器具有差分输出)。3.我需要将引脚AK34和AL34(156,25MHz振荡器)连接到引脚AW32和AW33(输入到抖动衰减器Si5324)。在这里我遇到了第一个

2019-09-25 11:45:13

你好;我正在使用VC709评估板。我想使用SI5324作为抖动衰减器。我使用DSPLLsim软件计算SI5324寄存器值。我想要的时钟是122.88MHz,但Si5324产生119.4 MHz。我

2019-10-18 09:36:35

theclock_control_program.vhd中有rom来存储配置si5324的程序,而si5324_clock_setup.psm是定义了si5324寄存器值的代码。我想知道在更改寄存器值insi5324_clock_setup.psm后如何获得newclock_control_program.vhd / .v。谢谢。

2019-09-26 10:32:19

在下小白一枚,花了一个多月的时间用FPGA控制SI5324C实现了时钟的分频,输入50M输出25M,当然了,这用MMCM或者PLL也能实现,但是SI5324C有一些特别的好处。程序在附件里

2017-11-24 20:31:36

Si539x芯片配置步骤第一次写博客(学习笔记),同时记录一次Si5394时钟芯片的配置,写这个教程的原因也是因为自己在网上搜资料的时候,用的人少之又少,让后面用到的人少走些弯路吧。前3点为芯片

2021-12-08 07:54:06

SI5342-EVB,评估板用于评估Si5342任意频率,任意输出,抖动衰减时钟倍频器。 Si5342结合了第四代DSPLL和Multisynth技术,可为需要最高抖动性能的应用生成任意频率时钟。可以使用Clock Builder Pro(CB Pro)软件工具控制和配置Si5342-EVB

2019-02-27 11:28:29

SI5346-EVB,评估板用于评估Si5346任意频率,任意输出,抖动衰减时钟倍频器。 Si5346在单个IC中包含2个独立的DSPLL,每个DSPLL具有可编程的抖动衰减带宽

2019-02-28 08:17:47

SI5347-EVB,评估板用于评估Si5347四路任意频率抖动衰减时钟倍频器。 Si5347在单个IC中包含4个独立的DSPLL,每个DSPLL具有可编程的抖动衰减带宽。 Si5347-EVB通过

2019-02-27 11:19:26

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

2018-11-12 09:12:43

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

我正在为clk_stm1~155.52MHz的SFP stm1输入计时我的GTX,这是从Si570到Si5324再到GTX模块我不确定这个clk的ppm,它可能会关闭多少...... Si

2019-09-23 06:44:53

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展

2008-12-27 12:24:05 6

6 随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前

2009-07-07 14:01:21 20

20 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)时钟倍频器,以产生高频时钟输出,用于以太网、10G光纤通道及其它网络设备。Ma

2010-03-01 08:54:52 126

126 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

2009-04-21 23:14:05 723

723

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-22 09:35:13 296

296

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-25 09:54:26 482

482

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-05-08 10:19:03 431

431

MAX3625A 低抖动、精密时钟发生器,提供三路输出

2009-08-13 13:01:27 828

828

MAX3624 低抖动、精密时钟发生器,提供四路输出

概述

MAX3624是一款低抖动精密

2009-09-18 08:56:41 682

682

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 1608

1608

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1345

1345

Si5374和Si5375是业界第一款集成了四个独立高性能锁相回路(PLL)的单芯片时钟IC,它所提供的PLL集成是其它竞争解决方案的两倍,抖动则低了40%。

2011-05-18 09:39:47 2225

2225

时钟抖动时域分析(下):

2012-05-08 15:26:25 29

29 介绍 此应用笔记侧重于不同类型的时钟抖动。时钟抖动是从它的时钟边沿偏差理想的位置。了解时钟抖动非常重要在应用中,因为它起着关键作用,在时间预算一个系统。 随着系统数据速率的增加,定时抖动成为关键

2017-04-01 16:13:18 6

6 时钟抖动时域分析,第 2 部分

2017-10-26 16:10:42 6

6 时钟抖动时域分析 第 3 部分

2017-10-26 16:13:28 4

4 时间域中分析的时钟抖动,第 1 部分

2017-10-26 16:16:23 4

4 随着SERDES应用越来越多,速率也越来越高,SI的问题渐渐变得越来越重要,它对PCB设计,SERDES参数优化都有着非常重要的指导作用。而器件选型也往往以SI仿真开始。但是在仿真时,工具会让用户

2017-11-18 13:17:01 4726

4726

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。

2018-05-30 09:00:00 5165

5165

这些抖动衰减时钟倍增器结合了第四代DSPLL™和Multisynth™技术,为需要最高抖动性能的应用程序实现任何频率时钟生成和抖动衰减。这些设备可通过一个串行接口进行编程,该接口具有电路内可编程

2019-07-01 08:00:00 20

20 的Multisynth™技术,可产生四个精度为0 ppm的独立时钟。每个输出时钟可独立配置,以支持各种信号格式和电源电压。si5338在节省空间的4x 4 mm qfn封装中提供低抖动频率合成。该设备可通过与I2C/SMBus兼容的串行接口编程,并支持1.8、2.5或3.3V核心电源的操作。

2019-10-29 08:00:00 0

0 本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 电子发烧友网站提供《SI5324 时脉产生器参考设计.pdf》资料免费下载

2020-12-31 05:33:41 12

12 AD5324 Evaluation Software

2021-02-20 10:55:14 6

6 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 7378

7378

AD5324评估软件

2021-04-09 16:41:47 11

11 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 AD5324评估软件

2021-05-30 12:56:25 5

5 ADL5324 S参数

2021-06-11 10:11:58 1

1 电子发烧友网为你提供ADI(ti)EVAL-AD5324相关产品参数、数据手册,更有EVAL-AD5324的引脚图、接线图、封装手册、中文资料、英文资料,EVAL-AD5324真值表,EVAL-AD5324管脚等资料,希望可以帮助到广大的电子工程师们。

2021-08-17 00:00:04

Si539x芯片配置步骤第一次写博客(学习笔记),同时记录一次Si5394时钟芯片的配置,写这个教程的原因也是因为自己在网上搜资料的时候,用的人少之又少,让后面用到的人少走些弯路吧。前3点为芯片

2021-11-25 20:21:03 18

18 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1071

1071 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 1

1 1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 657

657

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1026

1026

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1128

1128

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 960

960

电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1

电子发烧友App

电子发烧友App

评论