异步二进制减法计数器时序分析

- 二进制(41223)

- 计数器(92682)

- 减法(8274)

- 时序分析(22453)

- 异步(17994)

相关推荐

用74ls90设计六进制加法计数器

74LS90是一种常用的二进制计数器芯片,它可以实现二进制数的加法或减法计数。本文将介绍如何使用74LS90设计一个六进制加法计数器。 74LS90是一种双时钟输入的二进制计数器芯片,具有异步

2023-12-14 17:30:11 2281

2281

2281

228114级二进制串行计数分频器CD4060电子资料

概述:CD4060是一款14级二进制串行计数/分频器,它是由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。

2021-04-08 07:40:14

30进制加法计数器和30进制减法计数器

如何用multisim软件仿真双时钟加/减计数器CT74LS192和译码器CC4511和译码器SM4205构成的30进制加法计数器和30进制减法计数器,求仿真接线图。PCB打样找华强 http://www.hqpcb.com/3 样板2天出货

2012-10-07 21:13:28

74161设计12进制计数器

74161设计12进制计数器,1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。2.新建BDF文件及保存工程同前篇。3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示图1十二进制计数器连接图4.建立VWF文件,仿真后得到结果如图2

2021-07-22 06:33:31

二进制计数器在时钟稳定的情况下出现跳变的情况

如题,LZ采用外部50M时钟作为输入,通过PLL锁相环分频得到100K的时钟。将100K的时钟作为二进制计数器的clk.但在SignalTap中发现,采到的数据在上升沿变化后,等时钟维持稳定时,数据出现了变化。怕自己没说清楚,附上时序图和程序

2019-11-28 21:53:14

二进制计数器选择不同的开关

用二进制计数器实现控制选择不同的开关,电路输入信号为一路方波,当此信号的第一个方波信号输入时,电路使用开关1,当此信号的第二个方波信号输入时,电路使用开关2,本人小白,麻烦回答具体点,附上简单的电路图,谢谢啦

2017-06-26 09:30:44

二进制与十进制数对照显示实验相关资料下载

这是一个可以对照显示0~9这10个数字的二进制和十进制的电路。二进制数字用4个发光二极管显示;它们排成一行,亮表示1,灭表示0。十进制数字用一个数码管表示。数字的变化采用CD4040组成加法计数器,手动加1计数。

2021-04-27 07:21:40

二进制格雷码与自然二进制码的互换

。而绝对式编码器是直接输出数字量的传感器,它是利用自然二进制或循环二进制(格雷码)方式进行光电转换的,编码的设计一般是采用自然二进制码、循环二进制码、二进制补码等。特点是不要计数器,在转轴的任意位置

2011-03-08 14:16:59

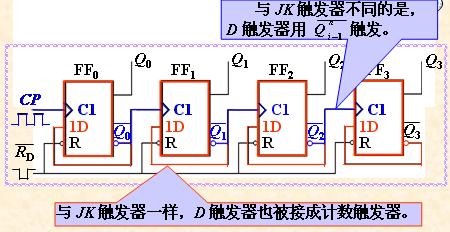

计数器及时序电路原理及实验

Altera EPM7128SLC84-15,时钟,四位八段数码管。三、实验内容1、用D触发器设计异步四位二进制加法计数器。2、用JK触发器设计异步十进制减法计数器。3、用74161两个宏连接成八位二进制同步

2009-10-10 11:47:02

N进制计数器的实现

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一个二-五-十进制计数器,能够进行二进制、五进制计数、通过简单联线组成十进制计数

2008-07-05 13:41:26

十二进制计数器

我的实训作业,求各位帮忙设计一个十二进制计数器,要电路仿真图设计任务与要求1.每隔1s,计数器增1。2.用数码管显示计数值。3. 当定时器递增到12时,定时器会自动返回到01显示,然后继续计时。我

2013-12-10 11:15:27

如何使用USART接收二进制数

我想制作一个以8个LED的形式实现二进制计数器。该计数器通过USART发送一个8位二进制数,并让8个LED显示数字(如果位为0,则指示灯熄灭,当位为1时指示灯亮)。这样做的最佳方法是什么?

2018-10-08 14:07:42

如何理解二进制运算规则 二进制是如何运算的

二进制运算规则二进制的运算算术运算二进制的加法:0+0=0,0+1=1 ,1+0=1, 1+1=10(向高位进位);二进制的减法:0-0=0,10-1=1(向高位借位) 1-0=1,1-1=0 (模

2019-12-11 17:49:02

怎么使用LUT设计一个4位二进制上变频计数器

嗨,我需要使用LUT设计一个4位二进制上变频计数器。我正在尝试遵循多路复用器方法。任何想法都非常感谢。谢谢小学以上来自于谷歌翻译以下为原文Hi , I need to design a 4bit

2019-02-14 11:29:07

怎么实现二进制计数器?

大家好,由于我是初学者,我尽可能多地尝试,看看我是否能够克服编程FPGA的学习曲线。这次我用VHDL实现了一个二进制计数器。图书馆IEEE;使用IEEE.STD_LOGIC_1164.ALL

2020-03-13 09:16:40

求助,同步二进制减法计数器的状态表该怎么画?

请问各位,同步二进制减法计数器的状态表该怎么画?之前只做过同步加法和异步减法,现在混淆了,同步减法的次态是代入特性方程算出来之后再作为下一个初态,还是直接递减不用算?

2022-11-23 20:44:42

浅析计数器的组成部分及其功能

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-12-08 08:32:28

集成四位二进制计数器

④ 构成脉冲分频器集成十进制计数器【74LS290】集成十进制计数器【74LS390】1. 集成四位二进制计数器【74LVC161】(1) 逻辑符号CR:CR:CR: 异步置0端。优先级最高。PE:PE:PE:并行置数端。次高优先级。TC:TC:TC:进位信号。CEP,CET:CEP

2021-07-29 07:20:09

异步时序控制器的设计

设计一脉冲异步二进制加1/减1计数器.电路有一输入线X,其信号为脉冲.另一信号M是电位,当M=0时,电路为加1计数器,当M=1时电路为减1计数器。使用钟控D锁存器实现。

2010-09-28 10:30:47 0

0

0

0十进制计数器

十进制计数器

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特别是当二进制数的位数较多时,阅读非常困难,还

2007-06-20 13:46:05 4188

4188

4188

4188什么是二进制计数器,二进制计数器原理是什么?

什么是二进制计数器,二进制计数器原理是什么?

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 30352

30352

30352

30352十进制计数器,十进制计数器原理是什么?

十进制计数器,十进制计数器原理是什么?

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特

2010-03-08 13:19:54 24108

24108

24108

24108本的二进制加法/减法器,本的二进制加法/减法器原理

本的二进制加法/减法器,本的二进制加法/减法器原理

两个二进制数字Ai,Bi和一个进位输入Ci相加,产生一个和输出Si,以及一个进位输

2010-04-13 11:11:55 5132

5132

5132

5132异步二进制加法计数器时序分析

计数器是一种常用的数字部件,是触发器的重要应用之一。顾名思义,计数器就是能够累计输入脉冲数目的数字电路。它是一种记忆系统,除用作计数外,还可用作分频、定时等

2011-04-19 11:29:28 12187

12187

12187

12187

74LS161异步置零法构成任意进制计数器的Multisim仿真

介绍了集成4位二进制计数器 74LS161 异步置零法构成任意进制计数器的 Multisim 仿真方案,即以波形方式显示计数器的计数过程、过渡状态形成异步置零信号的过程,用四踪示波器以面板

2011-08-05 14:25:22 336

336

336

336CC4060—14位二进制串行计数器

CC4060 由一震荡器和14 极二进制串行计数器位组成,震荡器的结构可以是RC 或晶振电路。CR 为高电平时,计数器清零且振荡器使用无效,所有的计数器位均为主从触发器。

2012-03-29 15:01:57 198

198

198

198二进制计数器74hct4020资料

Harris CD74HC4020和CD74HCT4020为14级纹波进位二进制计数器。所有计数器级都是主从触发器。阶段状态提前一次计数每个输入脉冲的负时钟转换;a高MR线上的电压水平将所有计数器重置为零状态所有输入和输出都经过缓冲。

2022-07-10 10:25:33 12

12

12

1224进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81二进制与十进制数对照显示实验,十进制,二进制对照

CD4040组成加法计数器,手动加1计数。

2.二进制与十进制数字对照显示实验 本电路可以形象地显示0~9的二进制数。按动加1按钮AN2,计数器的输入端CP得到一个负脉冲信号,计数器进行

2018-09-20 18:26:41 2326

2326

2326

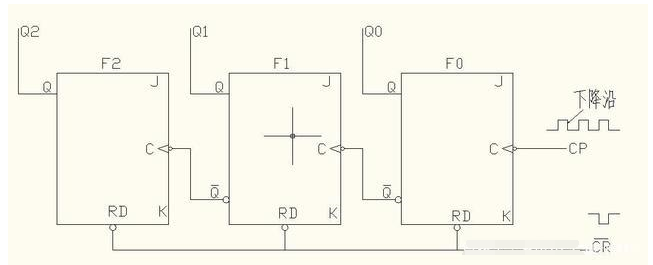

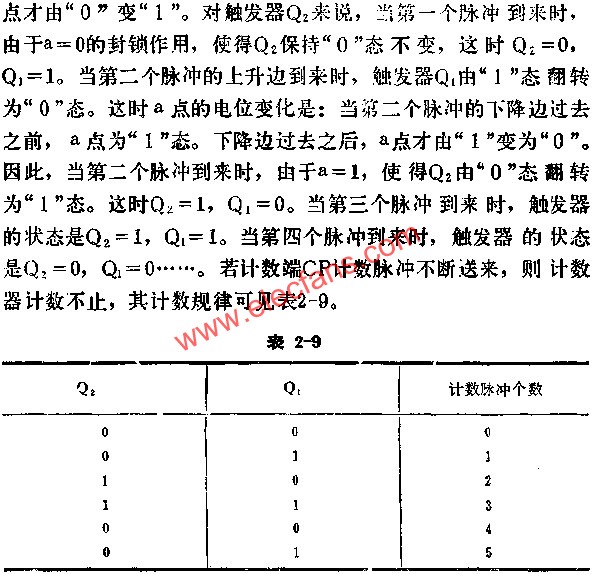

2326减法计数器的结构原理

该计数器是一个3位二进制异步减法计数器,它与前面介绍过的3位二进制异步加法计 数器一样,是由3个JK触发器组成,其中J、K端都悬空(相当于J=1、K=1),两者的不同 之处在于,减法计数器是将前一个触发器的Q非端与下一个触发器的CP端相连。

2021-04-18 11:19:47 16340

16340

16340

16340

同步计数器和异步计数器的区别主要在哪里

、应用等方面。 一、工作原理 同步计数器:同步计数器的工作原理是,在时钟信号的驱动下,对输入的二进制数进行加法或减法运算,从而得到计数值。在每个时钟周期内,同步计数器的计数值都会根据输入的二进制数进行更新。因此,同

2023-12-13 14:54:24 1724

1724

1724

1724 电子发烧友App

电子发烧友App

评论