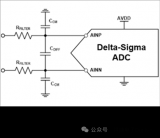

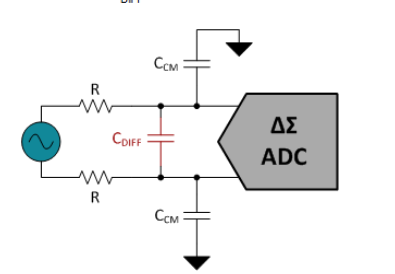

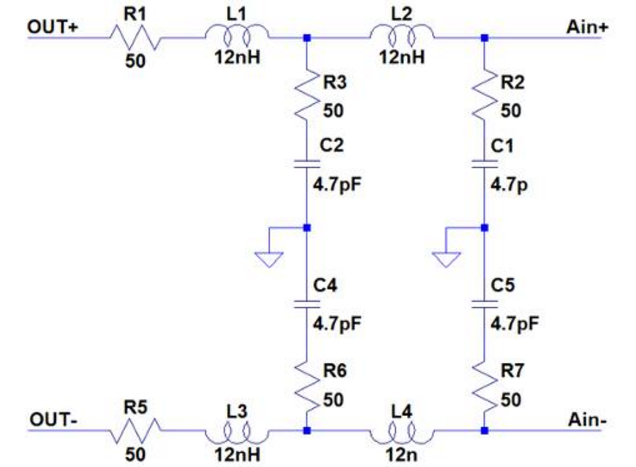

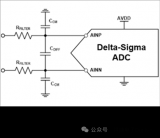

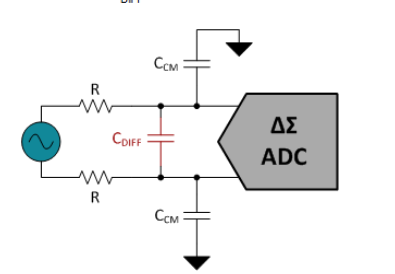

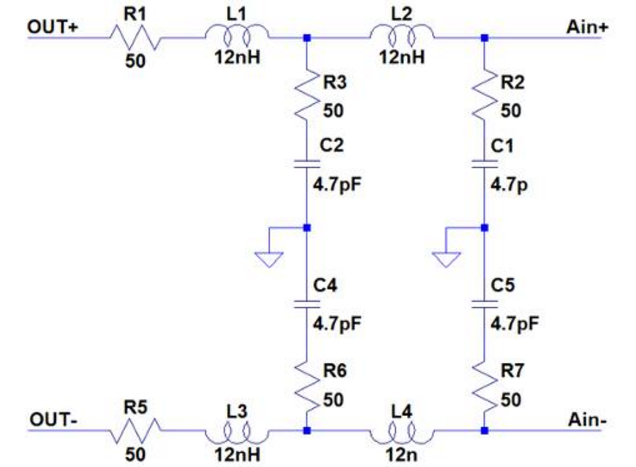

低速 Δ-Σ ADC 通常需要一个简单的单极 RC 滤波器来减少混叠效应。对于差分信号,滤波器结构通常由两个滤波路径组成:一个差分滤波器(源自两个滤波器电阻 RFILTER 和差分电容器 CDIFF

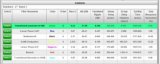

2024-01-11 09:16:51 3108

3108

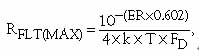

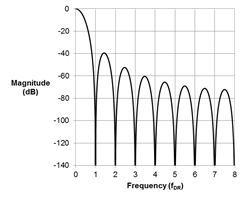

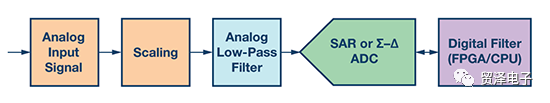

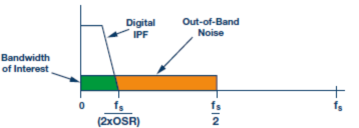

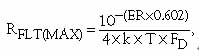

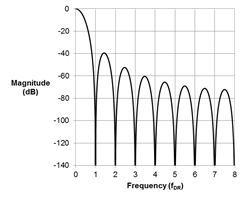

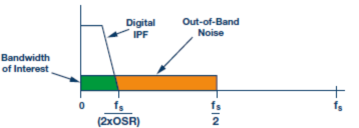

在我的上一篇文章中,我讨论了增量-累加模数转换器 (ADC) 的2个重要特点。这2个特点简化了抗混叠滤波器的设计:一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号

2018-05-22 09:17:52 7284

7284

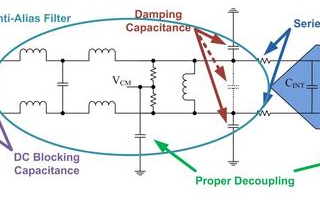

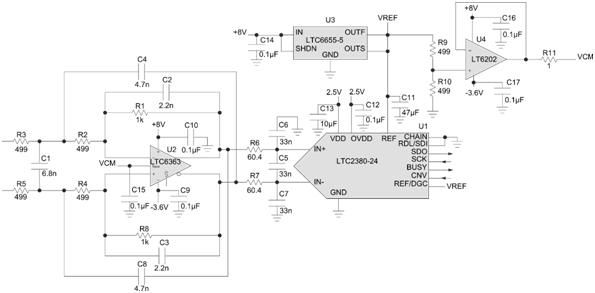

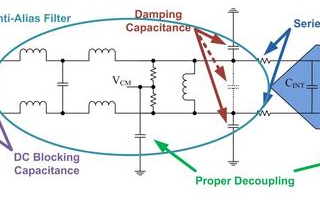

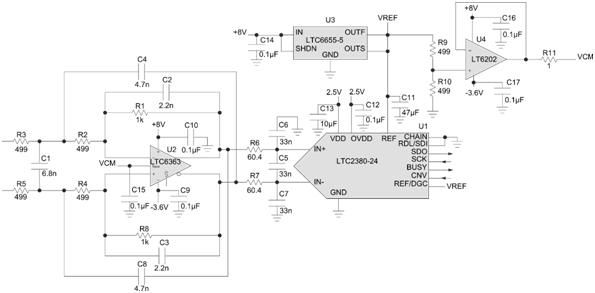

在考虑噪声因素以及与ADC模拟输入和共模电压节点有关的其他失真情况时,自带开关电容输入采样网络的ADC同样也可作为一个简单的指标。图1显示集成驱动放大器和抗混叠滤波器(AAF)的典型ADC模拟输入。

2020-09-02 10:01:02 1551

1551

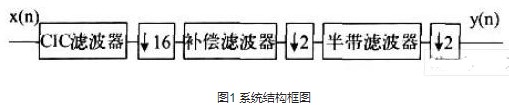

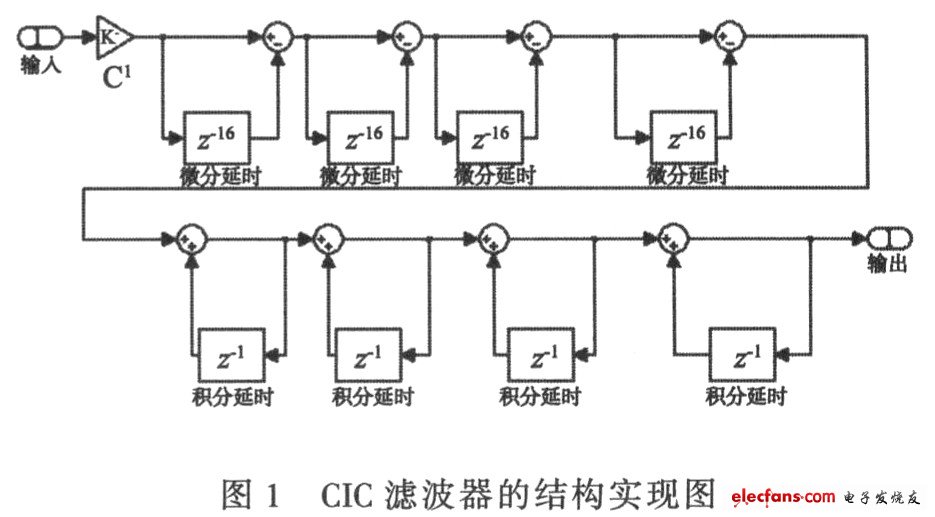

信号依次经过积分,降采样,以及与积分环节数目相同的梳状滤波器。在内插CIC中,输入信号依次经过梳状滤波器,升采样,以及与梳状数目相同的积分环节。 CIC滤波器的发明者是 Eugene B. Hogenauer,这是一类使用在不同频率的数字信号处理中的滤波器,在内插和抽取中使用

2020-12-05 10:21:00 3636

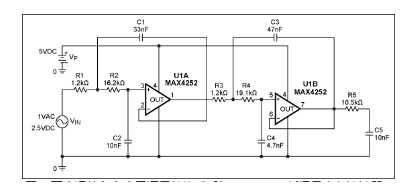

3636 对于许多ADC应用,缓冲器输入端的简单RC滤波器将提供足够的抗混叠滤波。对于需要高阶滤波器的应用,通常使用有源滤波器。该滤波器中的有源元件必须具有足够的带宽、快速建立、低噪声和低失调,以便在信号到达ADC之前不会损坏信号。

2023-01-06 09:17:46 3902

3902

? 答案: 为了减小模拟信号链的尺寸,降低其成本,并提供ADC抗混叠保护(ADC采样频率周围频段中的ADC输入信号不受数字滤波器保护,必须由模拟低通滤波器(LPF)进行衰减)。20 V p-p LPF

2023-04-23 16:59:44 925

925

1 ADC采样模型

(本文为笔者早期所写,当时对卡尔曼滤波器理解尚未透彻,如今回顾,该模型还有所缺陷,

假设ADC采样的值已经为稳定状态,设 k + 1 k+1 k+1时刻ADC采样值为 X k

2025-12-01 07:44:27

限制。当今的替代方案是,借助更经济的现代ADC的高采样速率,达到运用过采样技术的目的。图2.通过添加数字抽取滤波器比较频谱噪声密度以高于奈奎斯特定理要求的最小值的FSE速率对信号进行采样,可以通过

2021-08-04 07:00:00

我看ADS7066有可编程滤波器,请问使用该滤波器时,是否可以简化设计抗混叠滤波的截止频率?是否会有像SD ADC一样的过采样效果?

例如,采样10KHz采样频率,设置过采样为16倍,请问ADC

2024-11-25 07:29:54

什么是抽取?DDC的作用是什么?DDC滤波器应该多宽?DDC滤波器的频率是固定的吗?DDC滤波器是否影响SNR和SFDR?ADC能否提供多个DDC?

2021-05-21 06:34:42

本帖最后由 xizhong1991 于 2016-8-18 17:08 编辑

请教各位前辈一个问题 ,我本来的信号的AD采样率是92.16MHz,带宽为5MHz,我用FIR滤波器对它滤波,但是

2016-08-18 17:07:34

的前端设计中,往往要在输入端加一RC无源低通滤波器,技术资料在计算截止频率是并没有考虑到SAR ADC内部输入端的负载(开关的等效电阻和采样电阻),为什么??还有,RC低通滤波器的引入就会为系统带入一个极点,会影响到稳定性,设计时是不是要分析下稳定性以避免采样电路发生振荡??

2019-01-08 14:06:26

1、miniDSP可以做什么工作?

2、降采样滤波器是通过miniDSP实现的吗

2024-10-25 09:33:56

我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR)的因子抽取调制器采样频率

2018-08-30 15:05:47

一般的∑-∆型ADC 都内置有数字滤波器,这些数字滤波器对信号会产生相移吧,这个相移有多大,对做数字PID有影响吗?

2023-12-07 06:22:55

各位好!想请教如下问题:在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。我想请教的是:用RC低通滤波的话,转折频率是可以满足,但是RC

2019-05-17 13:30:09

的卷积;奈奎斯特脉冲可以表示为 sinc(t/T) 函数与另一个时间函数的乘积。因此,奈奎斯特滤波器以及相应的奈奎斯特脉冲为无穷多个,其中,常用的是升余弦成形滤波器,如下图所示,其中 α称为滚降系数

2008-05-30 15:51:15

这是一个温度传感器采样电路,其采样电压时R555上的电压。此电路图中的R554和C546是构成RC滤波电路,为什么采样后的电位经过RC滤波器到达单片机后,不会在R554上产生压降呢?求高手剖析下这个简单的电路图?

2015-01-20 20:15:38

应用需求的最佳滤波方案(有时称为滤波器类型)。一般情况下,采用过采样、而且过采样频率越高,滤波器设计越容易。但是,过采样需要更高速率的ADC,成本也越高。例如,过采样因子为8时,采样频率是最高信号频率的八

2019-01-02 19:03:43

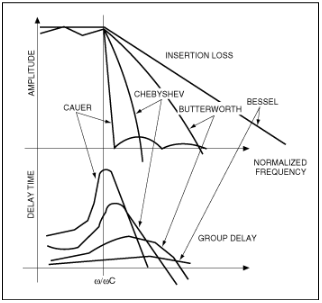

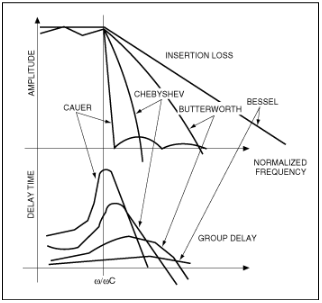

几乎所有电子电路中都能看到有源模拟滤波器的身影。音频系统使用滤波器进行频带限制和平衡。通信系统设计师使用滤波器调谐特定频率并消除其它频率。为了使高频信号衰减,所有数据采集系统都在模数转换器(ADC

2019-07-31 06:24:00

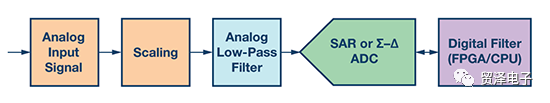

本文介绍了一个用于带宽150 kHz、精度16 bit的高精度、宽带∑-△模数转换器中的降采样低通滤波器。本设计可以集成在SOC芯片中,主要应用于医疗仪器、移动通信、过程控制和PDA等领域。

2021-04-12 07:02:56

以LTE无线通信系统为例,提出了一种完整的降采样FIR滤波器的设计和硬件实现方案。该方案在利用FDAtool得到滤波器系数之后再进行定点化,并将各系数拆分成2的幂次方相加减的形式,以便进行移位

2021-04-14 06:56:15

的不同点,提出采样回路中低通滤波器设计的重要性和特殊性。并针对这些分析提供了一套切实可行的降低电流采样回路干扰的解决方案,在实际应用中取得了明显的效果改善。

2019-10-21 06:08:53

的不同点,提出采样回路中低通滤波器设计的重要性和特殊性。并针对这些分析提供了一套切实可行的降低电流采样回路干扰的解决方案,在实际应用中取得了明显的效果改善。

2019-10-18 08:17:21

怎么利用赛灵思FGPA实现降采样FIR滤波器?这种滤波器在软件无线电与数据采集类应用中都很常见。

2019-08-15 08:21:22

在我的上一篇文章中,我讨论了增量-累加模数转换器 (ADC) 的2个重要特点。这2个特点简化了抗混叠滤波器的设计:一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号

2018-09-05 14:52:59

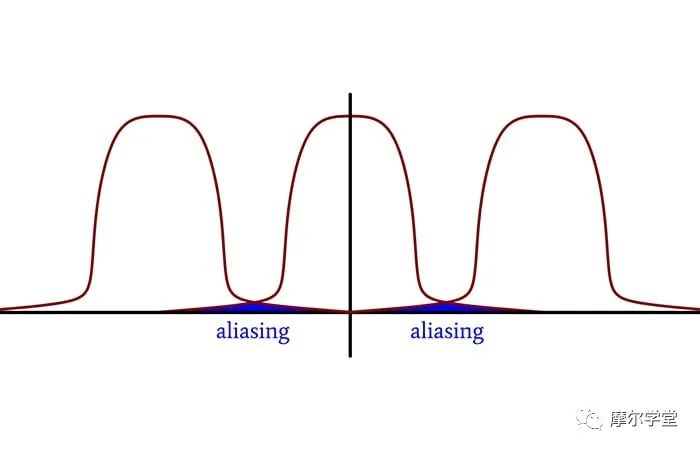

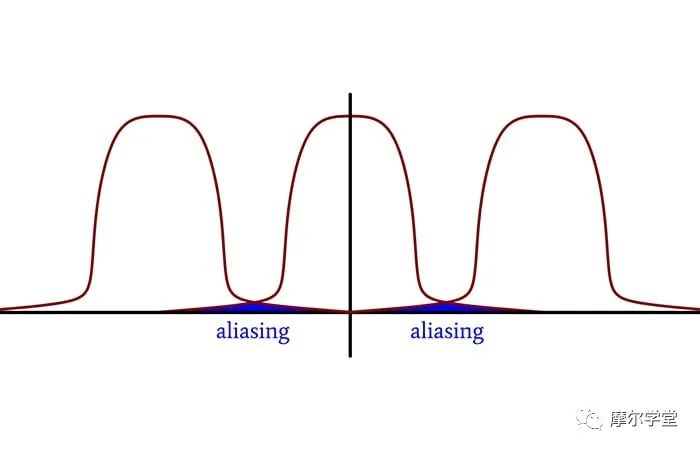

,根据要衰减多少频率分量来选择ADC采样率,这些频率分量将混叠到感兴趣的频谱中。假设您使用一阶RC低通滤波器作为抗混叠滤波器,其截止频率为20 kHz。频率响应如下所示:如果以100 kHz采样,则折叠

2020-09-18 10:12:55

各位大侠,小弟最近要设计一个用于sigma-delta ADC的数字抽取滤波器,甚是着急,但是苦于毫无头绪,敬请各位高手指点啊。下面是设计指标: 信号频率为250hz,调制器采样频率频率为

2012-02-26 22:00:16

各位大侠,小弟最近要设计一个用于sigma-delta ADC的数字抽取滤波器,甚是着急,但是苦于毫无头绪,敬请各位高手指点啊。下面是设计指标: 信号频率为250hz,调制器采样频率频率为

2012-02-26 15:52:55

调谐特定频率并消除其它频率。为了使高频信号衰减,所有数据采集系统都在模数转换器(ADC)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号

2019-07-29 07:15:50

(ADC)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号到达ADC之前或者离开DAC之后,消除叠加在信号上面的高频噪声。如果ADC的输入

2019-08-20 07:46:51

各位好!想请教如下问题:

在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。

我想请教的是:用RC低通滤波的话,转折频率是可以满足

2025-01-16 07:43:58

高ADC SNR。 它还能放宽滤波器滚降要求,从而减轻抗混叠滤波器的压力。 过采样降低了对滤波器的要求,但需要更高采样速率ADC 和 更快的数字处理。1. 对ADC 使用过采样速率所取得的实际SNR

2018-10-16 18:45:40

类器件被放置在ADC之前,用来衰减信号中Nyquist频率以上的成分,即高于ADC采样率一半的信号分量。这些滤波器频率响应的过渡带通常都设计得尽可能陡,目的是尽可能将截止频率以上的信号统统滤掉

2021-05-14 07:55:00

请问信号经过有源低通滤波器,需要考虑压降吗?信号由传感器输出经过滤波电路。再最后输出来。

2018-01-16 12:45:58

大家好!我看一些电能电量分析采集的文献中提到对信号进行FFT,所以要在ADC前端设计抗混叠滤波器,以避免产生延拓频率的噪声。一般采样频率为fs时,滤波器截止频率为fs/2。如果我不对信号进行

2018-10-09 16:08:19

非线性系统的状态方程和观测方程不准确时,非线性自适应采样滤波器的滤波精度将偏离真实值;严重时将引起滤波器的发散,得到完全虚假的滤波值,失去了滤波原本的意义。为

2009-12-14 14:06:22 11

11 基于频率采样法FIR数字滤波器的设计:在研究FIR数字滤波器的基础上,介绍了应用MATLAB软件设计有限长冲激响应(FIR)数字滤波器的流程。并以低通数字滤波器为例实现仿真过程。仿真

2010-03-31 09:23:35 67

67 集成方案简化模拟滤波器设计

本篇应用笔记介绍开关电容滤波器用于ADC (模数转换器)输入端抗混叠和降噪以及DAC (数模转换器)输出端信号重建滤波的优势。总结了MAX74xx

2009-12-19 12:05:43 1640

1640

模拟滤波器注入噪声原理及设计

有时候,事情根本没有意义!例如,您 Δ-Σ ADC 输入端 RC 滤波器或放大器的低通滤波器会产生更大噪声的数字输出

2010-03-19 17:00:33 1721

1721

如何使用模拟滤波器注入噪声

例如,您 Δ-Σ ADC 输入端 RC 滤波器或放大器的低通滤波器会产生更大噪声的数字输出。难道您没有设计过降低噪声的

2010-03-23 08:57:02 1060

1060 滤波器,滤波器电路,滤波器原理

一、概述

1.定义

凡是可以使信号中特定的频率成分通过,而极大地衰减或抑制其他频率成分的装置或

2010-03-24 13:58:57 2774

2774 光滤波器,什么是光滤波器

基于干涉原理的滤波器:熔锥光纤滤波器、Fabry-Perot滤波器、多层介质膜滤波器、马赫-曾德干涉滤波

2010-04-02 16:54:04 2482

2482 本文主要论述了用于音频系统ADC的过采样抽取滤波器的设计 系统论述了滤波器的多级实现

2011-04-19 10:21:56 94

94 根据实际的研发过程,详细讨论了音频ADC中 Sigmadelta 调制器的设计过程,即调制器系数的生成方法 并且深入的研究了降采样的作用和工作原理,并在此基础上给出了降采样滤波器的具体

2011-08-29 16:03:59 51

51 引 言 IIR 滤波器 不易做成线性相位,FIR滤波器只要满足一定条件就可做成线性相位,FIR滤波器有传统的设计方法,如窗函数法、频率采样法、切比雪夫逼近法等;曾喆昭等人提出了一种

2011-09-05 14:27:29 3327

3327 CIC滤波器是常用于多速率采样抽取或内插过程中的高效滤波器,具有结构简单,易于工程实现的特点。以提高采样速率为例,首先介绍了内插理论和CtC滤波器原理,重点给出了CIC滤波器

2011-09-20 15:12:49 73

73 本文首先推导出过采样滤波器组精确重构的条件,由于此时所需的约束条件数比临界采样时少,因而可以设计出频域衰减特性更好的滤渡器组 然后提出了精碲重梅约束条件下原壅低通滤

2012-03-19 15:39:45 12

12 您有没有想过Σ-Δ模数转换器(ADC)如何才能在不同带宽下获得如此高的分辨率?秘诀就在于数字滤波器。Σ-Δ ADC之所以与其他类型的数据转换器不同,是因为它们通常集成有数字滤波器。本系列博文分为三部分,我将在第一部分中讨论数字滤波器的用途,以及常用于Σ-Δ ADC的一些数字滤波器。

2016-06-09 03:37:00 10124

10124

常用的Σ-Δ_ADC数字滤波器类型,学习资料,感兴趣的可以瞧一瞧。

2016-10-26 17:00:40 0

0 基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 采样率转换中Farrow滤波器实现结构研究

2017-02-14 17:13:52 58

58 滤波器的基础是谐振电路,只要能构成谐振电路组合就可实现滤波器。滤波器有4种基本原型,即低通滤波器、带通滤波器、带阻滤波器和高通滤波器。实现滤波器就是实现相应的谐振系统。电感、电容形成的滤波器,称为集总参数滤波器;各种射频/微波传输线形成的谐振器,称为分布参数滤波器。理论上,滤波器是无耗组件。

2017-05-03 16:20:54 20627

20627

网络应尽可能接近50 Ω,以便最大限度地吸收此非线性电荷。使用高吸收性滤波器可抑制采样过程中产生的非线性信号音,从而改善SFDR。

2017-09-16 06:26:00 8592

8592

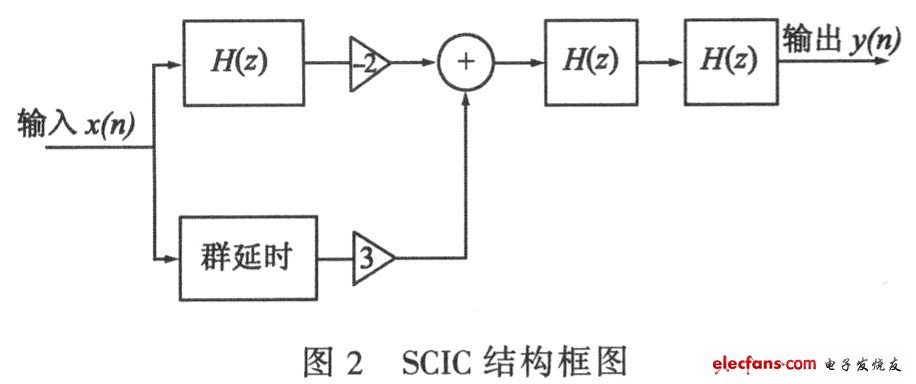

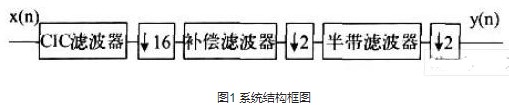

针对软件无线电接收机数字下变频中高速数字信号的降采样需求,利用半带滤波器及级联积分梳状滤波器,设计了一种半带滤波器前置的多级抽取滤波器架构。通过Simulink搭建系统模型验证之后,利用Xilinx

2017-11-17 09:01:55 6493

6493 )前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号到达ADC之前或者离开DAC之后,消除叠加在信号上面的高频噪声。如果ADC的输入信号超出转换器采样频率的一半

2017-12-05 13:12:18 715

715

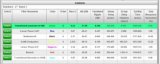

设计了采样频率为640 MHz、过采样率为64的高频数字抽取滤波器。该数字抽取滤波器由CIC(Cascaded Integrator Comb)滤波器(降16倍)、CIC补偿滤波器(降2倍)和半带

2018-02-21 12:08:00 2297

2297

∑-△调制器与数字抽取滤波器是∑-△ ADC 实现16bit 以上精度的关键电路模块。∑-△调制器依靠过采样与高阶闭环负反馈控制实现的噪声整形技术,将基带内的量化噪声搬移到高频段,而数字抽取滤波器

2019-05-08 08:18:00 5732

5732

滤波器系数决定滤波器特性,理论上讲,只用一组滤波器系数是不能实现可变参数滤波器的。由2节可知,下抽取率N与滤波器截止频率成反比,与阻带衰减成正比,与滤波器长度成正比。假设下抽取率为N0时滤波器系数h(n),n=0,1,2…L-1,我们怎样通过h(n)这组基准系数来获得N不等于N0时的滤波器系数呢?

2018-10-26 14:37:36 9955

9955

具有可配置数字滤波器的32位过采样ADC

2019-08-19 06:03:00 4709

4709 (ADC)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号到达ADC之前或者离开DAC之后,消除叠加在信号上面的高频噪声。如果ADC的输入信号超出转换器采样频率的一半,则该信号的大小被可靠地转换;但是,在其变回数字输出时,频率也发生改变。

2019-05-07 16:12:30 7596

7596

数字滤波器通常位于FPGA、DSP 或处理器中。为了减少系统 设计工作,ADI 公司提供了一些集成后置数字滤波器的精密 ADC。例如,AD7606 集成了一个一阶后置数字sinc 滤波器用 于过采样。它很容易配置,只需上拉或下拉OS 引脚。

2019-08-22 10:34:50 6118

6118

类似于Δ-Σ型ADC过采样、高吞吐速率SAR ADC过采样还能改善抗混叠性能,并降低总噪声。 很多情况下,过采样是Δ-Σ型ADC的固有属性,可以顺利实现,并且集成数字滤波器和抽取功能。 然而

2019-09-14 10:05:00 4627

4627

针对Σ△ADC输出端存在的高频噪声问题,设计了一种 Sinc数字抽取滤波器,实现了Σ-△调制器输出信号的高频滤波。分析了Sinc滤波器的结构原理,基于 Spartan6FPGA进行滤波器的设计与实现

2020-08-26 17:12:00 17

17 模拟滤波器在电子信号合成系统中应用广泛,可为ADC提供抗混叠和降噪,为DAC提供信号重建滤波¹。不同的设计要求需要使用不同的滤波器架构,常用的滤波器有贝塞尔、巴特沃思以及椭圆滤波器。

2020-11-10 16:22:42 10415

10415

模拟滤波器在电子信号合成系统中应用广泛,可为 ADC 提供抗混叠和降噪,为 DAC 提供信号重建滤波¹。不同的设计要求需要使用不同的滤波器架构,常用的滤波器有贝塞尔、巴特沃思以及椭圆滤波器。贝塞尔

2020-12-07 22:48:00 6

6 几乎所有数据采样系统中扮演着重要角色。大多数模 / 数转换器(ADC)都安装有滤波器,滤除超出 ADC 范围的频率成分。有些 ADC 在其结构本身上就具有滤波功能。我们接下来讨论数据采样系统、滤波要求以及与混叠的关系。

2020-12-11 22:57:00 5

5 LTC2508-32: 具可配置数字滤波器的 32 位过采样 ADC 数据手册

2021-03-21 07:20:35 15

15 ,模拟滤波器又称为抗混叠滤波器 (AAF)。混叠频段中不需要的信号和噪声可能源自驱动放大器、电源切换引入的杂散,甚至是意外的干扰因素(干扰器)。 混叠频率大小直接取决于 ADC 采样速率,数据转换器在给定瞬时带宽下的工作速度越快,混

2021-06-22 09:54:28 3832

3832

简易LC滤波器设计方案

2021-06-22 10:01:49 85

85 基于FPGA的_ADC数字抽取滤波器Sinc_3设计(现代电源技术基础杨飞)-该文档为基于FPGA的_ADC数字抽取滤波器Sinc_3设计总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 13:58:04 27

27 减小模拟信号链的尺寸和成本,并提供ADC抗混叠保护(ADC输入信号位于ADC采样频率附近的频带中 不受数字滤波器保护,必须由模拟低通滤波器LPF衰减)。20 V p-p LPF 驱动器的典型应用是

2023-02-15 10:08:20 1240

1240 通过驱动ADC实现优化的混合信号性能,这是一大设计挑战。图1所示为标准的驱动器ADC电路。在ADC采集期间,采样电容将反冲RC滤波器中指数衰减的电压和电流。混合信号ADC驱动器电路的最佳性能受到多个

2023-02-22 07:15:07 2134

2134 数字滤波器的原理基于数字信号处理技术和滤波器算法,通过对离散时间信号进行处理和滤波,实现对信号频率的选择性衰减和增强。数字滤波器的输入信号为经过模数转换器转换的模拟信号,经过采样后变成离散时间

2023-02-24 11:23:36 6615

6615 本文研究了奈奎斯特-香农采样定理的一个重要方面,并解释了它与模数转换中抗混叠滤波器需求的联系。

2023-05-19 15:17:39 4679

4679

抗混叠滤波器:这一类器件被放置在模数转换器(ADC)之前,用来衰减信号中Nyquist频率以上的成分,即高于ADC采样率一半的信号分量。这些滤波器的响应通常都设计得尽可能陡,目的是尽可能将截止频率

2023-06-10 16:35:19 1803

1803

低通滤波器的截止频率和采样频率 低通滤波器是一种常见的信号处理技术,它被广泛应用于声音、图像和视频等领域。在实际应用中,我们需要了解其截止频率和采样频率,以便为信号提供最佳过滤效果。 一、低通滤波器

2023-09-12 14:52:03 24751

24751 电子发烧友网站提供《任意重采样滤波器设计应用说明.pdf》资料免费下载

2023-09-14 14:31:41 0

0 非常重要。 以下是选择SAR ADC前端RC滤波器的一些关键因素: 1. 带宽和采样率 前端的滤波器应该能够过滤掉不需要的高频信号,以确保ADC的输出仅包含所需的信号,并且完整而清晰。选择滤波器的截止频率应该低于系统带宽的一半,以确保信号的完整性。对于SAR ADC而言,采样率

2023-09-13 10:01:45 1551

1551 什么是数字滤波器的采样速率?和输入信号的频率有什么关系? 数字滤波器的采样速率是指数字滤波器输入信号的采样频率,也称为采样率,通常用赫兹(Hz)表示。在数字信号处理中,为了实现对模拟信号的数字化

2023-10-20 15:02:30 4402

4402 高通滤波器、低通滤波器、带通滤波器怎样测幅频特性? 高通滤波器、低通滤波器和带通滤波器是常用的滤波器类型,它们在信号处理中起到了至关重要的作用。测量它们的幅频特性是评估和理解这些滤波器性能的重要手段

2024-03-28 17:28:51 7913

7913 电子发烧友网站提供《Δ-Σ ADC中的数字滤波器类型.pdf》资料免费下载

2024-09-06 09:50:13 4

4 电子发烧友网站提供《用于AIC111的高效重采样滤波器.pdf》资料免费下载

2024-10-23 10:13:51 0

0 本文为手把手教学ADC采样及各式滤波算法的教程,本教程的MCU采用STM32F103ZET6。以HAL库的ADC采样函数为基础进行教学,通过各式常见滤波的实验结果进行分析对比,搭配VOFA+工具直观的展示滤波效果。

2024-10-28 10:51:11 11469

11469

LHA5278H是一款8通道同步采样24位Z△ADC,其输出速率在使用FIR滤波器时高达512kSPS,使用SINC滤波器时最高达1.024MSPS。

2025-11-25 09:08:16 1025

1025

电子发烧友App

电子发烧友App

评论