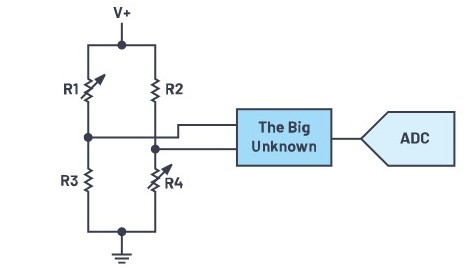

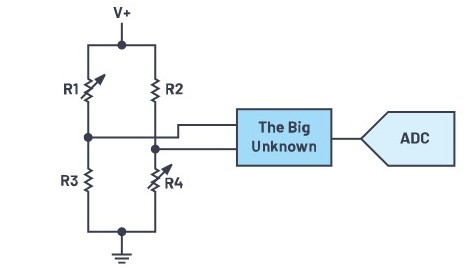

数据采集和通用测试测量设备中使用的精密信号链必须适应宽广的输入电平范围。信号链可能需要提供高输入阻抗,同时支持增益和衰减,并调整共模电平以确保信号落在ADC的适当输入范围内。

2023-07-07 12:35:48 371

371

匹配传感器输出和 ADC 输入范围可能很难,尤其是要面对当今传感器所产生的多种输出电压摆幅时。本文为不同变化范围的差分、单端、单极性和双极性信号提供简便但高性能的 ADC 输入驱动器解决方案,本文

2013-07-23 09:26:46 3545

3545 在本文中,“传感器”和“输入信号”可以互换使用,代表ADC信号链的任何类型的电压输入。ADC信号链的输入信号可以是传感器、来自某些源的信号或控制回路的反馈。

2021-08-18 10:26:41 4810

4810

16位数据寄存器中。模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。ADC 的输入时钟不...

2021-08-05 06:53:44

示波器使用8位ADC来数字化所输入的信号,这主要由示波器的应用需求及ADC的技术发展所决定。随着一些新兴应用的不断推进,8位ADC往往会因为噪声的原因而丢失细节,无法很好地满足市场需求。力科

2019-06-10 08:13:51

我用的是AD9220采集信号,这款ADC数据是并行输出,测试的时候我给的0V输入(VINA-VINB=0),其中有一位数据输出的电平应该一直是低,但是在时钟周期内会出现一段高的情况。如图,蓝色是时钟信号,黄色为我测试的其中一位数据输出信号:此款芯片的时序图如图:

2019-01-22 12:37:12

问一个ADC AD9628-125的问题,使用中发现,采样输出信号的底噪与输入信号功率关系密切,没有输入信号,噪底很干净,噪声水平与预期相当,使用19MHz -16dBm的单音输入测试,显示spur

2023-12-06 06:51:41

STM32家族中的所有芯片都内置了逐次逼近寄存器型ADC模块.内部大致框架如下:每次ADC转换先进行采样保持,然后分多步执行比较输出,步数等于ADC的位数,每个ADC时钟产生一个数据位。说到这里

2021-07-09 07:30:00

在使用STM32F030C8 adc进行采集时,启动采样时在输入信号会出现一个很大的过冲信号,尝试过单通道单次采样,单通道重复采样,均出现以上问题,下面是具体的采集波形,硬件电路信号由运放输出直接

2018-09-04 15:35:57

我有一个项目,用到AD7610BSTZ。一个现象是这样的:我输入的模拟量增加2MV,34401数字万用表可以测得。但是ADC转换的数字量并没有变化。不知道为什么? 另外一个问题是:ADC数据转换必须要用到采集保持IC吗?如果不用会对采集精度有影响吗?

2018-12-03 09:09:25

输出电阻rds和互导gm都会受到输出电压vgs的影响,那么在mos场效应管的小信号模型中,输出电阻和互导是否会受到交流信号的影响不断变化?

2023-04-28 14:32:13

用verilog 语言来写一个。。。当输入端4位数据发生变化时,输出端会输出一个脉冲信号,就仅输出一个就行,我想用数据变化产生的上升沿谢谢亲们了 {:1:}

2014-03-18 20:05:03

AD5326在使用中严格按照资料时序施加串行数据,并且在写入后经过readback验证,要转换的数确定已经写入输入寄存器,但是在写完数据 stop位后给出 LDAC信号,发现并没有转换后的数据输出。想知道AD5326具体使用方法,和注意事项。

2019-01-04 10:17:47

AD5684的命令位+地址位+数据位一共24位,但是SPI通信只能传送16位数据怎么办?请问有没有推荐的方案或者案例

2023-12-08 08:13:53

你好!我在数据手册上看AD8421可以单电源供电,但是我单电源供电后,输入正信号(0~50mV)3KHz正弦波,输出为1.26V直流信号。输入信号幅值和频率变化,输出均没有变化。附件是原理图:附件123.png52.7 KB

2018-09-03 14:05:31

我用的是AD9220采集信号,这款ADC数据是并行输出,测试的时候我给的0V输入(VINA-VINB=0),其中有一位数据输出的电平应该一直是低,但是在时钟周期内会出现一段高的情况。

如图,蓝色是时钟信号,黄色为我测试的其中一位数据输出信号:

此款芯片的时序图如图:

2023-12-12 07:29:21

设计了一个ADC电路,使用ADA4930-1放大器和AD9642-210BCPZ,芯片采样率在210M,在放大器输入端加3MHZ正弦波输入信号,测量放大器输出基本正常且为正弦波。FPGA控制

2018-11-12 09:54:32

Link传输的设置,但没有关于如何连接数据位的规范。块是否处理位到差分线的摄像机链接映射?以上来自于谷歌翻译以下为原文Can anyone describe how a 24-bit RGB data

2019-03-18 14:59:18

H750 UART 7数据位 + 校验接收数据异常的原因?如何解决?

2021-12-06 07:46:07

MODBUS rtu发送报文时,是将报文转换成二进制再从首到末尾依次按位发送的吗?数据位中间有没有间隔?

2024-01-18 17:50:32

首先我们先了解下“位”与“字”的区别,位一共有两种状态0和1,0代表关、1代表开,对用于PLC中的X、Y、M、S,处理关/开信号的软元件称之为位软元件。我们再说下字,字有单字和双字,单字由16

2020-12-09 16:51:35

STM32串口如何实现7位数据位?

2021-12-06 07:21:02

STM32实现7位数据位支持需要满足什么要求?

2021-12-03 07:40:17

各位TI的大神们:请教下,鄙人最近在开发一款数据采集系统,底端的传感器是0~10V模拟输出的,想在TI的网站找一款24位的直接能采集0~10V电压信号的芯片,竟然没找到,绝大部分都是最大支持到

2019-06-21 08:16:49

。 aduc7061内部应该有两个24位的ADC,但从读出来的数据看,[size=13.3333330154419px]ADC0DAT好像是16位的,不像是24位的ADC输出。[size

2018-09-27 11:43:42

如下图所示是RF开关hmc221的电路,工作频率2.1GHz,只使用其中一条通路RF1,RF2通过电容后经50欧电阻到地。但是实际调试中用频谱仪测输出频率和功率,在控制信号电平变化时,输出信号功率

2018-12-27 09:28:52

短路而损坏芯片!

**iEnable是数据有效标志,可以通过屏蔽IO区域来操作少量的IO变化,从而不影响其它端口的正常工作。比如8个IO口输入输出各4个,配置输出时需要屏蔽掉4个输入,否则输入将受

2023-06-10 12:56:48

labview出串口通讯能9个数据位吗?我单片机配置是9个数据位

2018-04-04 09:15:22

stm32中的串口通信中的USART_WordLength,数据位的长度包不包括开始位哪些?

2018-10-11 17:57:54

和精度都应当优于所选择的ADC。模拟放大器不仅能放大模拟输入信号,而且还具有阻抗变化的作用。对于输入电阻比较小的ADC,而信号源的内阻又比较大时,需要选用高输入阻抗、低输出阻抗的放大器,有时也可以加接电

2021-03-26 07:00:00

串口多机通讯,上位机如何设置串口9位数据位/TB8**常用的串口数据位设置只有5~8位,但对于多机通讯要求9位数据位,即要求通过设置TB8区分地址与数据的发送。**先贴一下多机通讯的过程:主机要发送

2022-02-23 07:28:55

原子哥在串口初始化中 void uart_init(u32 pclk2,u32 bound){。。。。USART1->CR1|=0X200C;//1位停止,无校验位.。。。。}没有对bit12进行或操作啊? 那岂不是到底是9位还是8位数据不确定了?谢谢指点!!

2019-06-13 04:35:10

我用vs2010,c++编写了一个串口助手程序,然后为什么端口号和校验位下拉菜单有显示,而波特率,数据位,停止位就没有呢,我的方法都是一样的啊。。。求大神指点

2020-03-12 03:45:07

您好:我使用ADA4930驱动器芯片直流耦合信号驱动ADC。当没有模拟信号输入的时候,adc会采集到毛刺信号。只要有信号输入之后,从此之后ADC就不会采到毛刺信号。请问是什么原因导致的。谢谢

2018-08-08 09:32:16

;每组输入信号(D3~D0)的数据位宽是可自定义的,因按键开关个数限制,在验证实验时将其位宽定为1位。表4.1给出了对应的真值表。原作者:语雀

2022-07-04 16:09:34

故障现象:

a、项目中使用AD9258-105芯片,上电默认不进行任何配置时,通道A或通道B的某些位没有输出(特别是低几bit,比如D0~D5。具体是哪些位,无规律),电压固定在0.2V

2023-12-13 08:05:07

512bit的数据同时输入),以达到更好的效果,但是当前的NICE接口的读写数据位宽都是32bit,

我的问题:

1. 是否可以在协处理器上添加另外的数据通道,比如AIcore的专用通路?

2. 是否可以

2023-08-12 07:40:33

1、 解决方案(必要的公式、文字等)在课外实验中,我们选择利用ADC对输入的信号进行采集,然后利用串口控制DAC的输出,实现通过串口控制DAC输出采集到的波形的功能。在本实验中,是通过判断串口发送

2019-07-05 06:42:13

aci_gap_get_oob_data 得到了数据配对数据包显示未设置 OOB 数据位。aci_gap_set_authentication_requirement(0x01 - 启用绑定0x01 启用 MITM0x02 仅限

2022-12-08 09:02:44

的一部分。数据采集系统的其他部分也可增加其灵活性,包括信号输入接口、参考电压接口、用于ADC的时钟和采样系统以及用于转换后ADC输出数据的数据管理。 通常情况下,模拟信号输入接口共享一个通用输入输出(I/O

2017-12-19 17:10:08

在驱动芯片信号端输入信号为什么没有输出

2019-06-20 10:07:05

任何人都可以帮助代码或功能,将在4位模式下接口4X20液晶和PIC18F46K22与端口1,2,3,4,而不是上或下Nybble,因为我发现的所有代码。我已经尝试改变4X数据位和掩码的移位,但是没有成功。我希望有人有一个功能,你可以改变数据位以外的只是nbyle。谢谢!

2019-11-07 09:41:34

如何收发数据位宽度为9位的数据?

2022-01-27 06:33:31

本帖最后由 liuyongwangzi 于 2018-6-21 09:44 编辑

ADC采样模拟信号提供表示输入信号的量化数字码。数字输出代码得到后处理,并且结果可以报告给使用该信息做出决定

2018-06-21 09:42:04

转换器的数字接口状态良好,然后检查转换器的输出是否普遍代表输入信号。之后,我再查看零输入(转换器噪声)。在您测得ADC噪声后,便可将输入短路接地。利用DAC,您可以将数字输入编程为模拟零输出。 此类

2016-01-29 14:47:40

如何测量不断变化的信号

2019-09-16 09:08:45

随着ADC的供电电压的不断降低,输入信号摆幅的不断降低,输入信号的共模电压的精确控制显得越来越重要。交流耦合输入相对比较简单,而直流耦合输入就比较复杂。 典型的例子是正交下变频(混频器)输出

2019-06-19 06:50:39

在做一个设计,需要至少14位的ADC(1.8mV的分辨率),输入的是一个差分信号(±1.5V)和一个temp信号。有没有单电源供电的双通道的ADC满足我这个设计条件啊?我在选型里面筛选了好久都没有

2019-05-08 14:58:16

ADC 利用高抽样率和数字信号处理技术,将抽样,量化、数字信号处理融为了一体,从而获得了高精度的 ADC,目前可达 24 位,主要应用于高精度数据采集特别是数字音响系统、多媒体、地簇勘探仪器、声纳等

2020-12-25 09:20:51

AD603级联构成的AGC电路的检波电路中,小信号输入检波电路,Vagc输出信号变化不明显,如何让输入的小信号,在Vagc的输出也能有明显变化。电路按照数据手册AD603级联构成的AGC参考电路

2018-07-31 08:40:25

故障现象:a、项目中使用AD9258-105芯片,上电默认不进行任何配置时,通道A或通道B的某些位没有输出(特别是低几bit,比如D0~D5。具体是哪些位,无规律),电压固定在0.2V左右;b

2018-08-14 07:38:50

的方法,信号输入端加隔值电容。用万用表实测当隔直电容前端(隔直电容前端连接AD)电压为零时,获得ADS805E的输出数字量不断变化,变化范围为20mv,可能是什么原因导致的(输入时钟1MHz)??4.

2019-03-01 13:46:19

PCB板制版后,进行硬件测试发现,VCO输出不随输入信号变化而变化,只保持输出最低频率,VCO单独测试可用,VCO控制电压为0V时输出27KHZ,5V时输出46KHZ,请问VCO输出不随输入信号变化而变化,保持输出27KHZ是怎么回事?

2016-10-26 10:18:14

如题,中文手册中有一句“ADC滤波器进行真24位信号处理,以正确的采样频率转换来自ADC过采样的多位原始数据,然后从数字音频接口输出。”,这里的ADC滤波器的位数,和ADC的位数一样吗?是不是WM8978的ADC输出也是24位呢?

2019-02-14 00:19:40

图一是“接收内容”创建字符串类的属性-显示样式(因为十六进制显示才能正常接收,否则乱码),图二是modbus rtu 协议的数据传输,图三是我接收的传感器传输的其中一组数据,请问如何实现数据位的提取?谢谢

2019-03-30 15:07:31

做一个频率电压转换器的仿真,lm358的输出端有信号,但是741的输出端并没有变化,甚至还是反向了

2018-12-22 13:01:36

图一是“接收内容”-创建-字符串类的属性-显示样式(因为十六进制显示才能正常接收,否则乱码),图二是modbus rtu 协议的数据传输,图三是传感器传输的“接收内容”中的一组数据,请问如何实现数据位的提取?谢谢

2019-03-30 15:16:17

最近正在调试AD5754,芯片电压正常,±12,3.3v,和2.5v都正常供入。但是用FPGA写驱动程序是发现,只能读,SDO信号数据位全为0。不能够写入寄存器。下面附上我的波形附件无标题.JPG8.1 KB

2018-08-24 11:18:35

要检查运放输入端的阻抗匹配,因为输入端的阻抗失配会改变输出失调电压,由于输出幅度受到限制,因此会减小ADC的动态范围。 捕获数字输出数据以很高的频率(1GSps甚至更高)对信号进行采样意味着由转换器

2019-05-30 05:00:04

随着ADC的供电电压的不断降低,输入信号摆幅的不断降低,输入信号的共模电压的精确控制显得越来越重要。交流耦合输入相

2010-11-26 10:27:59 4769

4769

任何通过时钟电路进入ADC的噪声都能直接到达输出端。ADC中此电路的噪声机制可认为是一个混频器。当看到噪声时,以这种方式考虑输入就真正能洞察一切了。通过时钟输入进入ADC的噪声频率将混入模拟输入信号,并出现在转换器输出端的FFT中。

2017-09-14 17:17:12 8

8 随着ADC的供电电压的不断降低,输入信号摆幅的不断降低,输入信号的共模电压的精确控制显得越来越重要。交流耦合输入相对比较简单,而直流耦合输入就比较复杂。 典型的例子是正交下变频(混频器)输出到ADC

2017-12-10 12:09:24 11432

11432

将以上草图上传到Uno32板上,然后从MPIDE打开串行终端窗口。 ADC样本(整数ADC输出)以1秒的间隔打印在窗口上。您可以观察这些数字如何随着LDR上光线的变化而变化。如果您将手指放在LDR上并阻挡掉落在LDR上的光,则ADC输出将突然下降。

2019-12-05 16:59:48 7889

7889

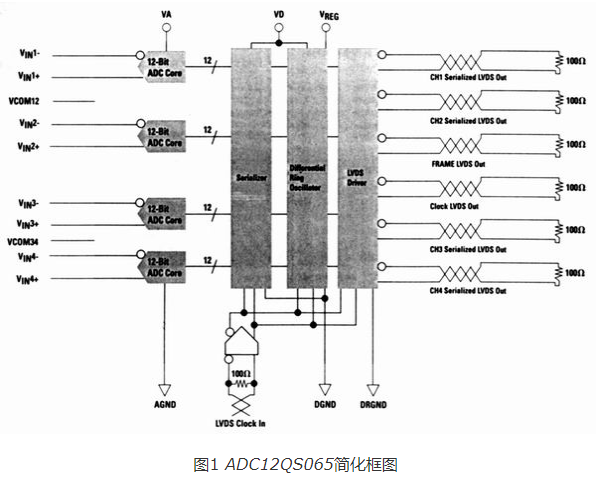

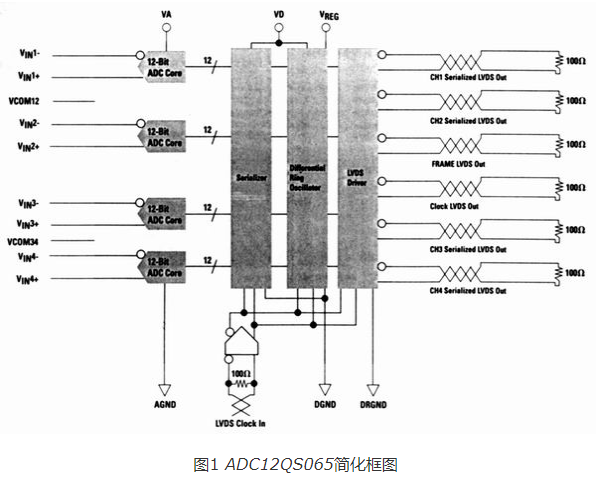

在输入信号转换数字数据之后,必须传输它们到DSP或ASIC/FPGA进行处理。流行的全差分输出信号传输是方便的。全差分的输出信号通过两条对称线给出和吸收电流。这种信号传输的一个例子是LVDS(低压差分信号)格式。ADC12QS065用LVDS来解决所有这些系统问题(图1)。

2020-04-04 17:43:00 2324

2324

这是一种纯粹的ADC驱动功能,无信号调理。 当前一级的驱动能力不够时,它为ADC提供高输入阻抗。 这种配置的噪声和功耗最低,因为没有附加电阻。 在单电源应用中,信号摆幅可能会受输入或输出放大器裕量要求的限制。 对于差分输入,可利用两个单位增益驱动器来实现高阻抗输入,参见CN0307。

2020-07-13 18:02:26 5247

5247

问题:有没有一个模块,能让我直接将微小的传感器输出讯号转换为ADC输入电压?

2021-04-03 09:11:00 1820

1820

STM32系列单片机控制寄存器只支持8、9位数据位。

2021-07-23 11:15:56 5603

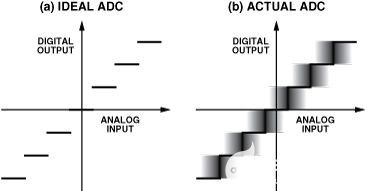

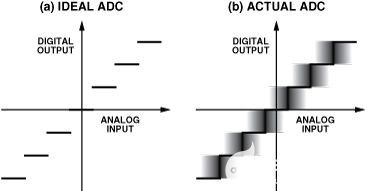

5603 这个情景真的令人很沮丧:你终于将模数转换器 (ADC) 搭建起来并开始运行,不过事情看起来有点儿不太正常。你输入了一个电压,不过ADC的输出有所不同。

出了什么问题?

看起来所有的设置都没有

2021-11-24 09:31:47 2421

2421 问题:STM32移植freemodbus 后测试时,只能使用无校验 ,设置奇偶校验时无法与上位机通讯解决方法如果串口助手使用串口配置为:数据位8 停止位1 有奇偶校验STM32需设置为:数据位

2021-12-24 18:44:23 19

19 基本输入输出Proteus图没有代码

2022-12-30 16:48:39 0

0 所有模数转换器(ADC)都有一定量的输入参考噪声,建模为与无噪声ADC输入串联的噪声源。不要将折合到输入端的噪声与量化噪声混淆,量化噪声仅在ADC处理时变信号时才有意义。在大多数情况下,输入噪声越少越好;然而,在某些情况下,输入噪声实际上有助于实现更高的分辨率。

2023-02-03 16:08:37 1267

1267

无源探头(探极)置于×10档时,输入示波器的信号如何变化?

2023-02-07 12:33:58 666

666

本应用笔记说明,ADC根据信号输入电平产生不同水平的噪声功率,并且ADC噪声会影响小信号和大信号电平极端情况下的整体接收器响应。如果在接收器设计中未正确考虑ADC噪声(和失真)功率的级联贡献,则转换器可能超出或低于任何特定应用的规定。

2023-02-25 11:40:40 1050

1050

在采样或子采样接收器设计中使用高性能奈奎斯特模数转换器(ADC)时,RF设计人员需要了解ADC在小信号和大信号输入下的噪声性能。接收器必须满足这两个信号电平极端下的灵敏度和阻塞(高电平干扰)要求

2023-03-02 15:15:10 930

930

数据采集和通用测试测量设备中使用的精密信号链必须适应宽广的输入电平范围。信号链可能需要提供高输入阻抗,同时支持增益和衰减,并调整共模电平以确保信号落在ADC的适当输入范围内 。 图1中的原理图显示

2023-07-07 18:40:03 531

531

FPGA相比MCU而言,在数据位操作上有很明显的优势。FPGA支持任意位拼接以及数据截取操作。本篇主要是总结和分享一些对数据位操作的实用语法技巧。内容不多,其中最最最重要的内容是数据的动态位截取操作。

2023-10-01 17:12:00 660

660

怎么办?晶振没有信号输出 晶振作为电子设备中常见的元器件之一,在电子系统中起到时钟信号供应的重要作用。然而,有时我们可能会遇到晶振没有信号输出的问题,这会严重影响设备的正常运行。本文将针对这一

2024-01-25 13:51:17 125

125

电子发烧友App

电子发烧友App

评论