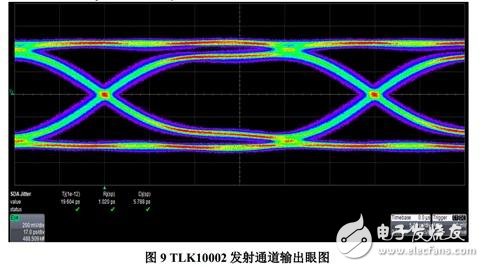

本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟,并且探讨

2013-09-26 14:34:31 3258

3258

对于fifo来说,H的设置至关重要。既要保证功能性,不溢出丢数,也要保证性能流水。深度设置过小会影响功能,过大又浪费资源。因此,总结下fifo设计中深度H的计算。

2022-08-29 11:19:03 1073

1073 SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04:02 495

495

在很久之前便陆续谈过亚稳态,FIFO,复位的设计。本次亦安做一个简单的总结,从宏观上给大家展示跨时钟域的解决方案。

2024-01-08 09:42:26 323

323

。FIFO计数器是只读的。我想知道它怎么能从SUNC出来。有没有办法知道马培德在PIC结构中的位置?AD中断在我的代码中是高优先级的,唯一的其他中断是低优先级的UART。到目前为止,这个解决方案似乎可以解决我

2019-09-03 10:06:01

7174-10002

2023-03-28 14:49:47

本文以TLK3132为例,详细介绍了SERDES工作原理和器件特点,并以WI系统中的CPRI应用需求为例,提供TLK3132的设计方法等。

2021-05-25 06:40:19

的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。 本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8

2019-05-29 17:52:03

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

TLK10002 10-Gbps, Dual-Channel, Multi-Rate Transceiver datasheet (Rev. B)

2022-11-04 17:22:44

EVAL MODULE FOR TLK10002

2023-03-30 11:43:46

我们将两片 TLK 3101之间用光收发模块通过光纤互联,TLK 3101和光收发模块之间的接口匹配不存在问题,光功率都在正常的范围之内 ,但在实验室测试中经常出现TLK 3101帧同步丢失

2019-02-28 07:04:13

TLK2501 - Interface, Serializer, Deserializer (SerDes) Evaluation Board

2023-03-29 22:54:00

是同轴铜缆、控制阻抗背板或光纤链路。然后将其重构为其原始并行格式。与并行解决方案相比,它可以节省大量的功耗和成本,并且可以面向未来提供可扩展性,以提高数据速率。TLK2711-SP 可执行并行至串行

2021-03-24 16:27:52

TLK3132工作原理是什么?TLK3132在CPRI接口中有哪些应用?

2021-05-25 06:53:11

TLK7-EVM是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅80mm*58mm,底板采用沉金无铅工艺的6层板

2021-12-28 08:15:14

CSS单行、多行文本溢出显示省略号(……)解决方案

2020-05-20 17:06:47

F28035 的FIFO怎样判断是否溢出?怎样清除?急

2020-05-08 06:11:11

我正在尝试在流模式下使用 INT2 引脚进行 FIFO 溢出,因为我很笨,只将 INT2 连接到我的 MCU。INT1 是 NC。试图避免使用新板。数据表似乎自相矛盾,但我想我遗漏了什么。我已经尝试

2022-12-15 06:19:05

很多人卡在这里吧if (tmp[0] & BIT_FIFO_OVERFLOW) {mpu_reset_fifo();return -2;问题的本质就是,读取数据速度不够快导致FIFO溢出

2019-04-15 01:05:57

抄了原子哥的驱动代码,放在了c8t6最小系统板上去跑,一切正常,自检原本通过不了,一顿操作后可以通过了,加速度角速度读取也OK,唯独读取FIFO中的数据读不出来具体为mpu_dmp_get_data

2022-02-10 06:12:34

可能是出现FIFO溢出问题解析,不断进行循环读fiffo就可以得到正常数据。形如这样:注意:printf(“pitch:%froll:%fyaw:%f\r\n”,pitch,roll,yaw);语句不要放在while里面!

2022-02-10 08:03:14

随着SerDes芯片集成度,复杂度,传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。为解决该测试难题,通过Nautilus UDI方案的导入,成功得实现了32 Gbps

2021-05-10 06:58:55

我想使用STM32F407的CAN通讯来接收六维力传感器的力信息,但是这个信息长度有31个字节,当STM32发送请求力信息的命令时,传感器采集卡一次性就发出4帧的数据帧,使接收FIFO溢出。想利用

2024-03-12 07:55:27

mpu6050移植的网上调试成功的程序,但有问题,单步调试好像FIFO溢出,论坛上有说I2C速率不够的,用的模拟I2C,这个怎么办啊?

2016-04-18 14:47:11

描述这款经过验证的参考设计是一个完整的四通道 SDI 聚合与解聚解决方案。使用一个 TLK10022 将四个同步 HD-SDI 源聚合到一条 5.94 Gbps 串行链路中。串行数据经由铜缆或光缆

2022-09-20 06:46:43

什么是SerDes?

2021-06-24 07:52:02

包含用于访问高速信号(高达 10Gbps)的 SFP+ 光学模块仓的双通道 XAUI 至 SFI 参考设计支持灵活的计时方案,包括从高速侧恢复的外部抖动消除时钟采用 TLK10232 器件,该器件是唯一

2018-08-02 08:26:56

基于Blackfin的解决方案 针对ADSP-BF706 BLACKFIN+处理器的EVWSS软件架构基于SigmaDSP的解决方案

2021-01-21 06:25:57

遵循信号走线限制,这些接口的抖动余地仍然是非常小的。固定频率振荡器可用于很多通用的SERDES标准;但是,这些解决方案价格昂贵。此外,这种做法缺乏灵活性,并且使调试、测试和生产变得困难。另一种解决方案

2019-05-21 05:00:13

业内首个signoff驱动的PrimeECO解决方案发布

2020-11-23 14:28:15

使用NVRAM的简单解决方案

2021-01-13 06:56:35

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

2019-10-12 09:05:54

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

2048正好是我设定的FIFO深度,所以问题应该是FIFO溢出了,我是这样理解的:PALIN_mReadFromFIFO()这个函数虽然读出了fifo中的数据,但是并没有释放fifo的空间,导致只能正确

2014-05-28 19:57:05

SerDes的基本结构是由哪些部分组成的?怎样去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有传输时钟信号吗?

2021-10-18 08:53:42

为 EMI 敏感和高速 SERDES 系统供电

2019-05-21 14:34:36

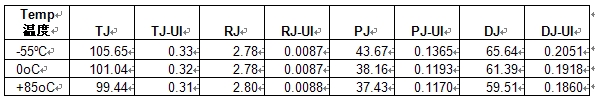

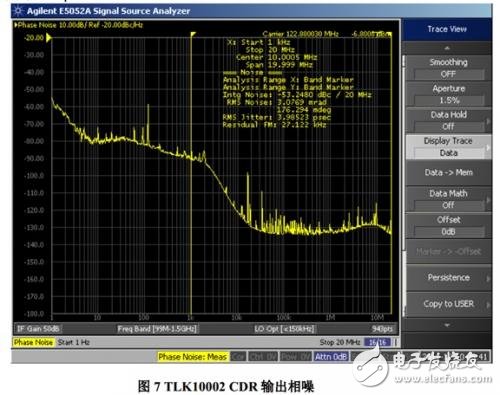

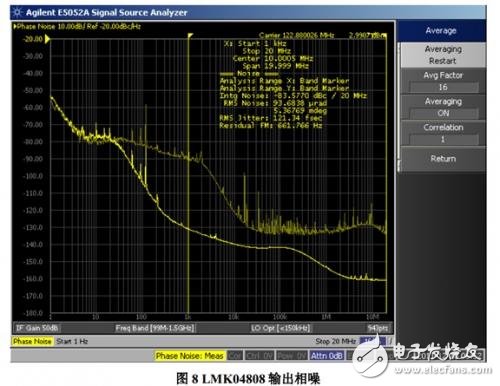

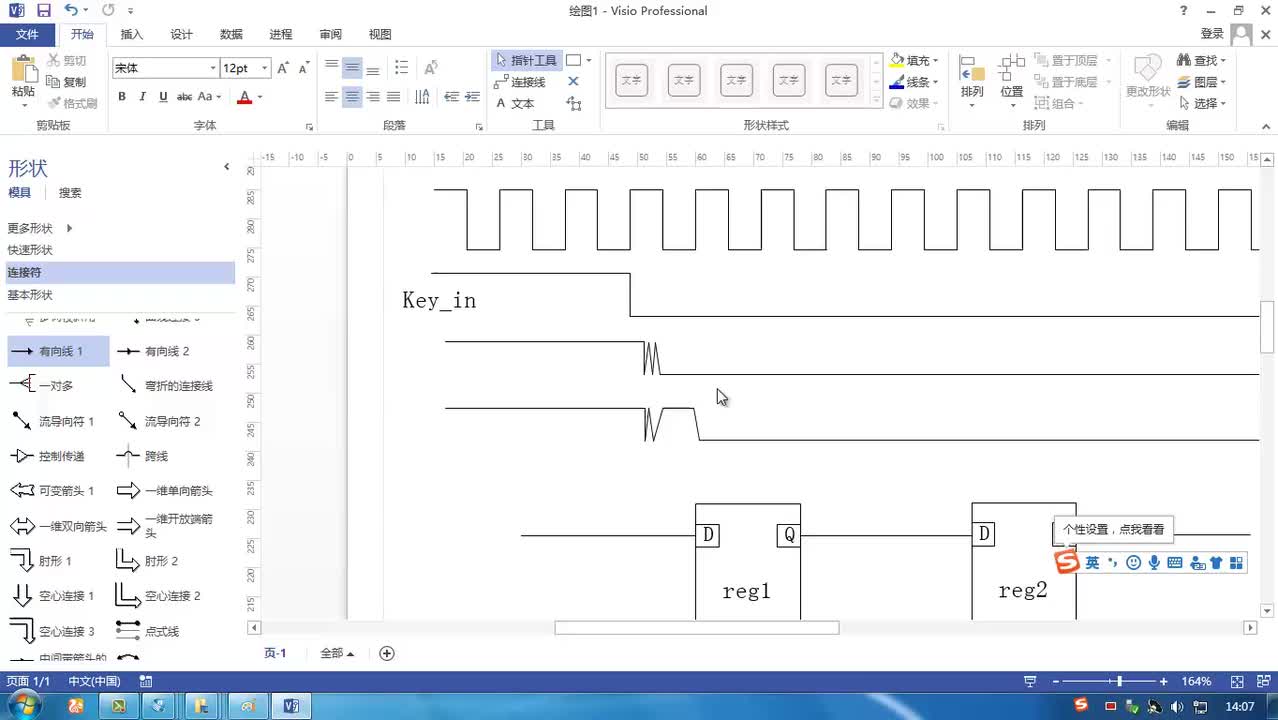

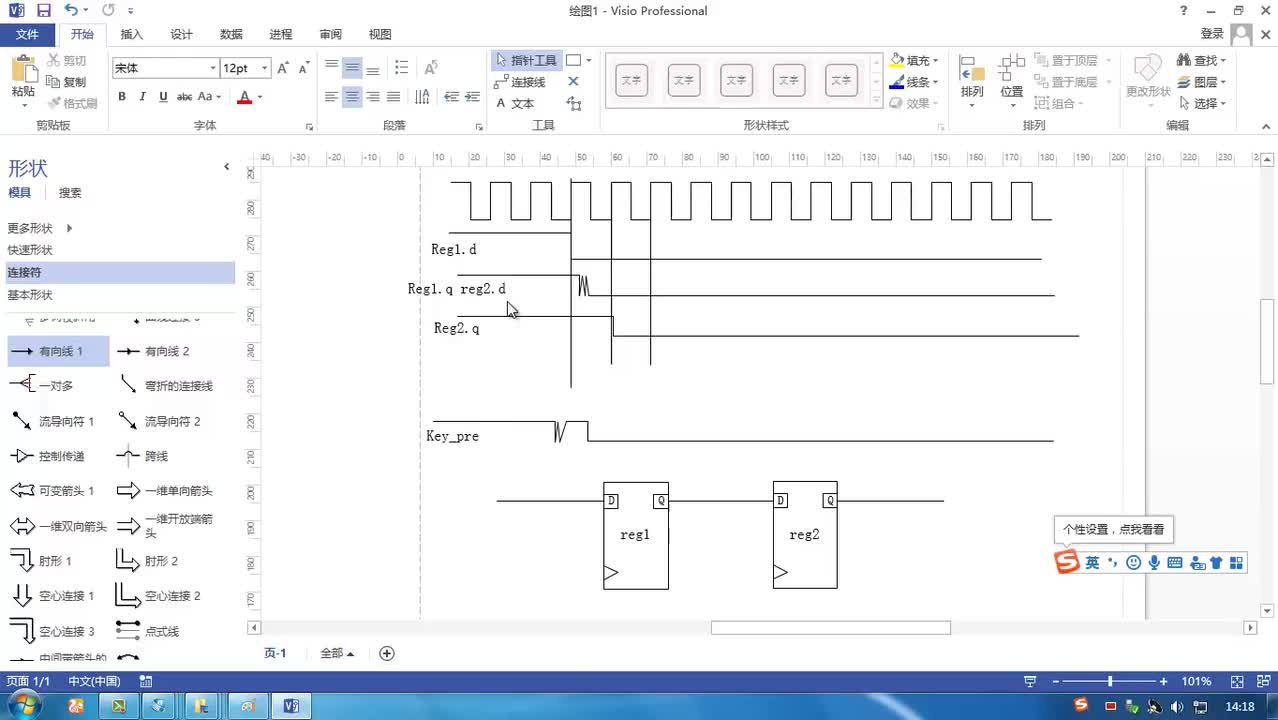

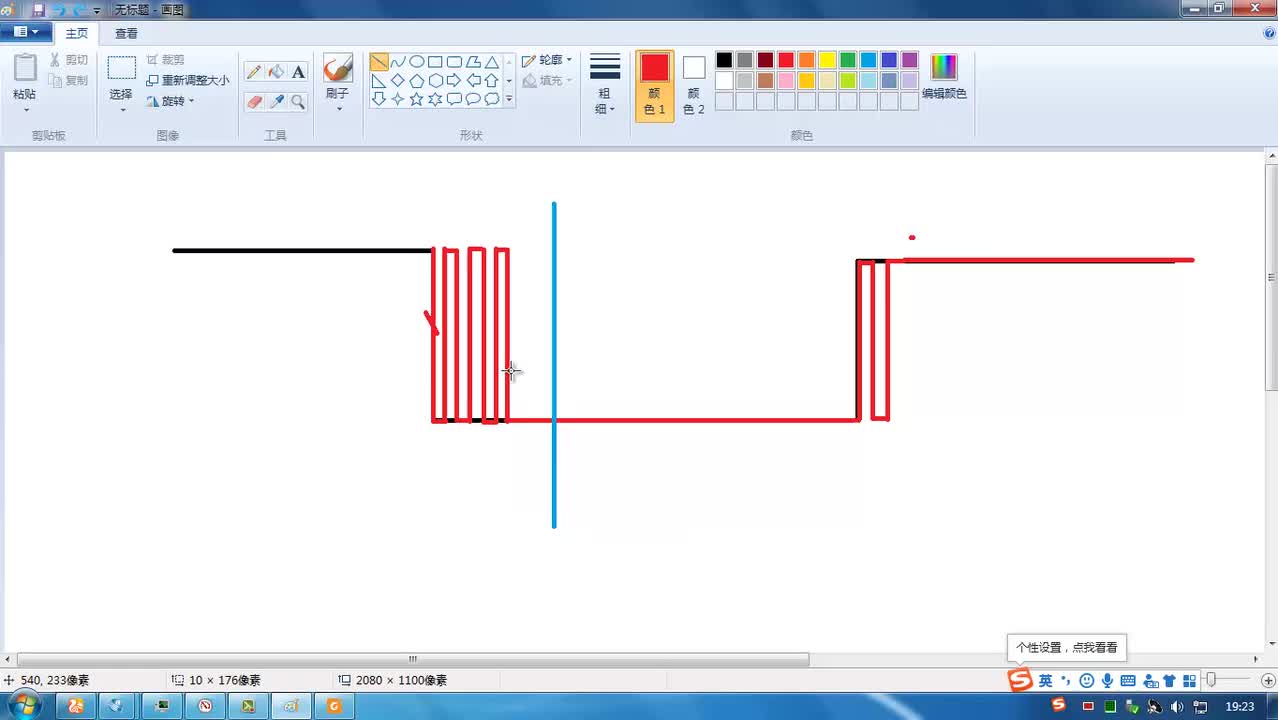

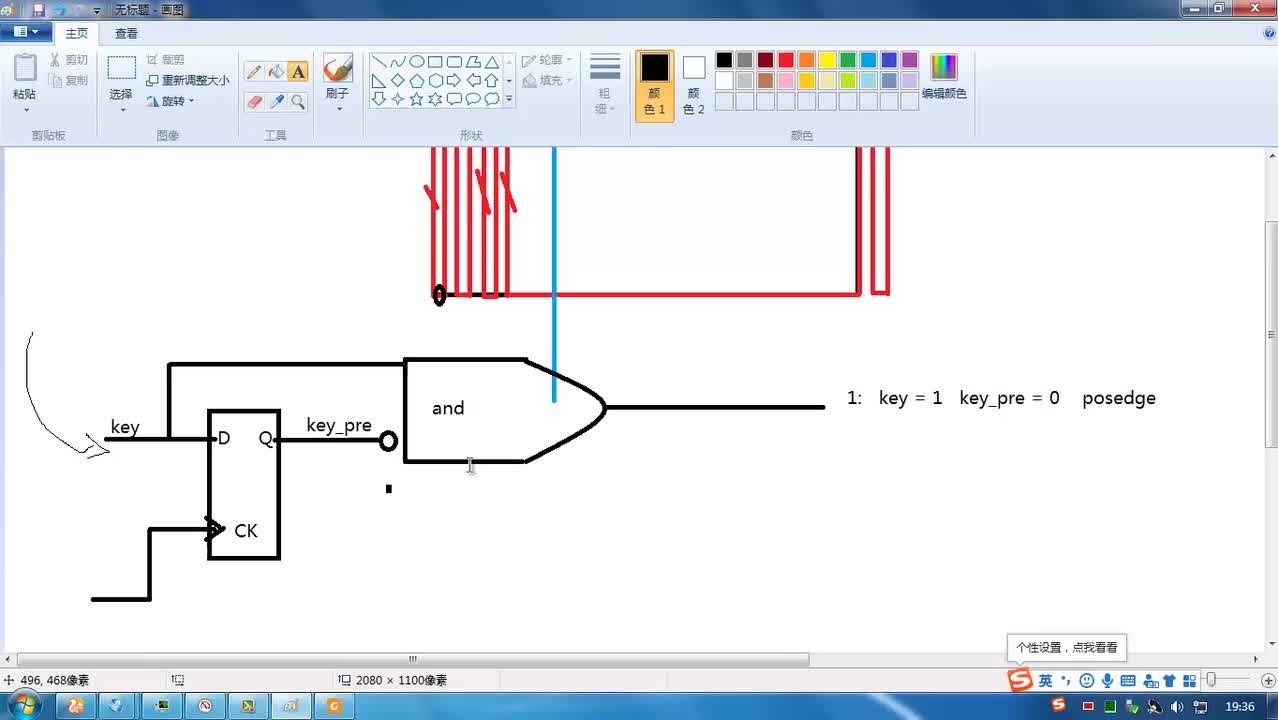

漂移及漂移形成的原因是什么?光纤漂移引起的SERDES FIFO溢出问题分析BBU SERDES 双系时钟方案及具体实现

2021-04-19 08:35:11

6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

2018-08-02 06:11:31

您好!我想请问一下,TLK2711的数字地可不可以接普通的数字地,如果不可以,会有什么问题出现?谢谢!

2019-05-20 14:09:42

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中

2020-10-28 17:15:14

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中

2020-11-01 20:21:02

串行化为更高速度的数据流。随后您既可通过高性能线缆传输该数据流,也可通过光模块由光纤传输。在另一端,您可通过解串串行化数据重新构建最初较慢速度的串行链路。要简化这一过程,您可使用TLK10002双通道

2018-09-13 10:02:04

The TLK2711A is a member of the WizardLink transceiver family of multigigabit transceivers

2010-09-09 20:31:46 43

43 The TLK1201A/TLK1201AI gigabit ethernet transceiver provides for ultrahigh-speed, full-duplex

2010-09-09 20:42:18 12

12 The TLK2201A and TLK2201AI gigabit ethernet transceivers provide for ultrahigh-speed full-duplex

2010-09-09 20:47:36 23

23 The TLK2201B and TLK2201BI gigabit ethernet transceivers provide for ultrahigh-speed full-duplex

2010-09-09 20:52:22 20

20 什么是fifo (First Input First Output,先入先出队列)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 高速串行接口设计的高效时钟解决方案

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架

2010-04-09 13:24:59 968

968

溢出,溢出的检测方法有哪些? 在定点小数机器中,数的表示范围为|x|<1. 在运算过程中如出现大于1的现象,称为“溢出”。在定点机中,正常情况下溢出

2010-04-13 11:02:03 11007

11007 德州仪器 (TI) 宣布推出业界首款 6 千兆位每秒 (Gbps) 的双通道串行器-解串器 IC (SerDes),其可为无线应用提供 高达470 兆位每秒 (Mbps) 至6.25 Gbps 的连续数据速率。该TLK6002支持从原有

2010-06-03 08:34:52 1434

1434 SERDES在数字系统中高效时钟设计方案,无论是在一个FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。

2012-02-16 11:23:43 5383

5383

本文以TLK3132为例,详细介绍了SERDES工作原理和器件特点,并以WI系统中的CPRI应用需求为例,提供TLK3132的设计方法等。

2012-05-07 16:01:58 6293

6293

以TI公司的TLK10002为例,研究了多速率环境下的PRU设备自适应接入问题,给出了RRU设备速率自适应的流程图和方法。采用本方案的RRU设备,能够自动进行通信速率调整,极大地降低了网络

2012-11-09 17:29:01 37

37 针对实时型相机对系统小型化、通用化及数据高速率可靠传输的需求,文中在研究高速串行器/解串器(SerDes)器件TLK2711工作原理的基础上,提出了高速串行全双工通信协议总体设计方

2013-06-25 15:59:43 100

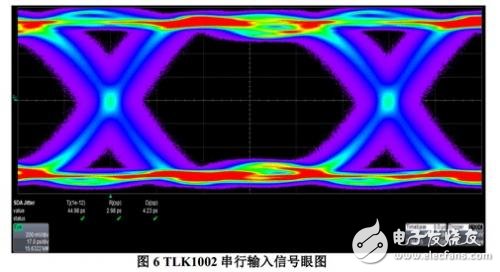

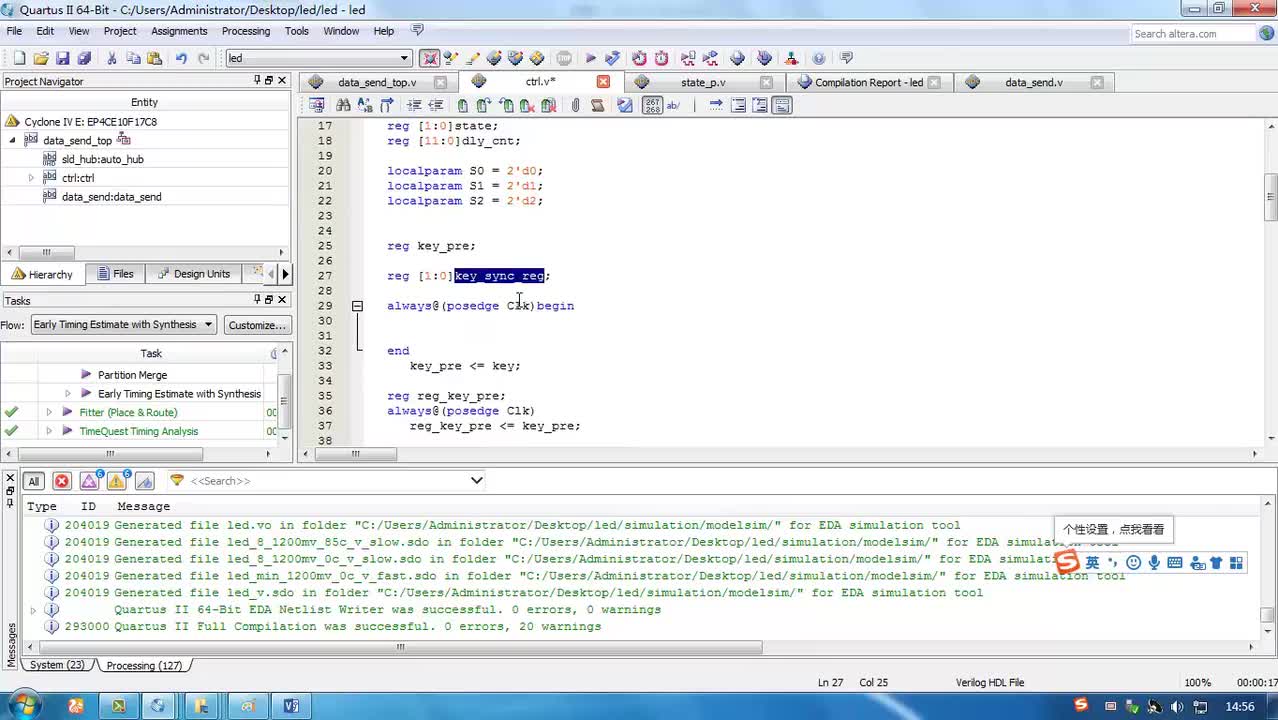

100 深度不够的情况下有可能会造成 FIFO 的溢出。本文首先会对这个问题进行一般性地分析, 在此基础上我们将以德州仪器公司 10GSERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES

系统时钟,并且探讨了这种模式的具体实现方式。 同时,为了验

2016-12-21 16:19:33 0

0 TLK2521数据手册

2017-01-03 11:41:35 0

0 MPU-6000(6050)为全球首例整合性6轴运动处理组件,相较于多组件方案,免除了组合陀螺仪与加速器时间轴之差的问题,减少了大量的封装空间。为什么FIFO数据会溢出?MPU6050的DMP在工作的时候。

2017-11-29 14:38:54 16613

16613 TI 提供的 TLK6002, TLK10002 等多种速率的通用 Serdes 芯片,在不同的领域得到了广泛的应用。特别在光纤拉远的应用中,由于 TLK6002, TLK10002 独特的配置灵活性和优良的适配宽容度,已成为业界的主流配置。

2018-05-08 16:04:33 7

7 随着SerDes芯片集成度、复杂度、传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。但通过Nautilus UDI方案的导入,成功实现了32 Gbps SerDes

2018-06-10 10:51:17 4433

4433

电子发烧友网为你提供TI(ti)TLK1211相关产品参数、数据手册,更有TLK1211的引脚图、接线图、封装手册、中文资料、英文资料,TLK1211真值表,TLK1211管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)TLK10002相关产品参数、数据手册,更有TLK10002的引脚图、接线图、封装手册、中文资料、英文资料,TLK10002真值表,TLK10002管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)TLK1221相关产品参数、数据手册,更有TLK1221的引脚图、接线图、封装手册、中文资料、英文资料,TLK1221真值表,TLK1221管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)TLK100相关产品参数、数据手册,更有TLK100的引脚图、接线图、封装手册、中文资料、英文资料,TLK100真值表,TLK100管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:10:12

电子发烧友网为你提供TI(ti)TLK106L相关产品参数、数据手册,更有TLK106L的引脚图、接线图、封装手册、中文资料、英文资料,TLK106L真值表,TLK106L管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:10:12

电子发烧友网为你提供TI(ti)TLK105L相关产品参数、数据手册,更有TLK105L的引脚图、接线图、封装手册、中文资料、英文资料,TLK105L真值表,TLK105L管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:10:12

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 4072

4072

SERDES的优势 引脚数量和通道优势 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。 对于现代的SERDES来说

2021-07-23 11:59:46 3794

3794 电子发烧友网为你提供ST(ST)STTH10002TV1相关产品参数、数据手册,更有STTH10002TV1的引脚图、接线图、封装手册、中文资料、英文资料,STTH10002TV1真值表,STTH10002TV1管脚等资料,希望可以帮助到广大的电子工程师们。

2023-02-17 18:33:43

电子发烧友网为你提供ST(ST)STTH10002TV2相关产品参数、数据手册,更有STTH10002TV2的引脚图、接线图、封装手册、中文资料、英文资料,STTH10002TV2真值表,STTH10002TV2管脚等资料,希望可以帮助到广大的电子工程师们。

2023-02-17 19:15:19

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4706

4706

FIFO,可以直接在自己的设计中配置和使用它,该设计是完全可综合的。 为什么要自己设计FIFO 那么,为什么呢?网上有很多关于 FIFO 的 Verilog/VHDL 代码的资源,过去,我自己也使用过其中的一些。但令人沮丧的是,它们中的大多数都存在问题,尤其是在上溢出和下溢出

2023-06-14 09:02:19 461

461 TLK10002SMAEVMTLK10002SMAEVM制造商TLK10002SMAEVM供应商TLK10002SMAEVM怎么订货TLK10002SMAEVM价格黄云艳13632767652优势

2021-12-22 14:33:14 327

327

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

2023-09-25 10:55:33 497

497

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-10-16 14:50:37 558

558

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用? 1. 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO在处理时序有明显的区别。同步FIFO相对来说是较为

2023-10-18 15:23:58 789

789 请问异步FIFO的溢出操作时怎么样判断的? 异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出

2023-10-18 15:28:41 299

299 尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44:59 449

449

计算原理,介绍其风险及可能带来的后果,并提供一些应对策略和措施,旨在帮助程序员理解溢出问题并提供有效的解决方案。 一、溢出计算原理 1.1 数据类型与范围 C语言中的整型数据类型包括char、short、int、long等,它们在内存中占有

2023-11-30 11:45:30 664

664 内存溢出与内存泄漏:定义、区别与解决方案 内存溢出和内存泄漏是计算机科学中常见的问题,在开发和调试过程中经常会遇到。本文将详细介绍内存溢出和内存泄漏的定义、区别以及解决方案。 一、内存溢出的定义

2023-12-19 14:10:12 884

884

电子发烧友App

电子发烧友App

评论