抖动时钟分发。Silicon Labs的新型Si532xx PCIe时钟缓冲器具有40fs RMS(典型值)的附加抖动性能,可为严格的PCIe Gen 3和Gen 4抖动规范提供超过90%的余量,从而简化时钟分发和降低产品开发风险。

2018-03-15 11:14:48 1827

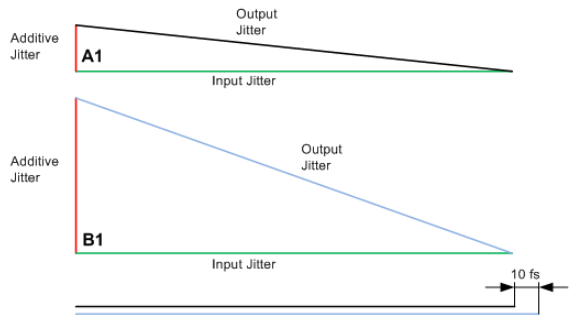

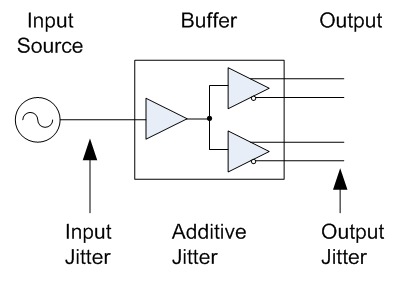

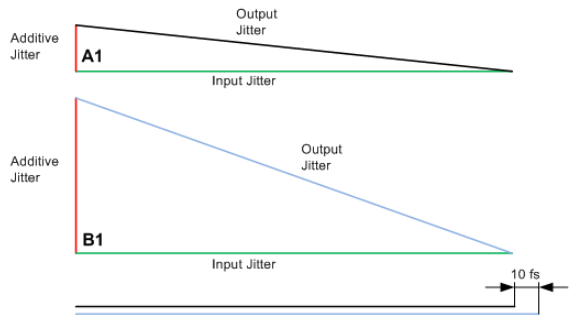

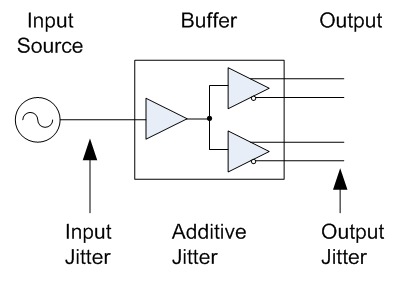

1827 低抖动时钟源。 随着系统要求的不断提升,问题也随之而来:时钟线路上添加的简单缓冲器会不会让时钟抖动变得更差?如果会,在添加简单缓冲器之前应该考虑什么问题? 图 1:系统级说明 附加抖动定义 这就是存在附加抖动的地方。

2018-07-16 09:38:48 4229

4229

由于车用电子产品愈见精密,使得系统时钟树的结构也愈来愈复杂。频率讯号的数量提升已为现今所需的时钟缓冲器提供低抖动和低偏差功能,同时降低系统功耗。

2020-04-21 11:06:14 617

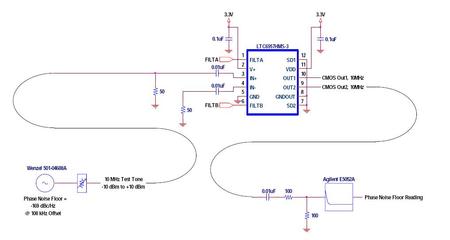

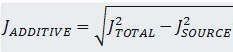

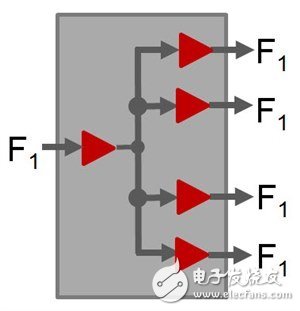

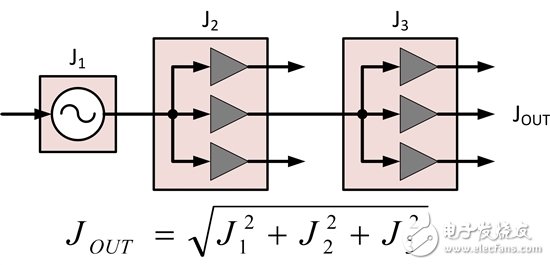

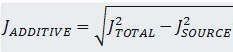

617 扇出缓冲器就是一个很好的例子。时钟缓冲器产生的附加抖动主要影响时钟的宽频带噪声。它可使用图 2 中所示的方根公式进行计算。图 2. 时钟扇出缓冲器的级联为驱动器件带来的附加抖动附加抖动的计算

2018-09-13 10:11:44

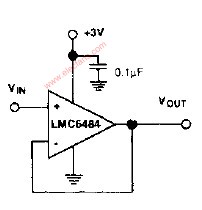

有合理的理由。例如,为什么在运算放大器配置成的缓冲器的反馈路径中有一个电阻器?图 1:在反馈路径中包含电阻器的运算放大器缓冲器电路现实情况是工程师经常不知道自己为什么使用电阻器 R2。他们可能在以前的原理图中看到过,觉得必须包含它。这些电阻器通常用于低速应用 (

2022-11-22 08:01:36

ADCLK846 / PCBZ,ADCLK846评估板是一款高性能时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能差分地保持接近100欧姆

2019-02-21 09:54:43

AKD8181D,AK8181时钟扇出缓冲器评估板。因此,很容易评估DC / AC特性并确认产品功能

2020-08-25 15:26:54

CDCLVC1102 低抖动 1:2 LVCMOS 扇出时钟缓冲器

2023-03-28 18:26:07

•医学成像 •测试和测量设备 说明 CDCLVP1204是一个多用途、低附加抖动缓冲器,它可以从两个可选的LVPECL、LVDS或LVCMOS输入中的一个产生四个LVPECL时钟输出副本,用于

2020-07-09 10:05:06

寄存器来实现的。以上的程序中 USART_RX_BUF[t]在USART.C中定义的是一个接收缓冲器,在这里怎么变成了发送缓冲器?再定义一个发送缓冲器USART_TX_BUF[t]不是更好?

2019-07-16 03:32:02

`请问什么是音频缓冲器?`

2019-08-23 16:27:28

缓冲器单芯片实施相比,分立式缓冲器复合环路实施存在的设计难题。分立式缓冲器复合环路架构图1中Hi-Z AFE的分立式实施使用在复合环路中配置的精密放大器和基于分立式结型场效应晶体管(JFET)的源极跟随

2022-11-03 07:56:17

:使用 LMK00338 等 RefClk 缓冲器的服务器卡实例在使用缓冲器分配 RefClk 时,需要考虑缓冲器引起的附加抖动。附加抖动的定义是器件本身对输入信号产生的额外抖动量,计算方法是: 。假设噪声过程是随机

2018-09-17 16:12:25

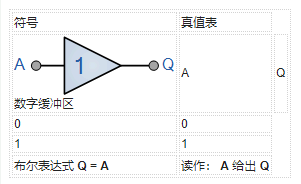

状态,以便每个附加的栅极连接都会增加栅极的负载。因此,扇出是可以由逻辑门的一个数字缓冲器同时驱动的并行负载的数量。用作电流源的缓冲区可以具有高达20个相同逻辑系列门的高扇出率。如果数字缓冲器具有较高

2021-01-26 09:16:58

高端时钟缓冲器用户不再需要面对抖动与电流的折衷

2021-04-06 06:24:31

如何去设计MP3播放器视频的输出部分?如何去解决超低功耗缓冲器应用的问题?

2021-04-20 06:02:33

如何去设计轨到轨CMOS模拟缓冲器?怎样对轨到轨CMOS模拟缓冲器进行仿真?

2021-04-23 06:35:57

。时钟缓冲器产生的附加抖动主要影响时钟的宽频带噪声。它可使用图 2 中所示的方根公式进行计算。图 2. 时钟扇出缓冲器的级联为驱动器件带来的附加抖动附加抖动的计算方法是:使用信号源 (…

2022-11-21 07:25:28

时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要达到所需的系统抖动性能,一定要保持尽可能低的时钟抖动,并在整个

2022-11-22 07:13:40

。优势是显而易见的。由于BJT具有较高的电压额定值,泄露尖峰会高出几百伏特,不过仍然处于所要求的开关降额设计范围内。根据尖峰的幅度不同,常常有可能在不使开关过压的情况下完全移除缓冲器。移除缓冲器优点

2022-11-17 07:51:39

》,掌握更多时钟技巧,如如何测量抖动以及如何使用分数 PLL 创建调制波形等;观看《如何测量扇出缓冲器中的附加抖动》视频;进一步了解我们面向无线及有线通信、工业以及汽车应用的时钟产品系列。

2018-09-13 14:18:06

测量扇出缓冲器中的附加抖动怎么计算?

2021-05-06 07:02:23

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

1,550 kg 的范围。该型号的特点是能量吸收量巨大,它是ACE将活塞管技术与滚动隔膜密封技术完美结合的典范。这样该类型的缓冲器,也可以作为终端减震装置直接安装在 5 至 7 bar 的气缸中,或

2018-04-21 17:11:16

你好,我通过我的硬件流一些二进制数据,我想使最新的1000位可用的CPU在任何时间点按需。我想通过DMA不断填充缓冲来实现这一点。因此,我想要一个循环缓冲器或一个能够保持至少1000位的FIFO缓冲器(UIT8BUF(128)),是否可以在硬件中实现?有什么建议吗?

2019-09-11 12:58:18

嗨,当我们在FIFO或GPIF FIFO中讨论FIFO时,FIFO是终结点缓冲器吗?也就是说,如果使用奴隶FIFO,当外部CPU将一个字节写入从属FIFO时,CPU直接将字节写入端点缓冲器中,或者

2019-07-08 11:13:26

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

大电流缓冲器

2019-10-31 09:11:09

ADCLK948 / PCBZ,ADCLK948评估板是一款性能非常高的时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能保持接近50欧姆

2019-02-21 09:54:06

了就是下雨了。今天咱们来看看零延时缓冲器吧。也是由缓冲一词想到的。它是指一种可以将一个时钟信号扇出成多个时钟信号,并使这些输出之间有零延时和很低的偏斜的器件。此器件很适合用于要求输入到输出和输出到输入

2014-05-20 17:32:38

ADCLK946 / PCBZ,ADCLK946评估板是一款性能非常高的时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能保持接近50欧姆

2019-02-21 09:55:44

`请问高速缓冲器是什么?`

2019-08-23 16:32:59

US5S110是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到两组10路低抖动LVCMOS时钟输出。

2022-06-21 15:45:45

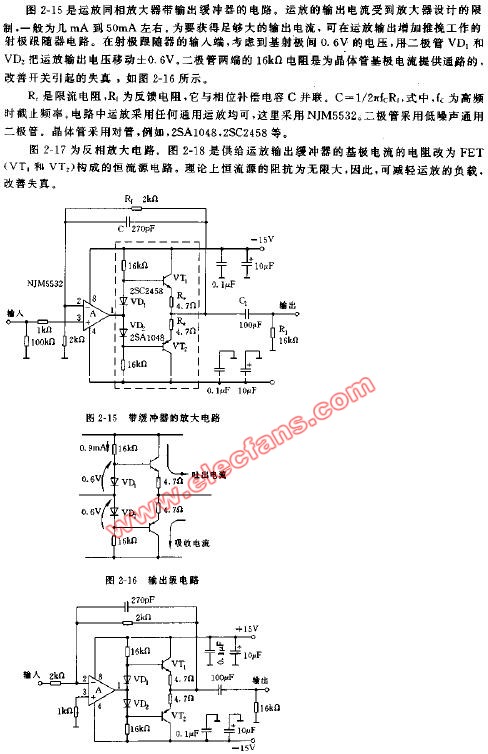

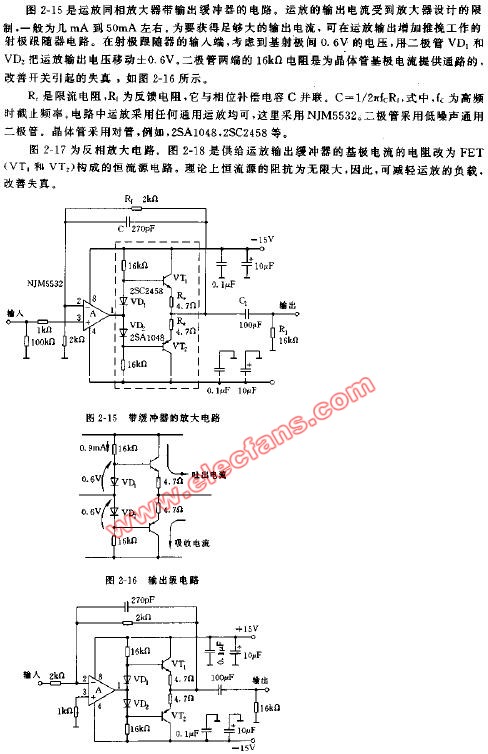

带缓冲器的放大电路

2008-12-17 01:42:14 957

957

摘要:DS34T10x和DS34S10x系列TDM-over-Packet (TDMoP)芯片采用抖动缓冲器来补偿包网络中存在的报文时延差异。本应用笔记将解释PDV的含义以及它如何影响通信质量,讨论抖动缓冲器的作用

2009-04-20 10:51:32 517

517

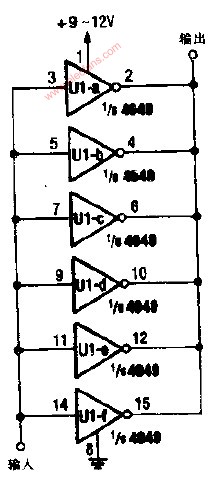

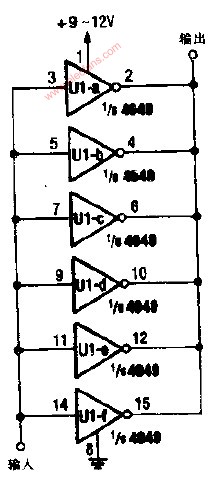

大电流缓冲器

通过4049非门

2009-09-11 10:47:50 3043

3043

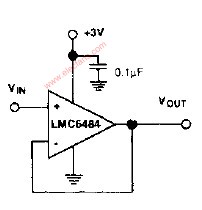

3V峰到峰单电源缓冲器

该

2009-09-11 10:58:27 694

694

TI推出正弦至正弦波时钟缓冲器

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款

2009-11-30 10:53:51 815

815 缓冲器,缓冲器是什么?

buffer 中文译名: 缓冲,缓冲器,缓冲液 解释:1、 电信设备。在数据传输中,用来弥补不同数据处

2010-03-08 13:30:11 2253

2253 锁存器和缓冲器的作用是什么?

锁存器广泛用于计算机与数字系统的输入缓冲电路,其作用是将输入信号暂时寄存,等待处理,这一方

2010-03-09 09:48:02 24819

24819 缓冲器,缓冲器基本原理是什么?

最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输

2011-09-03 19:10:46 9257

9257 嘉库公司日前发布了扇出缓冲器家庭中的一套新品,PL133-XX 和 PL135-XX。PL133和PL135作为扇出缓冲器中的新成员,具备嘉库产品高性能,低功耗,小尺寸(2.0x1.3x0.6mm DFN 封装)的特点

2011-04-12 09:19:58 1400

1400

日前,德州仪器 (TI) 宣布推出 2 款最新通用时钟缓冲器系列,进一步壮大其高性能时钟缓冲器产品阵营。CDCLVC1310 LVCMOS 时钟缓冲器可在晶振模式下实现 –169 dBc/Hz 的业界领先相位噪声

2012-04-05 08:47:28 1062

1062 IDT最新的差分扇出缓冲器系列运行于1.8V,拥有堪比3.3V版本的AC性能,适用于高性能通信、计算和网络应用。

2014-01-22 14:34:18 1926

1926 三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器

2015-11-16 11:59:30 0

0 LMK0033x是德州仪器(TI)推出的业界最低抖动的PCIe时钟扇形缓冲器。现在就让德仪的工程师向你介绍它的具体情况吧!

2018-06-13 11:52:00 4883

4883 EngineerIt-测量时钟扇出缓冲器的残余噪声

2018-08-13 00:23:00 3233

3233 起重机是一种重型机械,作业时产生的惯性也较大,容易产生意想不到的动作,所以,起重机缓冲器在这时候就起到作用了,起重机缓冲器是吸收起重机的运行动能,以减缓冲击的,起重机缓冲器作用及类型都十分广泛。

2018-12-04 15:45:15 10509

10509 液压缓冲器选型步骤1:下述参数是能量吸收计算中的基本数据。在一些情况下可能会需要一些变化或者其他数据 。

2018-12-05 16:21:59 18314

18314 液压缓冲器是一种安全缓冲装置,它能够对作用在它上面的物体进行减速缓冲直至停止,这样就会对作用的物体起到一定的保护作用。液压缓冲器性能优秀,在许多行业和产品里都有使用,比如运输、港口机械、电梯、冶金等行业。液压缓冲器有如下几个明显的优点。

2018-12-16 10:05:03 7626

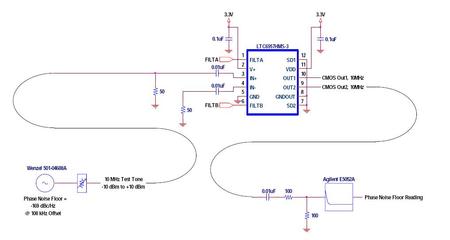

7626 您正在寻找低附加相位噪声(抖动)缓冲器,以将10MHz正弦波源作为参考时钟分配到您的系统中。在查看来自不同供应商的几个数据表之后,您意识到在这个相对较低的频率下给出的性能信息不多。市场上大多数高性能

2019-04-16 08:18:00 2816

2816

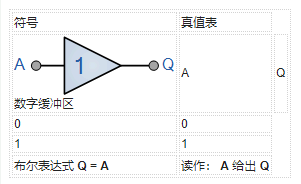

数字缓冲器和三态缓冲器可在数字电路中提供电流放大,以驱动输出负载,与单输入,单输出逆变器或 NOT TTL 7404的门,它在输出上反转或补充其输入信号,“缓冲器”不执行反转或决策制作功能(如具有

2019-06-26 12:02:27 14103

14103

ADCLK846:1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器

2021-03-20 11:31:10 9

9 AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整

2021-03-21 15:45:30 2

2 自适应抖动缓冲器-下载产生码

2021-04-12 16:47:30 3

3 ADCLK950:两个可选输入、10个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-19 16:40:05 7

7 ADCLK946:六路LVPECL输出,SiGe时钟扇出缓冲器数据表

2021-04-19 21:21:44 7

7 UG-942:HMC6832 3.5 GHz、低噪声、2:8差分扇出缓冲器评估板

2021-04-24 10:05:17 9

9 ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-25 16:26:36 7

7 ADCLK948:两个可选输入、8个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-25 16:29:54 7

7 UG-892:评估HMC7043高性能、3.2 GHz、14输出扇出缓冲器

2021-04-27 21:57:28 11

11 HMC7043:高性能、3.2 GHz、14输出扇出缓冲器数据表

2021-04-28 18:55:11 13

13 ADD8701:带VCOM缓冲器的12通道伽马缓冲器数据表

2021-05-08 12:28:26 3

3 ADH987S:3.3V低噪声1:9扇出缓冲器DC-4.5 GHz数据表

2021-05-22 19:21:46 1

1 HMC6832:低噪声、2:8差分扇出缓冲器数据表

2021-05-25 09:34:37 4

4 LTC6955:超低抖动、7.5 GHz、11输出扇出缓冲器系列数据表

2021-05-27 20:57:08 9

9 差分输出提供多达八路差分、低电压正射极耦合逻辑(LVPECL)输出。 图1. 连接至ADCLK948扇出缓冲器的ADF4351 PLL(原理示意图:未显示所有连接和去耦) 现代数字系统经常要求使用

2021-06-05 21:37:12 1

1 自适应抖动缓冲器-下载产生码

2021-06-16 11:08:38 4

4 缓冲器分为输入缓冲器和输出缓冲器两种;输入缓冲器的作用是将外设送来的数据暂时存放,以便处理器将它取走,输出缓冲器的作用是用来暂时存放处理器送往外设的数据。 缓冲器的工作原理: 当液压缓冲器受到

2021-08-25 17:31:25 22729

22729 缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU

2021-08-31 17:37:53 9948

9948 电源提示:以七步计算一个R-C缓冲器

2021-09-07 18:08:28 11

11

LMK00304 扇出缓冲器就是一个很好的例子。时钟缓冲器产生的附加抖动主要影响时钟的宽频带噪声。它可使用图 2 中所示的

2021-11-23 17:45:07 1769

1769

的 TI 时钟专家能解决您的所有时钟问题,满足您的任何需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速

2021-11-10 09:42:52 901

901

IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1500

1500

KOYUELEC光与电子提供技术支持有容微电子GM50301:超低附加抖动差分输出时钟缓冲器

2022-05-07 11:38:45 2271

2271 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1071

1071 的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。 对于需要多路时钟信号的电子系统来说,时钟源加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参

2022-10-18 18:36:54 18409

18409

测量扇出缓冲器中的附加抖动

2022-11-04 09:52:08 0

0 定时决定一切:如何测量附加抖动

2022-11-04 09:52:13 0

0 ADCLK944是一款超快型时钟扇出缓冲器,采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造。这款器件设计用于要求低抖动性能的高速应用。 该器件具有一路配中心抽头、差分、100

2023-01-04 17:07:41 805

805 1 到 4 扇出缓冲器-74AVC1T1004

2023-02-16 21:16:26 0

0 1 到 4 扇出缓冲器-74AVC9112

2023-02-21 19:33:20 0

0 GRANDMICRO有容微电子GM50101:超低附加抖动时钟缓冲器

2023-03-02 11:06:16 661

661

1 到 4 扇出缓冲器-74AVC1T1022

2023-03-03 19:53:47 0

0 DS34T10x和DS34S10x TDM分组(TDMoP)器件利用抖动缓冲器来补偿分组网络中存在的分组延迟变化(PDV)。本应用笔记解释了PDV及其对通信质量的影响。讨论了抖动缓冲器的功能和类型。本文还介绍了如何在TDMoP器件中设置抖动缓冲控制器的参数,以最大程度地减少PDV的影响。

2023-03-08 18:20:00 649

649

液压缓冲器强度是否能够调节,取决于液压缓冲器的种类,目前市面上较为常用的液压缓冲器包括可调液压缓冲器、不可调液压缓冲器,这两种缓冲器调节强度的实际效果是不一样的。

2023-04-24 16:12:01 2158

2158 高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29:55 805

805

电子发烧友网站提供《PI6C5913004最低输出抖动缓冲器IC 确保40GE/100GE设计性能.pdf》资料免费下载

2023-07-25 14:45:10 0

0 三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

2023-09-21 15:55:36 1607

1607 等应用已集成越来越多的PCIe终端,矽力杰新一代高性能PCIe时钟缓冲器SQ82100可以为系统提供20路超低附加抖动的LP-HCSL参考时钟,能够简化系统布局,进一步提高

2023-12-20 08:19:38 240

240

正在加载...

电子发烧友App

电子发烧友App

评论