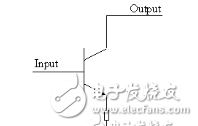

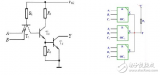

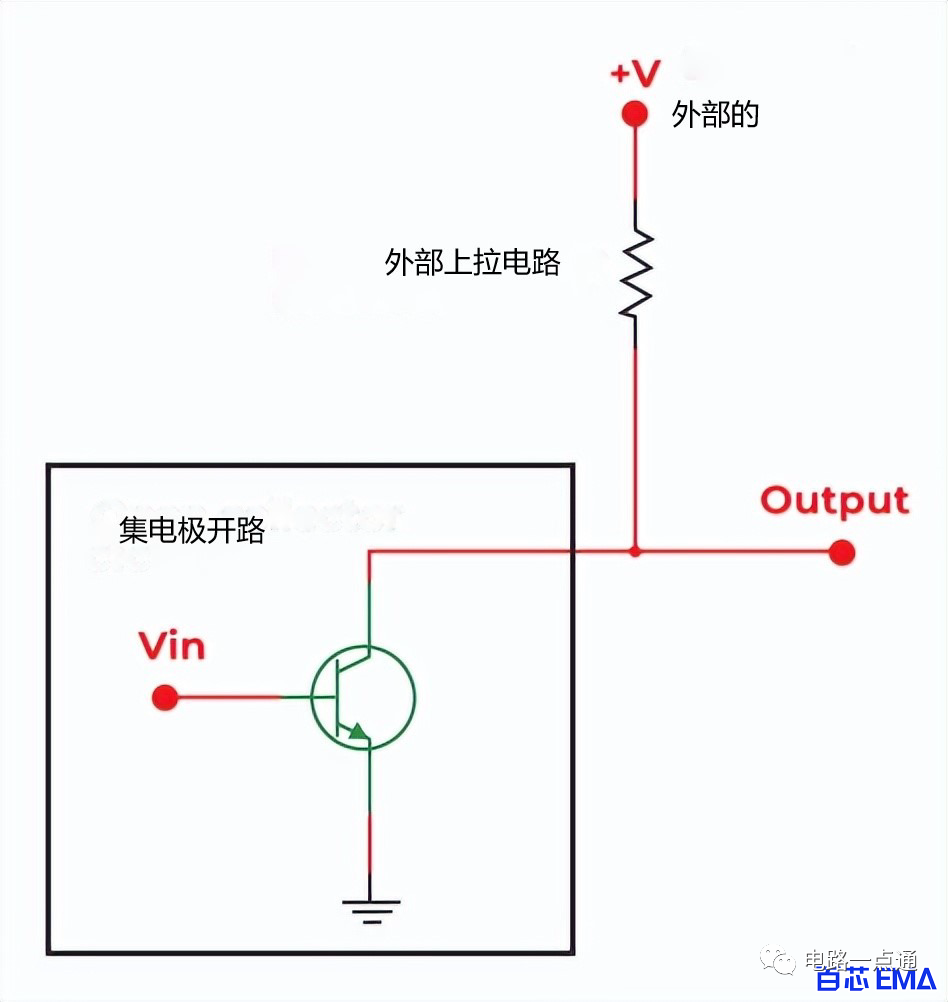

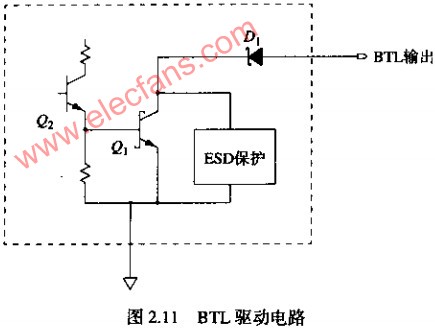

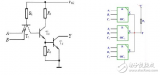

我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。对于图1,当左端

2022-11-21 10:37:35 5971

5971 集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-01 08:59:17 529

529 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-06 11:54:41 2842

2842

今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-07-17 09:03:55 2322

2322

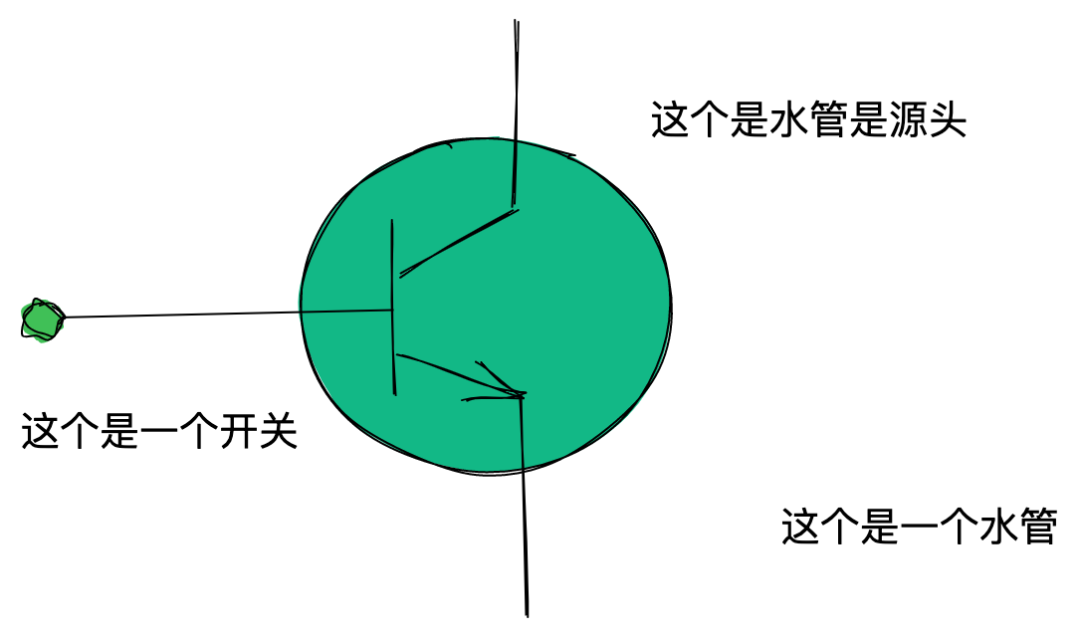

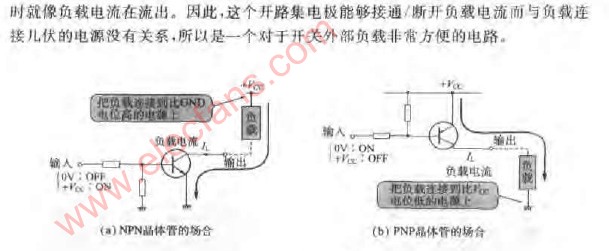

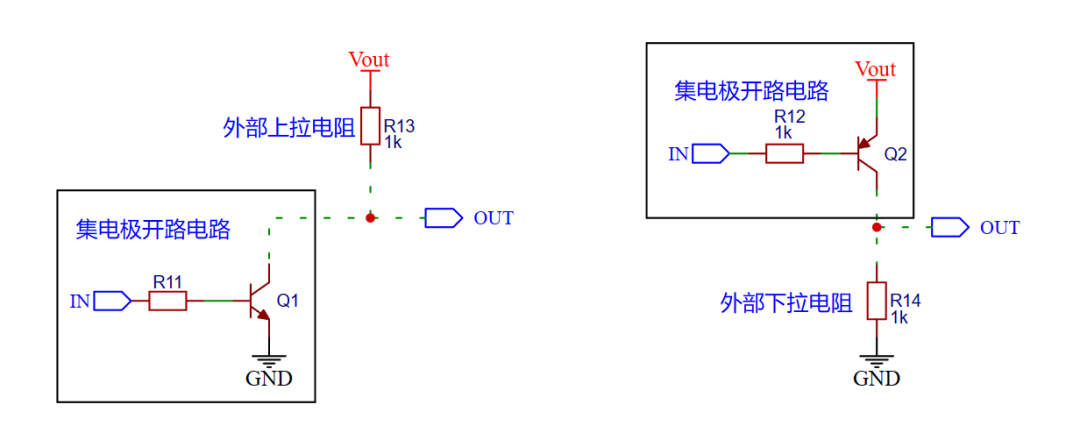

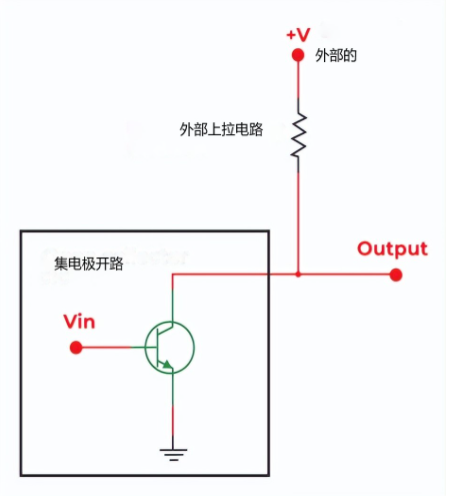

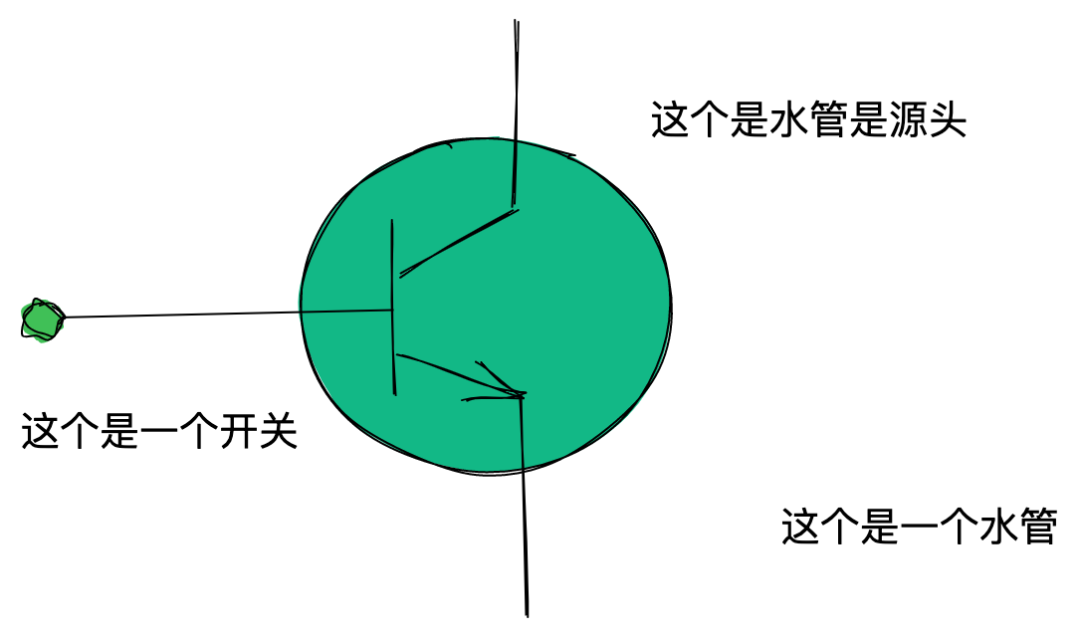

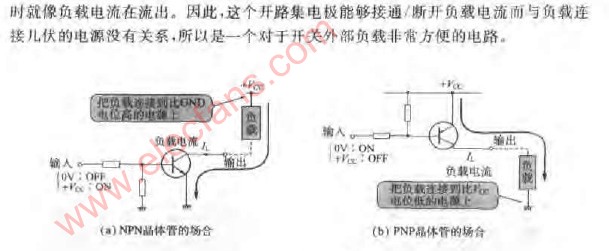

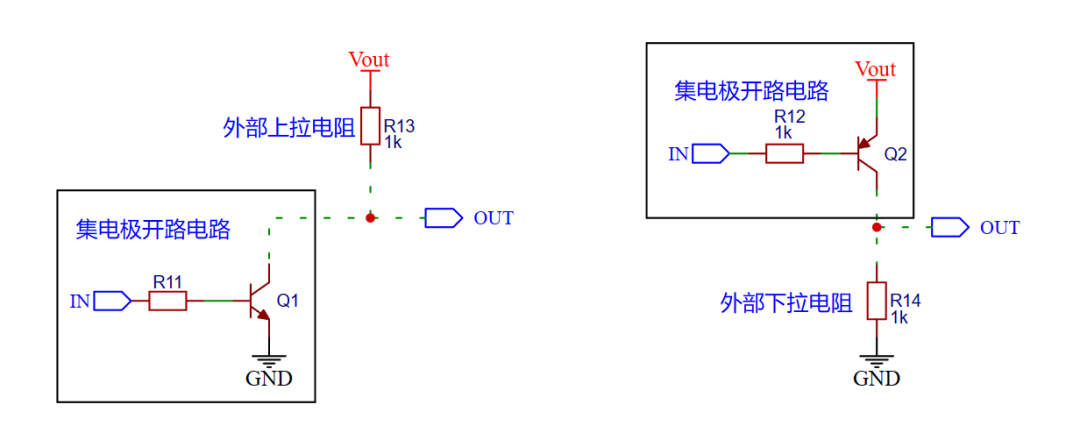

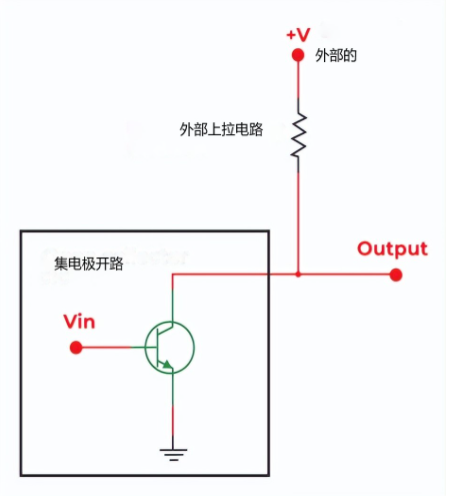

集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。

2023-07-21 10:00:28 793

793

漏极开路上拉电阻取值为何不能很大或很小?开关电源布线注意哪些?为何用万用表量电路板的电阻时需断电?

2021-11-12 07:59:46

集电极开路 漏极开路 推挽 上拉电阻 弱上拉 三态门 准双向口

2016-06-02 16:22:21

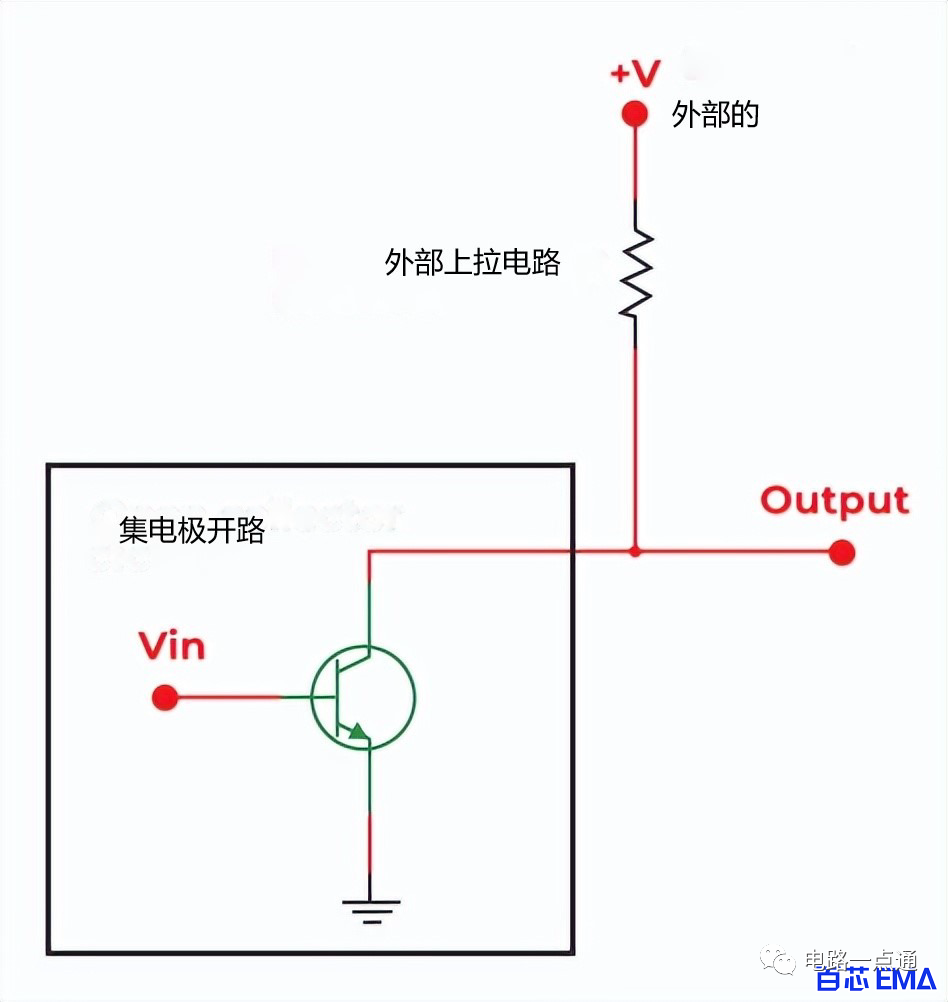

时给引脚或线路节点一个固定的默认的电平。上拉电阻有时还用来增加输出引脚的驱动能力。当所接电阻值比较大时称为弱上拉或弱下拉,否则就是强上拉或强下拉。上拉电阻应用比较普遍,大部分OC或OD输出都需要接上拉电阻。单片机的大部分I/O引脚也配备了弱上拉电阻。

2019-05-20 11:15:28

1、集电极开路输出上拉电阻电路为什么会速度降低和噪声变大?在此基础出引出了三态门?

2、多集电极开路上拉电阻输出实现了线或结构,有高为低,全低为高。那么什么电路结构可以实现线与结构,射极跟随,推挽,互补或者其他简单输出电路?

2024-01-28 16:32:00

的复位阈 值时,输出有效的复位信号;当电源电压上升到复位阈 值以上时,在至少140毫秒的时间内复位信号还将维持 有效。CS803提供漏极开路复位输出,CS809/810提供 CMOS复位输出。CS803

2021-07-27 11:31:25

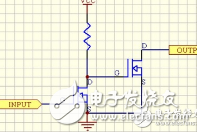

断开,而对于P0口来说,就是高阻态了。对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。另一种输出结构

2016-06-29 11:11:00

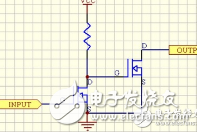

断开,而对于P0口来说,就是高阻态了。对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。另一种输出结构是推挽

2017-03-21 09:20:02

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2022-02-08 06:50:38

内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管

2017-10-12 10:41:10

开关断开,而对于P0口来说,就是高阻态了。 对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。 另一种

2018-03-20 16:19:06

设置成开路输出模式,并设置输出高,应该不会有电流流过电阻吧? 理论上漏极开路应该不会。相当于开路。我的理解对吗?

2023-06-26 07:17:51

我正在尝试在Verilog中实现一个开放收集器但是输出0会被卡住。模块......(inout wire sdcka,sdckb)...... always @(posedge aclk)begin

2020-03-26 08:07:16

端口需要配置为漏极开路输出或集电极开路输出,请问该怎么用啊没有相关的寄存器可以配置输出模式

2018-08-13 06:41:32

我使用 xmc7100 芯片,使用 pwm 功能时,我需要将引脚配置为开路和漏极输出。 当我没有连接上拉电阻器时,示波器会检测到应该没有波形,但是有波形表明开路和漏极输出配置不成功,为什么不呢? 能否将 pwm 引脚配置为开路和漏极输出?

2024-01-23 06:34:37

本帖最后由 gk320830 于 2015-3-4 23:25 编辑

【经典】集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

2012-07-29 21:17:03

什么是集电极开路(OC)?什么是漏极开路(OD)?

2021-03-10 06:35:21

PLC输入分为源型和漏型,什么是源型和漏型,是指传感器的晶体管类型吗?源型NPN和漏型PNP,还是指信号流入流出的方向,源极为流出,射极为流入?再或者是指信号输出的方式,集电极输出和射极输出?电子专业常说的有源指的是什么?什么有源负载,有源电路的。

2024-01-14 00:29:14

推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉

2021-11-24 07:22:11

单片机I/O开漏输出详解开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构

2021-11-24 08:11:44

1.什么是源型 漏型?什么是上拉电阻?下拉电阻?什么是 线驱动输出 集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接

2021-07-15 09:15:48

本帖最后由 zhihuizhou 于 2011-11-2 10:20 编辑

集电极开路、漏极开路、推挽、上拉电阻、弱上拉、三态门、准双向口集电极开路输出的结构如图1所示,右边的那个三极管集电极

2011-11-02 10:20:11

你好,我使用的是PIC16F18854和开放漏极输出模式,我的问题是开放漏极泄漏电流似乎没有在数据表中指定。指定了输入漏电流(D340,D341),但是没有提到开路漏极。端口部分中的电路显示通过

2020-03-11 06:35:45

如图电路是我从一个视频教程里找到的,是一个光控的蜂鸣器输出其中这个Q1的射极可以输出去控制Q2导通吗?我不明白为什么不使用Q1的集电极开路输出呢?这里搞一个射极输出控制有什么含义?

2019-07-29 02:02:50

的IIC引脚设置为漏极开路。我读了ug471:7系列fpga selectedIO资源, ug768:7系列硬盘 ug865:zynq-7000-pkg-pinout但我没有找到将iic引脚设置为漏极开路的方法。你可以帮帮我吗?谢谢。

2020-05-14 06:37:27

我正在连接一个5V PIC18到2.5V设备。PIC18上的一些输出可以是开路漏极。我非常熟悉漏极/开路集电极输出,并使用了很多年。然而,说明书上的措辞有点麻烦。从PIC18F66K80系列说明书第

2020-05-12 10:28:10

我正在尝试清理我们的代码,现在正在查看我们的代码,该代码将两个 RMT 通道(一个输入,一个输出)配置为在同一引脚上工作,输出为漏极开路。我想我明白其中的大部分内容,但我不明白为什么我们需要设置

2023-03-02 08:25:00

我正在使用 NUCLEO-L552ZE-Q 并制作了一个非常简单的测试电路来测试漏极开路输出信号。我将引脚配置为漏极开路输出,没有上拉或下拉,信号通过 1K 电阻上拉至 3.3V。当我设置引脚时,我

2022-12-27 06:13:19

你好。我用的是STM32G071GBU6,VDD电压我设计成1.8V。我有一些关于董事会的问题。1. 3.3V GPIO 输出控制- 我是否应该将 MCU 的 GPIO 引脚设置为漏极开路并连接它

2022-12-07 08:43:22

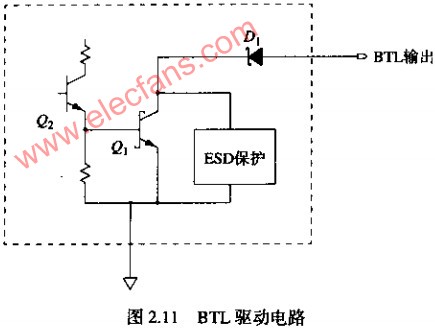

1.1.1 接口相关电路及概念1. 集电极开路输出在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指

2022-01-14 07:57:32

的,Vcc也要在数据手册规定的范围内。集电极或者漏极开路输出引脚是由一个晶体管控制的,当晶体管关闭时,输出引脚为悬空状态(开路或者高阻态)。一个常见的列子就是当N沟道晶体管导通时,输出信号接地,但关断时,输出

2019-04-23 08:00:00

集电极开路输出结构与推挽输出结构有什么不同?开漏电路有哪些特点?在使用开漏电路时有哪些注意事项?

2021-04-19 10:41:41

1.什么是源型漏型?什么是上拉电阻?下拉电阻?什么是线驱动输出集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做

2021-11-23 07:22:08

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-11-03 06:28:05

当三极管为开路输出时,三极管集电极通过一个负载,再从负载另一端接到电源,-----------------------------通常我们称为集电极开路输出。那么三极管为发射极这边来接负载时,这个

2019-08-01 00:03:31

请问各位:如何在QUARTUS II里将EPM1270的管脚配置为漏极开路?

2021-04-13 15:48:08

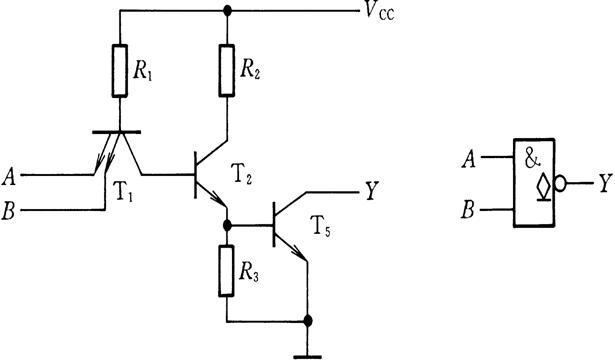

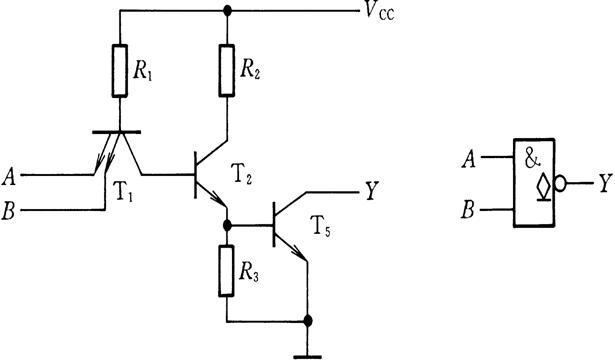

集电极开路门和三态输出门的应用

一、 实训目的1.熟悉集电极开路门(OC门)和三态输出门(TSL门)的逻辑功能;2.熟悉用OC门构成线与功能;3.熟悉用TSL门

2009-04-07 23:23:53 59

59 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,

2010-08-14 17:15:55 136

136 TTL或非门、集电极开路门和三态门电路

1.TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

2009-04-07 00:11:59 14317

14317

集电极开路门

在工程实践中将两个门的输出端并联以实现与逻辑的功能称为线与。 考察下图所示的情况。当将图中所示的两个逻辑门的输出连接在一起,并且

2009-04-07 00:15:19 20553

20553

集电极开路与非门的电路和图形符号

2009-07-15 19:02:06 7870

7870

开路集电极电路图

2009-08-15 17:27:30 864

864

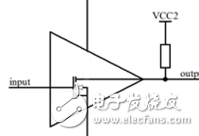

什么是漏极开路(OD)? 对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可

2010-03-04 15:37:00 51861

51861 漏极开路(OD)原理说解

漏极开路(OD),它与集电极开路(OC)是一致的,就是把下图的三极管改成CMOS管就是了。

2010-03-04 15:38:44 3052

3052 集电极开路(OC)/漏极开路(OD)输出的结构

A:我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个

2010-03-04 15:41:39 2810

2810 用来计算TTL集电极开路输出电路静态功耗的公式如下:

其中:VT=上拉电阻的有效

2010-06-01 16:17:42 2549

2549

集电极开路_漏极开路_推挽_上拉电阻_弱上拉_三态门_准双向口,感兴趣的小伙伴们可以瞧一瞧。

2016-11-16 18:32:35 0

0 介绍了什么是集电极开路,漏极开路,推挽上拉,电阻弱上拉,三态门。

2017-02-28 22:08:40 1

1 三极管导通时,集电极输出低电平;三极管关断时,集电极输出悬空,因此该电路在工作时需要外接负载电阻和电源。只要电阻的阻值和电源电压的数值选择得当,就能够做到既保证输出的高、低电平符合要求,输出端三极管的负载电流又不过大。

2017-11-09 12:17:53 145604

145604

漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。对于漏极开路(OD)来说,输出端相当于三极管的集电极。 要得到高电平状态需要上拉电阻才行。 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)。

2017-11-09 14:17:01 17820

17820

集电极开路输出的结构,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。漏极开路是驱动电路的输出三极管的集电极开路,可以通过外接的上拉电阻提高驱动能力。

2017-11-09 14:28:38 17067

17067

线与”逻辑是因为多个逻辑门的输出三极管(场效应管、二极管),共用一个上拉电阻,只要一个逻辑门输出低电平,即集电极(漏极)开路输出的管子导通,就把上拉电阻接地,输出低电平;只有全部输出管截止,输出端被上拉电阻置为高电平,这就是与逻辑的运算结果。

2017-11-09 17:13:35 23227

23227

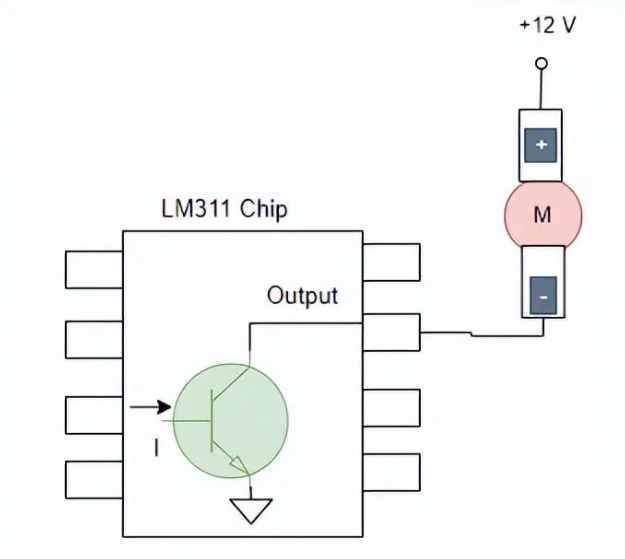

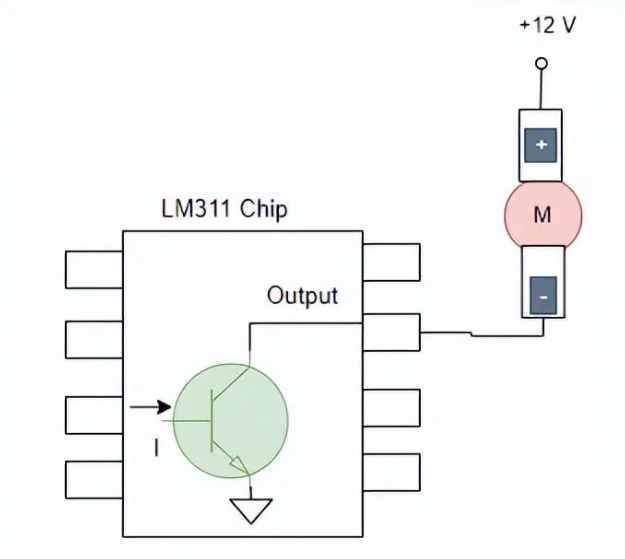

该装置包含六个独立的门,每个门执行缓冲功能。开路集电极输出需要外部上拉电阻才能正常逻辑操作。

2019-04-24 08:00:00 1

1 首先讲一下集电极开路输出(Open-Collector),单片机I/O常用的输出方式的开漏输出(Open-Drain),漏极开路电路概念中提到的“漏”是指 MOSFET的漏极。同理,集电极开路电路中的“集”就是指三极管的集电极。在数字电路中,分别简称OD门和OC门。

2019-08-26 17:30:00 12

12 集电极开路输出端或者MOS管漏极输出端其性质都是一样的,这种电路在数字电路中都要加上拉电阻。比如在单片机P0口其内部驱动电路是MOS构成的,其结构就是一个漏极开路电路,其内部没有上拉电阻。

2019-09-28 07:00:00 8622

8622 PmodOC1是使用MMBT3904晶体管的集电极开路BJT模块。

2019-11-29 14:38:33 1351

1351

A、开路集电极NPN的接线方式,采用内部电源(由于采用内部电源,所以“+24V”和“PLC”的短接片必须连接可靠,而且电流的流向为从“+24V”到“PLC”到控制板内部整理电路,再到“Xi”端子,经过外部接点后回到变频器的“COM”端子):

2020-11-11 08:00:00 1

1 电子发烧友网为你提供什么是集电极开路(OC)?什么是漏极开路(OD)?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-13 08:42:31 9

9 DM5438/DM7438缓冲器集电极开路输出资料手册免费下载。

2021-06-01 17:51:18 11

11 是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫

2021-10-28 17:51:00 9

9 1.什么是源型漏型?什么是上拉电阻?下拉电阻?什么是线驱动输出集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做

2021-11-15 13:51:02 0

0 上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路...

2021-11-15 20:21:06 34

34 单片机I/O开漏输出详解开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构

2021-11-15 20:36:07 7

7 是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫

2021-11-16 09:21:01 21

21 是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫

2021-12-05 10:36:05 13

13 1.1.1 接口相关电路及概念1. 集电极开路输出在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提

2022-01-14 14:32:40 23

23 如果开关断开,则由于开关电阻为无穷大(不考虑实际中的漏电流),所以流过的电流为0,因此在1k电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。

2022-08-31 14:18:39 1925

1925 因此集电极开路的输出视为NPN晶体管,它允许电流吸收到公共端。对于这样集电极开路电路,必须有一个电源才能使输出正常工作。当我们要求未连接任何电源时计算输出电压时,电压不会发生变化。必须计算输出端的电压以了解集电极开路电路的正常运行。

2023-01-08 15:03:01 2856

2856 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-01-13 09:48:30 908

908 集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2023-01-16 09:16:28 756

756 具有漏极开路输出的低功率逆变器-74AUP1G06

2023-02-14 19:05:03 0

0 具有漏极开路输出的 2 输入与门-74AHC1G09_Q100

2023-02-14 19:11:18 1

1 具有漏极开路输出的 2 输入与门-74AHC1G09

2023-02-14 19:11:35 0

0 带漏极开路输出的六角反相器-74LVC06A

2023-02-17 19:46:23 0

0 带漏极开路输出的六角反相器-74LVC06A_Q100

2023-02-17 19:46:40 0

0 带漏极开路输出的六角反相器-74HC05

2023-02-17 19:54:59 0

0 带漏极开路输出的六角反相器-74LV05A

2023-03-03 19:49:05 0

0 对于电浪涌发生器,开路输出电压的精度非常重要。因此,在校准电浪涌发生器开路输出电压时,必须使用高精度的探头。在这篇文章中,我们将介绍如何使用P6015A探头正确校准电浪涌发生器的开路输出电压。

2023-04-07 14:38:19 703

703

何为集电极开路电路?集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。由于NPN

2023-07-31 23:07:05 890

890

ttl电路中推拉输出,集电极开路输出,三态输出有何不同? TTL电路是一种常见的数字逻辑电路,在电路中经常出现推拉输出、集电极开路输出、三态输出这些术语。这些输出方式在不同的电路中具有不同的意义

2023-08-31 10:32:19 2131

2131 开路电压是什么意思? 开路电压指的是在电路中没有负载负荷的情况下,测量到的电源输出的电压大小。在没有负载的情况下,电源输出电压的测量结果往往会比有负载时高出一定比例。 为了更好地理解开路电压的概念

2023-12-12 14:09:47 3501

3501 集电极开路电路是一种常见的逻辑电路,它的特点是输出端有一个开路的集电极。

2024-02-17 15:11:00 292

292

集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2024-02-15 09:24:00 179

179

集电极开路门的内部结构设计会直接影响其开关速度。例如,电极间的距离、材料选择、通道长度等都会对开关速度产生影响。

2024-03-18 17:10:20 125

125

电子发烧友App

电子发烧友App

评论