集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-01 08:59:17 529

529 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-06 11:54:41 2842

2842

今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-07-17 09:03:55 2322

2322

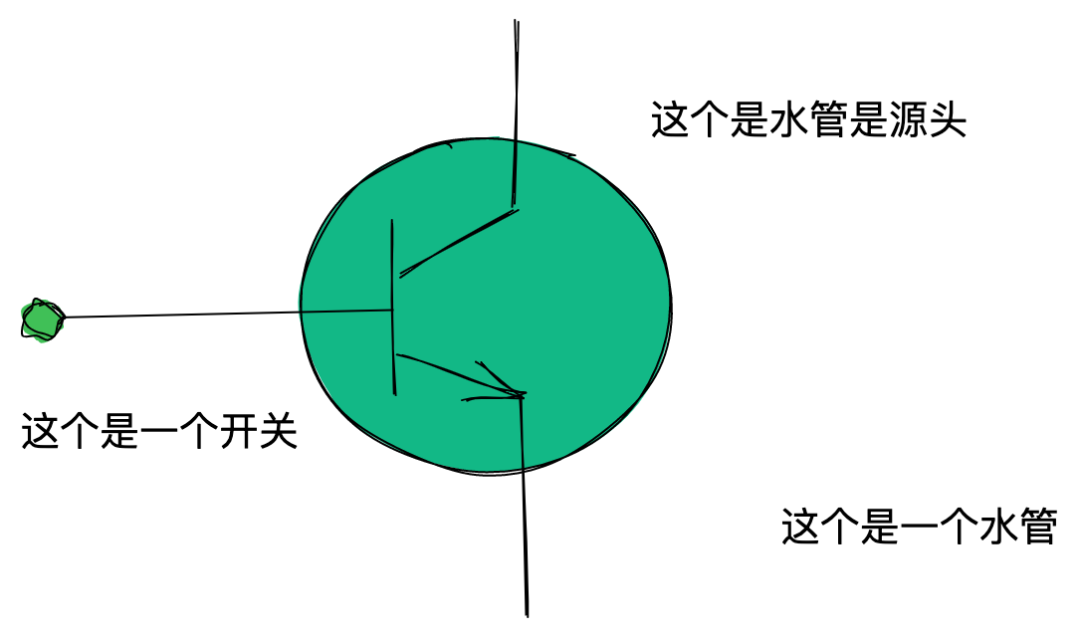

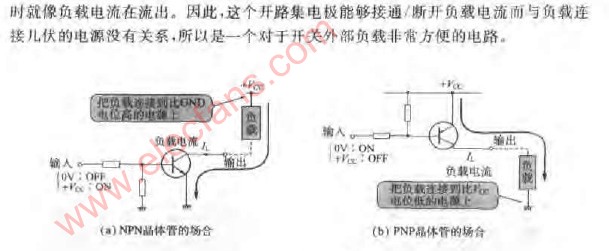

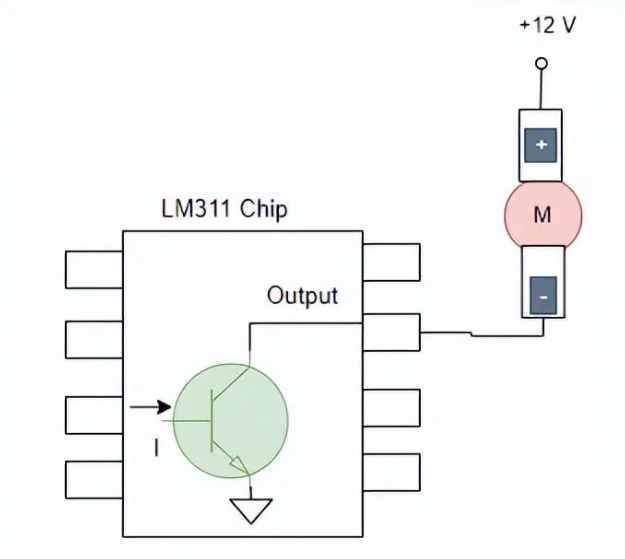

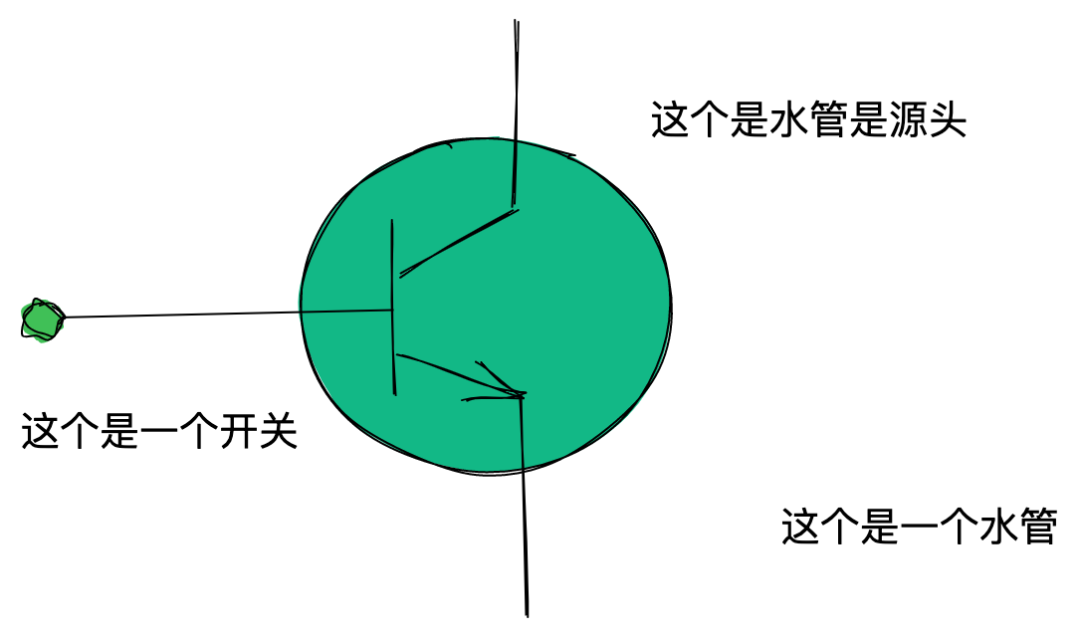

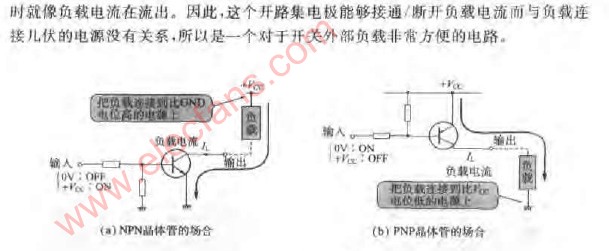

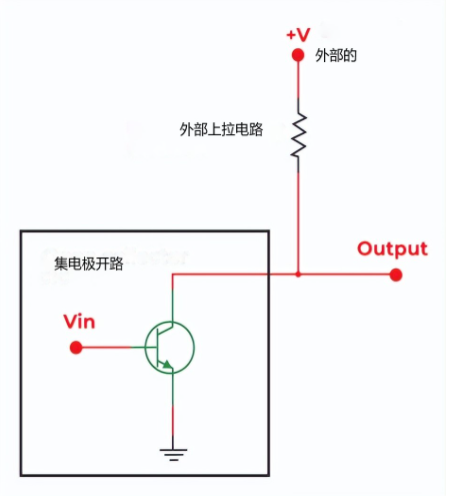

集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。

2023-07-21 10:00:28 793

793

漏极开路上拉电阻取值为何不能很大或很小?开关电源布线注意哪些?为何用万用表量电路板的电阻时需断电?

2021-11-12 07:59:46

地在MOS管的漏-源稳态截止电压上,出现电压尖峰。我的问题如下【1】MOS管的漏极就是相当于三极管的集电极,为什么要说成漏极,漏这个说法我一直不明白?【2】经常可以看到说变压的漏磁,漏磁通,或者电感的漏感,怎么理解这些定义?【3】上文说的,漏磁通下降了,漏感就任然可以释放储能,是根据什么?谢谢

2017-07-22 11:57:00

集电极开路 漏极开路 推挽 上拉电阻 弱上拉 三态门 准双向口

2016-06-02 16:22:21

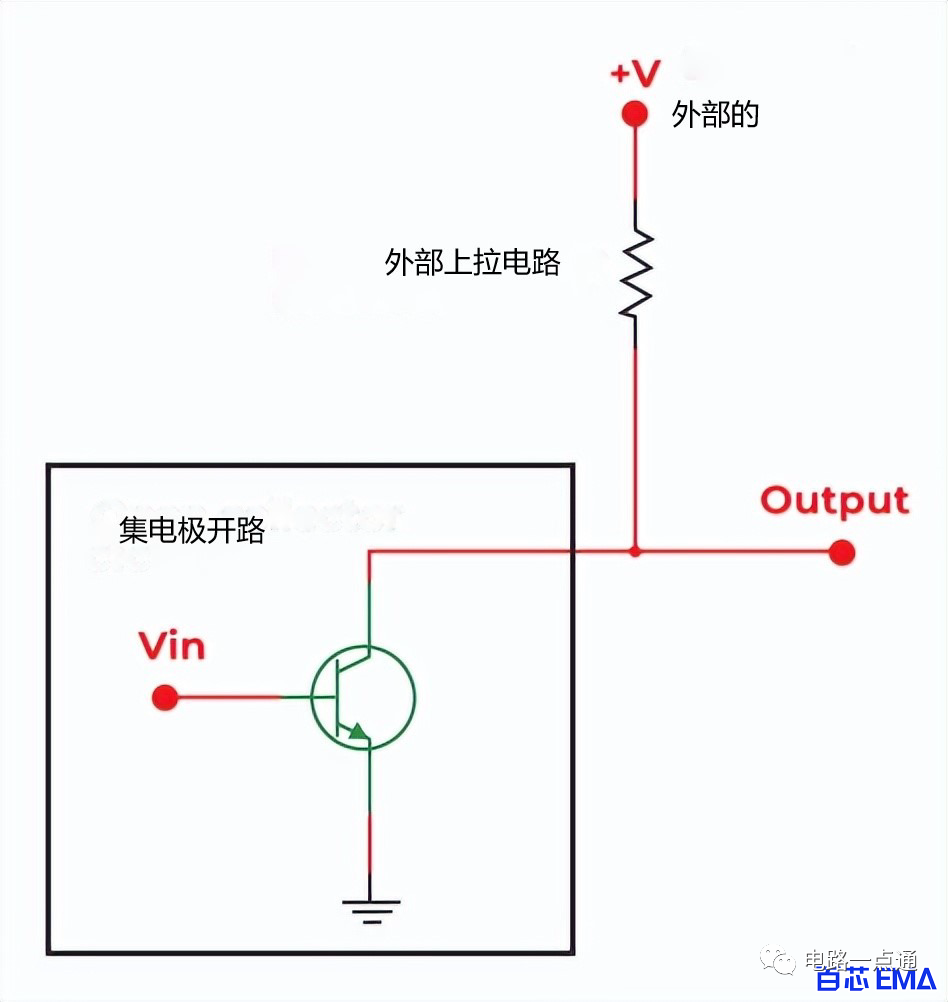

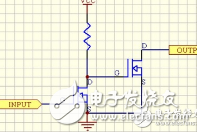

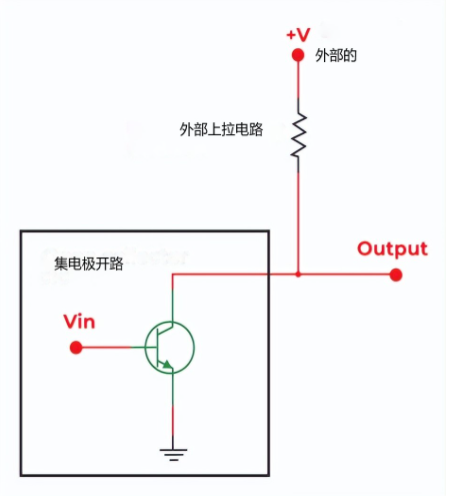

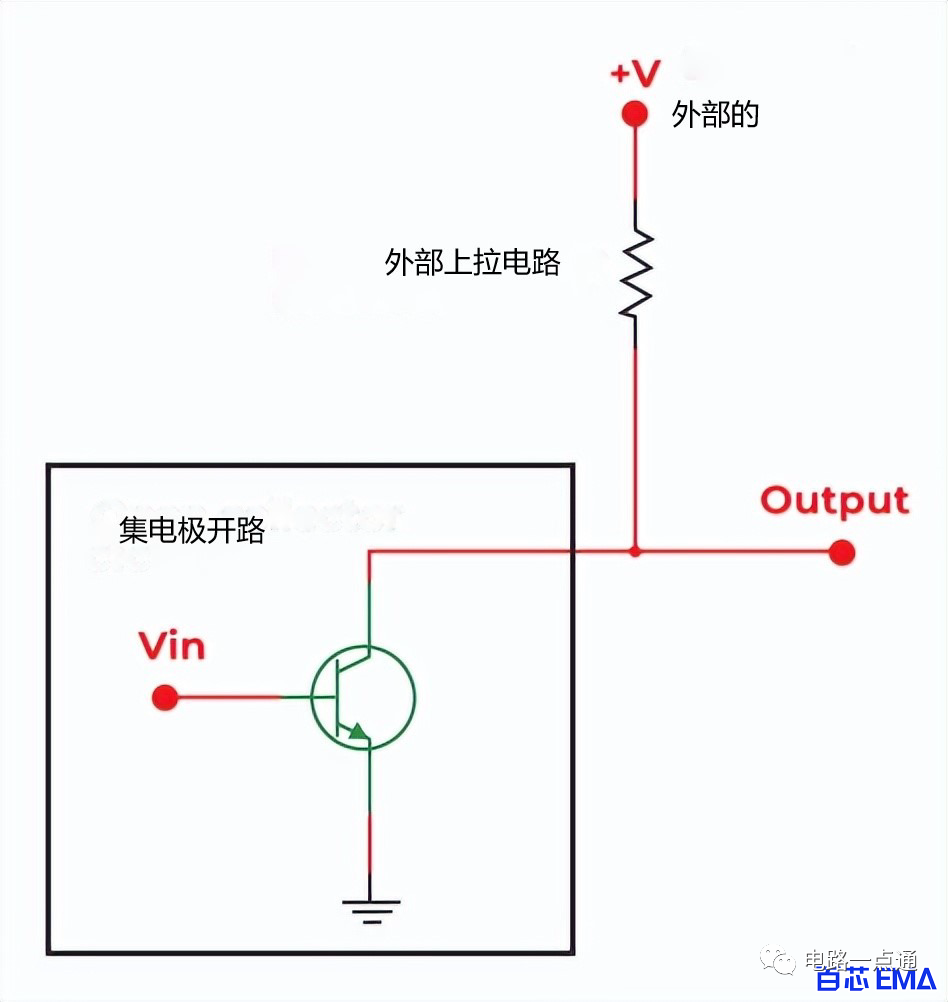

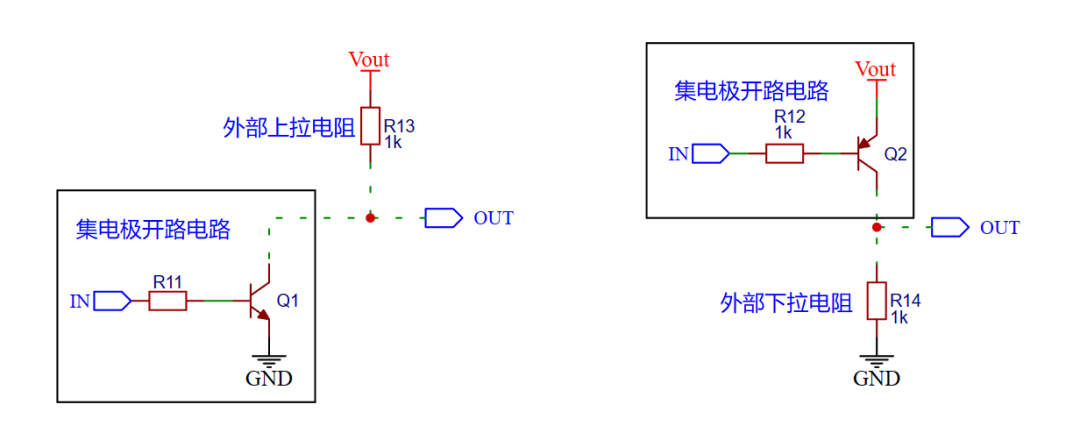

上拉就是通过一个电阻将芯片的一个引脚或线路中的一点接电源正极(Vcc),将该处电平拉向高电平。下拉就是通过一个电阻将芯片的引脚或线路中的一点接地,将该处电平拉向低电平。其主要目的是在电路驱动器关闭时给引脚或线路节点一个固定的默认的电平。上拉电阻有时还用来增加输出引脚的驱动能力。当所接电阻值比较大时称为弱上拉或弱下拉,否则就是强上拉或强下拉。上拉电阻应用比较普遍,大部分OC或OD输出都需要接上拉电阻。单片机的大部分I/O引脚也配备了弱上拉电阻。

2019-05-20 11:15:28

1、集电极开路输出上拉电阻电路为什么会速度降低和噪声变大?在此基础出引出了三态门?

2、多集电极开路上拉电阻输出实现了线或结构,有高为低,全低为高。那么什么电路结构可以实现线与结构,射极跟随,推挽,互补或者其他简单输出电路?

2024-01-28 16:32:00

三极管的原理光敏二极管的原理集电极电流Ic的形成

2021-03-10 07:36:40

断开,而对于P0口来说,就是高阻态了。对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。另一种输出结构

2016-06-29 11:11:00

断开,而对于P0口来说,就是高阻态了。对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。另一种输出结构是推挽

2017-03-21 09:20:02

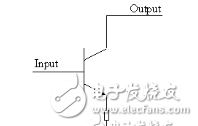

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2022-02-08 06:50:38

即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。另一种输出结构是推挽输出。推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出

2017-10-12 10:41:10

开关断开,而对于P0口来说,就是高阻态了。 对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。 另一种

2018-03-20 16:19:06

端口需要配置为漏极开路输出或集电极开路输出,请问该怎么用啊没有相关的寄存器可以配置输出模式

2018-08-13 06:41:32

我使用 xmc7100 芯片,使用 pwm 功能时,我需要将引脚配置为开路和漏极输出。 当我没有连接上拉电阻器时,示波器会检测到应该没有波形,但是有波形表明开路和漏极输出配置不成功,为什么不呢? 能否将 pwm 引脚配置为开路和漏极输出?

2024-01-23 06:34:37

本帖最后由 gk320830 于 2015-3-4 23:25 编辑

【经典】集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

2012-07-29 21:17:03

什么是集电极开路(OC)?什么是漏极开路(OD)?

2021-03-10 06:35:21

推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉

2021-11-24 07:22:11

单片机I/O开漏输出详解开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构

2021-11-24 08:11:44

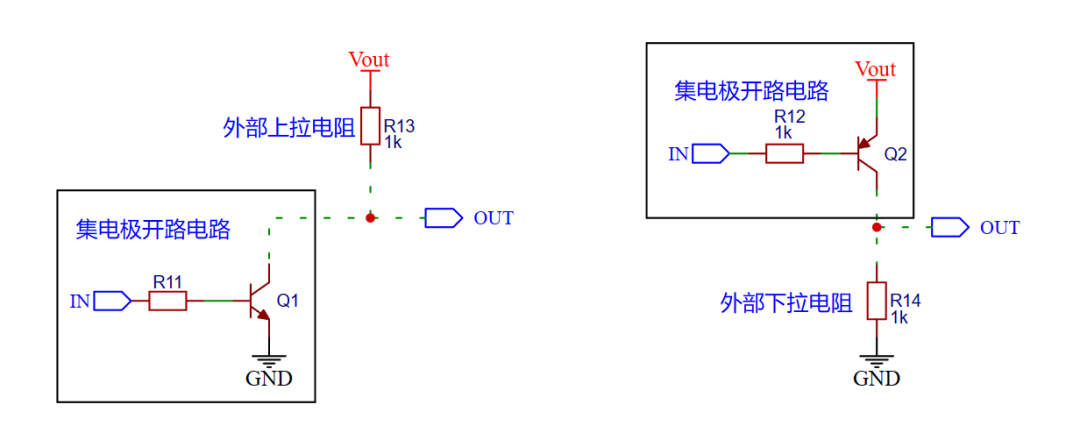

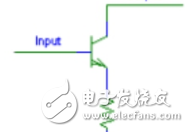

1.什么是源型 漏型?什么是上拉电阻?下拉电阻?什么是 线驱动输出 集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接

2021-07-15 09:15:48

本帖最后由 zhihuizhou 于 2011-11-2 10:20 编辑

集电极开路、漏极开路、推挽、上拉电阻、弱上拉、三态门、准双向口集电极开路输出的结构如图1所示,右边的那个三极管集电极

2011-11-02 10:20:11

你好,我使用的是PIC16F18854和开放漏极输出模式,我的问题是开放漏极泄漏电流似乎没有在数据表中指定。指定了输入漏电流(D340,D341),但是没有提到开路漏极。端口部分中的电路显示通过

2020-03-11 06:35:45

的IIC引脚设置为漏极开路。我读了ug471:7系列fpga selectedIO资源, ug768:7系列硬盘 ug865:zynq-7000-pkg-pinout但我没有找到将iic引脚设置为漏极开路的方法。你可以帮帮我吗?谢谢。

2020-05-14 06:37:27

我正在连接一个5V PIC18到2.5V设备。PIC18上的一些输出可以是开路漏极。我非常熟悉漏极/开路集电极输出,并使用了很多年。然而,说明书上的措辞有点麻烦。从PIC18F66K80系列说明书第

2020-05-12 10:28:10

我正在尝试清理我们的代码,现在正在查看我们的代码,该代码将两个 RMT 通道(一个输入,一个输出)配置为在同一引脚上工作,输出为漏极开路。我想我明白其中的大部分内容,但我不明白为什么我们需要设置

2023-03-02 08:25:00

我正在使用 NUCLEO-L552ZE-Q 并制作了一个非常简单的测试电路来测试漏极开路输出信号。我将引脚配置为漏极开路输出,没有上拉或下拉,信号通过 1K 电阻上拉至 3.3V。当我设置引脚时,我

2022-12-27 06:13:19

用运算放大器和三极管组成的恒流电路,想加上开路检测,检测到开路时输出高电平(或者是低电平)

2013-04-13 22:36:27

你好。我用的是STM32G071GBU6,VDD电压我设计成1.8V。我有一些关于董事会的问题。1. 3.3V GPIO 输出控制- 我是否应该将 MCU 的 GPIO 引脚设置为漏极开路并连接它

2022-12-07 08:43:22

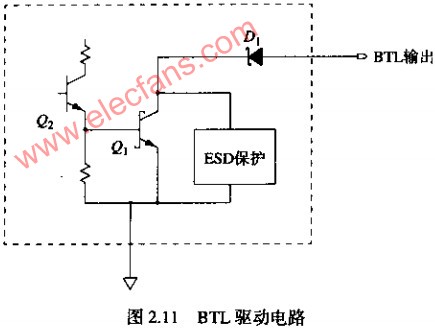

1.1.1 接口相关电路及概念1. 集电极开路输出在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指

2022-01-14 07:57:32

的,Vcc也要在数据手册规定的范围内。集电极或者漏极开路输出引脚是由一个晶体管控制的,当晶体管关闭时,输出引脚为悬空状态(开路或者高阻态)。一个常见的列子就是当N沟道晶体管导通时,输出信号接地,但关断时,输出

2019-04-23 08:00:00

集电极开路输出结构与推挽输出结构有什么不同?开漏电路有哪些特点?在使用开漏电路时有哪些注意事项?

2021-04-19 10:41:41

以前记三极管的何为发射极和集电极的时候都是死记硬背的,如下图带箭头的是e也就是发射极但是今天看到IGBT的原理图PNP的箭头处是集电极,于是就搞不太清楚这集电极和发射极的命名搜了网上说的 发射极即

2019-03-04 15:51:00

求助电路分析见下两图:MCU信号到集电极是高电平三极管导通吗?

2020-08-26 11:06:09

1.什么是源型漏型?什么是上拉电阻?下拉电阻?什么是线驱动输出集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做

2021-11-23 07:22:08

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-11-03 06:28:05

共集电极三极管能放大电压,而三极管本身就是可以放大电流的,这样应该来说共集电极接法的三极管能够进行功率放大,可是好像书上不是这样的,请问我的错误在哪?

2017-05-28 17:13:31

当三极管为开路输出时,三极管集电极通过一个负载,再从负载另一端接到电源,-----------------------------通常我们称为集电极开路输出。那么三极管为发射极这边来接负载时,这个

2019-08-01 00:03:31

请问各位:如何在QUARTUS II里将EPM1270的管脚配置为漏极开路?

2021-04-13 15:48:08

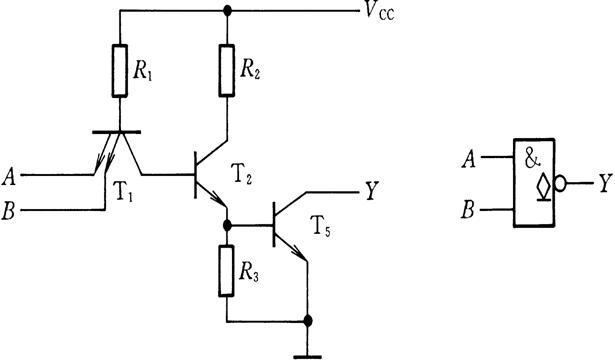

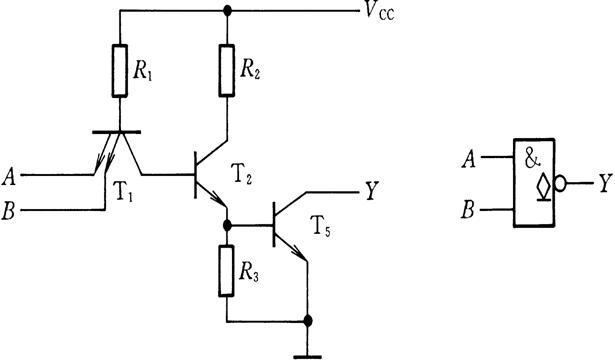

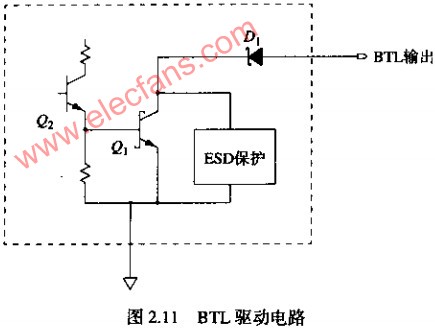

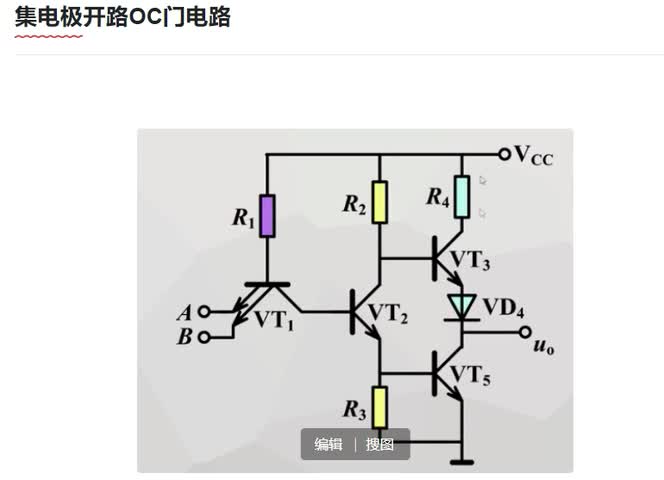

集电极开路门和三态输出门的应用

一、 实训目的1.熟悉集电极开路门(OC门)和三态输出门(TSL门)的逻辑功能;2.熟悉用OC门构成线与功能;3.熟悉用TSL门

2009-04-07 23:23:53 59

59 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,

2010-08-14 17:15:55 136

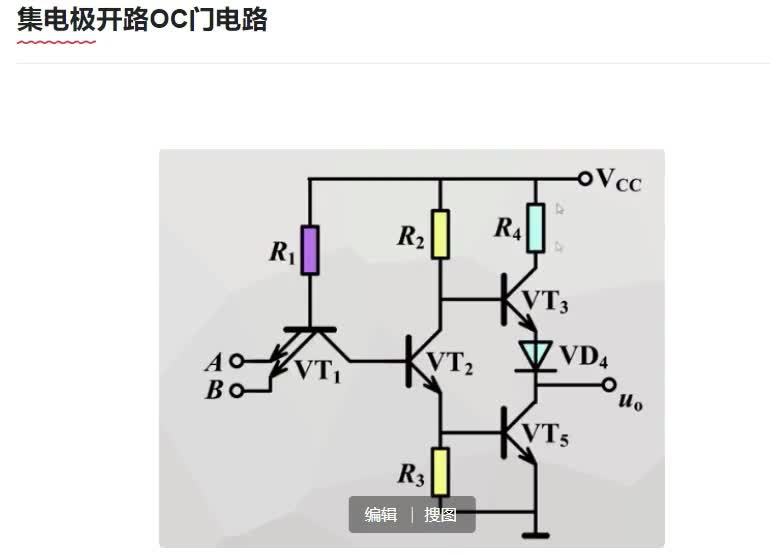

136 TTL或非门、集电极开路门和三态门电路

1.TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

2009-04-07 00:11:59 14317

14317

集电极开路门

在工程实践中将两个门的输出端并联以实现与逻辑的功能称为线与。 考察下图所示的情况。当将图中所示的两个逻辑门的输出连接在一起,并且

2009-04-07 00:15:19 20553

20553

集电极开路与非门的电路和图形符号

2009-07-15 19:02:06 7870

7870

开路集电极电路图

2009-08-15 17:27:30 864

864

什么是漏极开路(OD)? 对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可

2010-03-04 15:37:00 51861

51861 漏极开路(OD)原理说解

漏极开路(OD),它与集电极开路(OC)是一致的,就是把下图的三极管改成CMOS管就是了。

2010-03-04 15:38:44 3052

3052 集电极开路(OC)/漏极开路(OD)输出的结构

A:我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个

2010-03-04 15:41:39 2810

2810 用来计算TTL集电极开路输出电路静态功耗的公式如下:

其中:VT=上拉电阻的有效

2010-06-01 16:17:42 2549

2549

通过比较平衡电位和稳定电位的区别,进一步阐述了电池的电动势与开路电压的本质区别。讨论了各类锌锰电池开路电压的构成及其影响因素,以及生产过程中常见的开路电压问题。

2011-05-16 18:07:12 28

28 2012-11-23 21:49:17 4

4 2012-12-18 14:34:37 13

13 集电极开路_漏极开路_推挽_上拉电阻_弱上拉_三态门_准双向口,感兴趣的小伙伴们可以瞧一瞧。

2016-11-16 18:32:35 0

0 介绍了什么是集电极开路,漏极开路,推挽上拉,电阻弱上拉,三态门。

2017-02-28 22:08:40 1

1 在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指 MOSFET的漏极。同理,集电极开路电路中的“集”就是指三极管的集电极。在数字电路中,分别简称OD门和OC门。

2017-11-09 12:11:00 30603

30603

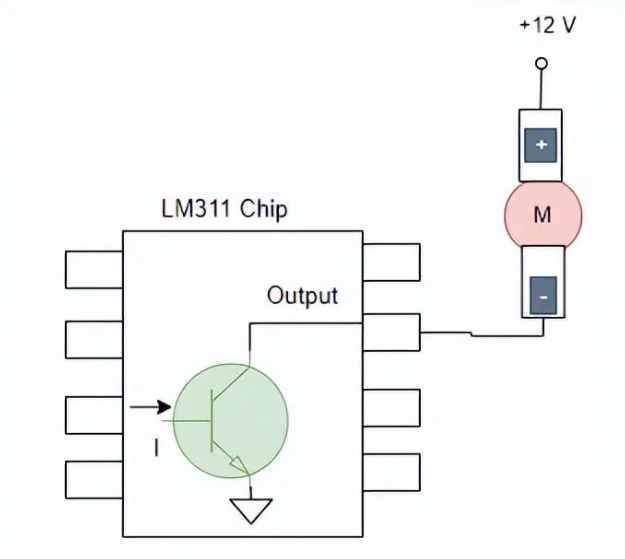

三极管导通时,集电极输出低电平;三极管关断时,集电极输出悬空,因此该电路在工作时需要外接负载电阻和电源。只要电阻的阻值和电源电压的数值选择得当,就能够做到既保证输出的高、低电平符合要求,输出端三极管的负载电流又不过大。

2017-11-09 12:17:53 145604

145604

漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。对于漏极开路(OD)来说,输出端相当于三极管的集电极。 要得到高电平状态需要上拉电阻才行。 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)。

2017-11-09 14:17:01 17820

17820

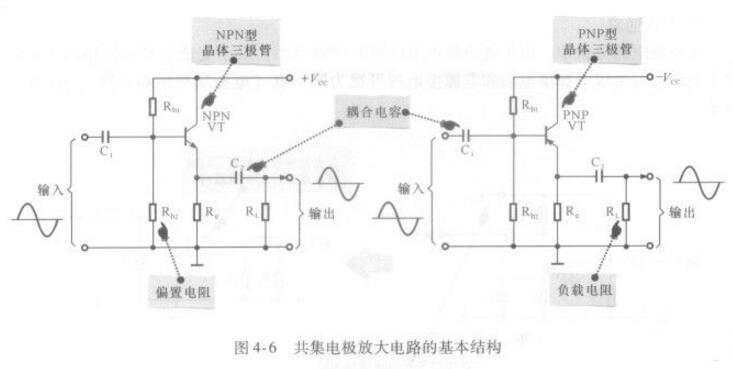

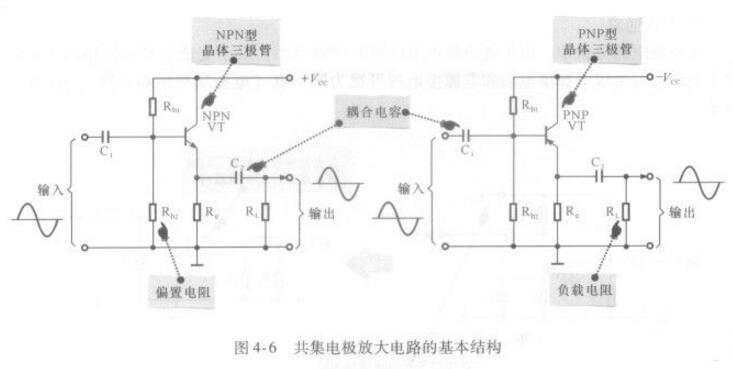

本文开始阐述了什么是共集电极电路和共集电极放大电路的基本结构,其次阐述了共集电极放大电路的功能与工作原理,最后介绍了共集电极放大电路的特性及详细的共集电极放大电路计算与分析。

2018-03-27 14:06:52 203764

203764

该装置包含六个独立的门,每个门执行缓冲功能。开路集电极输出需要外部上拉电阻才能正常逻辑操作。

2019-04-24 08:00:00 1

1 集电极开路输出端或者MOS管漏极输出端其性质都是一样的,这种电路在数字电路中都要加上拉电阻。比如在单片机P0口其内部驱动电路是MOS构成的,其结构就是一个漏极开路电路,其内部没有上拉电阻。

2019-09-28 07:00:00 8622

8622 PmodOC1是使用MMBT3904晶体管的集电极开路BJT模块。

2019-11-29 14:38:33 1351

1351

本文首先介绍了开路电压的概念,其次介绍了开路电压的计算方法,最后阐述了开路电压的影响因素。

2020-08-14 09:25:55 51230

51230 A、开路集电极NPN的接线方式,采用内部电源(由于采用内部电源,所以“+24V”和“PLC”的短接片必须连接可靠,而且电流的流向为从“+24V”到“PLC”到控制板内部整理电路,再到“Xi”端子,经过外部接点后回到变频器的“COM”端子):

2020-11-11 08:00:00 1

1 电子发烧友网为你提供什么是集电极开路(OC)?什么是漏极开路(OD)?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-13 08:42:31 9

9 DM5438/DM7438缓冲器集电极开路输出资料手册免费下载。

2021-06-01 17:51:18 11

11 1.什么是源型漏型?什么是上拉电阻?下拉电阻?什么是线驱动输出集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做

2021-11-15 13:51:02 0

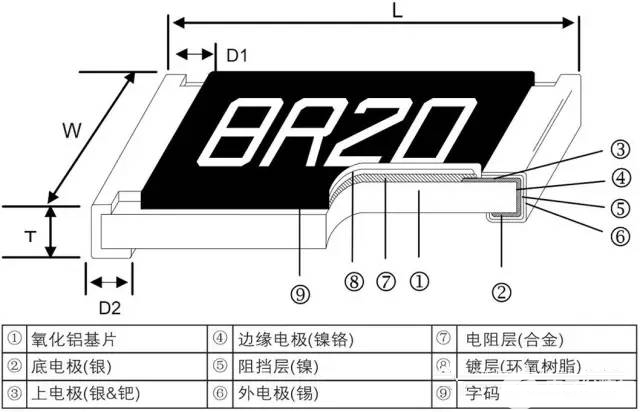

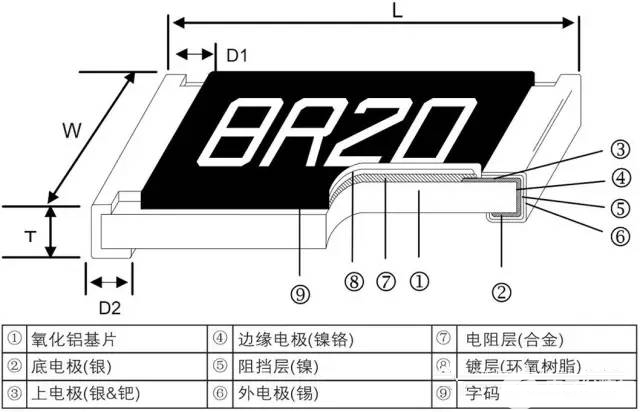

0 下图为贴片电阻结构图: 失效背景:电阻开路 问题分析:从失效样品图片来看,电阻本体没有电应力和结构损伤。如果没有电应力和结构损伤,一般是由于电极开路造成的失效,确定好失效模式和机理就可以针对性进行

2021-12-11 10:11:59 2702

2702

1.1.1 接口相关电路及概念1. 集电极开路输出在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提

2022-01-14 14:32:40 23

23 如果开关断开,则由于开关电阻为无穷大(不考虑实际中的漏电流),所以流过的电流为0,因此在1k电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。

2022-08-31 14:18:39 1925

1925 因此集电极开路的输出视为NPN晶体管,它允许电流吸收到公共端。对于这样集电极开路电路,必须有一个电源才能使输出正常工作。当我们要求未连接任何电源时计算输出电压时,电压不会发生变化。必须计算输出端的电压以了解集电极开路电路的正常运行。

2023-01-08 15:03:01 2856

2856 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-01-13 09:48:30 908

908 集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2023-01-16 09:16:28 756

756 何为集电极开路电路?集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。由于NPN

2023-07-31 23:07:05 890

890

ttl电路中推拉输出,集电极开路输出,三态输出有何不同? TTL电路是一种常见的数字逻辑电路,在电路中经常出现推拉输出、集电极开路输出、三态输出这些术语。这些输出方式在不同的电路中具有不同的意义

2023-08-31 10:32:19 2131

2131 开路电压是什么意思? 开路电压指的是在电路中没有负载负荷的情况下,测量到的电源输出的电压大小。在没有负载的情况下,电源输出电压的测量结果往往会比有负载时高出一定比例。 为了更好地理解开路电压的概念

2023-12-12 14:09:47 3501

3501 集电极开路电路是一种常见的逻辑电路,它的特点是输出端有一个开路的集电极。

2024-02-17 15:11:00 292

292

集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2024-02-15 09:24:00 179

179

pcb开路分析,这6个原因要注意

2024-02-21 16:43:39 181

181 集电极开路门的内部结构设计会直接影响其开关速度。例如,电极间的距离、材料选择、通道长度等都会对开关速度产生影响。

2024-03-18 17:10:20 125

125

电子发烧友App

电子发烧友App

评论