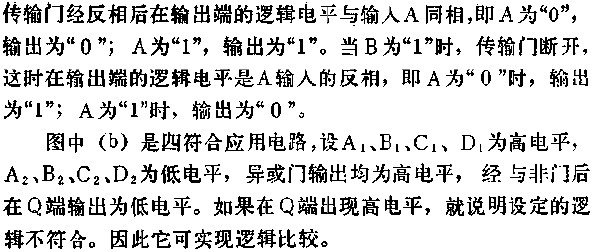

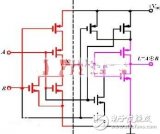

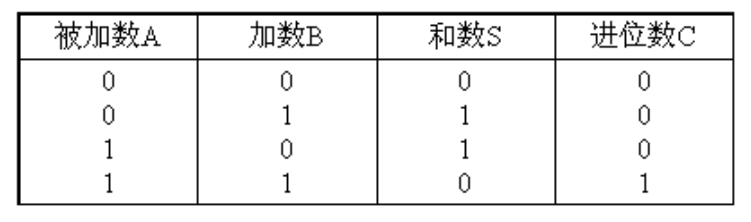

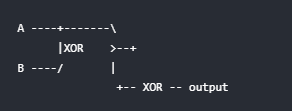

图A中所示是CMOS异或门的符号和真值表,B是四符合应用电路。由真值表可知,2输入端的异或门只有当输入信号

2010-09-14 00:56:03 7300

7300

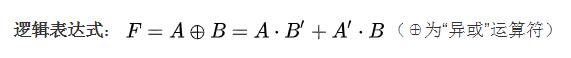

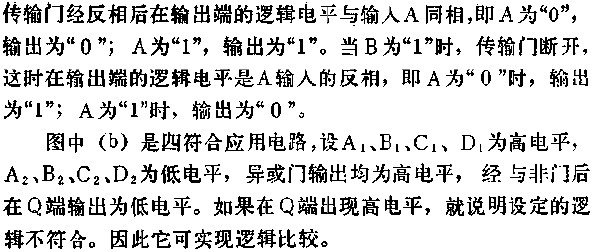

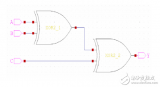

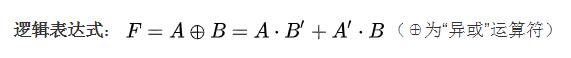

在这种实现中,当控制信号 B 为高电平时,异或门的输出将反转输入信号 A 的逻辑电平。如果 A 是高电平,则输出是低电平;如果 A 是低电平,则输出是高电平。而当控制信号 B 为低电平时,异或门的输出与输入信号 A 保持一致。

2024-02-04 17:40:01 990

990

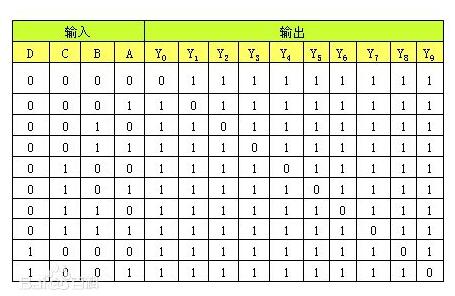

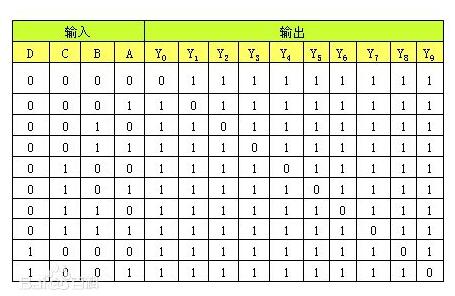

①简介74HC138芯片是一种三通道输入、八通道输出译码器,主要应用于消费类电子产品。(由于单片机I/O口资源有限,因此我们可以用它来实现I/O口的扩充)②管脚定义和说明③真值表(L:低电平 H

2021-11-22 08:56:19

工作电压范围:2.0V~6.0V最低输入电流:1.0uA真值表OE=0;LE=1 ; 输入和输出同步OE=0;LE=0 ; 输入的变化不会改变输出OE=1;LE=0/1 ;高阻态(三态门)OE接地,只控制LE

2021-12-07 06:43:42

①简介74HC573是一种八进制3态非反转透明锁存器。它是高性能硅门COMS器件。②管脚定义和说明OELEGNDVCC1D-8D1Q-8Q使能端锁存控制端地电源数据输入端数据输出端③真值表(L表示

2021-11-22 06:58:35

74LS00芯片资料及真值表

2012-12-07 13:03:28

异或门,相同得0,不同得1

2014-03-24 09:53:16

流水灯的部分电路第一张图只有2灯不亮 其他常亮 而 第二张图可以流水亮起测出来的真值表都是一样的。。。 不知道为啥输出结果不一样 求各位大神指点指点。。。。

2014-10-26 13:37:54

CD4053 的引脚功能见图4。CD4053 内部含有3 组单刀双掷开关3 组开关具体接通 哪一通道由输入地址码ABC 来决定。其真值表见表3。 图 4 CD4053 的引脚功能 表 3 CD4053 真值表

2012-09-10 10:41:44

你好我使用了VIVADO 2016.1,但我遇到了一个问题。我找到一些关键的真值表& nbsp;在实现后,LUT被更改,因此导致我不希望的逻辑错误。我怎样才能避免这种情况发生?有什么办法可以

2018-11-01 16:13:23

LUT与真值表有何关系?FPGA是如何通过两个相同输入的LUT5和一个MUX组成LUT6的?

2021-11-02 06:12:32

Q端为“1”(即高电平)、Q端为“0”(即低电平)时,称触发器处于“1”状态;反之,当Q=“0”、Q=“1”时,称为“0”状态。R-S触发器的真值表为表1-8。为了使触发器在计算机中和其它的部件能协调

2019-12-25 17:21:56

这个移位寄存器怎么设置呢?这个并行输入和并行输出是什么意思呢?我并行输入0001,那么也并行输出0001吗?想问一下这个寄存器的真值表,求大神解答

2017-06-24 12:50:31

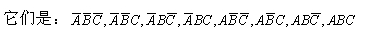

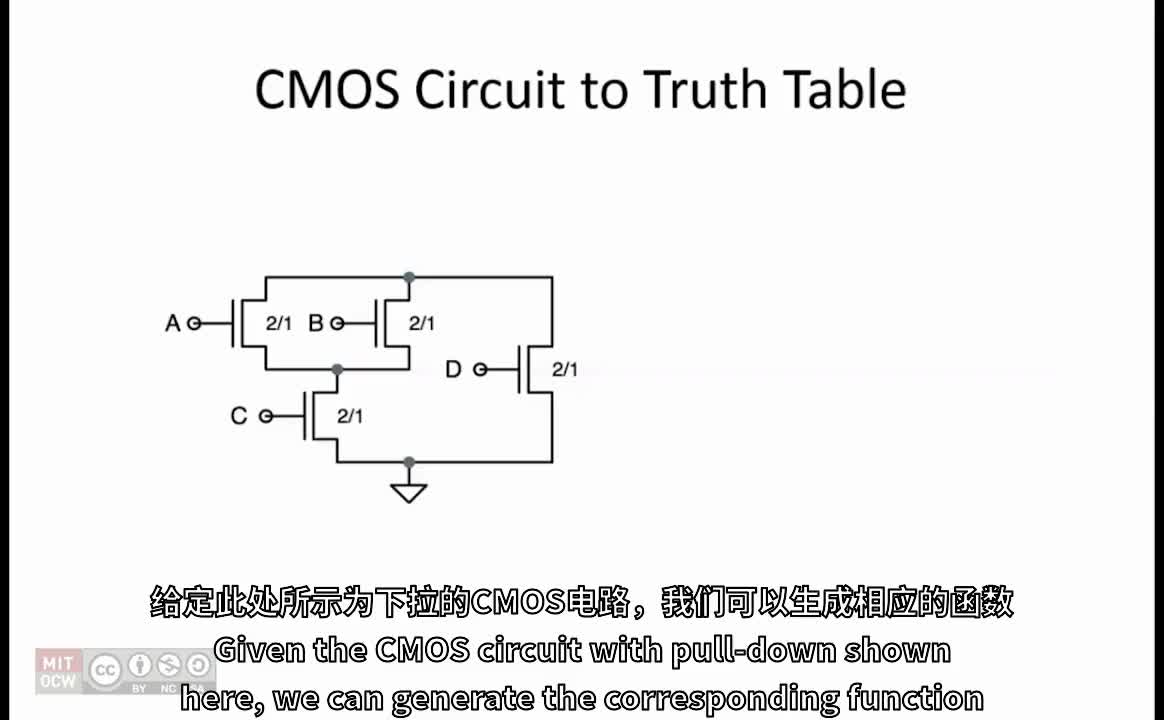

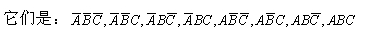

。ABCL0000111100110011010101010011110001101001 第三步,分析真值表后可知,当A、B、C输入变量中取值有奇数个1时,L为1,否则L为0。可见该电路可用于检查3位

2009-04-07 10:54:26

用逻辑分析仪分析已有电路的真值表,按下convert的第一个按钮,真值表的输出总是没有反应,还是一堆问号,我已经试过很多次了,求各位贴吧网友们的帮助!!!

2023-04-19 12:38:41

比如74ls74 138之类的,书上说在old_style macrofunctions里,quantus里没有啊

2014-11-22 14:55:09

的真值表,有8个输入信号和3个输出信号。I7输入为1时,对应的3个输出为110,当I6输入为1时,对应的3个输出为101,以此类推直至到I0的输入为1的时候。对应的三个输出为000。 变量表达式:依照

2020-04-24 15:07:49

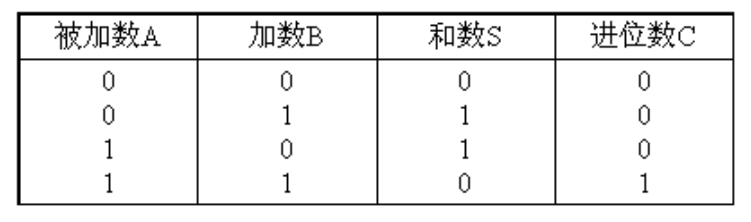

加法器,因为它给出两个二进制数的总和,因此,其设计比其他基本类型的逻辑门更复杂。真值表,逻辑符号和2输入异或门的实现如下所示。数字逻辑“异或”门2输入异或门符号真相表2输入异或门乙一种问00001个1个

2021-01-23 08:00:00

实现为例,分别讨论了用门电路、译码器、数据选择器的多种实现方案, 用实例说明了组合逻辑电路设计的灵活性与多样性。 1 三输入变量判奇电路的真值表及表达式 对于三输入变量的判奇问题, 设其输入变量

2011-11-07 16:13:06

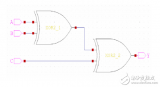

`刚开始学习数字电子技术,想问一下各位大神图中的两个与非门有什么用?我觉得不用也行,真值表输出跟输入完全一样啊`

2015-11-14 22:49:10

在复杂的数字电路中,用真值表的方法化简逻辑表达式很复杂,很麻烦,请问诸位高手有没有简单的方法化简逻辑表达式啊?小弟在这里不胜感激

2013-07-11 15:20:53

利用74LS00二输入与非门实现“与电路”、“或电路”、“或非电路”、“异或电路”、“同或电路”,要写出以上各电路的逻辑表达式和真值表,画出用二输入与非门实现的逻辑图并在实验箱上加以验证

2020-11-04 17:04:17

和真值表在与、或、非这三种最基本的逻辑门基础上进行一些扩展,就产生了一些常见的逻辑门如与非门、或非门、异或门、同或门,其符号和真值表分别如图3.8、图3.9、图3.10和图3.11所示。图3.8 与非门

2017-11-20 21:26:46

帮忙看看啊,是不是哪里出问题啊,和真值表完全不一样啊

2013-10-08 12:10:43

最近学这款软件,教材上说,打开帮助文件macrofunction,选messages项,继而选Macrofunction项和old_style macrofunction项,最后选Decoder中的74138,即可见到其真值表。哪位大神帮帮忙吧,最好截个图,非常感谢

2012-11-15 20:15:04

本帖最后由 gk320830 于 2015-3-8 20:32 编辑

QuartusII 7.2版本,想知道真值表,比如74ls138,7ls39

2012-12-20 13:53:48

MAX4539具有测量、自检和校准三种工作模式,不同工作模式可通过控制引脚CAL和地址引脚A0~A2进行选择,另外还具有使能控制和状态锁存,与CPU接口非常简单。工作模式及输入通道的选择参见真值表。

2019-08-02 06:05:08

更多信号,并且仅在所有输入关闭时才打开输出。下面是逻辑门的真值表和绘图。 也不或非门用于接收 2 个或更多信号,并且仅在所有输入关闭时才打开输出。下面是逻辑门的真值表和绘图。 异或异或门用于接收 2 个

2022-09-08 07:42:05

1、在FPGA中使用行为描述语句实现3-8译码器设计思路译码器电路有n个输入和2n个输出,每个输出都对应着一个可能的二进制输入。本实验设计实现一个3-8译码器,表3.1给出了该译码器的真值表。从

2022-07-01 15:26:26

各位大神:本人菜鸟一枚,刚开始接触单片机。想请问大神们,求常用单片机的功能表、引脚图、真值表。请发邮箱中164810174@qq.com 谢谢!

2013-04-25 18:18:35

关系真值表并画出逻辑图,并用multisim进行仿真(提示:仿真时输出码的状态可用发光二极管指示)。求给位大神帮忙哈,小弟在此感激不尽。。。。

2012-12-27 21:25:09

异或门输入端一端接入46khz方波,一端接地,输出端的方波有干扰

2018-01-04 11:20:44

合。5、详细讲解了比较器的特性和几个关键的参数,这将有利于对比较器的理解及电路设计。6、详细讲解光电传感器原理,特性。7、详细讲解了马达的驱动电路,教会大家如何利用真值表来设计马达的正反转和停转。8、详细

2015-07-24 12:01:53

路复用器的真值表,其逻辑功能是从四个输入中选择一个输出,因此选择信号需要两个比特。四选一多路复用器真值表原作者:硬木课堂语雀

2022-08-04 17:06:09

本帖最后由 gk320830 于 2015-3-9 22:17 编辑

逻辑函数与逻辑问题的描述 在讨论了与、或、非三种基本逻辑运算后,下面将从工程实际出发,提出逻辑命题,然后用真值表加以描述

2009-04-06 23:57:10

真值表 除了逻辑表达式,逻辑函数的描述方法还包括真值表和逻辑门。针对逻辑函数所有可能的输入组合一一列出输出值,我们就可以得到真值表。对于组合逻辑电路,只要列出所有可能的输入和对应的输出值,就可以完整

2020-12-23 17:25:49

及其对应的真值表。标准逻辑门逻辑与门符号真相表2输入与数字逻辑门乙一种问00001个01个001个1个1个布尔表达式Q = AB读为A AND B给出Q逻辑或门符号真相表乙一种问00001个1个1个01

2021-01-27 08:00:00

¡¤B = A ∩ B 其真值表为表 1-1。2.“或”门当两个输入端 A、 B 中, 只要至少有一个输入端为“1”时, 输出 端 C 就为“1” , 具有这种逻辑关系的电路叫做“或”门。其逻辑图如 图

2019-12-25 17:04:35

异或门电路

异或门和同或门的逻辑符号如下图所示。

2009-07-16 07:55:17 19884

19884

真值表,真值表是什么意思

把变量的各种可能取值与想对应的函数值,用表格的形式一一列举出来,这种表格就叫做真值表。设一个变量均有0、1两

2010-03-08 11:03:15 27756

27756 异或门,异或门是什么意思

异或门电路即,有2个输入端、1个输出端。当2个输入端中只有一个是高电平时,输出则为高电平;当输入端都是低电平或

2010-03-08 12:10:04 14813

14813 本文是74ls175的真值表及74ls175功能描述

2011-03-20 17:00:52 25396

25396

在电子技术中,N/2(N为奇数)分频电路有着重要的应用,对一个特定的输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。CD4013是双D触发器,在以CD4013为主组成的若干个二分频电路的基础上,加上异或门等反馈控制,即可很方便地组成N/2分频电路。

2017-10-23 15:08:07 2599

2599

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入

2017-11-19 17:59:49 62055

62055

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由

2017-11-20 08:54:42 83109

83109

异或门是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入异或门构成。若两个输入的电平相异,则输出为高电平1;

2017-11-28 12:07:05 65781

65781

表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

2018-01-30 15:16:13 64129

64129

与门真值表和与非门真值表的区别,与门真值表:有0出0,全1出1。与非门真值表:有0出1,全1出0。

2018-01-30 15:37:07 116740

116740

本文主要介绍了逻辑真值表怎么列出的_真值表是怎么画出来的。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个特定的方格图内,此方格图称为卡诺图。由A、B、C三个逻辑变量构成

2018-04-09 11:45:02 223669

223669

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入

2020-11-19 16:06:26 95481

95481

电子发烧友网为你提供三输入变量判奇电路的真值表及表达式资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-30 08:41:04 266

266 半加器是实现两个一位二进制数加法运算的电子器件,具有被加数A和加数B两个输入端、输出端Y,经常被应用在算数运算电路中,用于计算两个一位二进制相加,不考虑低位进位。

2021-07-09 09:46:58 47788

47788

2 输入单电源转换异或门-74LV1T86

2023-02-08 19:27:02 0

0 双 2 输入异或门-74LVC2G86

2023-02-09 19:22:43 0

0 双 2 输入异或门-74LVC2G86_Q100

2023-02-09 21:56:52 0

0 2 输入单电源转换异或门-74LV1T87

2023-02-10 18:36:39 0

0 四路 2 输入异或门-HEF4077B_Q100

2023-02-10 18:38:52 1

1 四路 2 输入异或门-HEF4077B

2023-02-10 18:39:06 0

0 低功耗 2 输入异或门-74AXP1G86

2023-02-10 18:39:40 0

0 四路 2 输入异或门-HEF4070B_Q100

2023-02-10 18:46:02 0

0 四路 2 输入异或门-HEF4070B

2023-02-10 18:46:15 0

0 2 输入异或门-XC7SH86

2023-02-10 19:02:31 0

0 2 输入异或门-XC7SET86

2023-02-10 19:04:17 0

0 2 输入异或门-74LVC1G86_Q100

2023-02-10 19:06:39 0

0 2 输入异或门-74LVC1G86

2023-02-10 19:06:53 0

0 低功耗 3 输入异或门-74AUP1G386

2023-02-10 19:10:35 0

0 3 输入异或门-74LVC1G386

2023-02-10 19:14:39 0

0 2 输入异或门-74HC_HCT1G86_Q100

2023-02-10 19:21:29 0

0 2 输入异或门-74HC_HCT1G86

2023-02-10 19:21:47 0

0 低功耗 2 输入异或门-74AUP1G86_Q100

2023-02-14 18:42:59 0

0 低功耗 2 输入异或门-74AUP1G86

2023-02-14 18:43:11 0

0 2 输入异或门-74AHC_AHCT1G86_Q100

2023-02-14 19:12:44 0

0 2 输入异或门-74AHC_AHCT1G86

2023-02-14 19:12:57 1

1 四路 2 输入异或门-HEF4030B_Q100

2023-02-15 18:40:51 0

0 四路 2 输入异或门-HEF4030B

2023-02-15 18:41:01 0

0 四路 2 输入异或门-74HC_HCT86

2023-02-15 19:34:20 0

0 四路 2 输入异或门-74LVC86A

2023-02-15 19:51:13 0

0 四路 2 输入异或门-74HC_HCT86_Q100

2023-02-16 21:10:44 0

0 低功耗双路 2 输入异或门-74AUP2G86

2023-02-17 19:03:41 0

0 四路 2 输入异或门-74AHC_AHCT86_Q100

2023-02-17 20:09:05 0

0 四路 2 输入异或门-74AHC_AHCT86

2023-02-17 20:09:15 0

0 双 2 输入异或门-74HC_HCT2G86_Q100

2023-02-21 18:25:14 0

0 双 2 输入异或门-74HC_HCT2G86

2023-02-21 18:25:30 0

0 为什么异或门又称可控反相器 异或门是一种常见的逻辑门,其中包含两个输入管脚和一个输出管脚。在逻辑运算中,异或门的输出值与两个输入值的逻辑值不同,称为“异或”,也被称为“可控反相器”。 在数

2023-09-12 10:51:22 2603

2603 共模差模输入计算公式详解 共模差模输入是电路中常见的一个概念,常用于放大运算器及其他电路中。本文将详细介绍共模差模输入的概念、计算公式及其应用。 一、共模和差模信号 在电路中,信号可以分为

2023-09-19 17:23:09 4077

4077 电子发烧友网站提供《XC7SET86 2输入异或门产品数据表.pdf》资料免费下载

2024-01-03 16:40:25 0

0 电子发烧友网站提供《四路2输入异或门74LVC86A数据手册.pdf》资料免费下载

2024-01-29 09:19:46 0

0 电子发烧友网站提供《四路2输入异或门74LVC86A-Q100数据手册.pdf》资料免费下载

2024-01-31 09:58:12 0

0 异或门可以用于实现二进制数的加减法。例如,我们可以使用异或门来实现两个二进制数的加法,如果两个相应的输入端上输入的数相同时则进行减法运算。

2024-02-04 14:47:09 740

740

正在加载...

电子发烧友App

电子发烧友App

评论