二进制中的两个数字0和1称为位(bit, 是二进制数字binary digit的缩写)。在数字电路中,使用两个不同的电平表示这两个位。一般情况下,1 用高电平表示,0用低电平表示,这种逻辑体制称为正逻辑。

2024-02-04 16:54:09 462

462

电路图如下!~想用光敏三极管的信号来使用单片机的外部中断,但是单片机I/O口一直保持初始值高电平,不能被光敏三极管的信号改变。同样的管脚,用一个震动模块产生的信号可是实现功能,但是光敏三极管就不能实现。请教高手是什么原因!~~如何解决?

2019-10-15 21:57:14

的方法是扩展一片8251 或 8250 通用同步/异步接收发送芯片(USART),需额外占用单片机I/O 资源。本文介绍一种用单片机普通I/O 口实现串行通信的方法,可在单片机的最小应用系统中实现与两个

2012-06-07 15:17:42

我已经成功地编程了CyPress I/O模块,但是当我进入驱动站时,诊断标签中的I/O LED不会变成绿色。 以上来自于百度翻译 以下为原文I've successfully programmed

2019-01-09 14:11:31

对于刚进入嵌入式学习的小伙伴,是不是总会遇到 I/O和GPIO的说法,两个到底都是什么呢?这里为你揭开I/O和GPIO的神秘面纱,快来学习一波。一句话总结, I/O是泛指所有类型的输入输出端口,包括单向的端口如逻辑门电路的输入输出管脚和双向的GPIO端口。

2021-12-09 07:31:48

我想用布尔开关来控制I/O输出的高低电平,请问出现图片这种情况,该怎么解决。还有如果要用8个开关控制8个口要用8个DAQ助手还是可以合在一起的。

2017-05-13 23:01:59

数字逻辑功能单元数字逻辑最终是需要通过数字电路的形式来实现的缓冲门:是仅具有缓冲功能的基本门电路,仅有一个输入端口,也仅有一个输出端口功能:将输入端口的信号电平原封不动地搬移到输出端口,输入为0

2021-07-29 08:04:47

数字逻辑功能单元有哪些呢?数字逻辑是怎样通过数字电路的形式来实现的?

2021-11-02 07:08:41

你好,当我直接连接逻辑低“0”到数字输出引脚,似乎输出引脚应始终是Low,但它总是高电压时,我检查了数字万用表输出引脚。为什么它的产量总是很高?最好的问候,…添加我的项目。如果你有什么问题,请告诉我

2018-09-13 15:20:20

输入管脚的处理 在多数情况下,集成电路芯片的管脚不会全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管脚,但实际上通常不会全部使用,这样就会存在悬空端子。所有数字逻辑器件的无用端子

2009-04-12 12:03:33

的《逻辑器件选型指导书》。3.6:逻辑器件的使用指南1:多余不用输入管脚的处理在多数情况下,集成电路芯片的管脚不会全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管脚,但实际上通常不会

2008-06-24 09:38:52

小弟毕设需要用到一个逻辑电平转换模块,主要问题如下: 1、FPGA输出的 3.3V 数字信号 需要通过 逻辑电平转换芯片,转换为1.8V或2.5V或3.3V中的一种。 2、 本设计需要16路数字IO

2015-09-04 21:21:28

兼容的问题。这并不罕见,例如,当工作于1.8V的数字电路必须和工作于3.3V的模拟电路通信时就会有这个问题。本文分析了逻辑电平的基本原理,并主要研究了如何在串行数据系统中不同的逻辑电平范围之间进行转换。[/hide]

2009-10-24 13:43:45

确定: - 损坏的用户I / O引脚的钳位二极管运行良好(我测量过) - 为LVCMOS25和上拉设置了正确的FPGA配置 - 即使在损坏的用户I / O引脚上将输入电压设置为逻辑电平“0”,我也始终

2020-04-07 12:26:15

双向管脚的控制代码本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 对于单向的管脚,输入信号或者输出信号

2015-07-01 10:32:49

实际的应用系统中,由于考虑未来的功能扩展或其它原因,经常会有未使用的 I/O。如何处理这些 I/O,关系应用系统的消耗电流甚至系统可靠性。因此,正确处理未使用的 I/O 端口,对于基于MCU

2021-11-04 09:09:01

量输入模块+数字量输出模块实现方式1、在200SMART软件里面添加远创智控YC9000的GSD文件,操作步骤由下图所示:点击GADML管理,点击浏览找到GSD文件放置位置选择您使用的plc,以我

2023-01-04 11:53:47

STM32F4开发板怎样通过引脚输入高低电平的方式对电机的正反转进行逻辑控制呢?STM32F4开发板与驱动模块如何实现对两个电机的逻辑控制呢?

2021-09-18 07:33:39

TC4052B各引脚功能及管脚电压 概述:TC4052B 多路逻辑开关用于选择与混合模拟信号和数字信号。TC4052B 是带参考电平的双向双路单刀四掷译码器。控制端子的数字信号经

2008-10-10 17:42:47

都可配置成输入、输出。每个bank的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。在差分信号的实现过程中,管脚分配应选择相应电平标准的bank中除首尾以外的其他48个IO

2020-12-23 17:17:47

,首先需要将模拟信号转换为数字信号,并对其编码后再提交给数字系统处理。 显然,为了满足以上这些要求,需要设计许多种类的数字电路才能实现人类的需求。数字逻辑就是这样一种用来分析和设计复杂的数字逻辑电路或

2009-04-07 10:44:14

labview怎么实现像plc一样的通过输入输出I/O量,控制开关量,比如通过I/O点控制继电器的吸合。怎么给I/O量分配地址,怎么在程序里使用这些变量实现一系列有序的动作。希望能附上一份样例程序,让小弟学习领会,请多指教,谢谢。

2016-04-25 00:51:33

stm32 的电平是3.3V,但是有些模块的电平要求5V,大家是怎么实现的呢?

2016-11-28 22:34:36

i2c_master_bit_ctrl.v 完成位传输的功能。位传输的功能包括数据按位传输的实现和I²C协议各个命令的实现两部分。如图 4-5 所示开始和重复开始命令的产生包括 5 个阶段:idle

2018-10-09 11:43:44

8-1数据选择器 逻辑功能:上图是8-1数据选择器的真值表,我们从真值表中可以看出,当A=000时,输出I0为高电平,其余为低电平,对应高电平的开关闭合,而对应低电平的开关则仍保持断开,因此,Y的输出为

2020-04-24 15:07:49

)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或

2019-08-11 04:30:00

请问一下我在使用51最小系统板做流水灯的时候通过程序无法改变I/O输出电平是怎么回事,I/O持续输出5V高电平,但是把芯片换到另一个基座就可以改变,请问哪里可能出问题了

2023-09-27 07:38:20

为什么配置I/O口:I/O端口寄存器复位后默认为输入(输出高阻态);为实现I/O端口功能需要先对端口进行I/O口初始化配置I/O口需要的几种寄存器:ANSELx(模拟选择寄存器):0 = 数字I/O

2021-11-24 06:19:54

前言此实验是通过STM32CubeMX来配置stm32实现按键输入,以此来了解stm32I/O的输入操作及如何使用HAL库来实现I/O输入。本实验中的按键操作使用的是软件中断,并未用到stm32

2022-03-01 06:58:08

,输出高低电平。就是通过这简单的控制电平来实现大多数的应用控制。1. 什么是 I/O 口?I 表示 IN(输入),O 表示 OUT(输出),所以 I/O = 输入/输出2. I/O 具体能做什么呢?如果你是刚刚步入电子的新手,那你最好要知道一下I/O口具体能做什么。感性的认识对你的..

2021-11-24 06:47:23

UEFI学习(四)-SuperIo的访问一、什么是Super I/O?二、我们要用SuperIo实现什么三、NCT5581D的访问机制一、什么是Super I/O?Super I/O 芯片也叫 I

2022-01-24 08:12:27

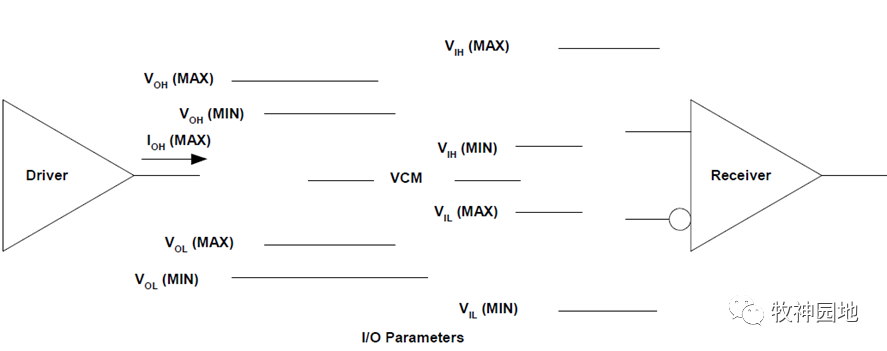

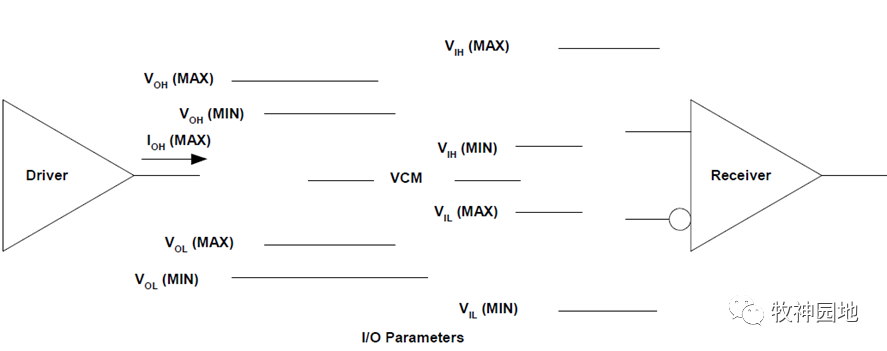

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2021-05-06 06:39:26

P1.7使用上升沿触发中断。在仿真运行时,在外部还没有加上中断信号时,会进入一次中断。每次都是这样,是不是由于仿真过程中I/O管脚有上升电平造成的?

2015-02-10 14:13:16

使用MCU的I/O管脚连接物理按键,当按键按下时会发送上升沿或下降沿的电平出发中断,这个容易判断。

请问,对于按键双击动作,以及按键长按动作,应该如何判断?

是否存在简单的实现方法,最好能给Demo源码,多谢!

2023-08-24 07:42:04

的作用。因此,探讨一些键盘的特殊结构,用尽可能少的输入输出端口实现较多数量的按键数仍具有重要的应用价值。 有些特殊情况下,在组成一个最小的单片机系统的过程中,由于通用的I/O口有限,而又需要大量的按键

2012-02-15 22:02:49

逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能,看!

2019-07-23 07:03:30

单片机I/O口如何检测按键输入电平?

2021-10-26 07:01:11

单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平

2017-12-14 20:15:53

信号,而非电平信号)直接模拟输入到片上外设模块,比如ADC模块等等。开漏输出模式开漏输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经N-MOS管,最终输出到I/O端口。这里要注意

2021-05-18 06:30:00

12路、模拟输入 4路:Neuron3150芯片I/07至I/0010管脚用来接收室内温湿度值,配置成4路模拟电路;I/O-O至I/O-6管脚和利用地址总线扩展出的3路I/O口共同形成24路数字

2021-06-17 07:30:00

12路、模拟输入 4路:Neuron3150芯片I/07至I/0010管脚用来接收室内温湿度值,配置成4路模拟电路;I/O-O至I/O-6管脚和利用地址总线扩展出的3路I/O口共同形成24路数字

2021-06-23 07:30:00

的SSI接口卡,但价格昂贵且驱动程序较为复杂。工控机上多配备数字量输入/输出卡。本文采用数字量输入/输出卡控制SSI并行接口模块SSI208P,实现了一种SSI接口的低成本、高速数据采集方法。1

2019-05-28 05:00:03

芯片上,接通Sink节点和计算机就可以实现该功能. 3.1 程序流程图 程序流程图如图2所示. 3.2 程序结构 3.2.1 实现I/O控制的配件文件 配件中定义了I/O控制的模块

2018-11-13 16:27:39

我毕设要做一个多通道数采系统,需要用NI 多功能数采卡的数字I/O输出控制CD4051的3个控制端,在数字输出的编程上遇到了点问题。想请教一下,这个DO输出的数字量是瞬时的还是持续的?我需要通道选定后保持,然后发波、采集,完了之后再切换通道,即改变数字输出量。这个数字I/O编程怎么实现?

2014-04-25 21:44:34

如何实现数字系统的电平和极性转换?比较器在电路中起到什么作用?

2021-04-14 06:31:09

在数字电路中开关(switch)是一种基本的输入形式,它的作用是保持电路的连接或者断开。Arduino从数字I/O管脚上只能读出高电平(5V)或者低电平(0V),因此我们首先面临到的一个问题就是

2022-01-17 08:35:42

操作PIC24 I/OPIC24是一款16位的单片机,它的I/O操作和STM32差不多,但是比STM32更简单。操作PIC24的I/O输出高低电平需要配置一下寄存器:1.TRISx,该寄存器控制I

2021-11-24 07:30:02

至 300VDC 输入电压的灵活解决方案通过 MCU 实现可编程开关阈值优秀的长期可靠性,并提供数字隔离功能提供湿电流控制选项输出可以是 I2C 输出,也可以是数字输出

2018-09-20 08:55:55

MCU通用I/O引脚扩展 低端MCU由于I/O口数量不足导致部分功能无法实现,用户需要使用数字集成芯片进行扩展,如74LS系列移位寄存器,但是这种集成芯片也会由于引脚数量限制而无法确保单片机端口

2024-01-08 09:35:10

怎么实现基于可编程逻辑器件的数字电路设计?

2021-05-06 08:36:18

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

嗨,大家好,我需要能够驱动连接到的特定设备3.3 I / O bank(配置为输出)至逻辑高电平为3.5V。有可能的将I / O引脚上的上拉电阻器设置为+ 5v以帮助实现此目的?如果你想知道什么我

2019-05-15 14:18:47

。这类转换器的常见应用是以字节(byte)访问的存储器及I/O器件。 自动感测双向逻辑电平转换器(推挽型输出)的工作原理是:启用(EN)引脚为低电平时,转换器处于待机状态;EN引脚为高电平、I/O

2018-10-10 17:10:37

硬件设备树莓派 * 157H76两相四线步进电机 * 1DM542驱动器 * 136V DC开关电源3.3V-5V电平转换(驱动器输入需要5V脉冲,树莓派可控管脚输出电压不够)接线接线如下所示

2021-07-08 09:29:55

描述此参考设计是一个具有双隔离输出的 1W 电源,适合于空间受限的应用。利用 24V 和 3.3V 隔离输出,此设计专用于为工厂自动化设置的可编程逻辑控制器 (PLC) I/O 模块供电。此设计符合

2022-09-22 06:22:07

电平才能跳变,否则维持原来状态。如下图,A、B分别是2个输入端电平,O是输出端电平,怎样用简单的电路实现功能?关键是第2阶段和第4阶段的跳变条件要满足。

2013-10-28 14:16:25

DSPF2812 GPIOF12配置成通用I/O,发现输出不了逻辑高电平,结果发现这个管脚没有内部上拉,是这个原因吗?

2020-06-04 14:04:45

闪存设备管理技术的现状及存在的问题是什么?闪存设备I/O软件的分层结构是怎样的?怎样设计并实现闪存设备I/O软件?

2021-04-27 06:44:40

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

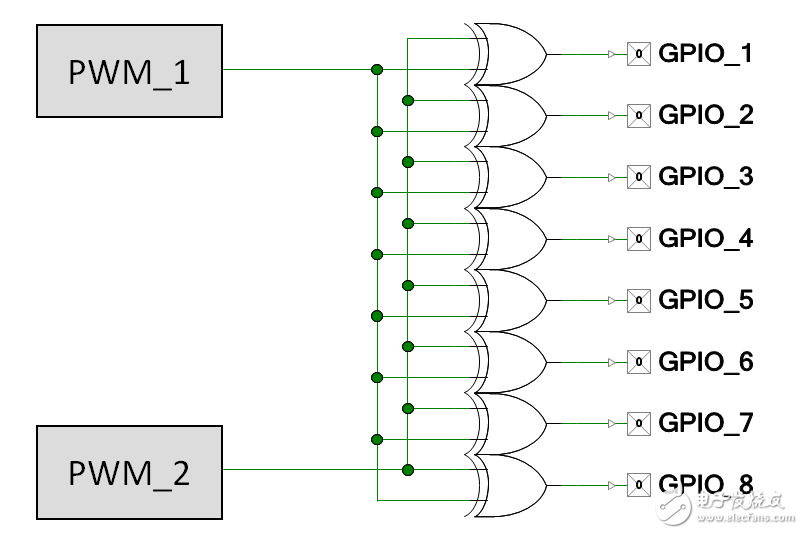

硬件实现的应用包括了灵活的编码输入,PWM 信号I/O,PID 控制,定制计数器实现,数字协议仿真,离散控制和定制测量等等。[hide] [/hide]

2009-07-23 08:15:57

。以下将要讨论基于下一代I/O技术的一些应用。设计挑战1、高数据吞吐量需要新的信令方案由于高端手机LCD显示器的分辨率超过了SVGA(800×600),而翻盖式电话中应用处理器和LCD模块之间的RGB

2019-05-27 05:00:06

机型丰富,更多选择 S7-200 SMART PLC提供不同类型、I/O点数丰富的CPU模块,单体I/O点数最高可达60点,可满足大部分小型自动化设备的控制需求。另外,CPU模块配备标准型

2020-12-04 16:21:47

MxxxT 工业远程以太网I/O 数据采集模块内嵌32 位高性能微处理器MCU,集成1 个工业级10/100M 自适应以太网接口支持标准

2021-10-26 19:50:14

数字系统的基本算法与逻辑电路实现:本章主要介绍数字系统的基本算法设计及对应的逻辑电路的实现方法。算法设计中主要考虑的因素1.逻辑指标这是数字系统最重要、

2009-09-01 09:04:09 0

0 摘 要:介绍了声纳脉冲侦察模块的测向测距原理、硬件设计及其实现。声纳脉冲侦察模块硬件电路以数字信号处理器为核心,通过可编程门阵列实现逻辑控制,再配以适当

2006-04-07 00:36:43 722

722

二值数字逻辑和逻辑电平

二进制数正好是利用二值数字逻辑中的0和1来表示的。二值数字逻辑是Binary Digital Logic的译称。 与模拟信

2009-04-06 23:37:10 3518

3518

摘要:逻辑电平转换技术及其缺陷—Maxim的解决方案。

对逻辑电平转换的需求越来越多的数字IC采用与以往不兼容的电源电压、更低的VDD、或者VCORE和VI/O不同的

2009-04-23 14:01:11 3035

3035

基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

本文是对三极管实现逻辑电平转换进行具体分析,希望能帮助到大家!

2016-03-24 17:35:11 14

14 三电平SVPWM方案的实现,有需要的下来看看

2016-03-30 14:59:59 24

24 逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能。

2017-09-19 14:19:18 23

23 问题而写。文章先介绍常用的几种逻辑电平,然后给出其与光模块的接口电路。 TTL 电路的电平就叫 TTL 电平,CMOS 电路的电平就叫 CMOS 电平。 TTL 集成电路的全名是晶体管-晶体管逻辑集成电路(Transistor-Transistor Logic),标准 TTL 输入高电平最小 2V,输出高电平

2017-11-06 16:50:08 100

100 异或门是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入异或门构成。若两个输入的电平相异,则输出为高电平1;

2017-11-28 12:07:05 65781

65781

DigilentPmodLVLSHFT是一个数字逻辑电平转换器。

2019-11-29 14:53:50 1774

1774

本文档的主要内容详细介绍的是使用单片机实现单个数码管指示逻辑电平的C语言实例免费下载。

2020-11-12 17:33:55 9

9 电平转换在实际电路设计中常常会用到,不同种类逻辑电平之间的转换一般通过特定逻辑功能器件实现(如使用MAX232实现TTL转RS232等等),但随着器件集成度的增加,工艺的提升,现在的控制器使用的逻辑

2021-01-07 17:07:00 12

12 电子发烧友网为你提供实现管脚电平数字逻辑功能和降低CPU负载资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-14 08:46:14 9

9 为了精简电路 电器中会用到逻辑电平代替复杂的接线 他们都是如何设计的呢? CMOS器件与TTL器件 CMOS电平与TTL电平 如何利用MOS管实现双向电平转换 什么是LVDS电平

2022-12-14 11:36:07 437

437 差分逻辑电平之间的匹配,主要应用于时钟和高速信号。

2023-06-25 14:56:13 1499

1499

进行逻辑计算或判断,从而实现数字电路的功能。 在现代电子设备中,信号的逻辑状态往往通过逻辑电平来表示。逻辑电平分为高电平和低电平两种,通常高电平表示“1”,低电平表示“0”。“1”和“0”是数字电路中最基本的逻辑符号,

2023-09-19 17:16:11 694

694 为什么要进行电平转换?电平转换的几种实现方式 电平转换是在数字信号中,将信号的电平从一种电平转换为另一种电平的过程。电平转换通常用于将数字信号从一个设备传输至另一个设备。 在数字系统中,电平转换

2023-11-01 14:56:17 1194

1194 什么是线与逻辑,要实现它,在硬件特性上有什么具体要求? 线与逻辑是一种基本的数字逻辑电路,用于实现布尔代数中的逻辑运算。在线与逻辑中,当所有输入信号都是高电平时,输出信号才为高电平;否则,输出信号

2023-11-17 14:11:38 1408

1408 Metal-Oxide-Semiconductor)。 TTL是一种基于晶体管的数字逻辑电平标准,使用5V电源供电,逻辑高电平(1)通常在2.4V以上,逻辑低电平(0)在0.4V以下。TTL逻辑电平的优点是速度快、噪声容忍度高,常见于早期的数字电路。然而,由于功耗较大,现在更常用的是

2023-11-17 14:16:06 650

650 逻辑电平是数字电子系统中的关键概念之一。它决定了信号被认定为高电平还是低电平,并进一步影响着数字电路的正确操作。逻辑电平是用来表示数字信号状态的电压水平。在数字电子系统中,常用的逻辑电平有高电平

2023-11-24 08:20:20 1681

1681

电子发烧友App

电子发烧友App

评论