事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象:

我们有的同学可能已经学习了这样的一条PCB布线规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。

如OC或OD电路要控制一个电平就是通过它这个开关的通断来实现的。有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为了防止电路失控的情况下仍然是有效电平,那么当然是低电平有效才更“保险”了。结构上,象OC电路那样,由于集电极更难击穿,所以,也更不容易损坏。

对于其它图腾柱输出的电路,虽然0和1都有同样的风险,但应用中还是有人愿意加一个上拉电阻,以取得类似OC或OD输出的效果。至于为什么不采用下拉电阻而用上拉电阻,大家也可以分析一下。

另一个方面是OC或OD输出的电路,使用上拉电阻后具有节能的效果。因为关断后它是具有获得高电平时的电流几乎为0。

解密:数字电路为什么是低电平有效的多?

- 数字电路(79616)

相关推荐

如何看懂电路图(六):数字逻辑电路详解

数字电子电路中的后起之秀是数字逻辑电路。把它叫做数字电路是因为电路中传递的虽然也是脉冲,但这些脉冲是用来表示二进制数码的,例如用高电平表示“ 1 ”,低电平表示“

2012-05-11 14:48:16 42175

42175

42175

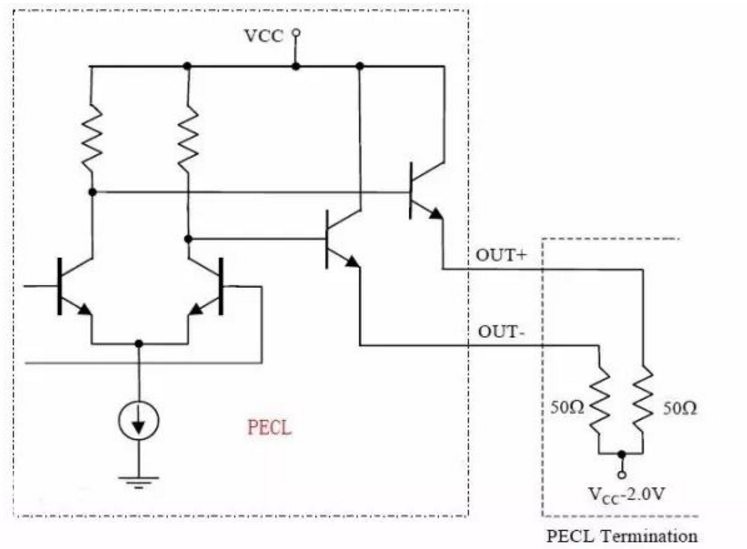

42175数字电路电平标准与接口设计解析

在高速电路中如何实现高速驱动输出呢?要么增大驱动电流,要么降低电平标准,或者提高晶体管工作速度。显然前者会带来非常大的功耗,因此改变电平标准和改进晶体管设计成为选择,虽然低电平更容易受到干扰,所以需要更严格的硬件设计。

2017-12-17 07:38:50 12769

12769

12769

12769

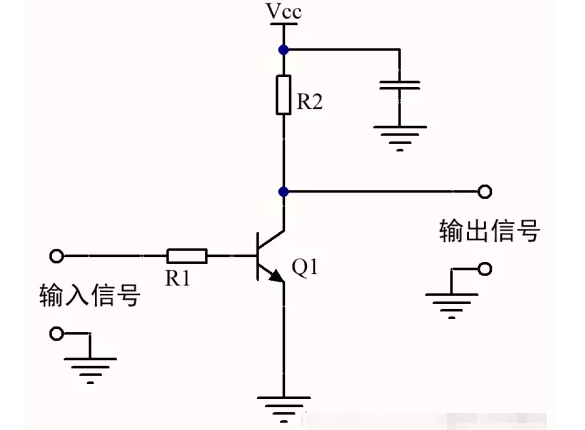

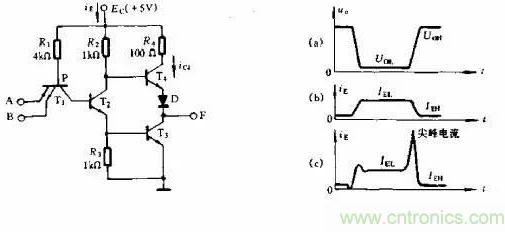

三极管电平转换电路设计

在数字电路的领域,常常把电压简化为电平,来描述逻辑状态。比如TTL电平信号规定,+5V等价于逻辑“1”,也称为高电平,0V等价于逻辑“0”,也就是低电平。数字电路里,只有0和1两个状态。其实从0V

2023-04-20 14:35:09 1740

1740

1740

1740

高电平和低电平是什么意思?区别是什么?

高电平和低电平是数字电路中经常会出现的专业名词,它们所表面的意思就是电路上有和无,两者之间没有中间值,在不同的电路上,电压的具体值也是各不相同的。如果用简单的语言表达它们的意思就是开和关,平时

2023-05-26 10:17:30 24069

24069

24069

24069

数字电路是什么

电源电压的高电平和低电平来分别表示0和1,从而实现信息的表达。 不同于生活中使用的数字0123456789,在电子硬件中最常使用的是2进制和16进制,而数字电路中采用的就是二进制。 二进制中一个字节(byte)通常由8个数据位(binary digit)组成,

2023-11-06 17:25:57 1126

1126

1126

1126

低电平和高电平的区分方法

高电平低电平主要应用于数字电路。体现在电路上就是只有‘有’和‘无’,没有中间值,这个有在不同电路上的电压值不相同。如果是5V供电的数字电路,高电平就是5V,或接近5V。低电平就是‘无’,就是0V或

2018-08-28 14:59:04

低电平转高电平问题

有个3V供电的电路,有个控制脚低电平有效(0V可触发,1.5V和3V不可触发),但这个控制脚接一个100K的电阻到地,就变成了高电平有效(0V不可触发,1.5V可触发,3V也可触发),为什么会这样呢?

2009-07-20 16:05:29

数字电路为什么是低电平有效的多

数字电路为什么是低电平有效的多设计时常常是低电平有效,本文讲解一下内因,大家有兴趣的看看。 事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰

2016-10-03 09:45:27

数字电路及其应用

|CB样板贴片,麦1斯1艾1姆1科1技全国1首家P|CB样板打板 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用

2013-09-05 11:12:39

数字电路及其应用

。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。注意:有关产品手册中常

2012-12-03 21:37:43

数字电路及其应用

一连串的脉冲(电压),这就是数字信号。人们把用来传输、控制或变换数字信号的电子电路称为数字电路。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1

2009-04-07 09:39:18

数字电路和模拟电路的隔离探讨

话说,数字电路和模拟电路在同一个电路板上最好要隔离,防止相互干扰,为什么会有干扰呢?小弟不才,就此做一个简单的说明,希望有高手大牛来赐教!简单来说:数字电路是离散量,说白了就只有1和0,也就是高低电平

2013-04-19 19:28:25

数字电路的应用介绍

。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。注意:有关

2018-08-28 15:36:27

电平特性数字电路中有哪几种电平

认识单片机在一片集成电路芯片上集成微处理器CPU、存储器、I/O接口电路,从而构成了单芯片微型计算机,即单片机。电平特性数字电路中只有两种电平:高电平和低电平高电平:5V或者3.3V,取决单片机

2021-07-21 07:45:56

FPGA数字电路设计经验分享

是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。FPGA数字电路设计经验分享[hide][/hide]

2012-03-05 16:33:30

NE555触摸电路中人体杂波信号是高电平还是低电平?

NE555电路中,触摸2脚低电平有效有动作,触摸6脚高电平有效有动作,触摸电路中人体杂波信号是高电平还是低电平?

2024-01-10 13:03:22

PWM的输入是高电平有效还是低电平有效的?

请问High-Voltage Motor Control + PFC Kit v2.0的IPM的输入极性,PWM的输入是高电平有效还是低电平有效的?

2020-06-10 11:04:26

RTC中断输出(低电平有效)

本帖最后由 张艳陈媛 于 2017-6-2 19:22 编辑

这张图是RTC中断输出,我查过芯片,是开漏低电平有效,请问下面的NMOS和上面的PMOS是如何工作的?希望详细点!谢啦

2017-06-02 19:19:16

为什么单片机有些管脚要设计成低电平有效?

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过它

2011-08-30 09:36:11

为什么单片机有些管脚要设计成低电平有效?

就是通过它这个开关的通断来实现的。有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为了防止电路失控的情况下仍然是有效电平,那么当然是低电平有效才更“保险”了。结构上,象OC电路那样

2011-11-07 10:21:06

为什么单片机管脚设计成低电平才有效

为什么单片机管脚设计成低电平才有效它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象:我们有的同学可能已经

2017-09-18 13:17:18

什么是数字电路

本帖最后由 gk320830 于 2015-3-7 06:25 编辑

数字电路 现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二值

2009-04-06 23:45:00

你都知道数字电路有哪几种状态吗

数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定上拉就是将不确定的信号通过一个电阻嵌位在高电平

2021-11-03 06:11:45

单片机的管脚为什么要设计成低电平电路呢

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过...

2022-01-14 07:17:56

如何将开关的开/断状态转变成Arduino能够读取的高/低电平

在数字电路中开关(switch)是一种基本的输入形式,它的作用是保持电路的连接或者断开。Arduino从数字I/O管脚上只能读出高电平(5V)或者低电平(0V),因此我们首先面临到的一个问题就是

2022-01-17 08:35:42

如何看懂数字电路图?

数字电路是实现一定逻辑功能的电路,称为逻辑电路,又称为开关电路。这种电路中的晶体管一般都工作在开关状态。数字电路可以由分立元件构成(如反相器、自激多谐振荡器等),但现在绝大多数是由集成电路构成(如与门电路

2021-02-25 07:58:41

我想学数字电路设计

大家好,我是电子爱好者新手,现在想学点数字电路设计。刚把数字电路这么课程学完。我想学电路设计,不知道如何下手。比如FPGA什么的,这些都怎么开始学习啊。请知情者指点下。谢谢

2013-08-02 08:17:31

模拟电路与数字电路的基础知识详解

电子电路是单片机硬件部分的基础知识,电子电路分为模拟电路和数字电路。单片机是使用数字电路,但ADC功能涉及模拟电路。1、模拟电路与数字电路2、欧姆定律3、电源正极和负极4、TTL电平和CMOS电平

2022-01-25 07:15:00

模拟电路和数字电路接地要点

干扰导致错误动作,严重的会导 致机器毁损!!! 主要因为数字电路、模拟电路的工作电平一般为 3.3-15.5V(15.5V一般用于 232接口通讯 的最高电平);而通常电源回路的电平一般在市电范围

2016-07-23 22:54:41

模拟电路和数字电路接地要点

机器毁损!!!主要因为数字电路、模拟电路的工作电平一般为 3.3-15.5V(15.5V一般用于232接口通讯的最高电平);而通常电源回路的电平一般在市电范围(AC220V±10%),远远大于数字电路

2017-08-29 09:45:39

直接输出模式, CMOS 输出低电平有效

看TTP224B手册的时候看到这样一句话。直接输出模式, CMOS 输出低电平有效到底是指低电平时才能有效输出,还是指输出端输出低电平?

2020-10-18 15:39:26

数字电路及其应用

数字电路及其应用

编者的话 当今时代,数字电路已广泛地应用于各个领域。本报将在“电路与制作”栏里,刊登系列文章介绍数字电路的基本知识和应用实例。

2009-04-07 09:38:37 3341

3341

3341

3341低电平和高电平的区别

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平也不同。在TTL门电路中,把大于3.5伏的电压规定为逻辑高电平,用数字1表示

2017-11-14 10:37:26 291205

291205

291205

291205

详解TTL和CMOS电平

TTL电平最常用于有关电专业,如:电路、数字电路、微机原理与接口技术、单片机等课程中都有所涉及。在数字电路中只有两种电平(高和低)高电平+5V、低电平0V.同样运用比较广泛的还有CMOS电平、232

2017-11-15 14:34:49 6

6

6

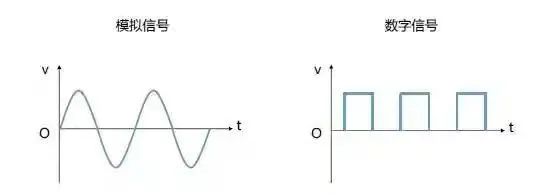

6什么是模拟电路 什么是数字电路

模拟信号和数字信号的特点不同,处理这两种信号的方法和电路也不同。一般地, 电子电路可分为模拟电路和数字电路两大类。 1. 模拟电路 处理模拟信号的电子电路称为模拟电路。模拟电路研究

2018-10-16 10:25:09 97754

97754

97754

97754PCB混合信号电路板应该如何设计详细设计准则资料说明

模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的“真”或“假”。在数字电路的高电平和低电平之间,存在“灰色

2019-02-03 10:13:00 3119

3119

3119

3119简析模拟电路与数字电路

模拟电路与数字电路的关系,有说所有电路都是模拟电路,数字电路只是模拟电路的一部分的;有说模拟电路和数字电路各成系统,井水不犯河水的;有说线性的就是模拟电路,非线性的就是数字电路,不一而足。

2019-07-03 17:35:50 9233

9233

9233

9233混合信号电路板应该如何设计有哪些准则

模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的“真”或“假”。在数字电路的高电平和低电平之间,存在“灰色

2020-01-18 17:24:00 2530

2530

2530

2530逻辑芯片输入的低电平有效和高电平有效

最近在看逻辑电路,刚刚看到编码器,发现二进制编码器是高电平输入有效,而优先编码器是低电平输入有效,于是就在想,同样都是编码器,为什么不去统一设置一个标准呢?上网搜了搜,有这么几条答案,汇集如下

2020-05-18 10:47:13 10085

10085

10085

10085数字电路和模拟电路怎么区分

数字电路就是开关电路;器件工作状态:不是导通就是截止,一般信号电平只管高、低。高为“1”,低电平为“0”;工作状态是脉冲电量。

2020-08-30 09:40:25 19403

19403

19403

19403

一文带你了解数字电路和模拟电路的区别

。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二进值数据的数字电路。 数字电路的特点 电路结构简单,稳定可靠。数字电路只要能区分高电平和低电平即可, 对元件的精度要求不高,因此有利于实现数字电路集成化。 数字信号

2022-12-05 17:36:59 7096

7096

7096

7096如何区分数字电路和模拟电路的电路图

数字电路就是开关电路;器件工作状态:不是导通就是截止,一般信号电平只管高、低。高为“1”,低电平为“0”;工作状态是脉冲电量。而模拟电路是放大电路,丝毫变化都要计较、考虑;是连续变化的电量。仅从

2020-12-15 14:52:00 13

13

13

13设计方案5-低电平、高精度、双极输入差分至单端信号转换24位A/D单电源差动至单端转换电路放大低电平双极信号并保持LTC2400的高电平

设计方案5-低电平、高精度、双极输入差分至单端信号转换24位A/D单电源差动至单端转换电路放大低电平双极信号并保持LTC2400的高电平

2021-05-26 09:28:01 14

14

14

14模电数电&TTL电平&上下拉电阻

电子电路是单片机硬件部分的基础知识,电子电路分为模拟电路和数字电路。单片机是使用数字电路,但ADC功能涉及模拟电路。1、模拟电路与数字电路2、欧姆定律3、电源正极和负极4、TTL电平和CMOS电平

2021-12-01 10:06:07 11

11

11

11为什么单片机管脚设计成低电平才有效

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过...

2022-01-14 14:44:43 2

2

2

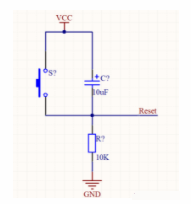

2高电平、低电平复位电路

单片机最小系统,即单片机能正常工作的最简单的电路。复位电路是单片机最小系统的组成部分之一。对于不同单片机,复位方式有高电平复位和低电平复位,从而相对应地就有两种复位电路,高电平和低电平复位电路,本文

2022-01-17 12:38:52 13

13

13

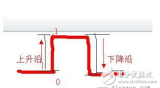

13数字电路的上升沿、下降沿,你到底搞懂几分?

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平也不同。

2022-02-09 09:50:54 1

1

1

1高低电平触发的上升沿触发和下降沿触发区别

低电平触发中断顾名思义,就是检测到引脚为低电平就触发,从而进入中断函数中处理这个中断,并且在高或低电平保持的时间内持续触发,假设是低电平触发,只要引脚为低电平时间内中断一直有效,那么就会一直进入中断,直到电平变化为高电平。

2022-04-27 15:00:56 16709

16709

16709

16709数字电路中最基本的门电路

门电路是数字电路中最基本的逻辑单元。它可以使输出信号与输入信号之间产生一定的逻辑关系。在数字电路中,信号大都是用电位(电平)高低两种状态表示,利用门电路的逻辑关系可以实现对信号的转换。

2022-09-16 15:04:44 2446

2446

2446

2446使用光耦给高低电平转化

在数字电子技术中我们会经常进行高低电平之间的转化,比如说一个模块在接收到信号的时候输出高电平,而另一个元件是低电平触发,如果这两个元器件能够很好配合使用的话,这就必须需要进行电平之间的转化,那应该怎么转化呢?我们今天使用光耦给大家提供一个高低电平之间的转化。

2022-12-12 09:12:12 6347

6347

6347

6347数字电路和模拟电路的区别

处理的信号不同 模拟电路处理的是时间和幅度连续变化的模拟信号,而数字电路处理的是用“0”和“1”两个基本数字符号表示的离散信号。在数字电路中,通常低电平用数字“0”来表示,高电平用数字“1”来表示。

2023-02-13 09:54:10 5905

5905

5905

5905为什么说数字电路无法取代模拟电路

,具有高精度和高保真度的特点。在很多领域中,数字电路的应用已经越来越广泛,然而数字电路无法取代模拟电路。 数字电路都是由数字信号构成,采用的是二进制数码的形式来表示电信号,有效抵御了电路噪声、干扰和衰减等因素

2023-08-27 15:37:05 1137

1137

1137

1137什么是逻辑电平?如何实现电平转换?(原理讲解+电路图)

逻辑电平是数字电子系统中的关键概念之一。它决定了信号被认定为高电平还是低电平,并进一步影响着数字电路的正确操作。逻辑电平是用来表示数字信号状态的电压水平。在数字电子系统中,常用的逻辑电平有高电平

2023-11-24 08:20:20 1681

1681

1681

1681

什么是时钟信号?数字电路的时钟信号是怎么产生呢?

什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号

2024-01-25 15:40:52 909

909

909

909数字电路中的逻辑门电路分类

数字电路中的逻辑门电路分类 数字电路是计算机系统中的重要组成部分,它们由逻辑门电路构成。逻辑门电路是一种基本的数字电路,用于根据输入的逻辑状态生成输出。逻辑门电路可分为多个类别,包括与门、或门、非门

2024-02-04 09:14:16 504

504

504

504cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平

)是常用的数字电路家族,两者都有自己的特点和应用范围。在介绍如何转换CMOS电平和TTL电平之前,我们先来了解一下它们的定义和特点。 CMOS电平: CMOS电平是一种用于数字电路传输的电压标准。常见

2024-02-22 11:10:52 341

341

341

341 电子发烧友App

电子发烧友App

评论