交织结构的优势可惠及多个细分市场。交织型ADC最大好处是增加了带宽,因为ADC的奈奎斯特带宽更宽了。同样,我们举两个100 MSPS ADC交织以实现200 MSPS采样速率的例子。

2020-06-09 09:54:49 6440

6440

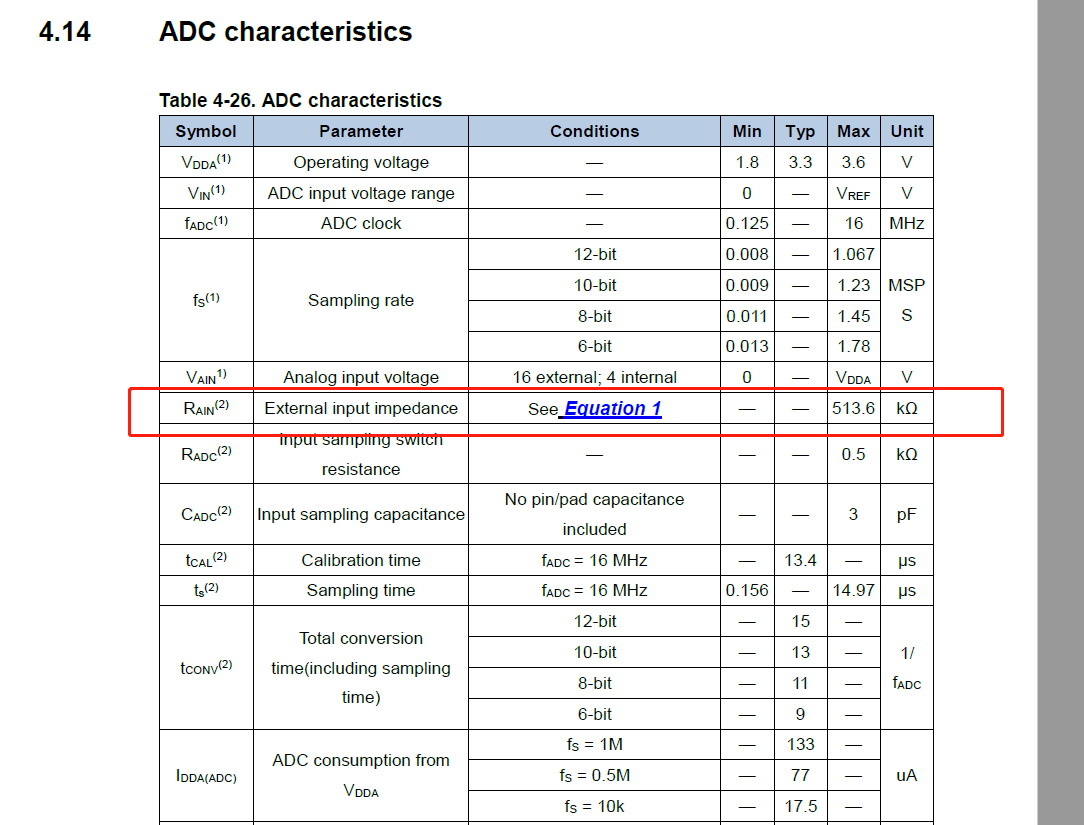

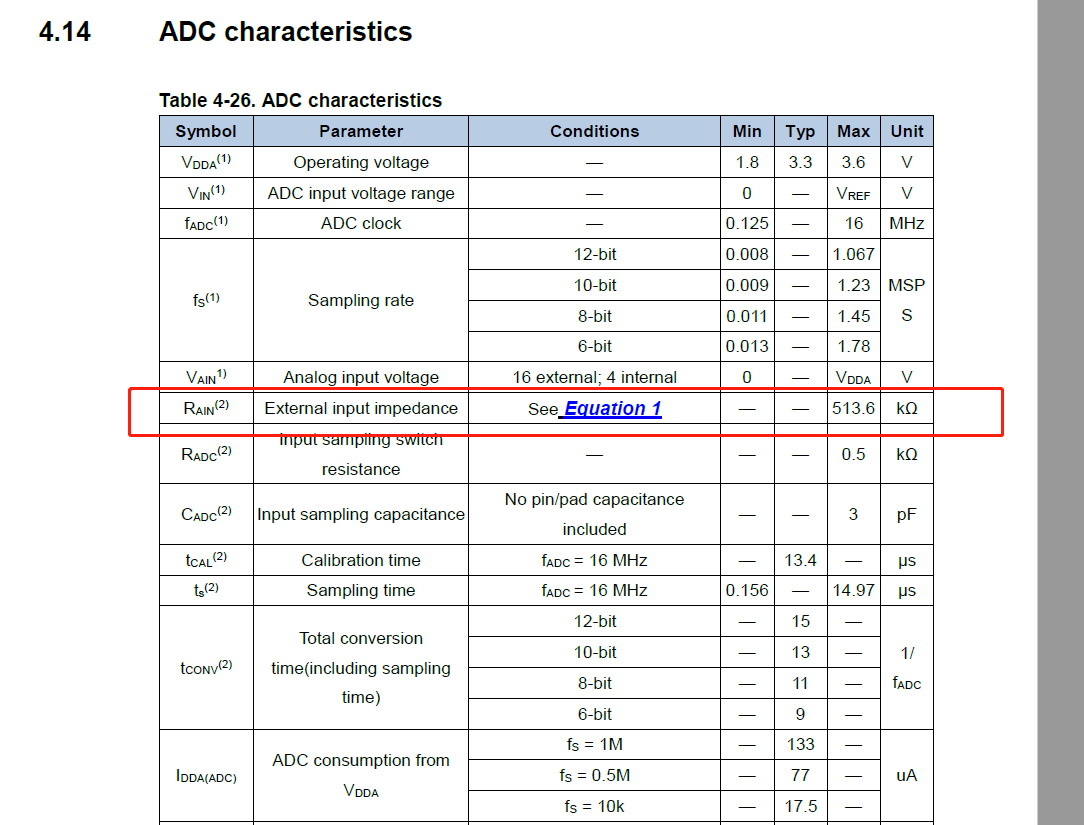

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

2012-03-22 10:45:30 5849

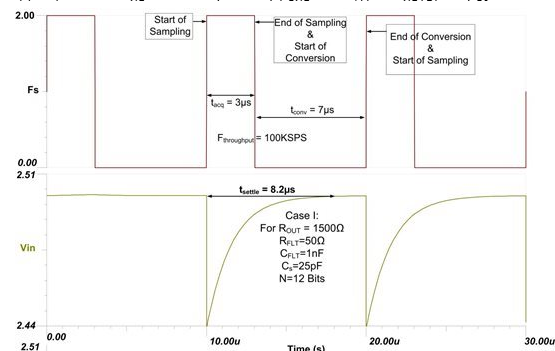

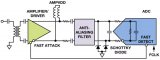

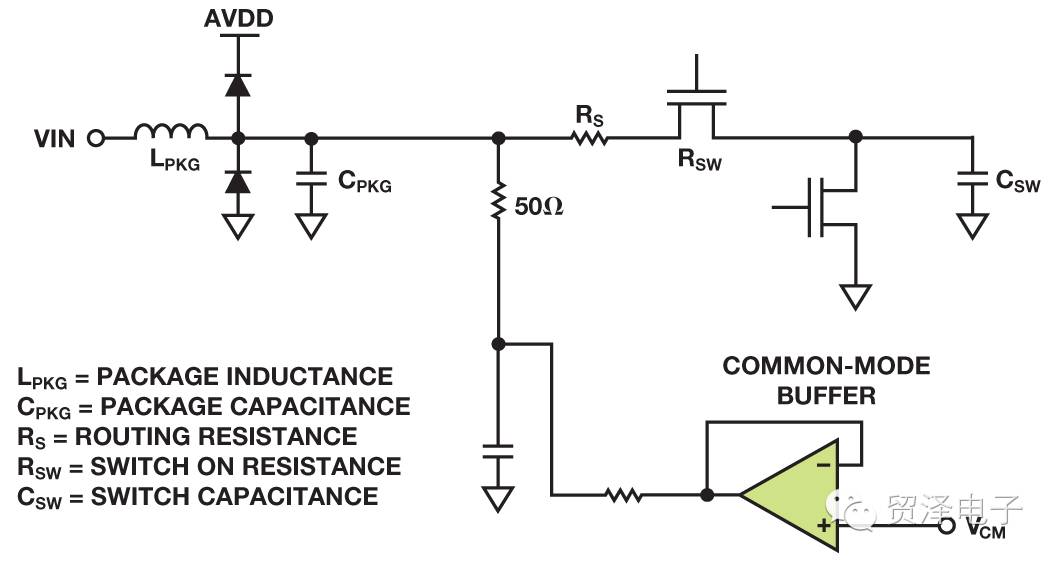

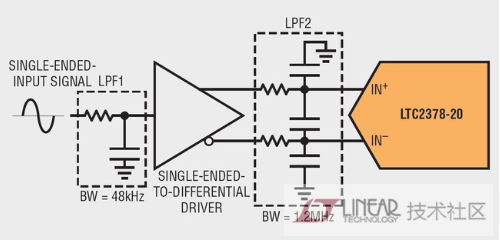

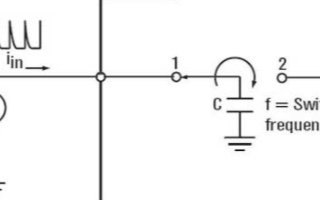

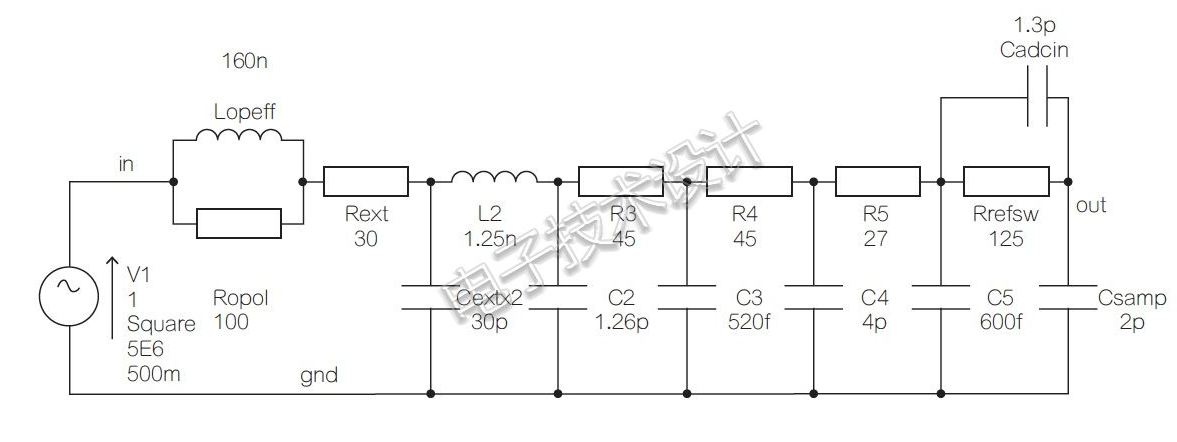

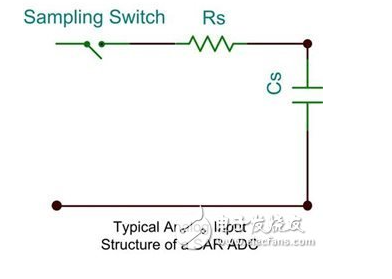

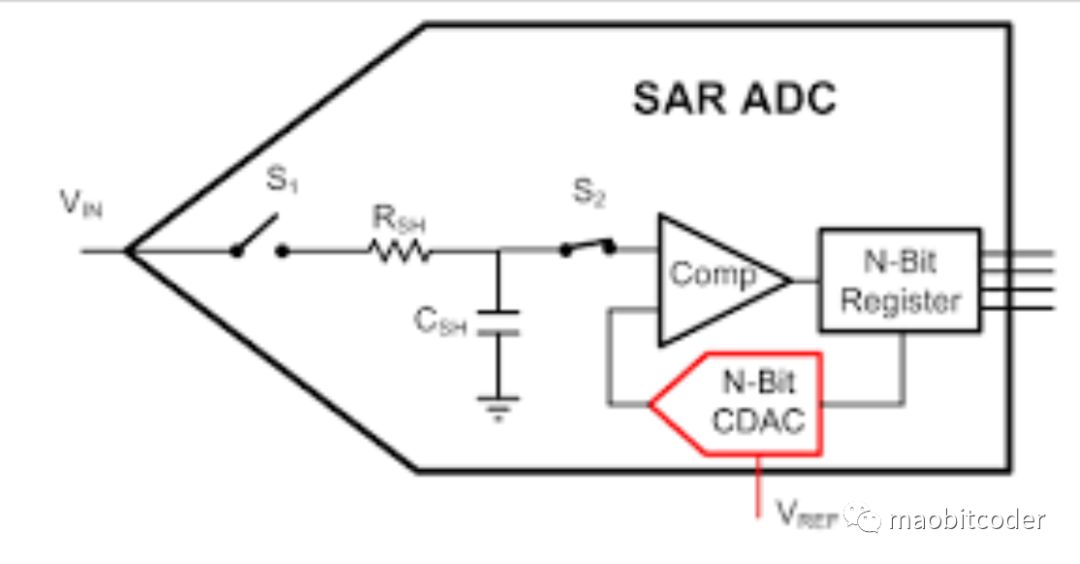

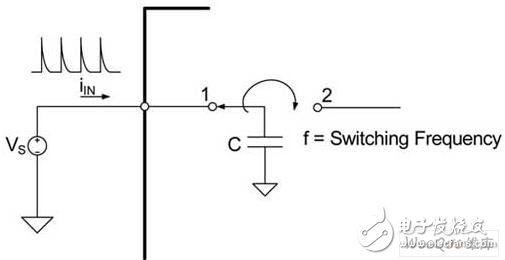

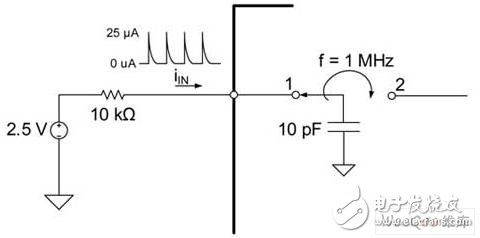

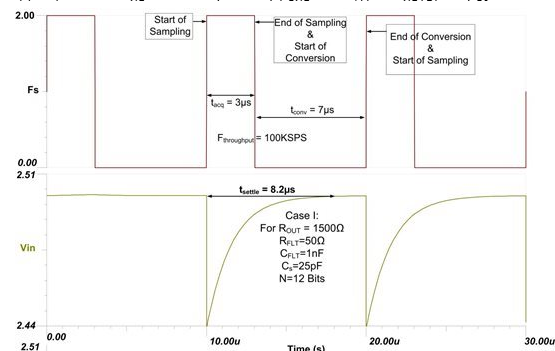

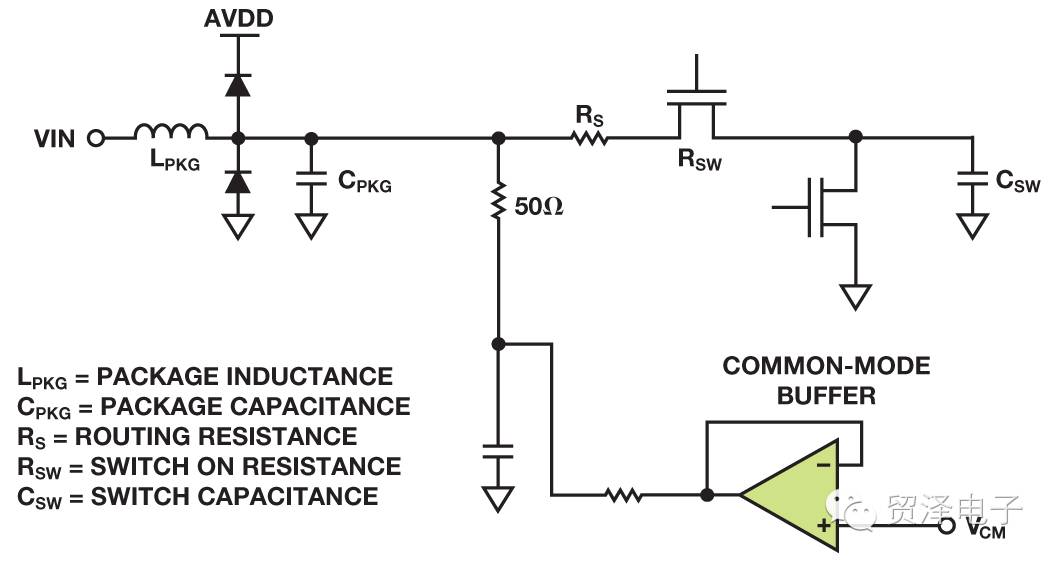

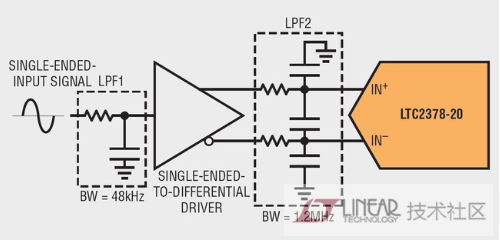

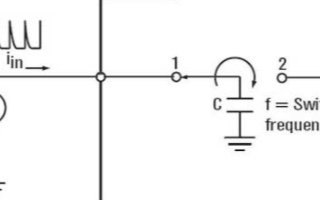

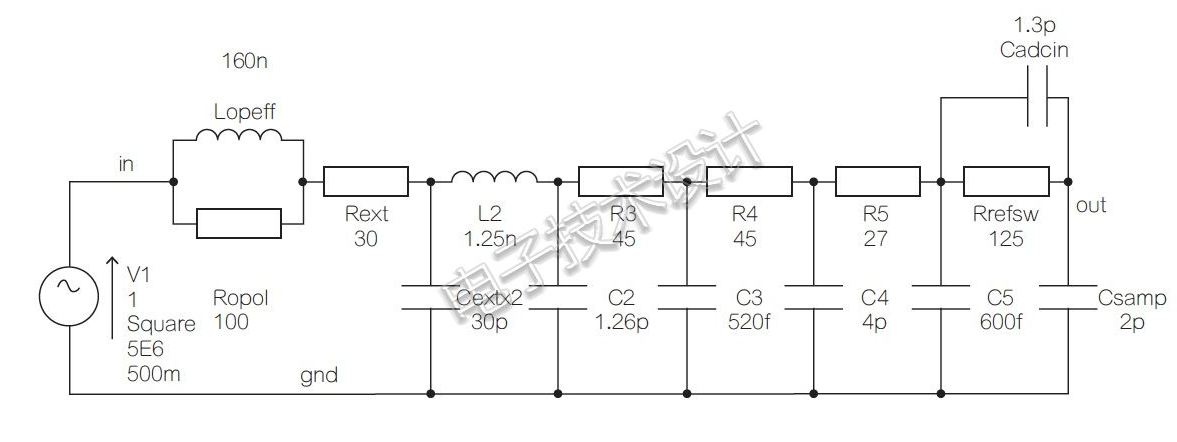

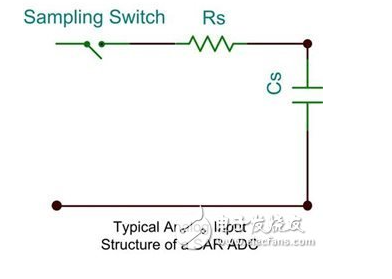

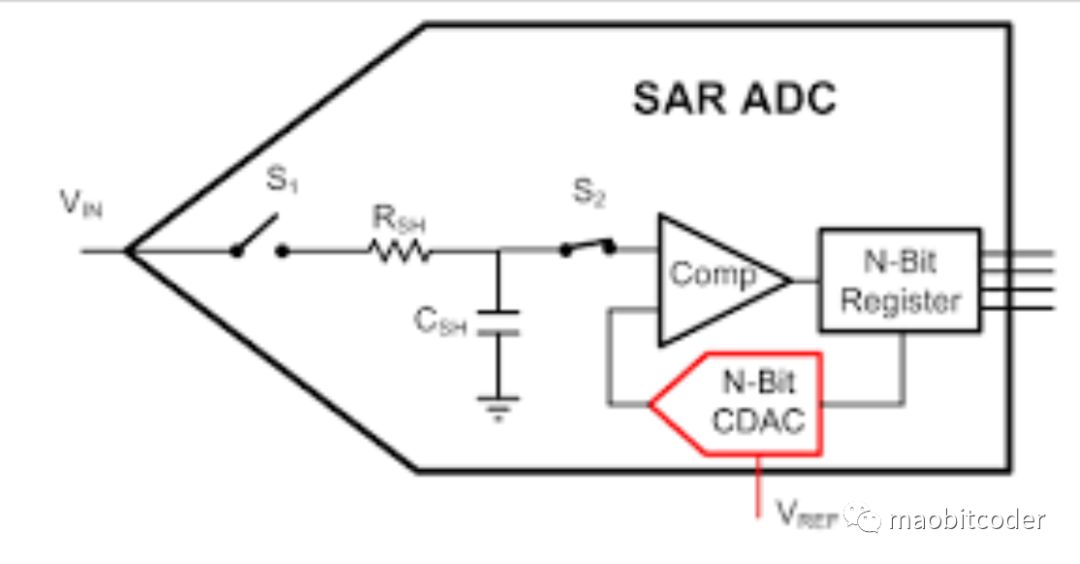

5849 ADC的采样过程和模拟输入结构来了解驱动器的要求。 SAR ADC的模拟输入是一个采样开关、一个电阻器和采样电容器的组合。图1显示针对一个SAR ADC的模拟输入结构。 图1 采样开关在一定的时间周期tACQ(采集时间)内关闭以获得输入信号,并在转换过程期间打开。

2018-04-16 09:23:31 5899

5899

A-to-D的转换期间内,输入信号变化超过了1 LSB ,则输出数字码会出现较大的误差,多数ADC或多或少都会遇到这样的问题。下面通过一个简单计算来说明非采样ADC的输入频率限制。 图1 非采样ADC(编码器)的输入频率限制 因此,如果ADC的分辨率N=12且在转换时

2021-04-28 11:02:50 24116

24116

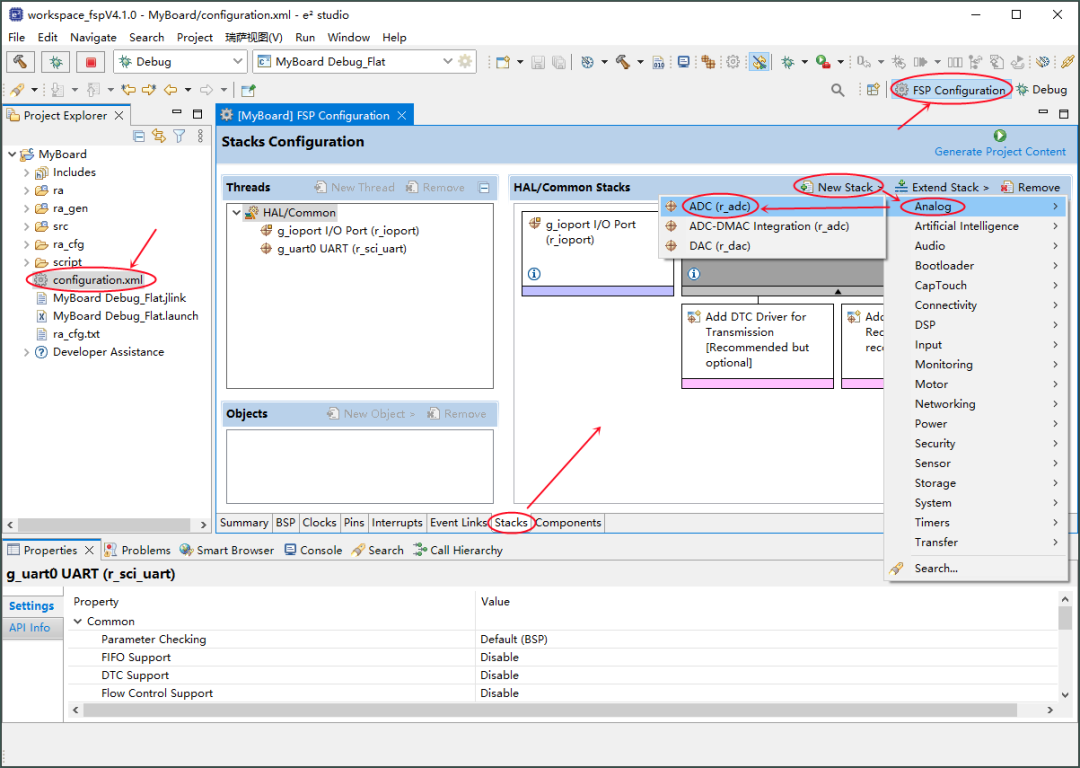

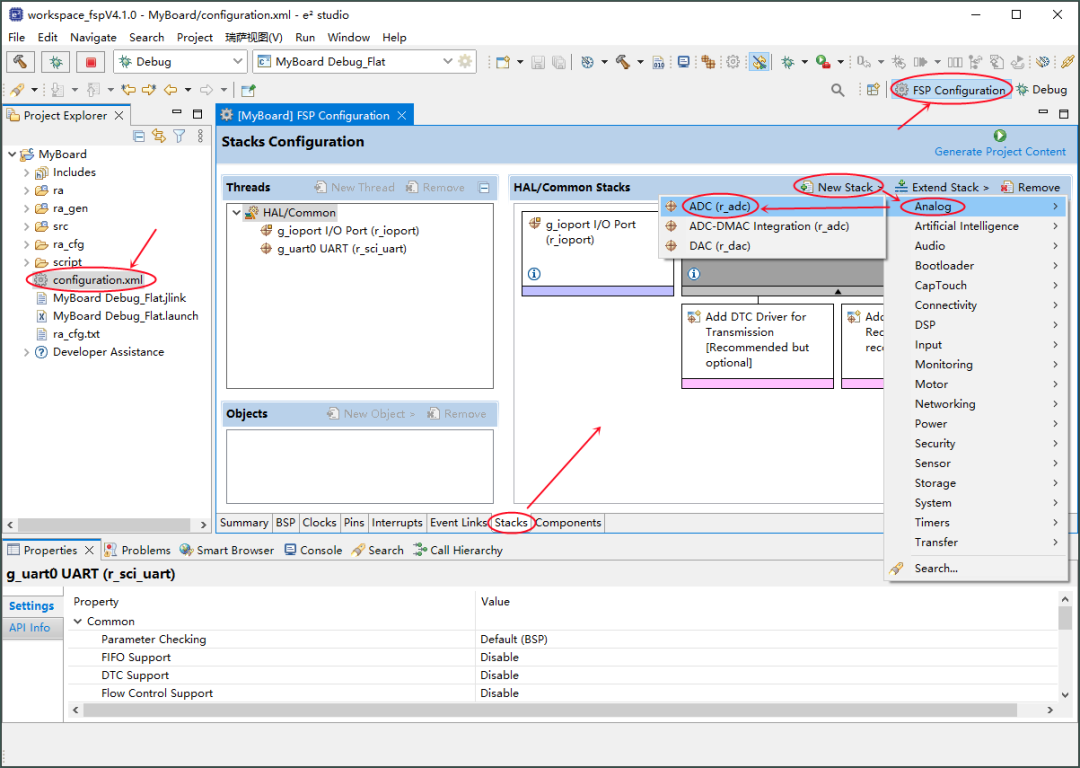

在RA6M4处理器的ADC里,有两路ADC可以分别采样当前的CPU内部温度和参考电压值。

2022-12-19 09:23:20 1498

1498

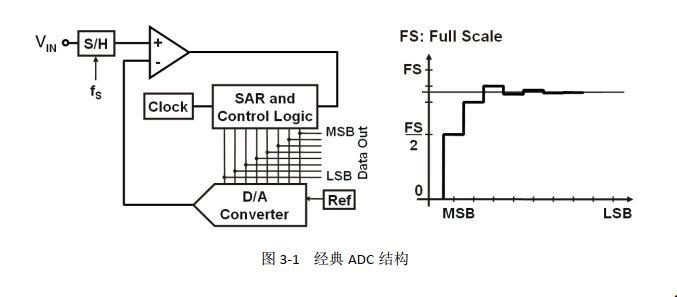

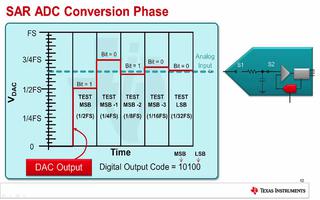

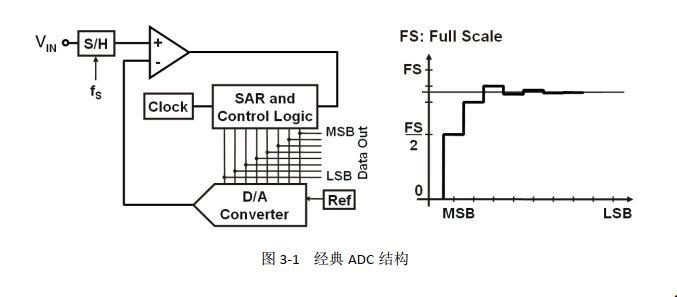

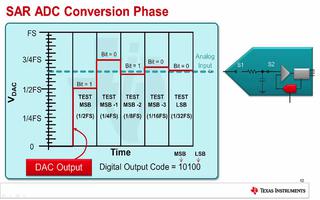

SAR型ADC,又叫逐渐逼近型ADC,属于瞬死值转换型-转换对象是模拟信号在采样时刻或前几个时刻抽样值,即时输出结果。

2023-02-07 16:52:03 2458

2458

昨天有小伙伴在课程群里问关于ADC的最小输入电平怎么算,唉,又激起了我的痛点。

2024-01-05 18:18:46 813

813

2808中epwm启动adc采样,现在希望在一次epwm中断中(采样读值在epwm中断中,不对adc设置中断函数),要求对某一通道连续采样四次,而不是用四个通道,请问有没有可能实现?

2020-05-12 09:33:34

我用的是28377s,我打算用fpu里的关于fft例程,想从外部取样信号计算,但是adc中断采样频率一直有问题,我查到对应的头文件中如图,ADC_SAMPLING_FREQ 应该就是调用adc中断的频率吧,但是无论我怎么改,好像采样出来都一样,也就是说这里改并没有效,为什么呢

2018-09-26 17:35:44

在使用STM32F030C8 adc进行采集时,启动采样时在输入信号会出现一个很大的过冲信号,尝试过单通道单次采样,单通道重复采样,均出现以上问题,下面是具体的采集波形,硬件电路信号由运放输出直接

2018-09-04 15:35:57

我是STM32初学者,无奈公司要一个月内改一个老的项目!以下是程序中关于有关ADC的配置,右边的注释都是我添加的(参照的固件库使用手册):void Set_System(void

2020-08-28 08:00:16

举个例子;假设ADC现在要转换的输入信号频率为50MHz-70MHz的,该信号带宽是20M ,那我ADC选择时是选用40M采样率的还是采用140M的,之前有看到一篇文档http

2016-04-27 13:04:10

本人在使用ADC时想使用多通道模式,所以便在CUBEMX上将十九个通道全部打开(包括三个内部通道),生成代码以后详细看了一下结构体的配置发现有几个疑惑,

1.ADC通道分为规则通道和注入通道,那么

2023-08-04 06:01:10

关于STM32ADC多通道连续扫描采样,DMA循环传输。通过ADC通道对两路直流信号和两路3.2v,1KHz的正弦信号进行采样,当设置每个通道的采样点数为30时,采样时间任意设置,采样输出的30个值

2015-08-19 19:48:43

1.关于STM32 ADC的工作频率STM32F1系列单片机的ADC都是12位的ADC,通过过采样原理也可以实现14位精度采样,这样可以达到更高的精度。STM32 ADC的时钟不要超过14MHz

2021-08-04 07:34:59

ADI关于ADC基本结构的经典文章合集ADC Architectures I The Flash Converter (pdf, 1544 kB) ADC

2010-07-08 22:15:43

1);

adc_data_convert_low_latency(kk2);

这个是SDK的 程序

上面程序是采样IN0 和IN1的差分输入电压,IN1 -3.3V,IN0-1.5V,我想采集IN0的1.5V的电压,这个P N输入该怎么设置啊,我把N输入设置为CLOSE采样的电压不对,

求解答,谢谢,

2023-05-05 15:26:52

我想请教一下大家,关于RTOS中的ADC采样率是怎么设置的,或者该在哪里去查看adc的这个采样率?

2023-04-07 16:08:11

SPI的几种模式不通用么

2023-10-10 08:15:16

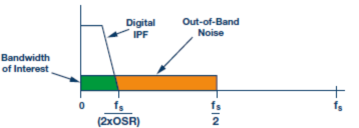

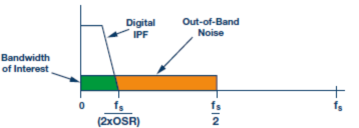

和反馈被粗略量化,常常只有一比特表示高电平或低电平的输出。ADC的模拟系统实现了这种基本结构,量化器就是完成采样的模块。如果存在保证环路稳定的条件,那么输出就是输入的粗略表示。数字滤波器获得该粗略输出

2017-04-21 10:50:35

。所有的通道均能以高达 200 kSPS 的速率进行采样,同时输入端箝位保护电路可以承受最高达±16.5V的电压。 传统的逐次逼近(SAR)型ADC,由于其采样电容的设计,模拟输入前端一般需要

2018-11-01 09:25:42

的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在高速低功耗的ADC应用中也成为一个比较常用的结构。 作为流水线ADC前端的采样保持

2018-10-08 15:47:53

。交织型结构可以弥补这一技术差距。图3.两个交织型ADC——奈奎斯特区增加采样速率能够为这些应用提供更多的带宽,而且频率规划更轻松,还能降低通常在ADC输入端使用抗混叠滤波器时带来的复杂性和成本。面对

2020-08-05 09:54:42

较小的晶体管尺寸支持的最大电压也较低。因此,在数据手册中规定的出于可靠性原因而不应超出的绝对最大电压,将当前主流的射频采样ADC与之前的老器件相比,可以发现这个电压值是变小的。 在使用ADC对输入信号

2018-09-21 14:38:04

通用模拟输入是工厂自动化普遍使用的单元电路,灵活测量模拟电压/电流信号以及RTD、TC成为组装过程中不可或缺的功能。工业4.0在工业结构、分布试管理、智能化控制方面带来了巨大变化,其高度 可配置性

2019-03-25 21:47:18

通用模拟输入是工厂自动化普遍使用的单元电路,灵活测量模拟电压/电流信号以及RTD、TC成为组装过程中不可或缺的功能。工业4.0在工业结构、分布试管理、智能化控制方面带来了巨大变化,其高度 可配置性

2022-03-16 11:23:20

如何使用Cypress PSoC5中DMA实现多路输入切换以及ADC采样保存的自动控制,有效减少对CPU时间占用?

2021-04-07 06:39:20

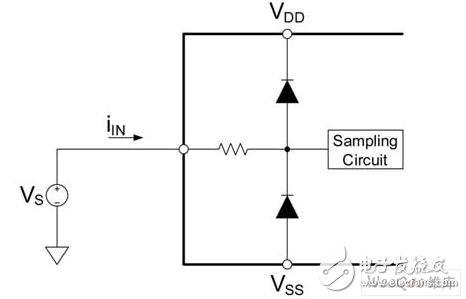

a TVS DiodeADC inputs 有几种方式可以保护ADC输入不受高压影响。部分ADC(特别是射频采样ADC)具有内置电路,可以检测输入电压并在超过设定阈值时进行上报。如数据手册中所述,该

2018-11-01 11:25:01

你好,我想用ADC和我的PSoC5来采样16个输入。我正在寻找最有效和最快的方式来做到这一点。我目前的尝试不太好,我尝试使用16个输入的AdcSARSy-Seq块。我得到一些模糊相关的值,但是性能

2019-09-20 11:02:11

和大家一起共同来探讨 ADC在应用中可能会碰到的问题。案例分享日前,有客户公司在用某ADC做AD转换的时候,碰到这样一个问题,客户传感器型号PT100,在采集信号时,输入采样端的波形如下:我们首先假定这是

2021-08-13 07:00:00

各位,最近看了一下拉扎维写的《射频微电子》这本书的第四章,里面谈到了几种接收机的结构。但不管哪种结构,都少不了ADC。在网上查了一下,大部分都采用了连续型的sigma delta adc,没有采用

2021-06-25 06:55:27

在应用单片机进行ADC项目设计的时候,结合以前弄的数据采集卡,这里有几个关于ADC采样的几个参数的问题,ADC的采样率,采样数,单次采样,连续采样等,这里想请教高手给指点一下,理解的更加清楚

2023-11-09 07:50:43

Hi all:

我们使用psoc6 的saradc来采样数据, ADC的频率为 1M sps,单通道 12 bit ,参考电压 1.2 v,配置如下图:

现在的问题是: ADC输入信号电压如果

2024-02-02 11:34:20

电流采样的几种方式1.直接用采样电阻,ADC测量电阻上面的压降,不经过运放等处理电路2.用采样电阻,ADC测量电阻上面的压降,经过运放等处理电路,比如差分放大、跟随器等3.电表、智能断路器等电力设备

2022-06-16 17:46:09

等效时间采样中应用的ADC,应该注意哪些问题呢?一般采样速率有何限制?对于ADC的模拟输入带宽呢?

2023-12-25 06:42:31

您好:我在选型高速ADC时,发现datasheet上标注了采样率范围,给出最小值典型值和最大值。比如AD9208,输入时钟最高6GHz,采样率三值分别为2500,3000,3100MSPS。请问

2018-07-30 08:53:53

采样保持电路的结构分为哪几种?如何去设计运算放大器?描述自举开关是如何实现的?怎样对运算放大器进行仿真验证?

2021-04-20 06:59:17

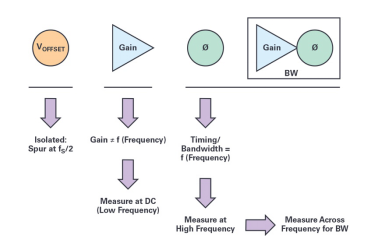

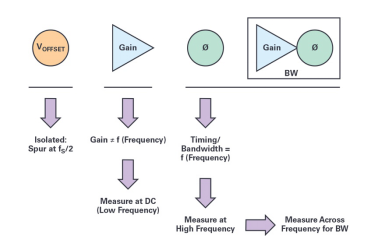

通用的输入采样结构有哪几种?每种输入采样结构对系统其它部分有什么影响?

2021-04-22 06:20:56

等效时间采样中应用的ADC,应该注意哪些问题呢?一般采样速率有何限制?对于ADC的模拟输入带宽呢?

2018-11-26 09:46:09

首先声明,本人新手,在学习中遇到了关于ADC12中从MEMORY读取采样数据的问题。不知道ADC12MEMORY的组成方式和它的工作方式还有读取方式,查了几本书,上面都没有,就想来求教了,望各位大神能给予帮助,让我能明白!!

2013-03-01 20:40:26

阻抗的虚部或容性部分(红线)也是如此,低频时的容性负载相当高,高频时逐渐变小到2 pF。这使得输入结构的设计更加困难,特别是当频率高于100 MHz时。

ADC如何能采样一个坏信号(如图3所示)并实现良好

2023-12-18 07:42:00

以上时则滚降到2 kΩ。输入阻抗的虚部或容性部分(红线)也是如此,低频时的容性负载相当高,高频时逐渐变小到2 pF。这使得输入结构的设计更加困难,特别是当频率高于100 MHz时。ADC如何能采样一个坏

2018-10-18 11:23:57

时则滚降到2 kΩ。输入阻抗的虚部或容性部分(红线)也是如此,低频时的容性负载相当高,高频时逐渐变小到2 pF。这使得输入结构的设计更加困难,特别是当频率高于100 MHz时。 ADC如何能采样一个坏

2018-09-17 15:38:24

;* 输入阻抗随时间变化(采样时钟-采样保持器);* 来自采样电容的电荷注入反射回输入网络。 无缓冲ADC 开关电容ADC(见图1)就是一类无缓冲ADC。无缓冲ADC的功耗通常远低于缓冲ADC,因为前者

2018-01-23 16:01:44

设置高速ADC的共模输入电压范围(中文)

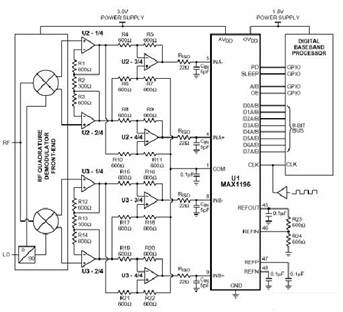

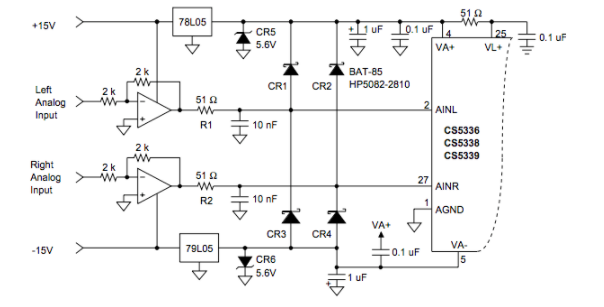

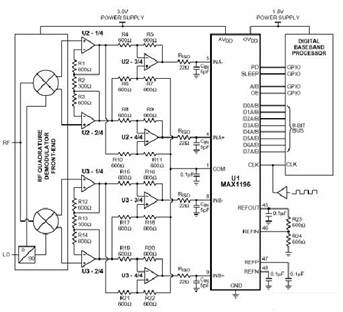

对于包含基带采样、高速ADC的通信接收机,输入共模电压范围(VCM)非常重要。特别是对于单电源供

2010-03-30 17:59:39 3883

3883

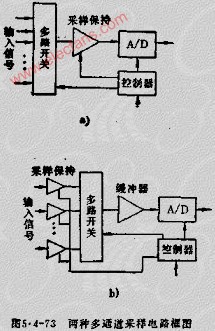

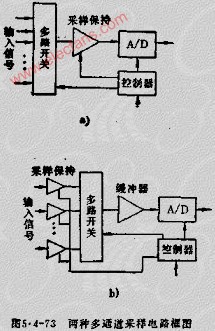

多通道采样电路结构

由于输入信号的数目,输入信号的电平和采样速度快慢的不同,多通道采样电路的结构不

2010-05-23 18:54:51 958

958

另外,如果 信号 调理电路 和 传感器 之间 的ADC 时,该 电路可 影响 ADC的输入 结构的选择。 有些 ADC可 配置的, 允许 选择 之间 单 端或 伪差分 输入结构 ( 器MAX186 , MAX147 ),而其他 允许 在单 端或 全差分 选择( MAX1298 , MAX1286 )。

2011-02-12 17:27:46 263

263 本内容提供了2812片内ADC采样时间计算。1)序列采样模式(SMODE = 0)[attach]12497[/attach]

2011-09-05 11:39:36 3094

3094 MAX11043是4路单端或差分、16位同时采样ADC。MAX11043每通道包含通用的滤波器模块和可编程增益放大器(PGA)。

2012-12-06 14:31:19 2233

2233 任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2017-11-22 17:46:05 1009

1009

。 图1采样示波器结构框图 采样示波器由两部分组成,主机和插拔模块。主机包括ADC转换器,数据存储器,触发器和顺序延时产生器。ADC转换器的指标一般是转换位数14bits,转换速率200KSa/s。这么低的转换速率为何能够测量高速的光或电信号(比如1

2017-11-23 05:44:01 947

947

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。

2018-05-20 09:39:00 7510

7510

使用高分辨率ADC(模数转换器)设计电路需要注意许多细节。经常忽略的一个细节是ADC的输入阻抗。当源的输出阻抗变高(例如,当由桥或RTD驱动时),这变得很重要。这个应用报告解释了输入采样是如何工作的,以及如何在ADS1216、ADS1217和ADS1218系列ADC中计算输入阻抗。

2018-05-25 14:51:47 25

25 任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2018-06-04 10:50:00 1894

1894

主要ADC采样技术简介SAR ADC原理介绍

2019-01-30 11:00:10 11404

11404

通用模拟输入是工厂自动化普遍使用的单元电路,灵活测量模拟电压/电流信号以及RTD、TC成为组装过程中不可或缺的功能。工业4.0在工业结构、分布试管理、智能化控制方面带来了巨大变化,其高度 可配

2022-03-23 21:00:00 827

827 这颗射频采样ADC经过测试可输入高达2 GHz频率的信号,因此选用RF肖特基二极管(RB851Y)。表2显示RB851Y的关键参数;表明该器件适合该应用。测试结果显示二极管防止了ADC输入电压超过其3.2 V的绝对最大电压(相对于AGND)。

2019-08-23 11:41:47 4488

4488

由于ADC的分辨率和采样率继续上升,模拟输入的驱动器电路(而不是ADC本身)已经越来越成为确定总体电路精度的限制因素。

2019-08-07 17:23:14 7017

7017

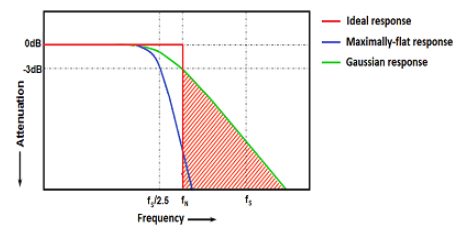

,Δ-Σ型ADC通常不适合用于输入通道间的快速切换(多路复用)。 如图1所示,Δ-Σ型ADC基本过采样调制器对量化噪声进行整形,使其大部分出现在目标带宽以外,从而增加低频下的整体动态范围。 然后,数字低通滤波器(LPF)过滤目标带宽以外的噪声,抽取器降低输出数据速率,使其回落至奈奎斯特速率。

2019-09-14 10:05:00 3426

3426

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样 ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2020-09-29 10:44:00 0

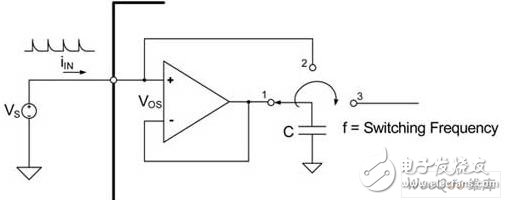

0 今天的模拟系统设计工程师面临许多设计挑战,他们不仅需要选择正确的IC元件,还必须准确地预测这些元件在系统内的相互影响。从这点来看,模数转换器的设计是一个巨大挑战,因为它具有必须在系统级加以考虑的各种不同的输入采样结构。本文将探讨几种通用的输入采样结构,并讨论每种结构对系统其它部分的影响。

2020-08-14 14:57:19 702

702

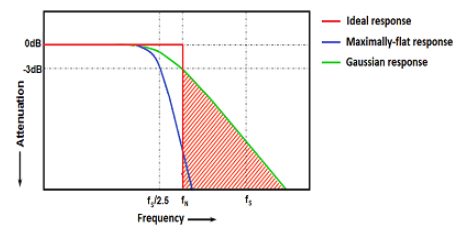

由于有限的输入带宽,除非您将采样率设置得非常低,否则ADC的带宽通常小于奈奎斯特频率。

2021-01-14 14:35:45 19331

19331

作者:Kendall Castor-Perry 在一些关于驱动采样ADC的文章中,谈到了电阻和电容影响输入端的稳定性。这个问题能被提出来是好事,但在我看来,处理方式似乎总是有点经验主义,却并没解释

2021-02-10 09:31:00 7222

7222

采样结构。下面介绍下几种基本结构: 许多CMOS模数转换器中,常用的解决方法是采用开关电容器结构实现输入采样。这种输入结构的最基本形式由相对较小的电容器和模拟开关组成,当开关设在位置1时,采样电容器被充电至采样节点的

2022-11-15 15:52:12 428

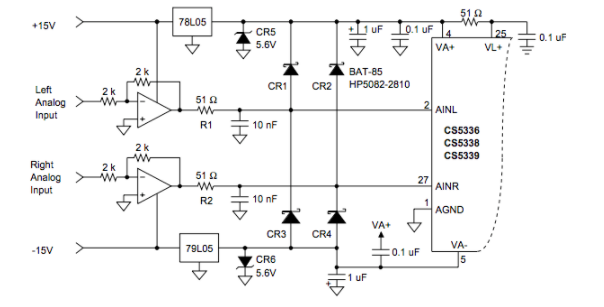

428 电压。 ADC 输入缓冲器和保护电路的设计对于优化和可靠的数据采集系统至关重要。Crystal Semiconductor 应用笔记“ADC 输入缓冲器”很好地涵盖了这一领域,系统设计人员应查看此信息。自从“ADC 输入缓冲器”出版以来,有很多关于 ADC 输入保护的附

2021-05-31 04:33:00 4924

4924

AD7607:8通道DAS,内置14位、双极性输入、同步采样ADC

2021-03-21 13:05:13 1

1 AD7606C-16:8通道DAS,具有16位、1 MSPS双极输入、同步采样ADC数据表

2021-03-22 14:02:04 14

14 UG-1770:评估AD7383双同步采样、16位、4 MSPS、SAR ADC、伪差分输入用户指南

2021-03-22 21:35:46 0

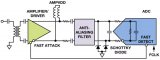

0 高速ADC使用外部输入时钟对模拟输入信号进行采样,如图1所示。图中显示了输入采样时钟抖动示意图。 图1、ADC采样 输入模拟信号的频率越高,由于时钟抖动导致的采样信号幅度变化越大,这点在图2中显示的非常明显。输入信号频率为F2=100MHz时,采样幅度变化如图红色虚

2021-04-07 16:43:45 7378

7378

具有±10.24V软范围输入的18位同步采样ADC

2021-04-18 19:32:54 7

7 AD7616-P:16通道DAS,带16位、双极性输入、双同步采样ADC数据表

2021-04-22 10:44:28 13

13 AD7366-5/AD7367-5:真双极输入,12/14位,2通道,同步采样SAR ADC数据表

2021-04-29 18:16:53 1

1 AD7366/AD7367:真双极输入,双12位/14位,2通道,同时采样SAR ADC数据表

2021-05-11 08:43:29 2

2 AD7352:差分输入、双采样、同时采样、3 MSPS、12位、SAR ADC数据表

2021-05-15 08:43:28 3

3 AD7357:差分输入、双采样、同时采样、4.2 MSPS、14位、SAR ADC数据表

2021-05-15 09:32:56 11

11 AD7605-4:4通道DAS,带16位双极性输入,同时采样ADC数据表

2021-05-22 11:22:29 1

1 AD7380/AD7381:双同步采样、16位/14位、4 MSPS SAR ADC、差分输入数据表

2021-05-23 13:09:38 7

7 1、开启ADC以后,延时一段时间,再采样,如果是连续采样的话,开始的几百个数据建议丢弃。原因就是开启ADC的瞬间,电压肯定是在波动状态的,这个时候采样肯定有问题。2、过采样。如果采样频率高于信号最高

2021-10-25 11:06:08 22

22 一个逐次逼近寄存器 (SAR) 模数转换器 (ADC) 通常需要一个驱动器来驱动其模拟输入,以获得所需的精度效果。但是在较低数据吞吐量和较低分辨率应用中,你也许不需要驱动器。让我们来看一看SAR ADC的采样过程和模拟输入结构来了解驱动器的要求。

2022-01-28 09:32:00 2769

2769

解决办法1配置adc的时候,采样周期需要设置大一些。sConfig.SamplingTime = ADC_SAMPLETIME_71CYCLES_5 ;分析:采样周期太小,会导致采样不准确,采样周期

2021-11-25 09:21:02 35

35 ADC转换就是输入模拟的信号量,单片机转换成数字量。读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。采样周期一般来说=转换时间+读取时间。而转换时间=采样时间+12.5个时钟周期。采样

2021-11-26 20:36:06 88

88 STM32 ADC 过采样技术

2021-12-08 16:21:06 41

41 STM8S003单片机ADC采样通道总共有5个,从AIN2---AIN6,多通道采样时需要将ADC转换设置为单次转换模式,每次切换采样通道后,需要重新初始化 ADC,采样结果在中断中读取。IO

2021-12-27 18:30:21 7

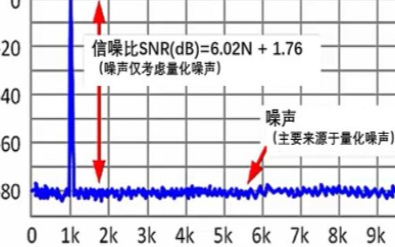

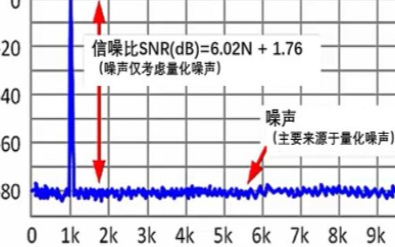

7 一般来说,我们可以提高ADC采样位数来提高ADC的信噪比,但是往往意味着ADC的成本可能也会更高。有没有不提高位数,同样优化信噪比的方法呢?有的,那就是过采样。

2022-03-07 08:56:00 6081

6081

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态内部时钟电路(Clock Circuit)为ADC A通道提供内部采样时钟,该时钟反转180

2023-02-22 11:11:23 2524

2524 测量电压和电流以及它们之间的相位角。过去,同步采样意味着设计人员必须使用多个ADC,并在每个通道上执行并行转换。同步采样ADC现在使用多个T/H在同一时刻对输入进行采样,然后对每个通道执行转换。

2023-02-24 17:24:21 2538

2538

单片机ADC采样输入阻抗怎么匹配

2023-05-17 17:00:00 4998

4998

adc采样率和带宽的关系 ADC(Analog-to-Digital Converter),即模拟转数字转换器,是将模拟信号转换成数字信号的重要器件。其中,采样率和带宽是ADC性能参数之一,也是

2023-09-12 10:51:12 6012

6012 SAR(逐次比较)型ADC的输入电容一般分为采样模式下的和保持模式下的电容。

2023-10-17 12:18:31 1947

1947

这种结构依然存在一些弊端, MDAC和子ADC的信号输入路径可能存在不匹配,也就是开关的RC时间常数的不匹配,导致在输入频率很高时,可能导致采样的信号存在很大的差异(孔径误差)。

2023-12-14 11:38:12 241

241

大家在使用ADC采样的时候是否计算过ADC的采样率,这个问题非常关键!

2024-01-23 09:29:47 560

560

电子发烧友App

电子发烧友App

评论