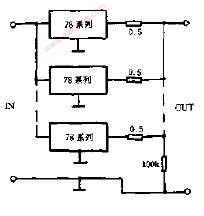

本应用笔记讨论了一种比例电路设计方法,把电阻偏差转换成可接受的电流变化量,可有效消除电压的变化。在此处给出的电路中,电压输出取决于电位器的比值,设计中也可以很好地

2012-03-06 15:20:21 1185

1185

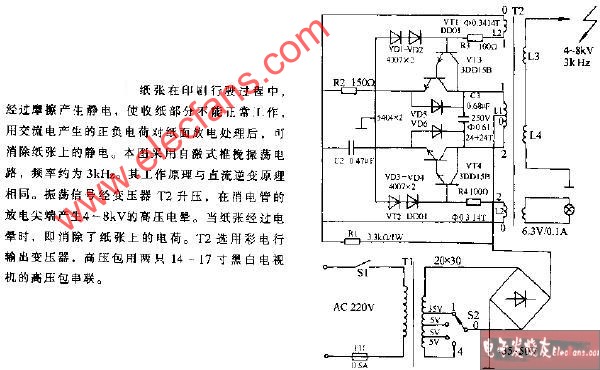

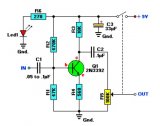

长时间看书、写字时,眼睛与书本之间的距离过近、光照过暗等是造成视力下降的主要原因。本例介绍的视觉疲劳消除器,可有助于消除视力疲劳,预防近视的发生。

2014-12-30 12:01:15 946

946

电路设计常见的八个误区:现象一:这板子的PCB设计要求不高,就用细一点的线,自动布吧;现象二:这些总线信号都用电阻拉一下,感觉放心些;现象三:CPU和FPGA的这些不用的I/O口怎么处理呢?先让它空着吧,以后再说。

2016-12-28 11:46:28 1322

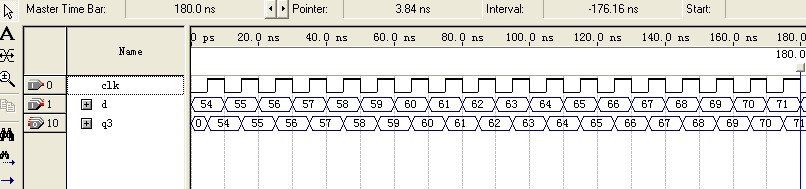

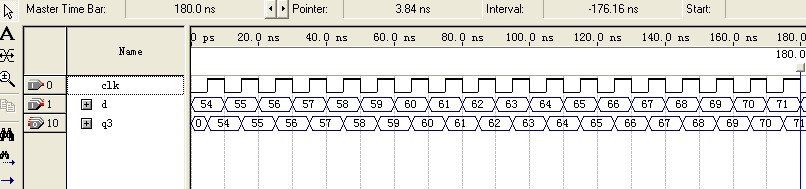

1322 ,被赋值对象会比赋值对象差一个时钟周期。 有了上述理解之后,我们就很容易明白为什么阻塞赋值的对象会立即发生改变,在fpga中我们多接触到的是时序电路,并不希望被赋值对象立即改变,所以有对于组合电路而言,常用阻塞赋

2017-09-19 18:32:43 11967

11967 赋值何时使用阻塞赋值才能设计出符合要求的电路。 他们也不完全明白在电路结构的设计中,即可综合风格的Verilog模块的设计中,究竟为什么还要用非阻塞赋值,以及符合IEEE 标准的Verilog 仿真器究竟如何来处理非阻塞赋值的仿真。 本小节的目的是尽可能地把阻塞和非阻

2021-08-17 16:18:17 6000

6000 本人水平低,现实需要两个UPS电源,当一个UPS故障(电池和市电都无法给负载供电),可自动切换到另一个UPS,急需电路设计!(不想用继电器组成互锁电路)

2012-10-14 21:03:43

两相混合式步进电机H桥驱动电路设计原理

2021-02-19 06:00:06

两路信号,它们的电压和为5V的电路设计,请问怎么设计

2016-12-10 16:19:37

两类无源传感器的分析在多次国家自然科学基金连续资助下,研究空间大范围分布无源阵列传感器及无源无线阵列传感器,拓展压电特性和元件在现代检测技术中的应用。 声表面波(SAW)器件是优良的传感载体和无

2010-04-13 20:28:12

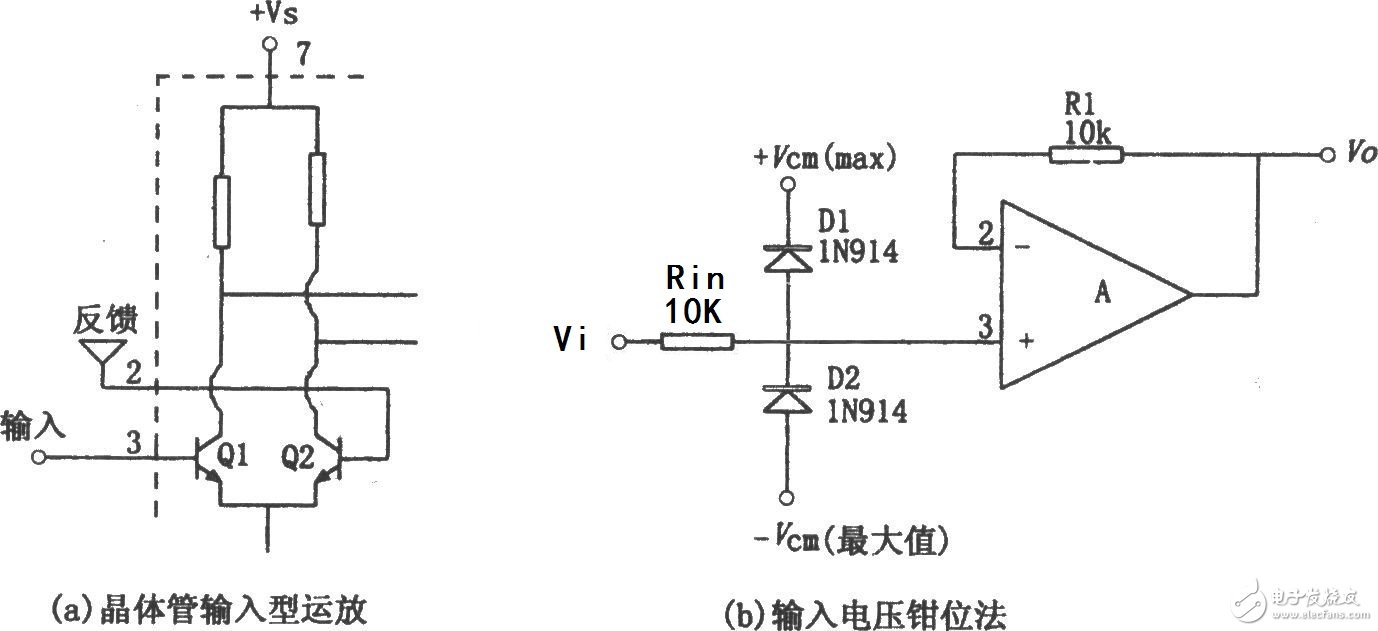

集电结的电流就过大,有可能烧坏晶体管Q2,使集成运放损坏。另外,在输出端上不论什么原因产生的输出瞬时过压也会造成阻塞现象。消除阻塞现象的方法一般可分为两类:限制输入电压法和防止输出瞬时过压法。图(b

2018-09-05 14:33:57

电路设计中的线板和网板指的是什么?两者有什么区别?谢各位大神了。

2015-08-11 22:59:33

的外包可以分为两类,即人力外包和项目外包。从人力外包的角度来看,尽管美国的高通公司等领先的半导体公司也雇用了大量的电路设计工程师,但仍有大量的合同工是通过劳务咨询公司雇用的。这样做的目的是为了节省金钱

2020-05-18 15:51:48

AD电源类电路设计电路电源分类LDO电源类开关电源类AC-DC电源功能快捷键合理的创建标题,有助于目录的生成如何改变文本的样式插入链接与图片如何插入一段漂亮的代码片生成一个适合你的列表创建一个表格

2021-10-29 06:08:34

简单的结构是图 4 所示的半桥电路。图 4:两种常用的 D 类拓扑结构是半桥和全桥配置。(图片来源:Digi-Key Electronics)全桥拓扑结构称为桥接式负载 (BTL),其优势是在供电电压

2018-12-21 10:28:21

的时间不可知)4.wait() 和 notify() 方法:两个方法搭配使用,wait()使线程进入阻塞状态,调用notify()时,线程进入可执行状态。wait()内可加或不加参数,加参数时是以毫秒

2018-07-06 15:11:48

不可知)4.wait() 和 notify() 方法两个方法搭配使用,wait()使线程进入阻塞状态,调用notify()时,线程进入可执行状态。wait()内可加或不加参数,加参数时是以毫秒为单位

2018-04-02 15:42:32

有个程序,想来了中断送到应用层,但驱动无法阻塞,应用层一直打印,麻烦大家给看下哪有问题?驱动是:测试程序是:现象是:

2020-06-05 14:34:27

最近公司数据库同步机制常发生阻塞,时不时的导致PCB工程系统卡死现象,只有找到阻塞源头并处理掉,才以消除阻塞,但数据库中查看会话阻塞是通过二维表方式展示的父子会话进程ID的,是很难清楚的展示各会话

2019-08-08 06:53:13

[td][/td]过孔(via)是多层PCB的重要组成部分之一,钻孔的费用通常占PCB制板费用的30%到40%。简单的说来,PCB上的每一个孔都可以称之为过孔。从作用上看,过孔可以分成两类:一是用作

2018-08-24 16:48:20

Verilog阻塞和非阻塞原理分析在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行

2009-11-23 12:02:57

[table][tr][td] Verilog中有两种为变量赋值的方法。一种叫做连续赋值,另一种叫做过程赋值。过程赋值又分为阻塞赋值和非阻塞赋值。阻塞性赋值使用“=”为变量赋值,在赋值结束前不可以进行其他操作,在赋值结束之后继续后面的操作。这个过程就好像阻断了程序的运行。非阻塞赋值使用“

2018-07-03 03:06:04

,常用阻塞赋值,时序电路常用非阻塞赋值。先看一个大家都熟悉的例子:先看非阻塞代码:clk为主时钟分频之后的时钟,clk先赋值给a,然后a在赋值给b,看一看生成的电路图可以看出是两个触发器,而且前一个

2017-04-05 09:53:11

` 本帖最后由 wcl86 于 2021-5-28 19:37 编辑

通过labview深度学习标注工具对样本进行标注,两类NG进行标注,标注完成后扩展样本数量级,以少量样本获得较好的标注训练

2021-05-27 22:25:13

`编辑推荐《普通高等教育电子科学与技术类特色专业系列规划教材:射频通信电路设计(第二版)》可以作为通信类和电子类(通信工程、电子信息工程、无线电技术、计算机等专业)本科生的教材或参考书,也可供从事

2018-01-18 17:31:11

同了在第一个clk上升沿到来时,由于b的值未知,赋给c之后,c也为未知值;紧接着,把a的值给b,由于a的值已经给出,所以,结束之后,a、b的值相同,c为x。综合之后,生成两级移位寄存器。 关于非阻塞

2016-11-03 20:26:38

阻塞与非阻塞作者:小黑同学一、 概述1、阻塞赋值对应的电路往往与触发沿没有关系,只与电平的变化有关系。阻塞赋值符号“=”。2、非阻塞赋值对应的电路结构往往与边沿触发有关系,只有在触发沿时才有可能发生赋值的情况。非阻塞赋值符号“

2020-04-24 14:49:45

就电子设计文章的发布渠道而言,可分为专业类和个人爱好类这两个基本类别,大体上可以确定哪些内容是可以发表的,哪些内容是不能发表的。个人爱好类曾经有Popular Electronics

2018-10-22 22:43:50

这是两个ADI的电路设计资料,希望对大家有用。

2012-08-10 14:16:00

AB类功放驱动电路设计目标AB类功率放大器驱动电路的研究与设计

2021-04-08 06:53:41

效果。(5)布线时避免90度折线,减少高频噪声发射。(6)可控硅两端并接RC抑制电路,减小可控硅产生的噪声(这个噪声严峻时可能会把可控硅击穿的)。按干扰的传播路径可分为传导干扰和辐射干扰两类。

2018-08-28 17:54:26

计算机等级三级嵌入式知识点总结二这个是一个计算机三级嵌入式的复习重点,个人总结,希望对考前几天复习的老铁们有用。但记得,刷题才是根本,看了重点需要配套刷题!!!凡是和存储器有关的指令只有两类:LDR

2021-12-23 07:10:59

比较简单各种电阻性有源功能单元电路(电流与电压的转换电路,电流与电压的放大电路),然后讨论两类有源滤波电路(有源基本模块的级联和无源电路的有源模拟)的设计问题,最后介绍有关非线性有源电路(电压比较、施密特

2009-08-20 19:01:16

如何消除电路中的电感?混沌与混沌同步原理是什么?常用的模拟电感电路有哪几种?

2021-04-22 06:29:49

遇到自激,就会很麻烦,因为调试起来很费时间,需要在保证带内性能的前提下,把自激现象消除掉。

2019-09-23 07:57:54

本帖最后由 carey123 于 2014-12-9 15:45 编辑

现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容

2014-12-09 15:44:18

本文重点剖析了全桥模拟型D类功放设计要素,实现了一种基于NXP公司新型绿色能效模拟D类功放TFA9810T电路设计,并重点对绿色节能高效、高输出功率、低温升效应、PCB布局、EMI抑制几个方面进行总结分析。

2021-04-22 06:20:52

两个板卡,都是采集电压信号的,但是频率不同,因此数据长度不同。现在希望把这两个板卡的数据写在同一个tdms中,并且两组数据分成不同的列。且组名、通道名都要能控制。请问有大神指导如何操作么?

2016-09-26 23:14:36

在使用应变传感器设计电路的时候,应变传感器zerobalance比应变传感器的出力大得多,在电路设计的时候如何将应变传感器的zerobalance的影响消除?

2022-02-22 15:00:57

电视之争,明面是产业政策和产业标准之争,实质是网络能力、技术实现、市场能力、行业趋势之争。 两类标准存在本质区别 市场未动,标准先行。关键技术的提出、设计和产业化都将启动一个又一个令人激动人心的产业链。随着

2019-06-19 06:21:59

1.静态数码管原理图LED数码管根据LED的不同接法分为两类:共阴和共阳

2021-11-18 08:15:52

晶振具有的等效电气特性晶振电路设计方案,电路中各元器件的作用是什么?消除晶振不稳定和起振问题有什么具体的建议和措施吗?

2021-04-13 06:19:09

目前应用最多的是ARM 7和ARM9两类处理器。 ARM 7较便宜,可跑uclinux(是一个不支持高级内存管理功能的嵌入式Linux系统统)、Vxworks、uc/os II等实时操作系统,但因

2018-08-14 05:46:57

损害LED.使用时必须增加保护电路限流。 按照电源类别,可以分成交流和直流两类。 当交流市电作输入时,只需要将电源电压整形滤波后接入直流应用电路。基于AX2028的LED驱动电路设计 LED产品

2018-11-29 17:08:29

为了在基板上形成功能性的MEMS结构,必须蚀刻先前沉积的薄膜和/或基板本身。通常,蚀刻过程分为两类:浸入化学溶液后材料溶解的湿法蚀刻干蚀刻,其中使用反应性离子或气相蚀刻剂溅射或溶解材料在下文中,我们将简要讨论最流行的湿法和干法蚀刻技术。

2021-01-09 10:17:20

作者:Mark Sauerwald 德州仪器 在用户访问www.ti.com 时,在搜索框中输入“均衡器”一词时,会发现两类截然不同的产品。一类是像 LMH0394 这样的自适应线缆均衡器,而另一类

2018-09-19 14:48:48

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

关于cpu访问GPIO、UART、I2C等接口,与cpu访问FLASH、ROM、SDRAM的区别?cpu访问GPIO、UART等外设,是通过特殊功能的寄存器,不也是在访问内存上的某一地址吗?而cpu访问FLASH、ROM也是访问内存中对应的某一地址。请问,访问两类,有何区别?

2019-09-10 05:45:16

变压器的漏感是不可消除的,但可以通过合理的电路设计和绕制使之减小。设计和绕制是否合理,对漏感的影响是很明显的。采用合理的方法,可将漏感控制在初级电感的2%左

2009-10-17 14:03:27 39

39 针对数字滤波器中存在的Gibbs现象,研究了改进窗函数与改变滤波因子截断长度综合法。鉴于该方法通带和阻带的截止频率不易控制的缺点,提出了消除Gibbs现象的一种全新的方法即

2010-01-12 18:54:39 26

26

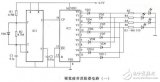

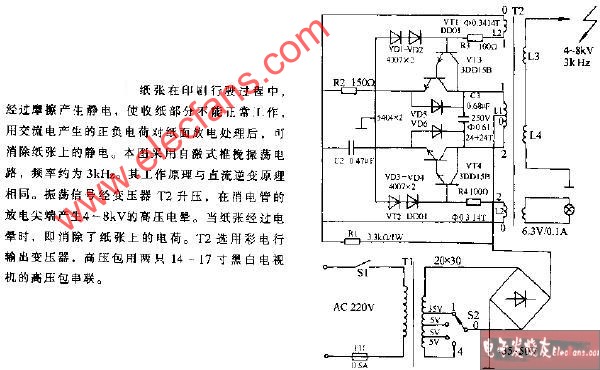

静电消除电路

2009-02-09 12:55:24 3482

3482

电路设计的常见问题

现象一:这板子的PCB设计要求不高,就用细一点的线,自动布吧

点评:自动布线必然要占用更大的PCB面积,同时产生比手动

2009-04-12 12:36:45 1520

1520

消除环流的电路图

2009-05-11 14:29:27 1744

1744

数字噪声消除器电路图

2009-05-30 15:59:24 1206

1206

电路的谐振现象分析

谐振现象是交流电路中产生的一种特殊现象,对谐振现象的研究有着重要的意义。在实

2009-07-27 08:11:02 10045

10045

维持阻塞D触发器

(a) 逻辑电路 &

2009-09-30 18:23:59 18683

18683

如何消除红眼现象/调节对比度/修整图象

用数码相机拍摄出数码图象仅仅只完成了拍摄工作,从这些操作中获得的乐趣远远称不上完全享受了数码摄

2010-02-23 13:46:48 621

621 阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别

2011-03-15 10:57:34 6892

6892 电子发烧友为您提供了运放阻塞以及消除电路图,希望对您的学习工作有所帮助!

2011-06-22 09:17:52 2663

2663

本文通过Verilog事件处理机制,详细讨论了阻塞与非阻塞赋值的区别、联系及其应用示例。由本文可知,阻塞与非阻塞赋值灵活多变,底层实现也差异甚大。因而在数字电路设计时,依据

2011-08-28 17:59:19 575

575

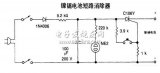

该短路消除器是用烧断的方法来消除镍镉电池组的内部短路的,注意:电池组负端要接到交流线路的一侧。为操作安全起见,要使用一个1:1的隔离变压器。 镍镉电池 短路消除器电路:

2011-10-19 10:28:54 2220

2220

基线消除电路先将成形后的核脉冲信号输入一阶低通滤波电路取出直流分量,再与原信号相减实现去除直流分量的作用。 基线消除电路 :

2012-04-06 10:07:51 2625

2625

这是一个很好的学习阻塞和非阻塞的资料,对于FPGA的学习有很大帮助。

2016-04-22 11:00:45 11

11 学verilog 一个月了,在开发板上面写了很多代码,但是始终对一些问题理解的不够透彻,这里我们来写几个例子仿真出阻塞和非阻塞的区别

2017-02-11 03:23:12 1194

1194 在一开始学到阻塞和非阻塞的时候,所被告知的两者的区别就在于阻塞是串行的,非阻塞是并行的。但是虽然知道这个不同点,有些时候还是很难真正区分用两者电路的区别,下载资料内以一个简单的串行流水线寄存器为例进行了分析。

2017-09-16 09:34:07 4

4 基于博弈论的传感网路由协议中存在布雷斯悖论现象使路由选择不能达到全局最优效果,而现有的路由协议忽视了对这一问题的研究。分析了布雷斯悖论对传感网路由协议的影响,提出了一种消除传感网路由协议中布雷斯悖论

2018-01-16 16:44:49 0

0 电路设计能力的判断方法 现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容是玄之又玄,能达到其最高九段标准的,地球上可能找不几个人。

2018-04-14 12:37:00 19226

19226

现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容是玄之又玄,能达到其最高九段标准的,地球上可能找不几个人。

2018-05-29 17:12:09 4317

4317

设计背景: 阻塞 (=)和非阻塞(=)一直是在我们FPGA中讨论的问题,资深的学者都是讨论的是赋值应该发生在上升下降沿还是在哪里,我们在仿真中看的可能是上升下降是准确的,但是在时间电路中这就

2018-05-31 11:40:14 6358

6358

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2020-01-30 17:41:00 20976

20976 阻塞赋值对应的电路往往与触发沿没有关系,只与输入电平的变化有关系。非阻塞赋值对应的电路结构往往与触发沿有关系,只有在触发沿时才有可能发生赋值的情况。

2020-06-17 11:57:41 10885

10885

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微

2020-11-19 15:48:56 927

927 @(posedge clk) begin q1 = d; q2 = q1; q3 = q2; end endmodule 上述代码综合后能得到所期望的逻辑电路吗? 答案是否定的, 根据阻塞赋值语句的执行过程可以得到执行后的结果是

2021-05-08 14:47:05 1799

1799

阻塞赋值和非阻塞赋值的可综合性 Blocking Assignment阻塞赋值和NonBlocking Assignment非阻塞赋值,原本是软件进程管理的术语。由于Verilog团队是从C语言发展

2021-05-12 09:45:09 2398

2398

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。 Verilog语言中讲的阻塞赋值

2021-12-02 18:24:36 5005

5005

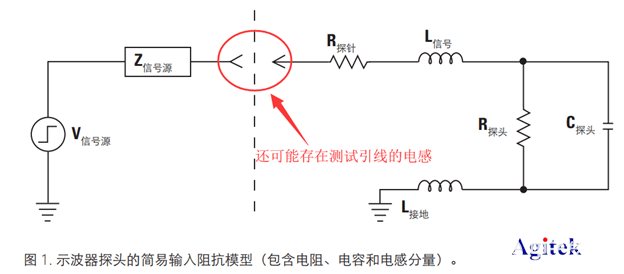

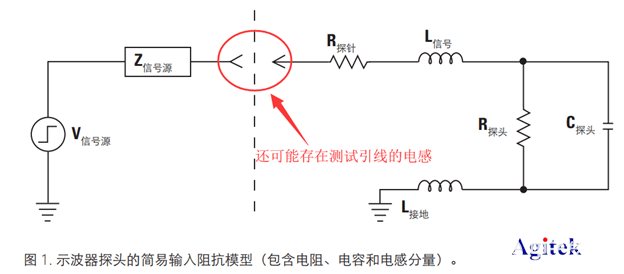

如何消除示波器探头所产生的过冲和振铃现象,抑制示波器测试系统自身产生谐振对于真实电路测量的影响? 所有的LC电路都可能会产生谐振,示波器探头也是LC电路,在使用过程中,要避免示波器探头自身带来的谐振

2021-12-21 17:46:50 2876

2876

Verilog HDL的赋值语句分为阻塞赋值和非阻塞赋值两种。阻塞赋值是指在当前赋值完成前阻塞其他类型的赋值任务,阻塞赋值由=来完成;非阻塞赋值在赋值的同时,其他非阻塞赋值可以同时被执行,非阻塞赋值由《=来完成。

2022-03-15 13:53:08 2524

2524 如何消除示波器探头所产生的过冲和振铃现象,抑制示波器测试系统自身产生谐振对于真实电路测量的影响?

2023-05-29 10:14:32 807

807

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2023-06-01 09:21:57 514

514 示波器探头是一种用于测量电路中信号波形的电子仪器。在使用示波器探头进行测量时,由于探头的存在,可能会产生过冲和振铃现象。这些现象会影响测量结果的准确性,因此需要采取一些措施来消除这些现象。

2023-06-04 14:51:00 2407

2407 阻塞通信(Blocking Communication):当进行阻塞通信时,调用者在发起一个I/O操作后会被阻塞,直到该操作完成返回才能继续执行后续代码。

2023-06-15 17:32:21 3580

3580 关于阻塞函数和非阻塞函数在CAN和LIN相关的开发库里,不可避免的会出现“收”和“发”的函数。如何快速有效的处理数据,是开发中重要的事项。

2022-07-05 14:38:43 692

692

今天给大家普及一下阻塞赋值和非阻塞赋值的相关知识

2023-07-07 14:15:12 1239

1239

”=“阻塞赋值与”<=“非阻塞赋值是verilog语言中的两种不同的赋值方式,下面将对两种赋值方式进行比较。方便进行理解和使用。

2023-09-12 09:06:15 587

587

阻塞 IO 模型 在Linux ,默认情况下所有的 socket 都是阻塞的,一个典型的读操作流程如图所示。 阻塞和非阻塞的概念描述的是用户线程调用内核 IO 操作的方式:阻塞是指 IO 操作需要

2023-10-08 17:16:51 426

426

阻塞就是外部有阻塞干扰信号的时候,设备还可以正常运行。一般分为带内阻塞和带外阻塞,由于直放站都是做宽带设备,一般只提带外阻塞。

2023-10-10 11:22:37 546

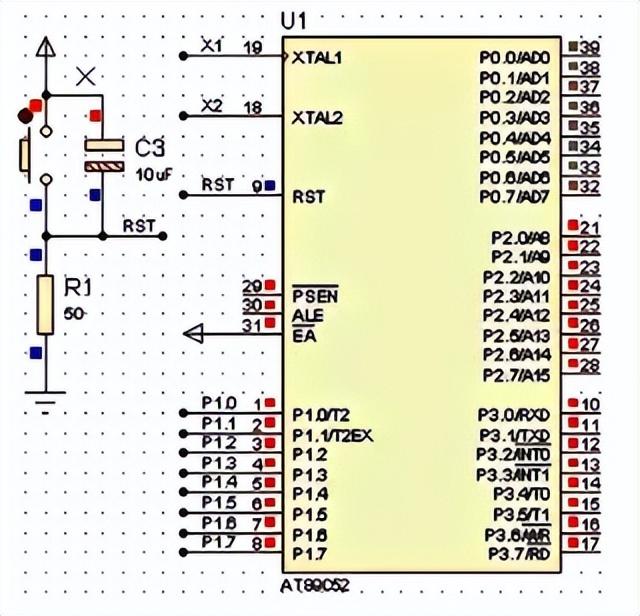

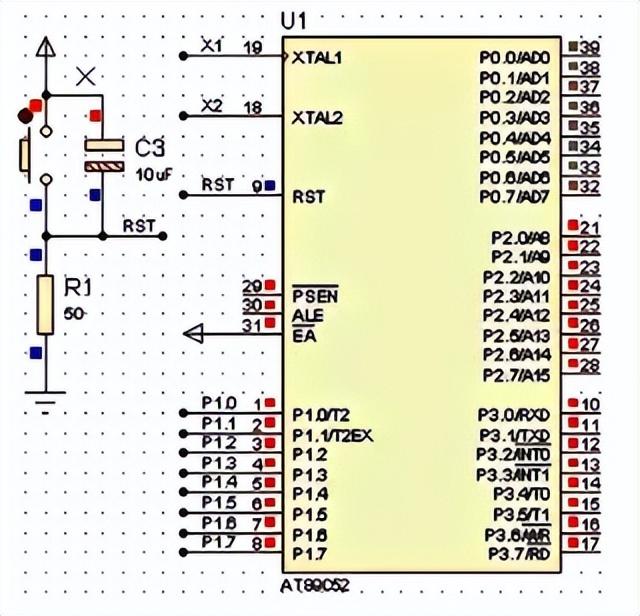

546 单片机外围电路设计需要注意的点有很多,包括单片机上拉电阻的选择、按键抖动及消除、三极管起到开关作用和电平转换的作用,以及电流电压驱动问题。其中,消除方法有两种:软件除抖和硬件除抖。

2023-11-06 11:14:59 847

847

集成电路按用途可分为模拟集成电路和数字集成电路两类。

2024-01-03 18:14:34 572

572 采取一系列措施来消除自激现象。 以下是消除小信号调谐放大器的自激现象的方法: 1. 分析自激原因:首先需要对自激现象进行深入分析,找出自激的原因。自激通常由以下几个方面引起:电路中的正反馈路径、放大器的增益过大、传

2024-01-31 10:44:53 152

152 自谐振现象对电路性能的影响及其避免方法 自谐振现象是指电路中的元件参数(如电感、电容等)与外部激励频率之间存在某种特定关系,从而导致电路发生共振现象。自谐振现象在电路设计和应用中是一个重要

2024-02-03 14:19:24 128

128 怎么判断截止失真和饱和失真 电路饱和失真怎么消除 截止失真和饱和失真是电路中常见的失真现象,会导致信号的失真和变形。 一、截止失真的判断和消除 截止失真是指在放大电路中,当输入信号的幅值超过某一

2024-02-18 14:43:49 1002

1002 Verilog是一种硬件描述语言,用于设计和模拟数字电路。在Verilog中,同步和异步是用来描述数据传输和信号处理的两种不同方式,而阻塞赋值和非阻塞赋值是两种不同的赋值方式。本文将详细解释

2024-02-22 15:33:04 202

202

电子发烧友App

电子发烧友App

评论