,即0和1,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。 触发器有集成触发器和门电路组成的触发器二种。触发方式有电平触发和边沿触发二种。 触发器应用很广,可用做数字信号的寄存,移位寄存,分频和

2023-01-11 17:17:07 9167

9167

电路为什么要有触发器这种结构?为什么要用时钟同步起来呢?一个乘法器如果不设计成触发的会是什么状态?最近在想电路同步异步的时候想到这个问题。

2016-12-08 17:41:52

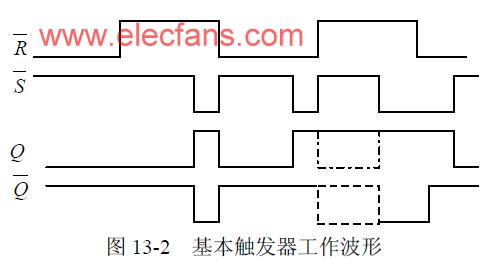

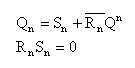

不变。所以,触发器可以记忆1位二值信号。根据逻辑功能的不同,触发器可以分为RS触发器、D触发器、JK触发器、T和T′触发器;按照结构形式的不同,又可分为基本RS触发器、同步触发器、主从触发器和边沿触发器。

2009-09-16 16:06:45

D触发器都是边沿触发器么,有人帮忙解释一下么,谢谢了!!!

2016-05-03 20:24:57

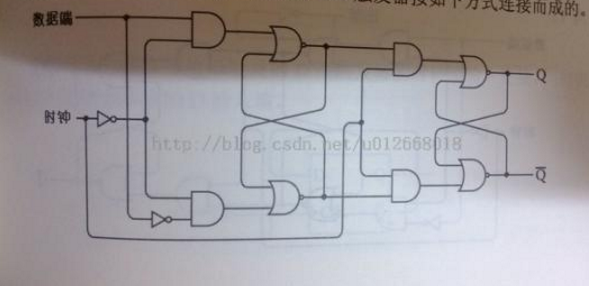

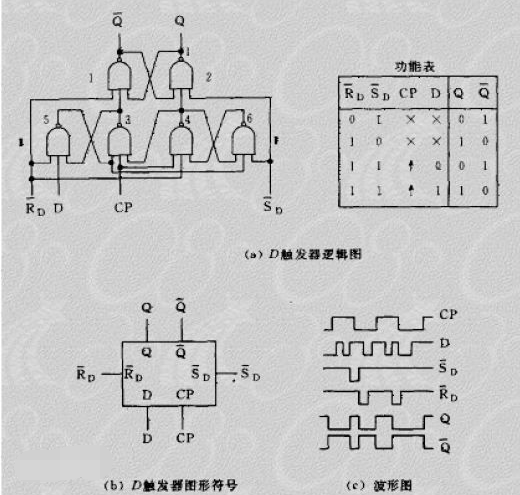

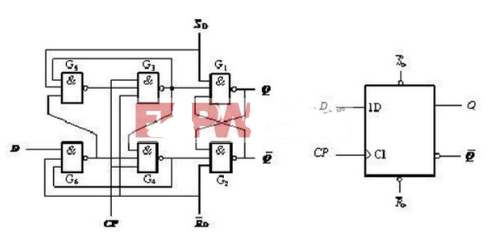

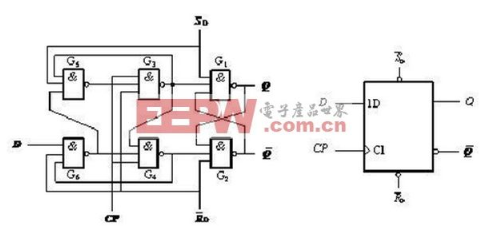

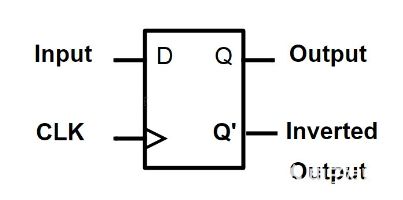

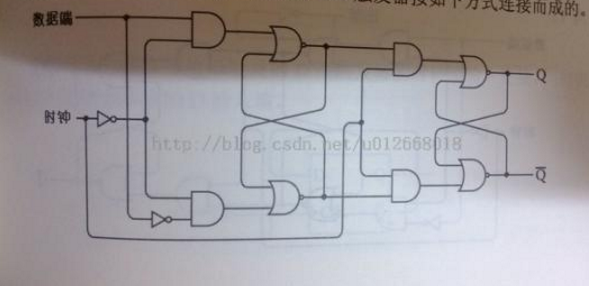

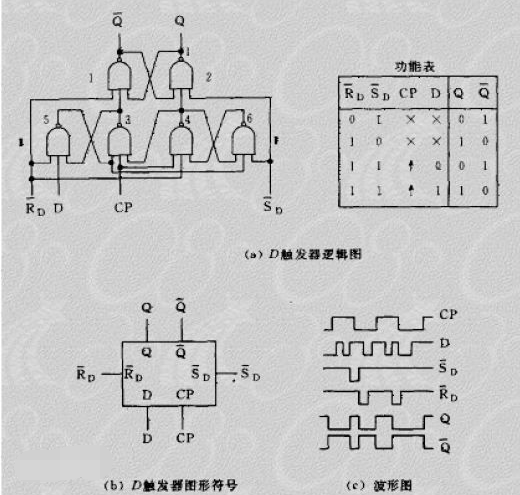

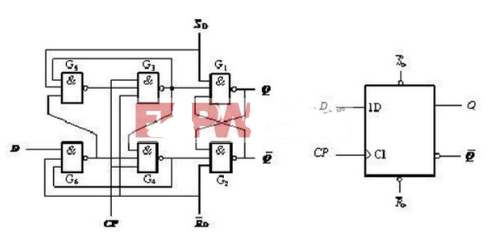

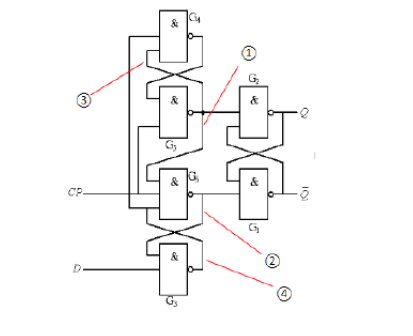

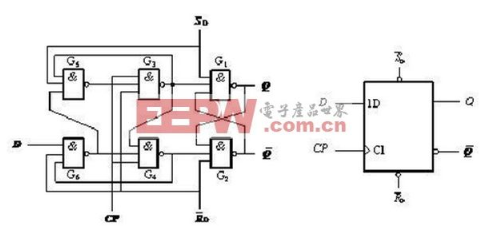

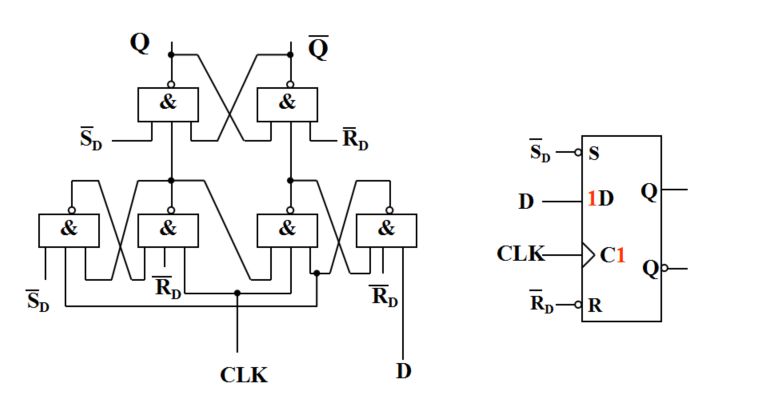

有木有。 事实上,触发器的工作原理并不复杂。首先我们来看图1。图1D触发器框图和内部门电路结构图1所示的是一个D类触发器的框图和内部门电路结构。框图中输入端的三角形代表着时钟信号边沿触发方式。同学们

2021-07-04 08:00:00

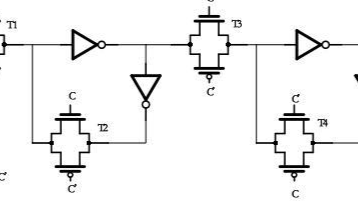

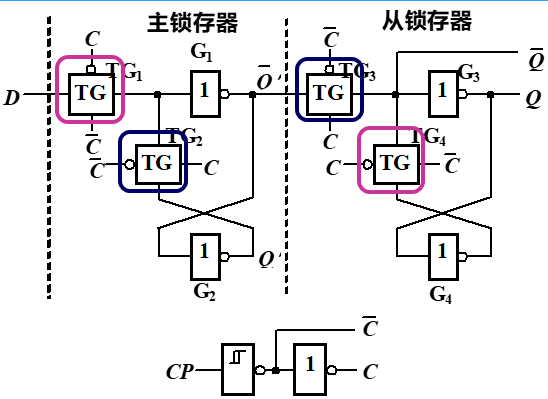

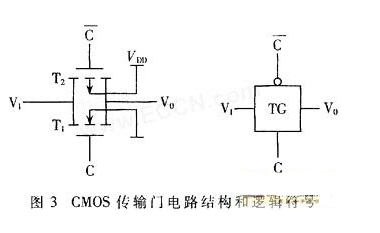

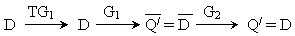

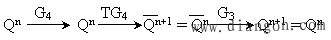

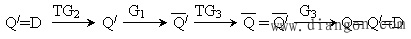

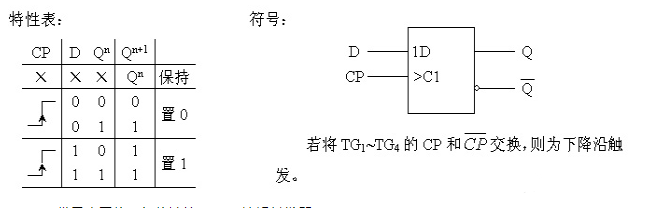

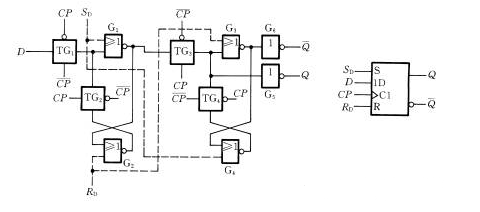

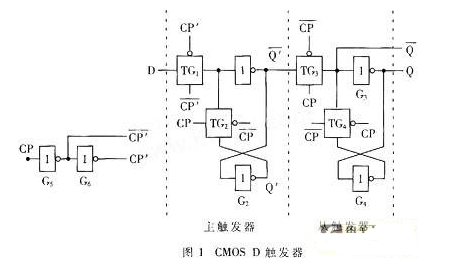

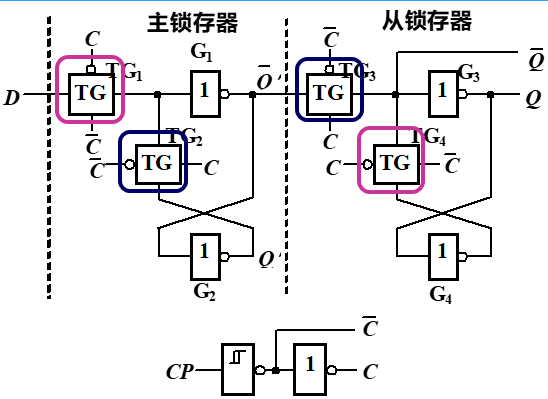

触发器的电路结构和图形符号 思考 :电平触发的D触发器的工作原理。 在CMOS电路中,经常利用CMOS传输门组成电平触发D触发器,如图6。 图6 :利用CMOS传输门组成的电平触发的D

2023-02-22 17:00:37

主从触发器(边沿触发)。主从JK触发器主从触发器通过使用两个串联配置的SR触发器消除了所有时序问题。一个触发器充当“主”电路,在时钟脉冲的上升沿触发,而另一个触发器充当“从属”电路,在时钟脉冲的下降沿触发。这

2021-02-01 09:15:31

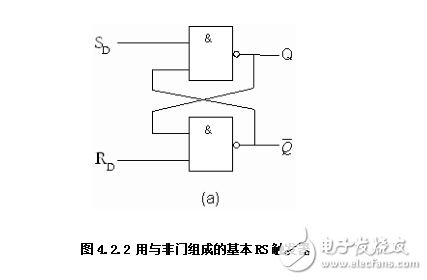

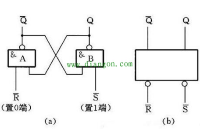

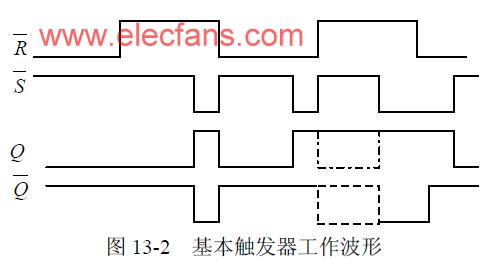

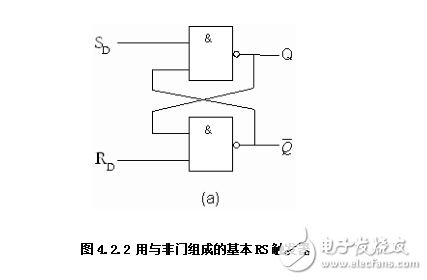

R-S触发器是最基本的一种触发器,它由两个“与非”门组成。它有两个输入端,分别称为置“0”端(也称为复位端、R端)和置“1”端(也称为置位端、S端);它有两个输出端,分别称为Q端和Q端。并且规定:当

2019-12-25 17:21:56

方式不同分为:电平触发器、边沿触发器和脉冲触发器。按电路结构不同分为:基本RS触发器和钟控触发器。按存储数据原理不同分为:静态触发器和动态触发器。按构成触发器的基本器件不同分为:双极型触发器和MOS型

2019-12-25 17:09:20

触发器敏感的SR锁存器,如图所示,现在S = D而R =不是D。D型触发器电路我们记得,一个简单的SR触发器需要两个输入,一个用于“设置”输出,一个用于“复位”输出。通过将反相器(NOT门)连接到SR

2021-02-03 08:00:00

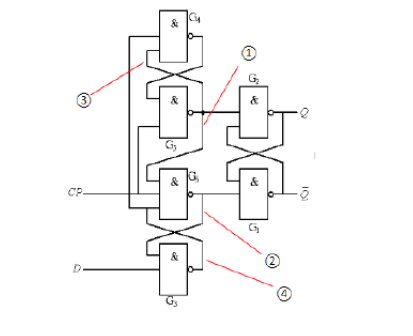

1、在FPGA中使用门级结构设计D触发器的思路一个逻辑电路是由许多逻辑门和开关组成的,因此用基本逻辑门的模型来描述逻辑电路结构是最直观的。本实验设计使用结构描述语句实现D触发器功能,采用带异步置位

2022-07-04 16:01:57

的位数设计,所以一般有8位寄存器、16位寄存器等。对寄存器中的触发器只要求它们具有置1、置0的功能即可,因而无论是用同步RS结构触发器,还是用主从结构或边沿触发结构的触发器,都可以组成寄存器。一般由D

2018-07-03 11:50:27

数字电路--若干种触发器工作原理

2016-12-26 16:51:00

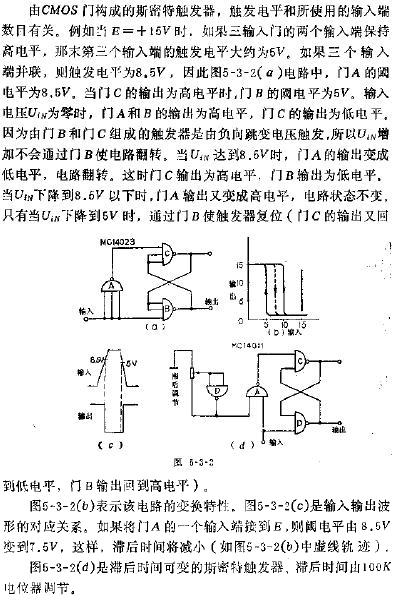

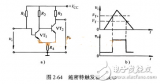

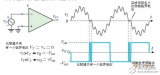

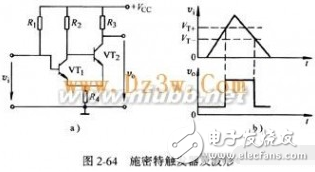

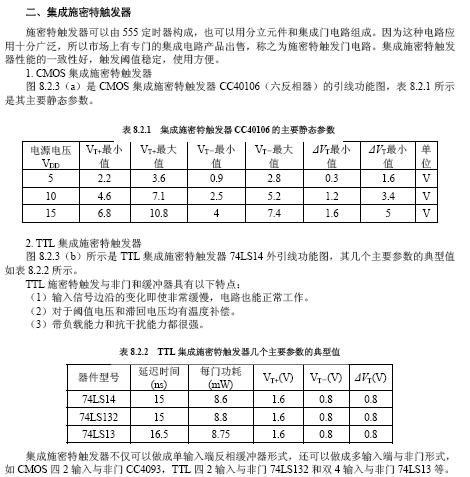

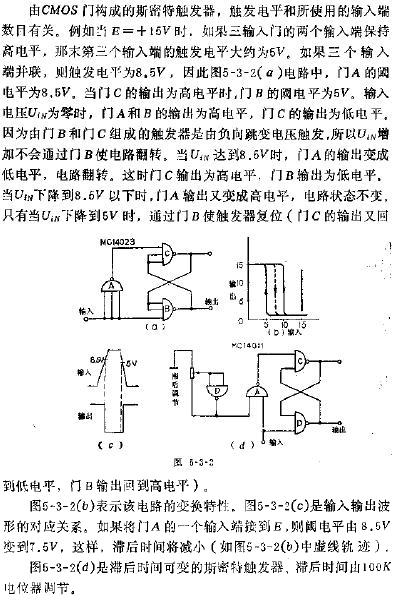

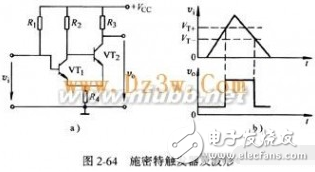

和正向递增两种不同变化方向的输入信号,施密特触发器有不同的阀值电压。门电路有一个阈值电压,当输入电压从低电平上升到阈值电压或从高电平下降到阈值电压时电路的状态将发生变化。施密特触发器是一种特殊的门电路

2011-11-14 14:30:44

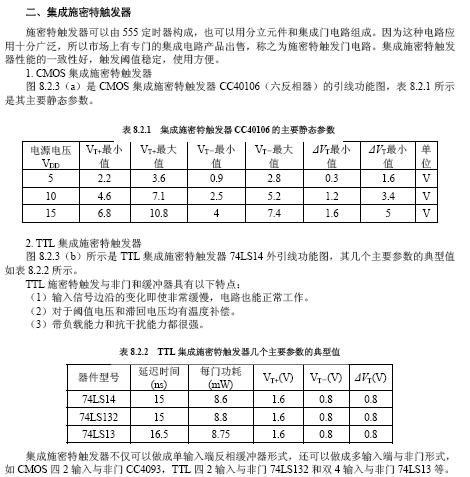

施密特触发器:8.2.1 用门电路组成的施密特触发器8.2.2 集成施密特触发器8.2.3 施密特触发器的应用 1、施密特触发器电压传输特性及工作特点

2009-09-24 15:38:23

。 (2)为了解决这个问题,必须改进电路设计,实际中常用的结构有三种类型:主从触发器.它的类型有:主从R-S触发器、主从JK触发器。维持阻塞触发器.维持就是在CP期间触发器完成其预定功能;阻塞就是在CP期间

2018-08-23 10:36:20

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲

2019-06-20 04:20:50

电平触发器和边沿触发器符号

2019-10-18 09:01:09

无论是用同步RS结构触发器,还是用主从结构或边沿触发结构的触发器,都可以组成寄存器。一般由D触发器组成,有公共输入/输出使能控制端和时钟,一般把使能控制端作为寄存器电路的选择信号,把时钟控制端作为数据输入

2011-10-09 16:19:46

锁存器的工作原理是什么?锁存器的动态特性及其应用有哪些?触发器的工作原理是什么?触发器的电路结构是如何构成的?

2021-11-03 06:48:50

40174 CMOS 六D触发器:

2009-08-08 11:32:28 46

46 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 0

0 rs触发器工作原理

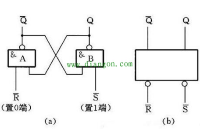

一、电路组成及符号

基本RS

2008-01-21 13:23:00 10624

10624

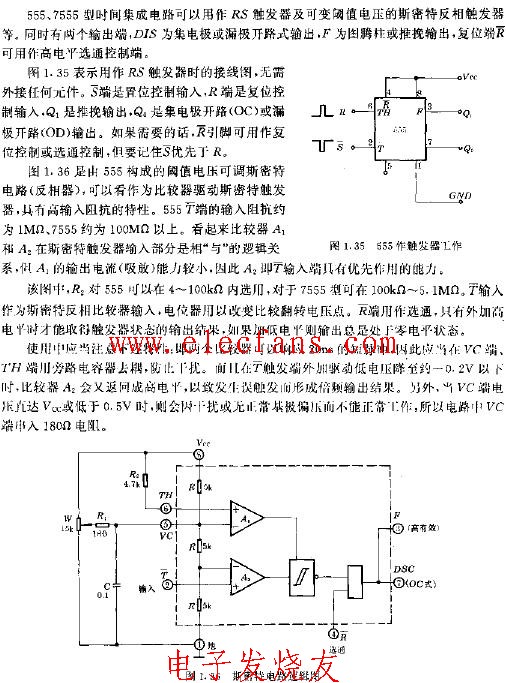

施密特触发器工作原理:具有回差电压特性,能将边沿变化缓慢的电压波形整形为边沿陡峭的矩形脉冲。

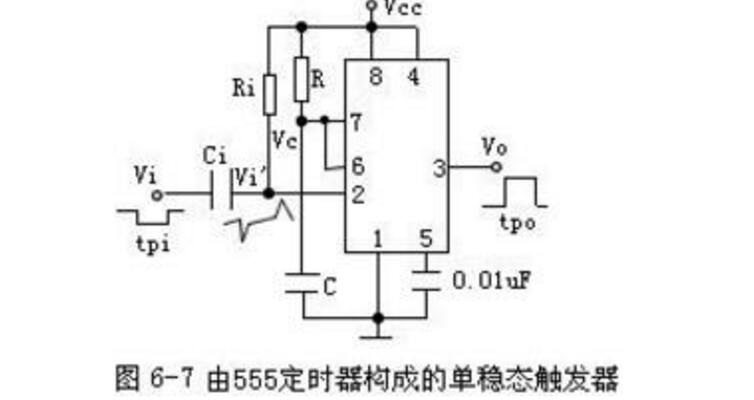

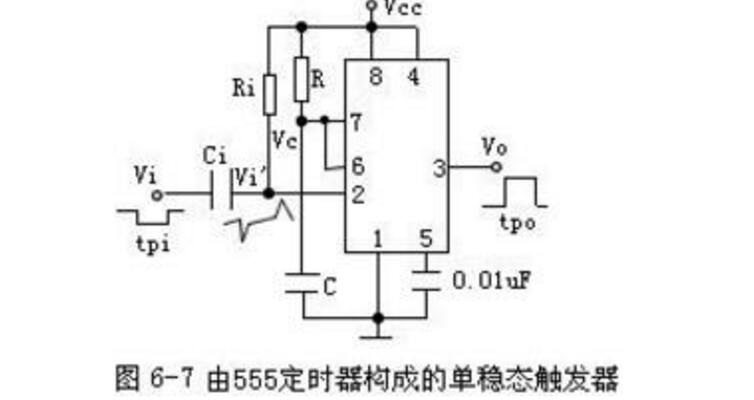

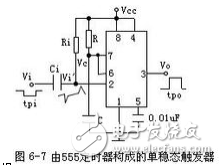

用555定时器构成的

2008-01-21 13:40:31 11172

11172

主从jk触发器电路及工作原理

2008-01-21 14:00:16 16093

16093

主从RS触发器电路及工作原理

1.

2008-01-21 14:02:53 3707

3707

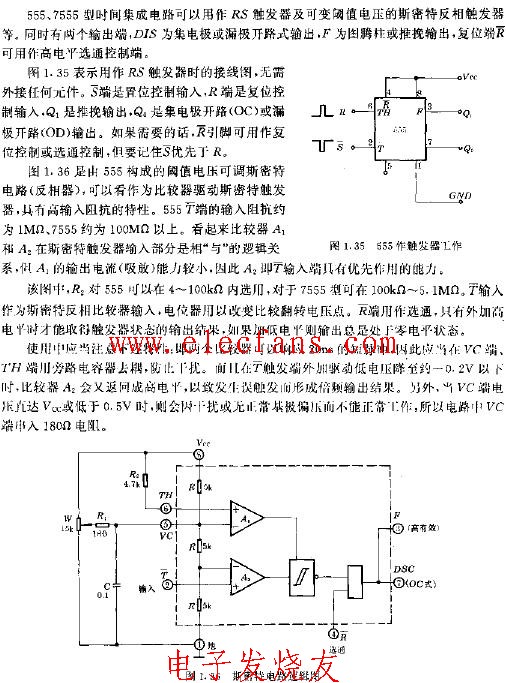

555作触发器工作电路图

2008-05-19 23:02:03 1164

1164

本节中,不详细分析触发器具体电路的工作原理,只简单了解即可。因为集成触发器的学习以应用时够用为度,不强调内部电路。重点:逻辑功能、触发方式。

2009-03-30 16:18:11 3245

3245

用CMOS门构成的斯密特触发器

2009-04-13 10:22:33 1301

1301

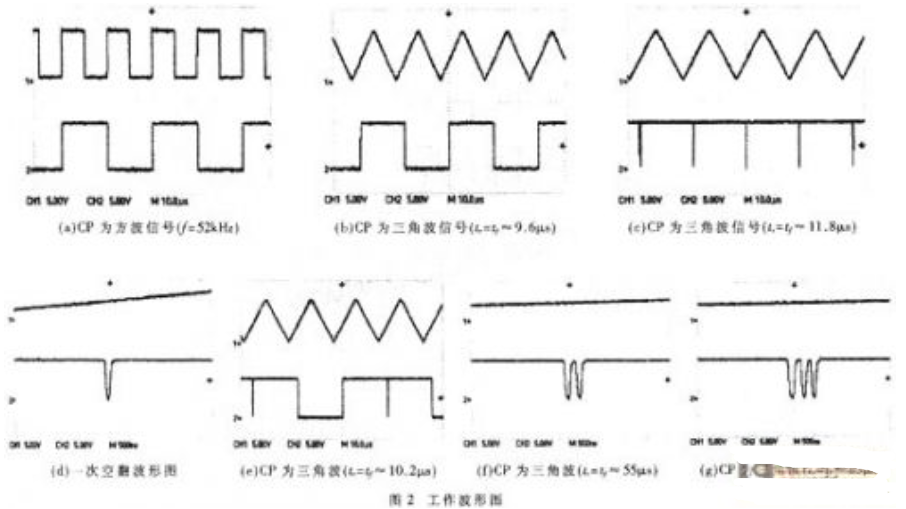

CMOS触发器在CP边沿的工作特性研究

对时钟脉冲(简称CP)边沿时间的要求,是触发器品质评价的重要指标之一。触发器只有在CP边沿陡峭(短的边沿时

2009-10-17 08:52:12 1622

1622

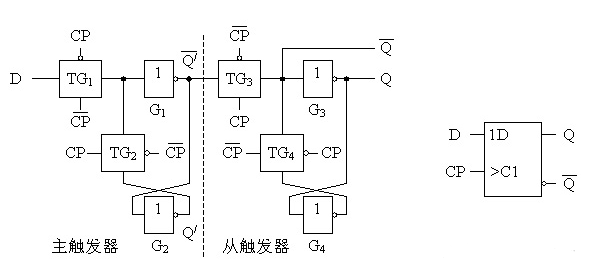

CMOS触发器的结构与工作原理

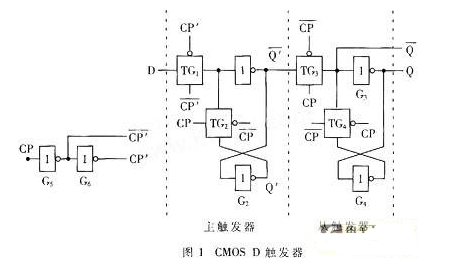

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪

2009-10-17 08:52:27 7151

7151

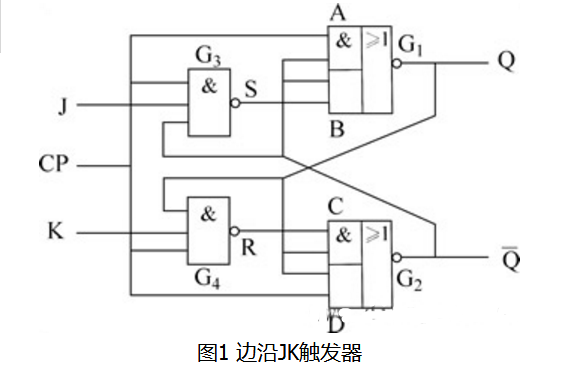

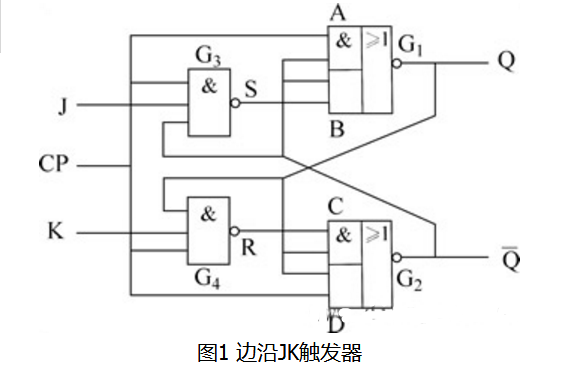

JK触发器工作原理详细介绍

JK触发器,采用与或非电路结构,它的工作原理为:CP为0时,触发器处于一个稳态;CP由0变1时,触发器不

2010-03-08 13:47:58 50600

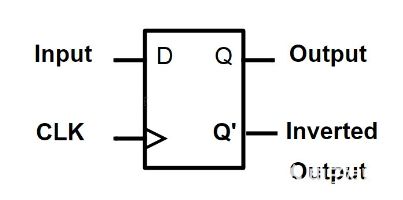

50600 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 4395

4395 D触发器工作原理是什么?

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出

2010-03-08 13:56:50 69365

69365

什么是RS触发器,RS触发器的工作原理是什么?

主从RS触发器

2010-03-08 14:00:11 29757

29757 RS触发器的基本工作原理图解分析

基本RS触发器由两个与非门G1和G2交叉耦合构成,如

2010-03-08 14:09:17 115947

115947 触发器的分类, 触发器的电路

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1554

1554 可以将电平触发器转换成更为灵活的边沿触发器(采用时间控制方法)。边沿触发器只在上升沿或下降沿处对输入采样。这种转换可以这样来实现:将原来的时钟信

2010-08-10 11:10:26 5657

5657

基本触发器的逻辑结构如图13-1所示。它可由两个与非门交叉耦合构成,图13-1(a)是其逻辑电路图和逻辑符号,也可以由两个或非门交叉耦合构成,如图13-1(b)所示。

2010-08-13 09:15:20 8226

8226

本次重点内容:1、触发器的概念和分类。2、同步触发器、主从触发器、边沿触发器的含义。

4.1.1 触发器概述一、触发

2010-08-19 08:57:47 19312

19312 图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 17220

17220

数字电路--若干种触发器工作原理

2017-01-07 21:08:03 0

0 一种单锁存器CMOS三值D型边沿触发器设计

2017-01-17 19:54:24 25

25 施密特触发器最重要的特点是能够把变化缓慢的输入信号整形成边沿陡峭的矩形脉冲。同时,施密特触发器还可利用其回差电压来提高电路的抗干扰能力。

2017-08-24 09:23:59 104194

104194

本文介绍了什么是施密特触发器、施密特触发器的主要特点,其次介绍了施密特触发器电路工作原理详解,最后介绍了施密特触发器的具体作用。

2018-01-16 11:50:23 36850

36850

本文主要介绍了施密特触发器的特点_施密特触发器作用。施密特触发器是最常用的整形电路之一。施密特触发器的显著特点是:施密特触发器有两个稳定状态,其维持和转换完全取决于输入电压的大小;电压传输特性特殊

2018-01-16 16:02:37 47805

47805

本文开始介绍了JK触发器工作特性与边沿JK触发器的特点,其次介绍了边沿JK触发器工作原理与特点,最后介绍了集成边沿式JK触发器边沿式JK触发器设计及波形仿真图形。

2018-01-30 17:17:49 35482

35482

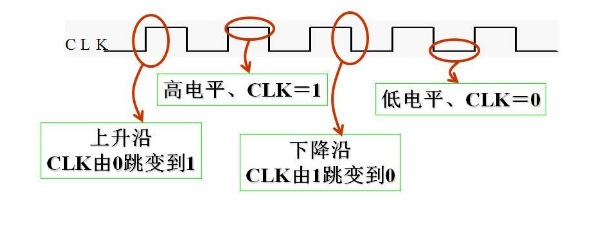

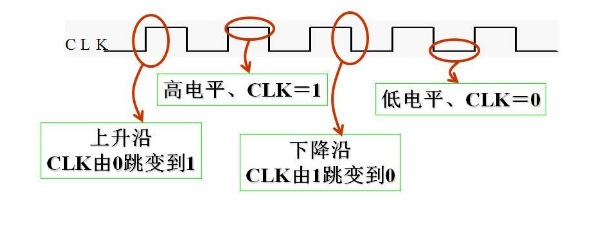

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 69651

69651

边沿触发器只在时钟脉冲CP上升沿或下降沿时刻接收输入信号,电路状态才发生翻转,从而提高了触发器工作的可靠性和抗干扰能力,它没有空翻现象。边沿触发器主要有维持阻塞D触发器、边沿JK触发器、CMOS边沿触发器等。

2018-01-31 09:17:11 28359

28359

触发器分为电平触发和边沿触发两类。电平触发的触发器原理较简单,学习触发器时,一般先学习电平触发。电平触发的触发器主要是基本RS触发器基本RS触发器由电平触发,并且有一个重要的约束条件:/SD和/RD不能同时为零。即:/SD+/RD=1。

2018-01-31 10:26:26 5830

5830

主从触发器可以有效克服钟控触发器的空翻现象,但主从触发器还存在一次翻转现象,降低了抗干扰能力。边沿触发器:只有在CP的上升沿(前沿)或下降沿(后沿)时刻才对输入信号响应(不管CP=1的时间有多长)。在CP=0、CP=1期间,输入信号变化不会引起触发器状态的变化。

2018-01-31 10:38:34 23436

23436

脉冲通常是指电子技术中经常运用的一种象脉搏似的短暂起伏的电冲击(电压或电流)。主要特性有波形、幅度、宽度和重复频率。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 13:41:40 51514

51514

按照稳定工作状态分,可分为双稳态触发器、单稳态触发器、无稳态触发器(多谐振荡器)等;按照逻辑功能划分,可分为RS触发器、D触发器、T触发器、JK触发器等几类;按照电路结构划分,可分为基本RS触发器、同步触发器(时钟控制的触发器)、主从型触发器、维持-阻塞型触发器和边沿触发器等几种类型。

2018-01-31 15:02:50 26914

26914

本文开始介绍了单稳态触发器电路组成和单稳态触发器的四种基本电路图,其次详细阐述了单稳态触发器工作原理,最后介绍了单稳态触发器的作用。

2018-03-27 10:02:25 71864

71864

本文开始介绍了触发器的定义和触发器的特点,其次阐述了触发器的分类和触发器的作用,最后介绍了触发器的工作原理。

2018-03-27 17:35:52 20675

20675 本文开始阐述了单稳态触发器工作特点和单稳态触发器的分类,其次阐述了单稳态触发器工作原理,最后介绍了常用的CD4098单稳态触发器。

2018-03-28 15:41:35 38999

38999

本文主要介绍了单稳态触发器芯片有哪些_单稳态触发器工作原理。单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用

2018-03-28 18:22:32 27878

27878

本文主要介绍了双稳态触发器的工作原理详解。双稳态触发器是脉冲和数字电路中常用的基本触发器之一。双稳态触发器的特点是具有两个稳定的状态,并且在外加触发信号的作用下,可以由一种稳定状态转换为另一种稳定

2018-04-04 10:58:47 95398

95398

数字时序电路中通常用到的触发器有三种:电平触发器、脉冲触发器和边沿触发器。

2019-07-05 14:38:54 13424

13424

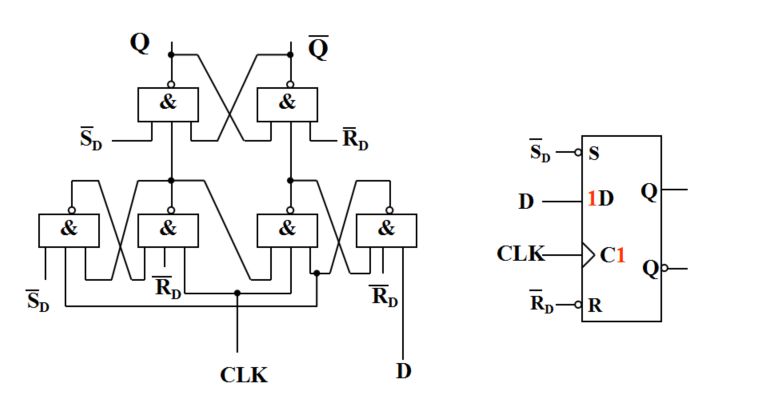

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

2019-07-12 08:50:36 96245

96245

触发器是一种具有记忆功能的逻辑单元电路,它能储存一位二进制码。它具有以下特点:①有两个稳定状态“0”态和“1”态;②能根据输入信号将触发器置成“0”或“1”态;③输入信号消失后,被置成的“0”或“1”态能保存下来,即具有记忆功能。

2019-07-15 08:50:31 7105

7105

当CP的上升沿到达时(CP从0跳转为1的瞬间),门A、C首先被打开,由于G3、G4、传输延迟的存在,输入端J、K的变化不影响G3、G4的输出,S、R仍为1,此时触发器状态仍然保持原态。当延迟过后,触发器仍然保持原态不变,分析过程同CP=1时。因此,当CP为上升沿时触发器保持原态不变。

2019-07-15 09:07:05 26194

26194

在分析维持-阻塞边沿D触发器的工作原理之前,让我们先来看看 R0的复位功能 、S0的置位功能是如何实现的吧。

2020-10-18 11:26:31 21399

21399

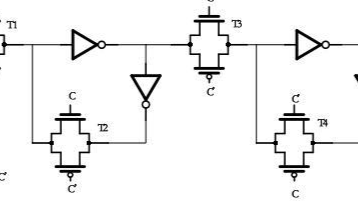

脉冲触发器由两个相同的电平触发的SR触发器组成,其中左SR触发器成为主触发器,右手侧称为从触发器。

2021-02-11 10:56:00 7953

7953

D融发器工作原理及过程说明: SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。 当SD=0且RD=1时,不论输入端D为何种状态,都会

2021-08-09 23:17:49 7776

7776 单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。 单稳态触发器工作原理 微分型单稳态触发器包含阻容元件构成的微分电路。触发器电路

2021-08-12 16:27:26 12953

12953 D触发器也称为“延迟触发器”或“数据触发器”,主要用于存储1位二进制数据,是数字电子产品中广泛使用的触发器之一。除了作为数字系统中的基本存储元件外,D触发器也被视为延迟线元件和零阶保持元件。

2022-10-11 17:21:02 119309

119309

的输出连接,其状态由主触发器的状态决定,称为从触发器。电路结构 主从RS触发器由两个同步RS触发器组成,它们分别称为主触发器和从触发器。反相器使这两个触发器加上互补时钟脉冲。如图7.4.1所示。 工作原理: 当CP=1时,主触发器的输入门G7和G8打开

2022-10-19 19:16:03 22366

22366

具有置位和复位功能的低功耗 D 型触发器;正边沿触发-74AUP1G74

2023-02-07 19:00:58 0

0 八路D型触发器;正边沿触发;三态-74HC_HCT574_Q100

2023-02-07 20:30:25 1

1 八路D型触发器;正边沿触发;三态-74HC_HCT574

2023-02-07 20:30:36 0

0 具有置位和复位功能的低功耗 D 型触发器;正边沿触发-74AUP1G74_Q100

2023-02-09 19:24:01 0

0 2.5 V/3.3 V 16位边沿触发D型触发器;三态-74ALVCH16374

2023-02-15 18:50:05 0

0 16位边沿触发D型触发器;5 V 耐受;三态-74LVC_LVCH16374A_Q10...

2023-02-15 19:19:21 0

0 16位边沿触发D型触发器;5 V 耐受;三态-74LVC_LVCH16374A

2023-02-15 19:19:35 0

0 八路D型触发器;正边沿触发;三态-74HC_HCT374

2023-02-15 19:40:30 0

0 具有 5 V 容限输入/输出的八路 D 型触发器;正边沿触发;三态-74LVC574A

2023-02-15 19:45:21 0

0 八路D型触发器;5 V 容限输入/输出;正边沿触发;三态-74LVC374A

2023-02-15 19:46:37 0

0 3.3V 16位边沿触发D型触发器;三态-74LVT_LVTH16374A

2023-02-15 20:00:35 0

0 八路D型触发器;正边沿触发;三态-74ALVC574

2023-02-16 20:36:27 0

0 八路D型触发器;5 V 容限输入/输出;正边沿触发;三态-74LVC374A_Q100

2023-02-17 19:42:31 0

0 3.3 V 16 位边沿触发 D 型触发器,带 30 欧姆终端电阻;三态-74LVT162374

2023-02-21 18:38:35 0

0 八路D型触发器;正边沿触发;三态-74AHC_AHCT574

2023-02-23 19:18:54 0

0 八路D型触发器;正边沿触发;三态-74AHC_AHCT374

2023-02-23 19:19:29 0

0 触发—时钟脉冲边沿作用下的状态刷新称为触发。

2023-02-27 10:29:57 5573

5573

16位边沿触发D型触发器;3.6 V 耐受;三态-74AVC16374

2023-03-03 18:47:35 0

0 八路D型触发器;正边沿触发;三态-74AHC_AHCT374_Q100

2023-03-03 19:26:52 0

0 16位边沿触发D型触发器;3.6 V 耐受;三态-74AVC16374_Q100

2023-03-03 19:29:48 0

0 在时钟为稳定的0或1期间,输入信号都不能进入触发器,触发器的新状态仅决定于时钟脉冲有效边沿到达前一瞬间以及到达后极短一段时间内的输入信号. 边沿触发器具有较好的抗干扰性能。

2023-03-16 15:35:57 6788

6788

本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

2023-05-22 16:54:29 9071

9071

简单的说触发器实现边沿出发是通过两级锁存器实现的,比如上升沿触发其实是,前一级是低电平锁存,后一级是高电平锁存。

2023-06-28 11:18:32 1054

1054

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 14168

14168

、工作原理、使用场景和实现方法等方面详细介绍插入触发器。 一、触发器的定义 数据库触发器是一种特殊类型的存储过程,它在特定的数据库操作(如插入、更新或删除)发生时自动执行。触发器可以由开发人员在数据库中创建,

2023-11-17 15:48:21 538

538 。本文将详细介绍施密特触发器的工作原理、稳态数以及其应用。 施密特触发器的工作原理 施密特触发器是由约瑟夫·斯密特于1938年提出的,它基于正反馈原理,能够将不稳定的输入信号转换为稳定的输出信号。施密特触发器一般由一

2024-02-04 09:53:12 657

657 单稳态触发器(Monostable Multivibrator)是一种具有两个稳定状态的逻辑电路,其输出在输入触发信号的边沿触发之后会暂时改变,并在一段时间后返回到初始的稳定状态。本文将详细介绍

2024-02-06 11:16:11 259

259 脉冲触发器和边沿触发器是数字电路中常用的存储器元件。它们都是根据输入信号的变化状态进行触发,并且可以实现特定的功能。然而,它们在触发方式、触发条件和触发时机等方面存在一些差异。本文将详细介绍脉冲

2024-02-06 13:45:50 526

526 单稳态触发器,具有一个触发输入(T输入)和一个时钟输入,以及一个输出。T触发器的输出状态取决于其当前状态、触发输入和时钟输入。 工作原理 T触发器的输出状态在时钟输入变为上升沿时根据触发输入的状态进行改变。当触发输入为高电平时,

2024-02-06 14:04:55 419

419

=1时:TG1导通,TG2截止,TG3截止,TG4导通

=1时:TG1导通,TG2截止,TG3截止,TG4导通

:

:

电子发烧友App

电子发烧友App

评论