带宽、采样率和存储深度是数字示波器的三大关键指标。相对于工程师们对示波器带宽的熟悉和重视,采样率和存储深度往往在示波器的选型、评估和测试中为大家所忽视。这篇文章的目的是通过简单介绍采样率和存储深度

2023-09-19 14:43:26 750

750

我的28335用了4个采样通道,其他通道接地。HSPCLK设置成1/6=150MHz,单通道采时,采样率最高到4MHz,应该能到12.5MHz。采样保持周期设为0,1,结果都一样。什么设置会影响到采样率上不去呢?

2018-12-24 14:16:37

各位大侠,STM32F103的ADC时钟和采样率如何设置啊

2012-10-09 23:35:58

字域内复制原始信号,ADC必须至少以输入信号最高频率分量的两倍对输入信号进行采样—否则的话,会产生混叠。所需的最小采样率被称为那奎斯特速率。或者反过来看,ADC能够准确转换的最高频信号为采样率的一半,这

2018-09-06 16:00:00

ADC参数释义AD芯片的选取针对高精度测量类的AD高速 ADC 关键指标的定义

2021-01-25 07:05:15

。基于这些初级采样速率值,考虑到0kHz至25kHz频段,相应的过采样因子约为16或32,处理增益为12dB至18dB,同时还严格按照奈奎斯特定理,简化了常规操作条件下的抗混叠低通滤波器。ADC至DSP

2021-08-04 07:00:00

举个例子;假设ADC现在要转换的输入信号频率为50MHz-70MHz的,该信号带宽是20M ,那我ADC选择时是选用40M采样率的还是采用140M的,之前有看到一篇文档http

2016-04-27 13:04:10

一般在ADC前端都会加抗混叠滤波器。但是,如果不加抗混叠滤波器的话,ADC采集到的信号频谱是不是由无限宽的频谱叠加得到的?比如我拿一个50MHz的ADC采集空中信号,是不是3GHz的信号也会混叠到我采集到的信号中?希望有大神能解答一下,谢谢啦~

2016-11-17 15:22:15

我有一个使用 esp32s3 的应用程序,我想通过 ADC1 对三个通道进行采样。如果我编程 3000 个样本/秒的采样率,是每个通道 3000 个样本/秒还是所有通道 3000 个样本。即我是否

2023-04-13 08:56:13

采样定理-------------被检测信号和ADC采样率的关系?由于盆底肌肉的电信号的频率在 20Hz~500Hz 之间, 所以根据采样定理--------------------------则

2022-05-12 16:43:05

你好,通过看AD7609数据手册,AD7609是一款18位、8通道、真差分、同步采样模数数据采集系统(DAS),有如下几个问题

1、手册里说吞吐速率为200KSPS是不是就是ADC芯片采样率为

2023-11-30 08:24:42

采样率,clk使用BCLK同步,SYNC使用LRCLK,外部的master提供的SCLK=24.576M和49.152M 两种情况,ADC采样I2S out输出信号噪底都比较差,只有65dBFS

2023-11-28 08:19:49

为什么ADUC7060的 adc 采样率为8k,而最新推出的aducm360采样率为3.9k.以后会有升级产品否?

2018-11-16 09:00:25

想问下ADuCM361的ADC采样率和更新速率的区别?看硬件手册和例程里都没找到adc的采样率,光看到设置更新速率,ADC采样率是固定的吗?还是和更新速率有关?

2024-01-11 06:40:53

我没有在数据表或技术参考中找到 C6 的 adc 的最大采样率。有人知道吗?顺便说一下,S3 的 adc 采样率仅支持 100ksps,对于 FOC 电流测量来说有点慢。C6的adc可以像ESP32一样达到2Msps吗?未来的生产是否有可能支持 adc 注入测量?

2023-04-12 07:06:18

本帖最后由 xizhong1991 于 2016-8-18 17:08 编辑

请教各位前辈一个问题 ,我本来的信号的AD采样率是92.16MHz,带宽为5MHz,我用FIR滤波器对它滤波,但是

2016-08-18 17:07:34

2500 Hz 左右的信号,并且 fft 的图也显示了 2500 Hz 左右的混叠。我的 i2s 设置有什么错误吗?将麦克风用作单声道是否会使采样率减半?字选择时钟应该与非 PDM 模式的采样率相同。我播放

2023-04-13 06:35:11

应该给我一个800 kSPS的吞吐量,但我观察到一个低得多的采样率。当我输入一个1千赫的三角波时,我看到混叠,而且每个周期的样本比我预期的要少得多。我显然错过了一些东西,但我不能确定我做错了什么。我

2018-09-19 15:26:33

我想知道ADC10的最大采样率。设备是CY8C21123-24SXIT。当前数据表提到如何计算采样率。但没有最大规格。我可以看到在旧的数据表中最大规格是7.35 kSPS。请告诉我ADC10的最大

2018-11-08 16:59:20

QX320F28335

12位的ADC采样率多少比较适用

2024-02-21 09:43:22

我想请教一下大家,关于RTOS中的ADC采样率是怎么设置的,或者该在哪里去查看adc的这个采样率?

2023-04-07 16:08:11

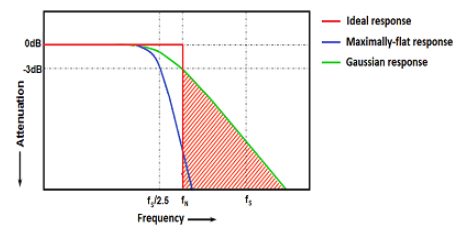

”。首先就是抗混叠电路的需求。例如当电路中的SAR型ADC采样率为fs时,根据香浓采样定律,输入信号的频率需要小于fs/2,频率超过fs/2的信号将会通过混叠效应“混入”有用信号频带中,并且无法区分。因此

2019-08-06 04:45:15

我在双模式下使用 STM32G431 MCU ADC。我试图控制采样率并发现了一个令人沮丧的问题。我不需要扫描多个频道。虽然获得最大采样率或通过预分频器控制采样率的唯一方法是启用扫描模式。这将是一个

2023-02-03 09:30:06

把labview范例改了一下,写了一个电压输出程序,这里有一个采样率,信号生成部分也有一个采样率与采样数不太明白这两者是怎么样的关系?谢谢各位

2018-04-16 22:52:53

各位好!想请教如下问题:在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。我想请教的是:用RC低通滤波的话,转折频率是可以满足,但是RC

2019-05-17 13:30:09

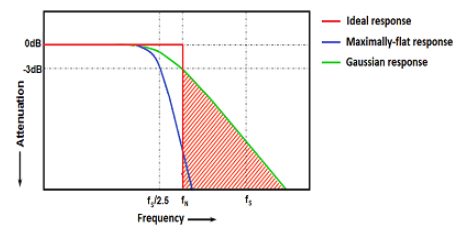

对于示波器而言,带宽、采样率和存储深度是它的三大关键指标。相对于工程师们对示波器带宽的熟悉和重视,采样率和存储深度往往在示波器的选型、评估和测试中被大家忽视。本文的目的是通过简单介绍采样率的相关理论

2019-03-25 16:19:01

你好;为什么ADC的采样率低于DAC。4DSP FMC150高速ADC / DAC FMC模块250 MSPS模数转换器(ADC)800 MSPS,2x / 4x插值数模转换器(DAC)谢谢

2020-03-25 09:46:10

介绍一种包含千兆采样率ADC的系统设计方案

2021-05-14 06:07:02

我有一个带有RF FMC模块的KC705。它们以RF板122.88 MHz提供的默认采样率工作。 RF板上的ADC / DAC为AFE7225,数据采用2线LVDS。参考固件使用IDELAY

2019-09-19 06:03:14

的带宽是100Hz,那么为了避免混叠现象采样频率必须大于200Hz。换句话说就是采样频率必须至少是信号中最大频率分量频率的两倍,否则就不能从信号采样中恢复原始信号。 在模拟视频系统中,采样率定义为帧频

2019-12-19 15:44:20

(时钟)速率和分辨率都是非常关键的参数。本文主要介绍一下采样率和分辨率对于信号发生器输出波形的影响。关键词:信号发生器、Arb、DDS、采样率、16GS/s、分辨率、16bit一、DDS和Arb的原理简介

2017-04-05 15:37:18

速率、所希望的输入带宽,但Σ-Δ ADC比较特殊。这种转换技术采用非常高的输入采样率和转换速率,而后续数字滤波降低了有效吞吐率,这会影响分辨率(动态范围)的提高。Σ-Δ ADC对抗混叠滤波器的要求与输入

2019-01-02 19:03:43

你好!在使用ADXL362三轴加速度计的过程中,无论我如何根据用户手册的说明修改ODR值(我不确定这个值是不是指采样率),我发现采样率无法提高。如此低的采样率不能满足我的需求。我想知道如何提高ADXL362的采样率。谢谢!

2023-12-27 06:35:28

本文利用Matlab设计了一个给定指标的适用于变采样率FIR 滤波器, 并对它进行了FPGA 硬件实现。

2021-04-15 06:26:16

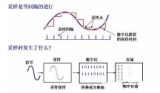

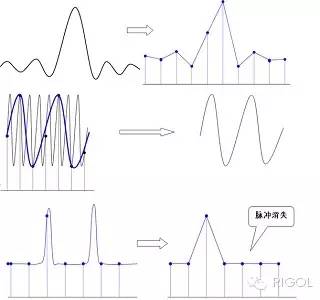

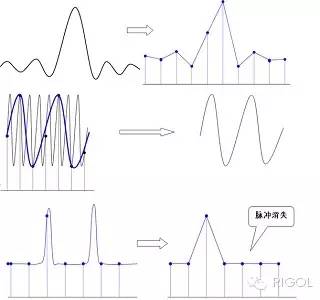

对于示波器而言,带宽、采样率和存储深度是它的三大关键指标。作为示波器关键指标的采样率如果不足会对测试结果有哪些影响呢?首先我们了解下什么是采样和采样率?通俗的讲,采样实际上是用点来描绘进入示波器

2020-02-12 14:26:05

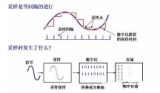

采样率会导致混叠现象。

图4.采样率《2fmax,混叠失真

然而这一定理假设记录长度无穷大及连续信号。由于没有一台示波器能提供无穷大的记录长度,根据定义,毛刺也不是连续的,所以采样率仅为最高

2023-05-06 15:34:16

如果ADC的最大采样率为40Msps,我们可以发送给ADC的最大 IF频率是多少?

2023-03-15 07:02:49

AFAIK IIS2DH 没有模拟抗混叠滤波器。如果我使用低 ODR 设置并且输入信号频率高于 ODR/2,是否会出现混叠?因为在我们的测试中,我们经常在信号输出信号中出现尖峰。如果是这种情况,我们只能提高采样率吗?

2022-12-16 06:38:27

怎样去计算STM32 ADC的采样率呢?ADC采样率最高的时钟是什么?

2021-10-26 08:13:46

你的抗混叠滤波器截止频率。方程式1计算出单极、低通滤波器的截止频率为-3dB:图2.ADC输入上的单极、低通滤波器有时候,一个单极、低通滤波器也许还不够。诸如振动感测等应用也许是用更少的过采样来分析

2018-09-05 14:52:59

,根据要衰减多少频率分量来选择ADC采样率,这些频率分量将混叠到感兴趣的频谱中。假设您使用一阶RC低通滤波器作为抗混叠滤波器,其截止频率为20 kHz。频率响应如下所示:如果以100 kHz采样,则折叠

2020-09-18 10:12:55

中有两种方法可以实现这一点。首先是减少采集存储器的长度。第二种是使用稀疏或抽取函数来抽取数据。降低采样率会增加数据混叠的可能性,尤其是在捕获富含谐波的信号时。为了限制混叠的可能性,可以以高速率对数据进行

2019-02-23 13:41:27

中有两种方法可以实现这一点。首先是减少采集存储器的长度。第二种是使用稀疏或抽取函数来抽取数据。降低采样率会增加数据混叠的可能性,尤其是在捕获富含谐波的信号时。为了限制混叠的可能性,可以以高速率对数据进行

2019-03-09 11:53:43

摘要:在数据采样系统中,高于二分之一采样率的频率成分“混叠”(搬移)到有用频带。大多数时间,混叠是有害的副作用,所以在模/数(AD)转换级之前,将“欠采样”的较高频率简单滤除。但有时候,特意设计利

2019-07-30 06:11:02

,由于时钟信号的周期长度已经跟时钟的上升、下降沿接近,因此此时的时钟信号就变成了正弦波。正弦波时钟信号波形理解了上述关键指标的涵义,就可以看懂所有的数字器件中最重要的时序信息,比如下面就是SPI接口

2019-07-21 21:43:14

嗨,我使用的是SPARTAN 3E XC3500E FPGA,ADC oboard具有3MSPS的差分采样率。但就我的目的而言,我需要采样速率为80MSPS的ADC。是否可以通过从外部连接ADC来

2019-03-28 15:29:37

在应用单片机进行ADC项目设计的时候,结合以前弄的数据采集卡,这里有几个关于ADC采样的几个参数的问题,ADC的采样率,采样数,单次采样,连续采样等,这里想请教高手给指点一下,理解的更加清楚

2023-11-09 07:50:43

分辨率和采样速率是选择模数转换器(ADC)时要考虑的两个重要因素。为了充分理解这些,必须在一定程度上理解量子化和奈奎斯特准则等概念。 分辨率和采样率可能是选择模数转换器(ADC)时要考虑的两个

2023-02-16 18:10:34

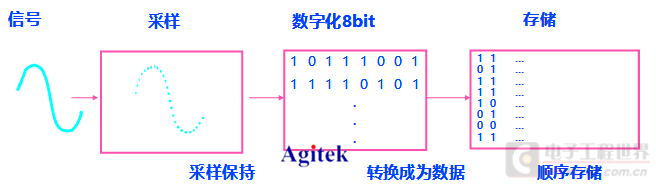

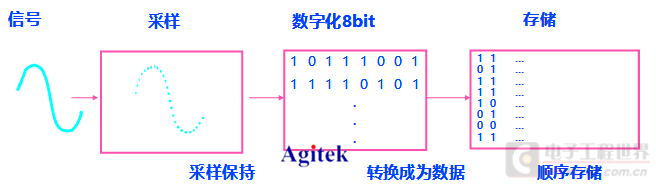

示波器的ADC的采样率,而垂直方向的电压量化级数则取决于ADC的位数。示波器的运作过程大概是这样的:我们通过探头给示波器输入一个信号,被测信号经过示波器前端的放大、衰减等信号调理电路后,然后高速ADC

2020-08-23 16:23:05

我们知道示波器的运作过程大致如下图所示:我们通过探头给示波器输入一个信号,被测信号经过示波器前端的放大、衰减等信号调理电路后,然后高速ADC模数转换器进行信号采样和数字量化,示波器的采样率就是对输入

2021-02-19 14:19:21

80%的工程师使用泰克示波器来加快其设计的调试与测试工作。本文作者——泰克公司大中华区市场开发经理张天生在接受国内某知名媒体专访时就示波器的一些关键指标进行了阐述,并在结尾作了趋势展望。

2019-07-24 06:52:09

。如果采样率低于Nyquist采样率则会导致混叠(Aliasing)现象。由Nyquist定理知道对于最大采样率为10GSa/s的示波器,可以测量最高频率为5GHz的信号,即采样率的一半,这就是示波器

2009-08-25 08:33:40

对于示波器而言带宽、采样率和存储深度是它的三大关键指标。相对于工程师们对示波器带宽的熟悉和重视,采样率和存储深度往往在示波器的选型、评估和测试中为大家所忽视。本文的目的是通过简单介绍采样率

2018-12-04 11:33:46

频段内终止—较低区域内的任何噪声或频率分量也将被混叠进入第一那奎斯特区域。好消息是,如果这是一个第一那奎斯特系统,那么数据转换器的数据速率只是所需RF输入采样率的几分之一。欠采样极大地减少了被提供给

2018-09-05 15:54:06

请问,要搭一个传输链路,链路中的ADC和DAC的参数,比如:采样率和分辨率一定要一样吗?

中频模拟信号,先模数转换数字化进行传输,之后需要数模转换,前后的ADC和DAC采样率和位数是否要完全相等?完全符合指标的器件不太好找。

2023-12-12 06:21:04

我原本ADC的配置如下图所示,用示波器测出来的采样率为3HZ左右。此时ADC读取的数值是正常的(假设我测的ADC为200左右)然后,我采样率提高到100HZ,这是读取的数值就不正常了,直接跳到了30000,并且在0- 30000来回波动。请问我的问题出在哪里呢。

2018-07-31 08:46:57

您好:我在选型高速ADC时,发现datasheet上标注了采样率范围,给出最小值典型值和最大值。比如AD9208,输入时钟最高6GHz,采样率三值分别为2500,3000,3100MSPS。请问

2018-07-30 08:53:53

打算采用AD400系列的adc芯片,考虑到前端电路有建立时间,且ADC最大采样率要小于建立时间的倒数。但是看到datasheet里面没有提及是否可以设置采样率,只说Turbo模式下最大2Msps,正常模式1.5Msps,那要是想设置1Msps该怎么办呢?

2023-12-04 07:47:27

双通道、14 位、3 GSPS 模数转换器 (ADC)。”那么请问这个3GSPS的采样率是射频采样率呢?还是基带或中频采样率?(希望贵公司的相关工程师可以出来介绍一下)另外目前我们团队(中国科学技术大学

2019-01-18 08:16:36

关于AD9684最低采样率,数据手册有两处描述,但是不一致。请问AD9684最低采样率到底是多少?

2023-12-04 06:34:44

DAC的采样率是什么意思?我记得ADC才会有采样率一说,那DAC的采样率是指的什么呢?请详解,谢谢

2019-05-09 11:58:22

我没有在数据表或技术参考中找到 C6 的 adc 的最大采样率。有人知道吗?顺便说一下,S3 的 adc 采样率仅支持 100ksps,对于 FOC 电流测量来说有点慢。C6的adc可以像ESP32一样达到2Msps吗?未来的生产是否有可能支持 adc 注入测量?

2023-02-28 06:26:08

F28335技术手册上面说,内部ADC最高采样率顺序采样可达到8M左右,同步采样可以达到4M左右,我采用的PWM触发其ADC同步采样,只读取一个通道的值,最高采样率可以达到750K,却提高不上去

2018-10-08 17:10:46

大家好!我看一些电能电量分析采集的文献中提到对信号进行FFT,所以要在ADC前端设计抗混叠滤波器,以避免产生延拓频率的噪声。一般采样频率为fs时,滤波器截止频率为fs/2。如果我不对信号进行

2018-10-09 16:08:19

您好, 请问有采样率250MHz左右 分辨率为12位,管脚兼容8位分辨率的adc吗? 谢谢!

2019-02-22 11:53:35

请问,要搭一个传输链路,链路中的ADC和DAC的参数,比如:采样率和分辨率一定要一样吗?中频模拟信号,先模数转换数字化进行传输,之后需要数模转换,前后的ADC和DAC采样率和位数是否要完全相等?完全符合指标的器件不太好找。

2019-01-18 19:45:50

大家好,我的问题与样品率有关。选择任意波形采样率的ADC采样率的标准是什么?在我的例子中,我的WaveDAC(50 KSPS)直接连接到ADC(17位;5kSPS和实际转换率=4935个SPS

2018-12-28 15:26:46

音频功放的关键指标是什么?

2021-06-03 06:00:03

由于拥有较高的分辨率和采样率,SAR型ADC一直被众多工业和汽车客户所亲睐。但是SAR型ADC由于其特殊的特性,所以对外围电路也相应的提出很多“特殊需求”。首先就是抗混叠电路的需求。例如当电路中

2022-11-07 06:09:13

由于ADC产品相对于网络产品和服务器需求小很多,用户和集成商在选择产品时对关键指标的理解难免有一些误区,接下来就这些误区和真正的关键指标做一些探讨

2011-06-13 11:06:32 1288

1288 带宽、采样率和存储深度是数字示波器的三大关键指标。相对于工程师们对示波器带宽的熟悉和重视,采样率和存储深度往往在示波器的选型、评估和测试中为大家所忽视。

2018-03-21 10:10:00 58575

58575

降。这是由于DS1000Z示波器采用了ADC复用的技术,在同时打开四通道时,采样率会下降到250Msa/s。

2019-10-10 15:26:18 17265

17265

ADC是指将连续变化的模拟信号转换为离散的数字信号的器件。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。

2019-12-06 15:04:49 1716

1716 对于示波器而言,带宽、采样率和存储深度是它的三大关键指标。作为示波器关键指标的采样率如果不足会对测试结果有哪些影响呢? 首先我们了解下什么是采样和采样率?通俗的讲,采样实际上是用点来描绘进入示波器

2020-03-13 10:01:07 11074

11074

由于有限的输入带宽,除非您将采样率设置得非常低,否则ADC的带宽通常小于奈奎斯特频率。

2021-01-14 14:35:45 19331

19331

Linux运维中常见的关键指标参数汇总

2021-05-05 09:06:00 1669

1669 adc采样率和带宽的关系 ADC(Analog-to-Digital Converter),即模拟转数字转换器,是将模拟信号转换成数字信号的重要器件。其中,采样率和带宽是ADC性能参数之一,也是

2023-09-12 10:51:12 6012

6012 工业ai质检的关键指标有哪些

2023-11-02 15:10:24 286

286 AD9361是一款高性能的射频前端芯片,广泛应用于无线通信系统中。其中一个重要特性是其具有灵活可调的ADC采样率。本文将详细介绍AD9361的ADC采样率设置范围,包括其相关特性、设置方法以及在实际

2024-01-04 09:37:57 904

904 示波器的三大关键指标有哪些? 示波器是一种用来观察和测量电信号的仪器。它通过显示电压随时间变化的图形,使我们能够观察信号的振幅、频率、相位和波形等特征。在选择和使用示波器时,有三个关键指标需要我们

2024-01-17 15:14:24 276

276 大家在使用ADC采样的时候是否计算过ADC的采样率,这个问题非常关键!

2024-01-23 09:29:47 560

560

电子发烧友App

电子发烧友App

评论