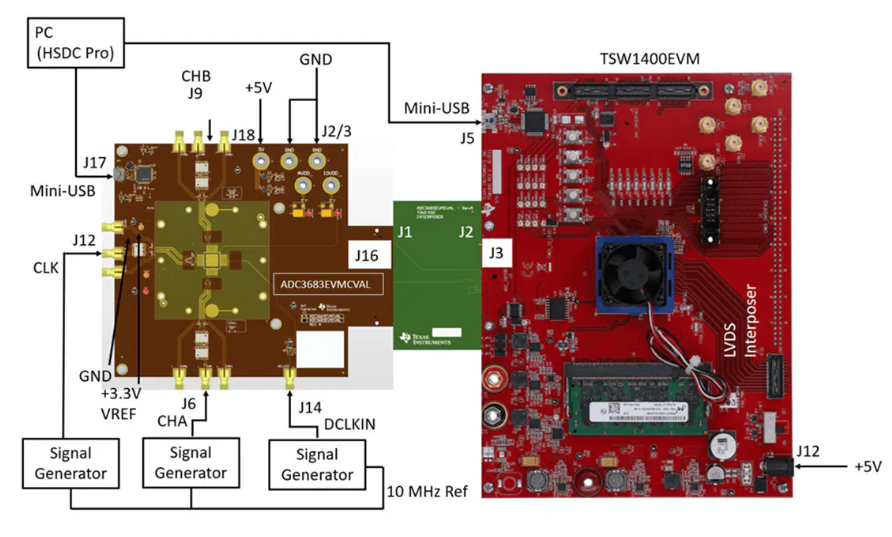

本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点。

2025-07-29 10:01:26 5142

5142

ADC1212D065HN - Dual 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps; CMOS or LVDS DDR digital outputs - NXP Semiconductors

2022-11-04 17:22:44

ADC1213D065C1 - Dual 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps serial JESD204A interface - NXP Semiconductors

2022-11-04 17:22:44

ADC1213S065C1 - Single 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps serial JESD204A interface - NXP Semiconductors

2022-11-04 17:22:44

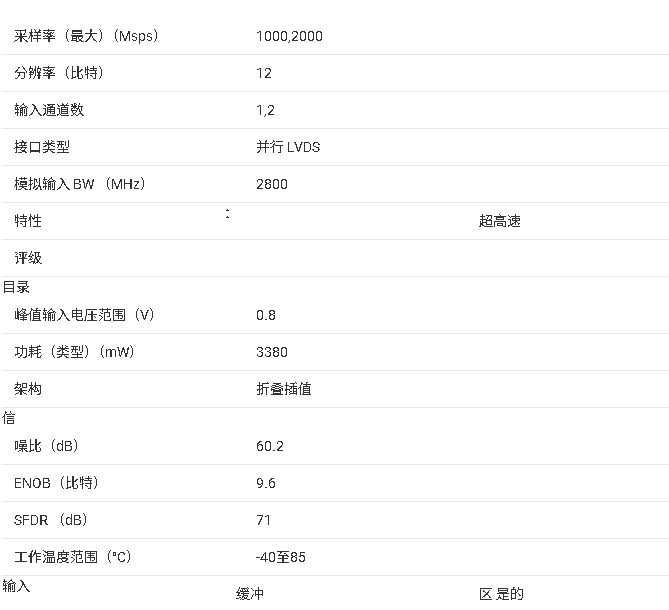

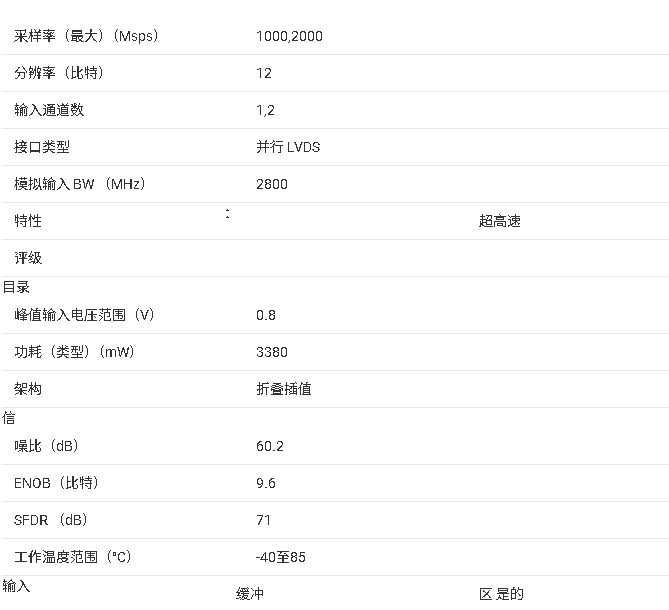

奈奎斯特区之外ADC12D1x00RF提供了一个灵活的LVDS接口,该接口具有多个SPI可编程选项,以简化电路板设计和FPGA / ASIC数据捕获。LVDS输出与IEEE 1596.3-1996兼容,并支持可编程共模电压。该产品采用无铅292球耐热增强BGA封装,额定温度范围为–40°C至85°

2021-01-08 09:15:08

奈奎斯特区之外ADC12D1x00RF提供了一个灵活的LVDS接口,该接口具有多个SPI可编程选项,以简化电路板设计和FPGA / ASIC数据捕获。LVDS输出与IEEE 1596.3-1996兼容,并支持可编程共模电压。该产品采用无铅292球耐热增强BGA封装,额定温度范围为–40°C至85°

2021-01-08 09:15:08

具有优异的噪声和线性性能,扩展了其可用范围超过第三奈奎斯特区。The ADC12D1x00RF provides a flexible LVDS interface which has

2018-07-30 07:21:58

QJ1600EVM,ADC12QJ1600EVM,,现货ADC12QS065CISQ/NOPB,ADC12QS065,-40 to 85,7,173ADC12

2020-12-14 08:56:49

ADC12DL065 Dual 12-Bit, 65 MSPS, 3.3V, 360mW A/D Converter datasheet (Rev. D)

2022-11-04 17:22:44

BOARD EVALUATION FOR ADC12DL065

2023-03-30 11:47:32

ADC12DS065 - Dual 12-Bit, 65/80/95/105 MSPS A/D Converter with Serial LVDS outputs - National Semiconductor

2022-11-04 17:22:44

ADC12QS065 Quad 12-Bit 65 MSPS A/D Converter with LVDS Serialized Outputs datasheet (Rev. I)

2022-11-04 17:22:44

IC ADC 12BIT PIPELINED 60WQFN

2023-04-06 17:07:15

IC ADC 12BIT PIPELINED 60WQFN

2023-03-23 07:44:37

ADC1410S065 - Single 14-bit ADC 65, 80, 105 or 125 Msps CMOS or LVDS DDR digital outputs - NXP Semiconductors

2022-11-04 17:22:44

ADC1413D065 - Dual 14 bits ADC; 65, 80, 105 or 125 Msps; serial JESD204A interface - NXP Semiconductors

2022-11-04 17:22:44

ADC1413D065C1 - Dual 14 bits ADC; 65, 80, 105 or 125 Msps; serial JESD204A interface - NXP Semiconductors

2022-11-04 17:22:44

ADC1415S065 - Single 14-bit ADC 65, 80, 105 or 125 Msps with Input Buffer CMOS or LVDS DDR digital outputs - NXP Semiconductors

2022-11-04 17:22:44

BOARD DEMO FOR ADC1415S065F2

2024-03-14 21:23:12

ADC1415S065HN - Single 14-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Mspswith input buffer; CMOS or LVDS DDR digital outputs - NXP Semiconductors

2022-11-04 17:22:44

(1)ADC、DAC选型时候的有个data input format 是lvds和cmos什么意思啊?1. lvds是不是那个DCO+和DCO-?。这两个信号是不是必须要从时钟专用引脚输入

2017-01-23 15:17:38

这是ADC的lvds时序图,目前遇到的问题时,我用一片Artix-7系列fpga同时采集4篇上述的ADC值,单片adc数据采集是正常的,多篇同时采集时,发现数据就不对了,望大神门帮忙解答使用了IDDR这个原语!

2023-04-17 15:28:34

由于我所采用ADS5240的ADC芯片,采样速率为20M,它输出LVDS电平,不知道选用什么型号的FPGA比较好呢?请各位老师推荐一下。谢谢!

2025-01-23 06:50:31

的EBGA317封装要求严格的电源和信号完整性设计。建议采用多层PCB布局,确保低阻抗电源和接地平面,减少信号串扰,优化时钟分配网络,降低时钟抖动对采样精度的影响。热管理策略高速ADC功耗高,需有

2025-12-31 09:18:18

布局布线组合在一起。一个星期之后,对第一个原型电路板进行测试。出乎预料的是,电路板性能与预期的不一样。 这种情景在你身上发生过吗? 最优PCB布局布线对于使ADC达到预期的性能至关重要。当设计包含

2018-09-18 15:44:13

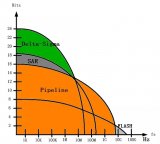

Brad Brannon,ADI公司系统应用工程师如此之多的模数转换器(ADC)可供选择,我们总是很难弄清哪种ADC才最适合既定应用。数据手册往往会使问题变得更加复杂,许多技术规格都以无法预料的方式

2018-10-26 10:49:24

总是很难弄清哪种ADC才最适合既定应用。数据手册往往会使问题变得更加复杂,许多技术规格都以无法预料的方式影响着性能。选择转换器时,工程师通常只关注分辨率、信噪比(SNR)或者谐波。这些虽然很重要,但其他

2017-04-04 12:51:19

能力比较重要,但最佳性能一般会发生在未达到完全驱动能力时。在高性能应用中,重要的是,将输出负载降至最低并提供适当的去耦和优化布局,以尽可能降低电源上的压降。为了避免此类问题发生,许多转换器都提供LVDS

2018-11-01 11:11:27

∑一△ADC原理是什么?LVDS收发器标准及其原理是什么?如何利用LVDS接收器去实现ADC?

2021-06-03 06:23:35

亲爱的大家,我的问题是如何通过LVDS将ADC AFE 5804 12位http://www.ti.com/product/afe5804连接到Spartan 3E入门套件。首先,我想模拟知道ADC

2019-07-10 08:19:23

,BANK12的供电是2.5V的

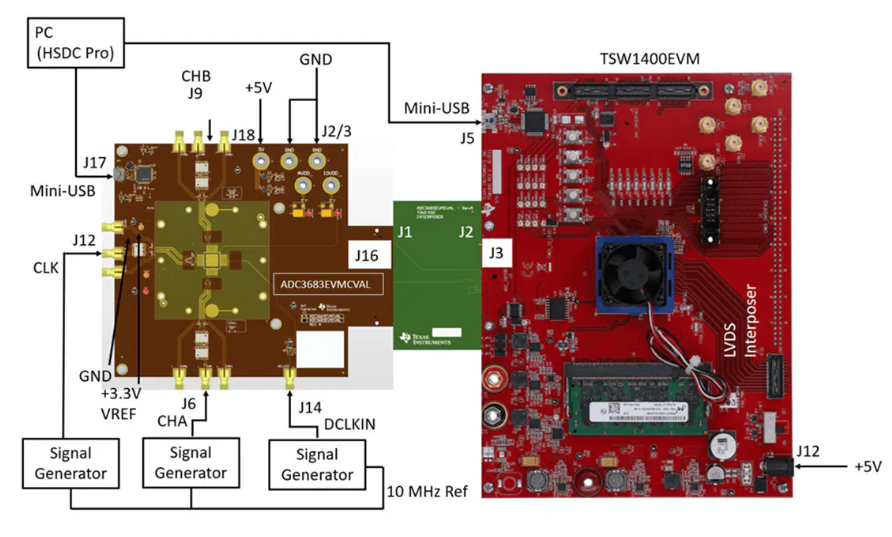

下图是ZYNQ-7000的LVDS接口电平要求

下图是ADC3663的LVDS接口电平要求

目前的设计是串联电阻,串联电阻对Layout有些不友好

所以想请教一下当ADC3663的LVDS输出给到ZYNQ-7000的LVDS接收这两者之间可以直连吗?

2024-11-14 07:43:06

、处理并消耗功率传输宽带频谱的效率很低。没有必要在后期处理中使用大量FPGA收发器来抽取和过滤宽带数据。高性能GSPS ADC让数字下变频(DDC)进驻到ADC内部。减少JESD204B ADC输出通道数可以最大限度地降低数据速率和系统布局的复杂度。

2019-07-22 08:41:38

`各位大神,问一个简单的问题。图中c48和c63是信号进入ADC的RC滤波电路的电容。关于这个电容,应该是要靠近ADC的输入引脚的吧?这两种布局方式在滤波效果上有明显的不同吗?RC滤波电路的R的布局有没有特殊的要求呢,它的位置是也是需要靠近输入引脚吗?还是随意。`

2018-08-11 10:17:42

为什么经过ADC采样后,我用matlab仿真后,底噪在-100左右,而ADC芯片资料上都在-120左右,请问如何降低ADC的底噪?analogchina-admin

2018-08-09 08:40:04

为什么经过ADC采样后,我用matlab仿真后,底噪在-100左右,而ADC芯片资料上都在-120左右,请问如何降低ADC的底噪?

2023-12-12 06:56:44

的LVDS数值的幅值是多少呢?我的理解是:LNA输出的给ADC的峰峰值是2Vpp,由于ADC采用12位位宽,最高位为符号位,那么0-1V,就对应0-2047数字量,所以+50mV/-50mV对应LVDS

2024-12-04 06:08:12

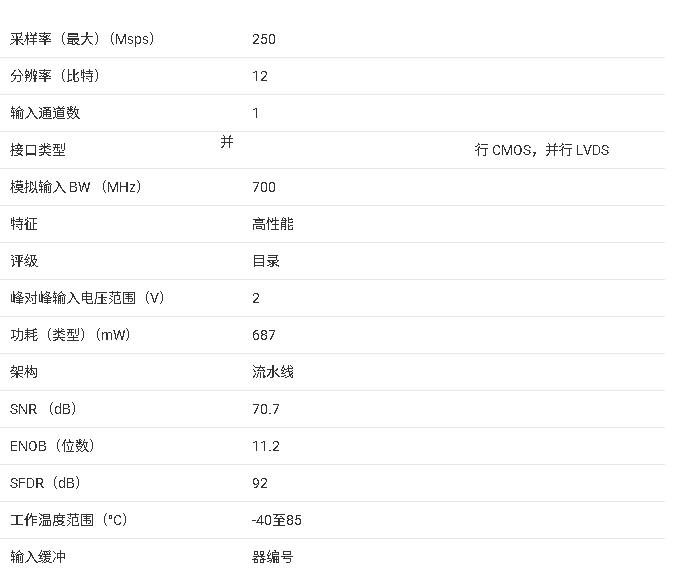

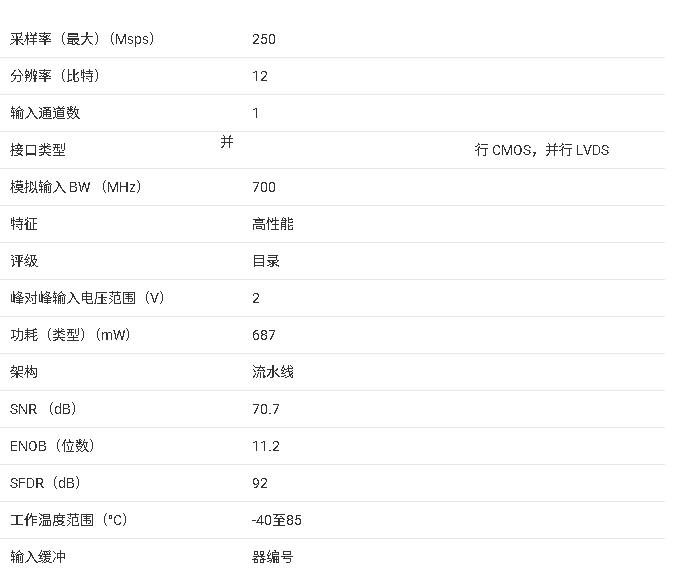

四通道、12 位、65MSPS 模数转换器 (ADC) Sample rate (Max) (MSPS) 65 Resolution (Bits) 12 Number

2022-12-06 09:46:42

The ADC12DL065 is a dual, low power monolithic CMOSanalog-to-digital converter capable

2009-10-10 09:43:57 13

13 The ADC12V170 is a high-performance CMOS analog-todigitalconverter with LVDS outputs. It is capable

2009-10-10 09:47:49 13

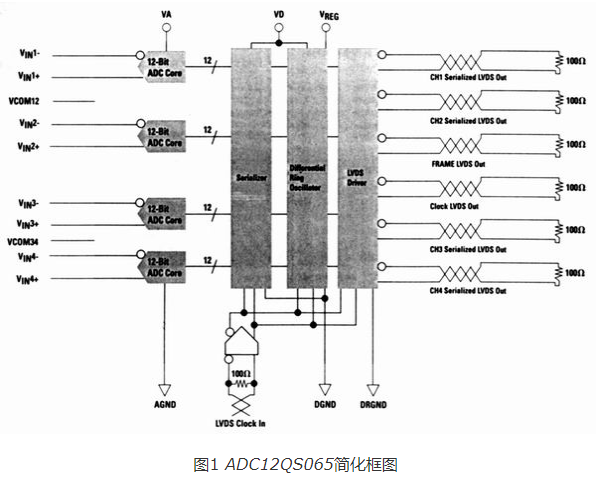

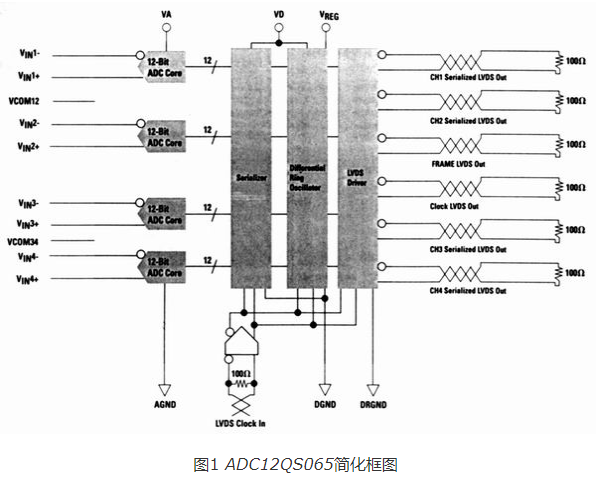

13 The ADC12QS065 is a low power, high performance CMOS4-channel analog-to-digital converter with LVDS

2009-10-10 10:10:06 8

8 The ADC10DL065 is a dual, low power monolithic CMOSanalog-to-digital converter capable

2009-10-10 10:27:13 10

10 The ADC12030, and ADC12H030 families are 12-bit plus signsuccessive approximation Analog-to-Digital

2009-10-10 10:48:44 12

12 ADC12D1000

2010-05-27 15:55:46 17

17 ADI ADC PCB布局方法,值得参考

2016-05-23 16:25:31 75

75 超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解码两方面,详述了实现LVDS数据接收应该注意的问题及具体实现方法,并进行实验测试、验证了方法的正确性。

2017-11-17 10:40:01 8505

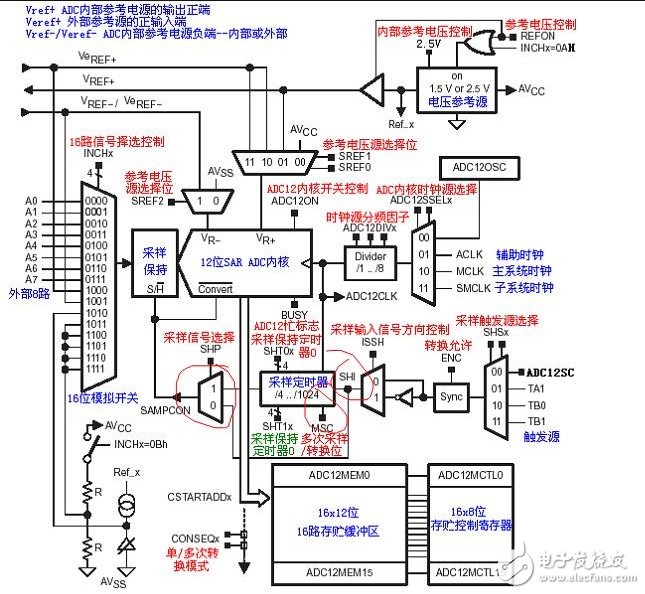

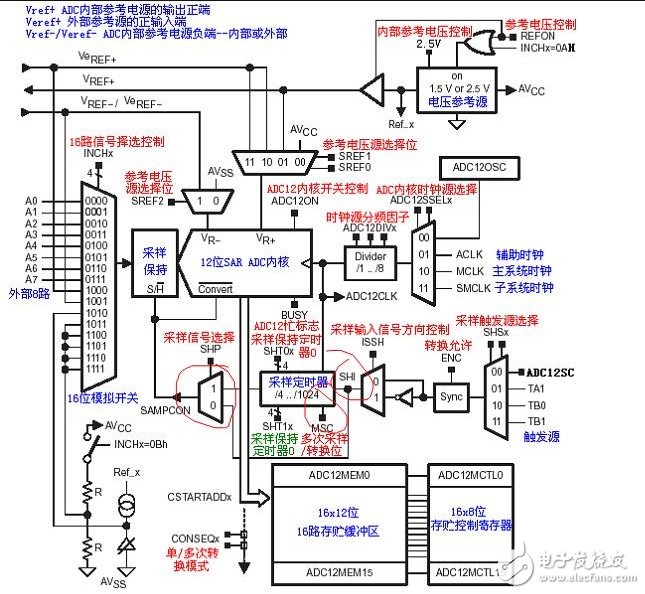

8505 ADC12是一个多源中断:有18个中断标志(ADC12IFG.0~ADC12IFG.15与ADC12TOV,ADC12OV),但只有一个中断向量。所以需要 设置这18个标志的优先级顺序,按照优先级顺序安排中断标志的响应,高优先级的请求可以中断正在服务的低优先级。

2018-04-10 17:55:02 12115

12115

msp430内部含有 ADC12模块,可以完成12位的模数转换,当对精度或其他指标要求不高时,可以选用430单片机内部的 ADC12完成模数转换工作。

2018-05-04 09:40:17 6

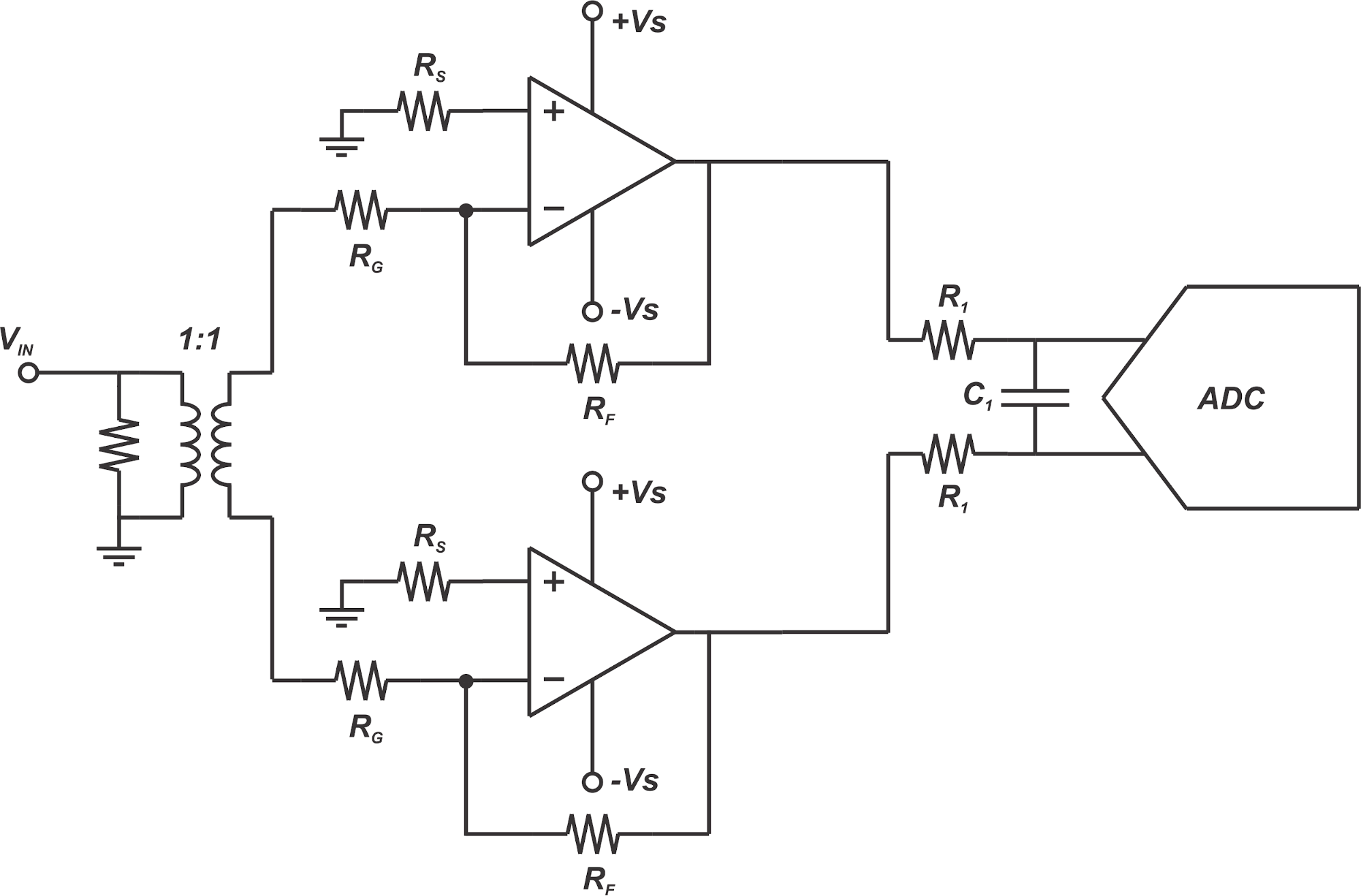

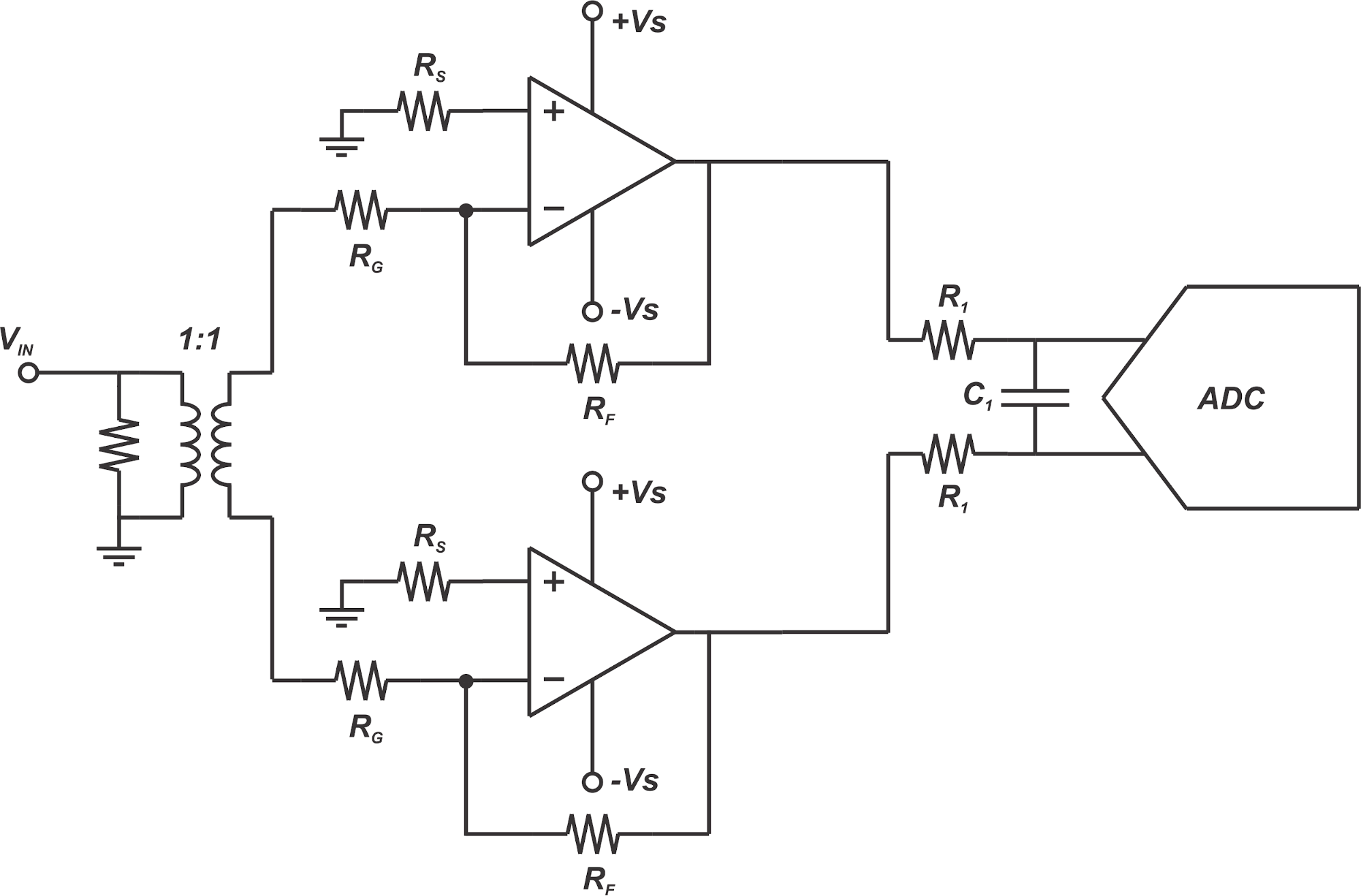

6 设计、差分输入驱动器的设计、数字接口和布局考虑都是十分复杂的问题。本文中的参考设计将采用ADC083000/B3000。

2019-05-30 08:18:00 5220

5220

电子发烧友网为你提供TI(ti)ADC12D1600QML-SP相关产品参数、数据手册,更有ADC12D1600QML-SP的引脚图、接线图、封装手册、中文资料、英文资料,ADC12D1600QML-SP真值表,ADC12D1600QML-SP管脚等资料,希望可以帮助到广大的电子工程师们。

2018-11-02 19:01:06

在输入信号转换数字数据之后,必须传输它们到DSP或ASIC/FPGA进行处理。流行的全差分输出信号传输是方便的。全差分的输出信号通过两条对称线给出和吸收电流。这种信号传输的一个例子是LVDS(低压差分信号)格式。ADC12QS065用LVDS来解决所有这些系统问题(图1)。

2020-04-04 17:43:00 3015

3015

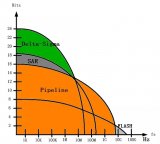

Sigma-Delta ADC是一种目前使用最为普遍的高精度ADC结构,在精度达到20位以上的场合,Sigma-Delta是必选的结构。通过采用过采样、噪声整形以及数字滤波技术,降低对模拟电路的设计要求,实现了其他类型的ADC无法达到的高精度和低功耗。

2020-10-02 17:57:00 90309

90309

时,ADC 采样、处理并消耗功率传输宽带频谱的效率很低。没有必要在后期处理中使用大量 FPGA 收发器来抽取和过滤宽带数据。高性能 GSPS ADC 让数字下变频(DDC)进驻到 ADC 内部。减少 JESD204B ADC 输出通道数可以最大限度地降低数据速率和系统布局的复杂度。抽取是

2020-11-25 09:13:00 20

20 AD9229:4通道、12位、50/65 MSPS、串行LVDS、3 V ADC

2021-03-19 13:23:40 8

8 AN-1142: 高速ADC PCB布局布线技巧

2021-03-20 22:11:52 33

33 AN-880: 温度测量系统对ADC的要求

2021-03-21 02:20:31 2

2 AD9222:8通道、12位、40/50/65 MSPS、串行LVDS、1.8 V ADC 数据手册

2021-03-21 09:24:35 7

7 ADC824:MicroCont824:MicroConverter/SoP/FUP-24位ADC-16-ADC-12-BIDAC-MCU数据-

2021-04-15 19:36:10 10

10 ADC824 Microcomporter,24位ADC,16位ADC,12位DAC,Flash MCU数据Sheet

2021-06-18 13:00:31 13

13 ADC芯片需求驱动(电源技术研讨会)-ADI常用芯片adc驱动程序,C语言,可以借鉴使用。

2021-09-15 13:21:22 19

19 最先进的每秒 112 吉比特 (Gbps) 长距离 (LR) SerDes PHY 的设计要求将模数转换器 (ADC) 的位数降至最低,以实现整个系统占用最小的面积和消耗最小的功率。为此,利用

2022-07-28 08:03:10 2303

2303 本文介绍了一种 12 位 10GS/s 交错 (IL) 流水线模数转换器 (ADC)。该 ADC 采用 4 GHz 输入信号实现 55 dB 的信噪比和失真比 (SNDR) 和 66 dB 的无杂散动态范围 (SFDR),采用 28 nm CMOS 技术制造,功耗为 2.9 W。

2022-12-15 16:32:33 4302

4302

PCB布局是优化高速板线性度性能的关键因素。 本系列的前几篇文章讨论了减少二次谐波失真的一些基本技术。 这篇文章,灵感来自TI文档”高速印刷电路板布局技术“,试图详细讨论如何在高速差分ADC驱动器中

2023-01-27 09:29:00 2217

2217

ADC12DJ3200EVM 供应商 ADC12DJ3200EVM怎么订货 ADC12DJ3200EVM 价格

2021-12-22 16:23:41 1445

1445

本文给大家分享串行ADC布局布线设计要点!

2023-07-10 16:54:38 2338

2338

了 TI GSPS ADC 的超大奈奎斯特区,在射频频率下具有出色的噪声和线性度性能,将其可用范围扩展到第 7 奈奎斯特区之外ADC12D800。LVDS输出与IEEE1596.3-1996兼容,并支持可编程共模电压。该产品采用无铅292球耐热增强型BGA封装,额定工业温度范围为-40°C至+85°C。

2023-09-20 15:02:52 0

0 、精密ADC和集成ADC等,主要应用于医疗仪器、测试仪器、音频处理和工业系统等领域,具有高稳定性、高精度和低噪声等特点。 ADC芯片具有多种结构,今天我们就来说一下ADC的五种结构: 1、FLASH 2、Folding 采用折叠型等结构的高速ADC,其速率同样可以达到10GSps以上

2023-10-09 16:01:04 3626

3626 电子发烧友网站提供《ADC12DL065低功耗、单芯片CMOS模数转换器数据表.pdf》资料免费下载

2024-07-22 10:43:06 0

0 电子发烧友网站提供《ADC12D500RF, ADC12D800RF 12位1.6/1.0 GSPS RF采样ADC数据表.pdf》资料免费下载

2024-07-22 10:28:07 2

2 电子发烧友网站提供《ADC12QS065四通道12位65 MSPS模数转换器数据表.pdf》资料免费下载

2024-07-25 10:24:34 0

0 电子发烧友网站提供《ADC12Jxx00 12位1.6或2.7GSPS ADC数据表.pdf》资料免费下载

2024-07-25 10:27:41 0

0 电子发烧友网站提供《ADC10DL065低功耗、单芯片CMOS模数转换器数据表.pdf》资料免费下载

2024-07-29 10:51:28 0

0 在现代电子设计中,ADC芯片扮演着至关重要的角色,它们将模拟信号转换为数字信号,以便微处理器或数字电路可以处理。选择合适的ADC芯片不仅能够提高系统性能,还能降低成本和功耗。 1. 确定应用需求 在

2024-10-31 10:33:31 2059

2059 电子发烧友网站提供《ADC12J2700EVM和ADC12J1600EVM用户指南.pdf》资料免费下载

2024-12-10 14:59:05 0

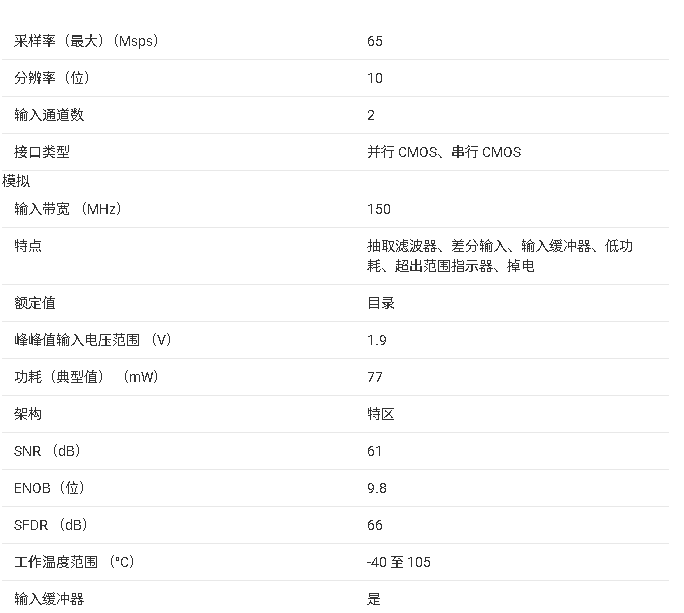

0 号(LVDS)接口输出数字数据。串行化LVDS接口支持高达1Gbps的输出速率。Texas Instruments ADC36XXQML-SP可使用内部抽取滤波器以过采样+抽取模式运行,以提高动态范围并放松外部抗混叠滤波器。

2025-09-04 15:43:30 676

676

ADC3910Dx 和 ADC3910Sx 是系列超低功耗 10 位 125MSPS 高速单通道和双通道模数转换器。高速控制环路受益于仅 1 个时钟周期的短延迟。ADC在125Msps时仅消耗92mW,功耗随较低采样率而变化。

2025-10-24 14:36:21 681

681

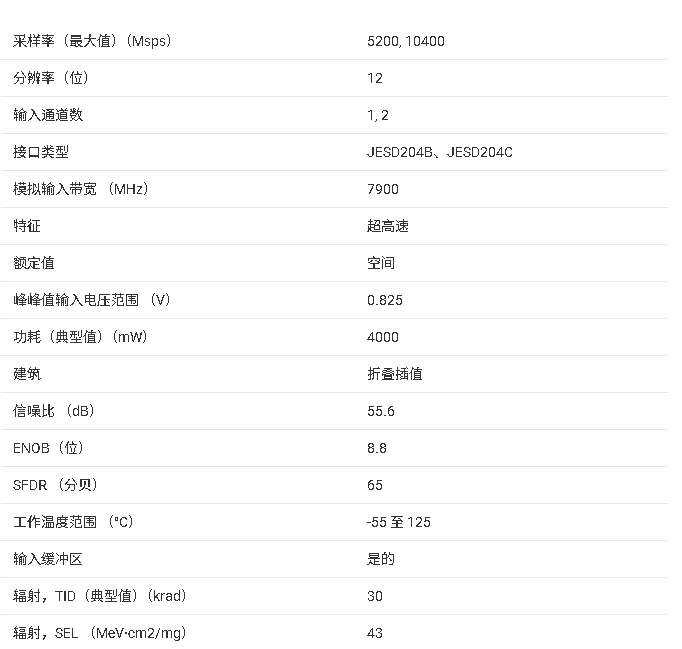

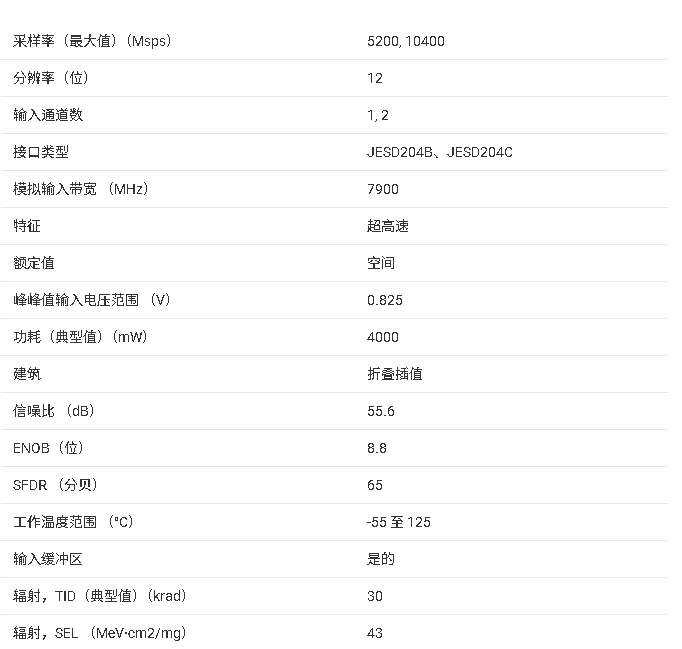

ADC12DJ5200-SEP器件是一款射频采样千兆采样模数转换器(ADC),可直接对从直流到10GHz以上的输入频率进行采样。ADC12DJ5200-SEP可配置为双通道5.2GSPS ADC或

2025-10-28 09:25:51 528

528

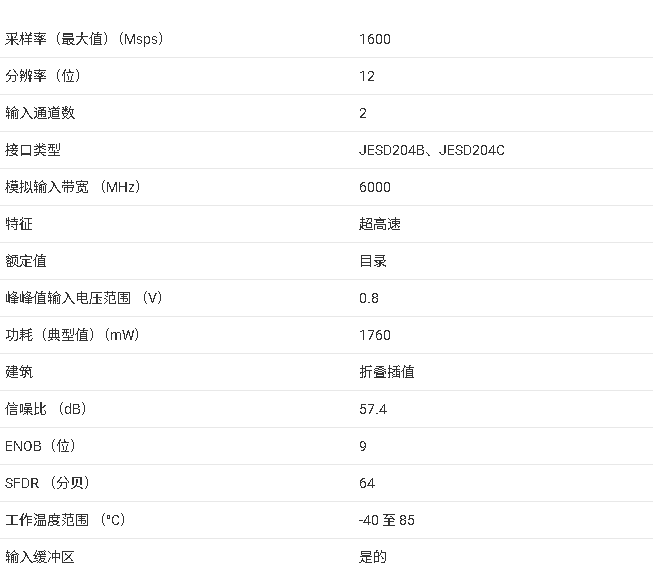

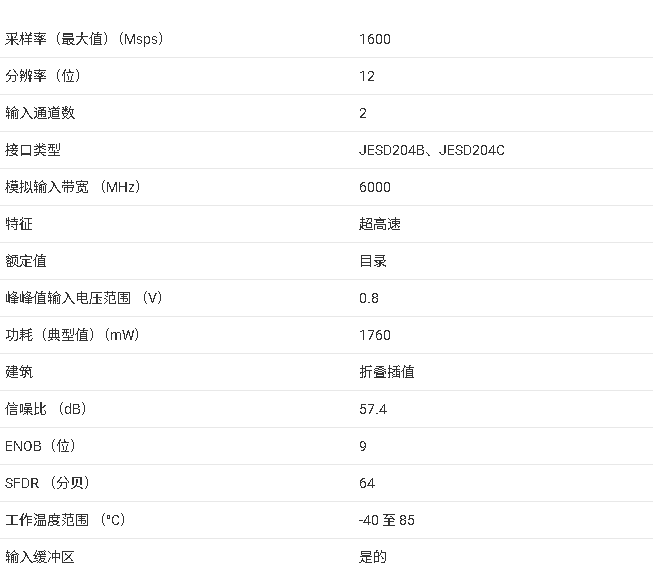

ADC12xJ1600 是四通道、双通道和单通道、12 位、1.6GSPS 模数转换器 (ADC) 系列。低功耗、高采样率和 12 位分辨率使 ADC12xJ1600 适用于各种多通道通信和测试系统。

6GHz的全功率输入带宽(−3dB)支持L波段和S波段的直接RF采样。

2025-10-31 11:20:51 966

966

ADC12DJ4000RF器件是一款射频采样千兆采样模数转换器(ADC),可直接对直流至10 GHz以上的输入频率进行采样。ADC12DJ4000RF可配置为双通道、4 GSPS ADC或单通道、8

2025-10-31 13:59:41 453

453

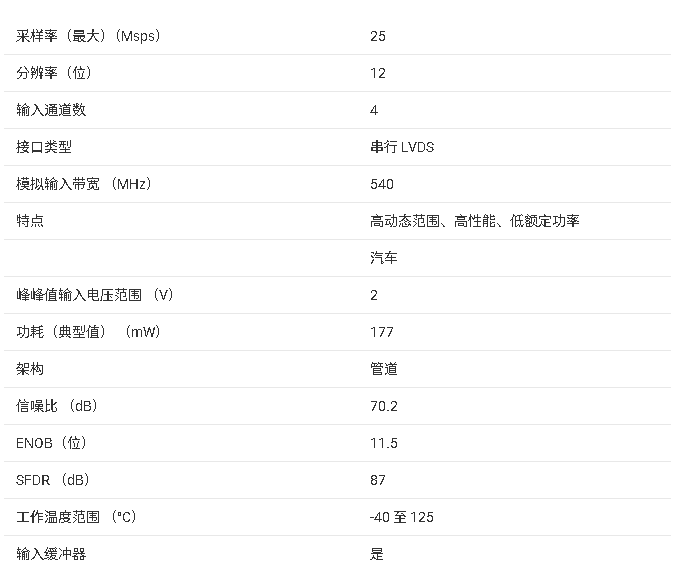

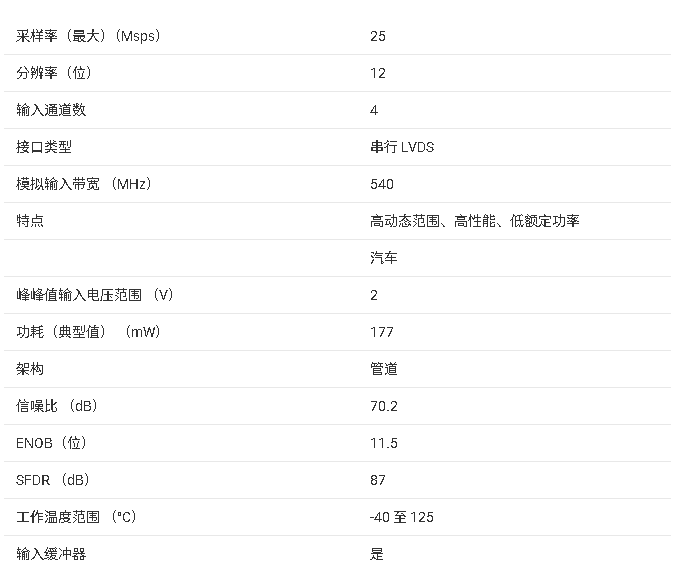

ADC3421-Q1 是一款汽车级、高线性度、超低功耗、四通道、12 位、25 MSPS 模数转换器 (ADC)。该器件专为支持具有大动态范围要求的高输入频率信号而设计。输入时钟分频器为系统时钟

2025-11-03 15:33:50 453

453

与ADC12D1600QML相比,该ADC12D1620QML采用封装重新设计,以实现更好的ENOB、SNR和X-talk。与其前身一样,该ADC12D1620QML是一款低功耗、高性能CMOS

2025-11-07 14:03:05 488

488

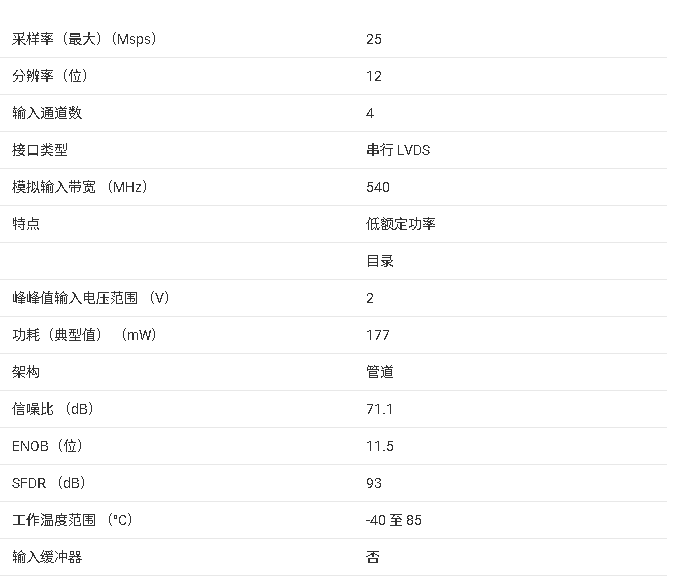

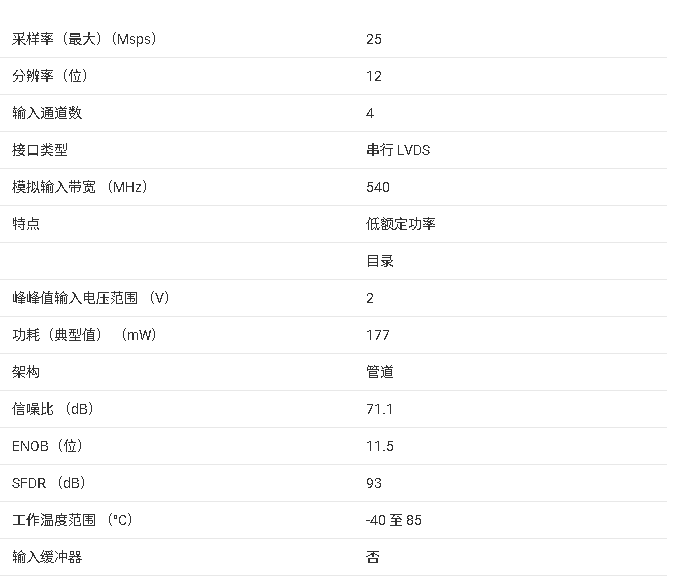

ADC342x是一款高线性度、超低功耗、四通道、12位、25MSPS至125MSPS模数转换器(ADC)系列。这些器件专为支持具有大动态范围要求的苛刻高输入频率信号而设计。输入时钟分频器为系统时钟

2025-11-11 13:54:59 449

449

ADC322x 是一款高线性度、超低功耗、双通道、12 位、25 MSPS 至 125 MSPS 模数转换器 (ADC) 系列。这些器件专为支持具有大动态范围要求的苛刻高输入频率信号而设计。输入

2025-11-12 11:03:56 476

476

12位1.6/1.0 GSPS ADC12D800/500RF是一种射频采样GSPS的ADC,可以直接实现 采样输入频率最高可达2.7 GHz及以上。ADC12D800/500RF增强了非常大

2025-11-18 15:15:13 434

434

ADC12D800/500RF提供灵活的LVDS接口,支持多个SPI可编程选项,便于板上设计和FPGA/ASIC数据采集。LVDS输出为兼容IEEE 1596.3-1996,并支持可编程共模电压。该产品采用无铅292球热增强BGA封装,覆盖工业级温度范围为-40°C至+85°C。

2025-11-19 09:25:42 367

367

12位、3.6 GSPS ADC12D1800是 TI 超高速 ADC 家族的最新进展,基于 10 位 GHz 系列 ADC 的特性、架构和功能。

ADC12D1800提供灵活的LVDS接口

2025-11-20 10:19:37 413

413

12位、2.0/3.2 GSPS ADC12D1x00 设备是 TI 超高速技术的最新进展 ADC系列,基于10位GHz系列的特性、架构和功能 ADC的。

ADC12D1x00 提供了灵活

2025-11-20 10:42:44 448

448

的 LVDS 接口,支持多个可编程 SPI 这些选项用于促进板设计和FPGA/ASIC数据采集。LVDS输出兼容以下 IEEE 1596.3-1996,并支持可编程共模电压。

ADC12D1x00采用带铅或无铅的292针热增强BGA封装 封装覆盖在额定工业温度范围内的-40°C至85°C范围内。

2025-11-21 15:42:17 601

601

ADS614X/2X具有细微增益选项,可用于提升SFDR在较低全声量输入范围的性能。它包含一个直流偏移校正环路,可用于取消ADC偏移。同时提供DDR LVDS(双倍数据速率)和并行CMOS数字输出接口。在较低采样率下,ADC自动以降低功率运行,性能不损失。

2025-11-25 09:41:39 303

303

ADS614X/2X具有细微增益选项,可用于提升SFDR在较低全声量输入范围的性能。它包含一个直流偏移校正环路,可用于取消ADC偏移。同时提供DDR LVDS(双倍数据速率)和并行CMOS数字输出接口。在较低采样率下,ADC自动以降低功率运行,性能不损失。

2025-11-25 11:17:48 336

336

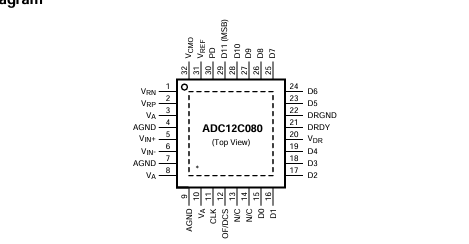

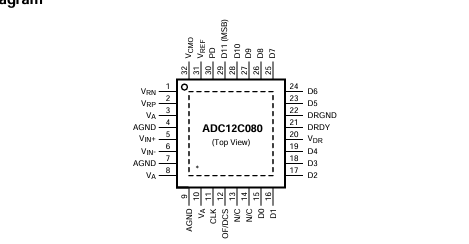

。 文件下载: adc12c080.pdf 一、ADC12C080概述 ADC12C080是一款采用CMOS工艺的高性能模数转换器,能够以高达80MSPS的速率将模拟输入信号转换为12位数字字。它采用了差分流水线架构,并具备数字误差校正功能和片上采样保持电路,在降低功耗和外部元件数量的同时,还能

2025-11-27 11:33:13 471

471

。 文件下载: adc10dl065.pdf 一、产品概述 ADC10DL065采用单+3.3V电源供电,具备内部采样保持电路、内部参考输出,支持2.4V至3.6V的电源范围,还有掉电模式、占空比稳定器以及

2025-11-29 11:14:49 959

959

、360mW的A/D转换器,它在众多领域都有着广泛的应用。 文件下载: adc12dl065.pdf 一、产品概述 ADC12DL065采用单+3.3V电源供电,具备内部采样保持电路和内部参考输出,参考输出

2025-12-01 13:54:45 341

341

,具有LVDS串行输出,广泛应用于超声、医疗成像、通信等多个领域。 文件下载: adc12qs065.pdf 一、产品概述 ADC12QS065采用单+3.3V电源供电,内部集成了采样保持电路和参考电压源,具有低功耗的特点。它还支持掉电模式,在不进行转换时可显著降低功耗。其时钟和数据帧时序设计使

2025-12-03 10:07:26 516

516

探索ADC12130/ADC12132/ADC12138:高性能12位A/D转换器的技术剖析 在电子设计领域,模拟 - 数字转换器(ADC)是连接模拟世界和数字世界的关键桥梁。德州仪器(TI

2025-12-10 10:35:02 376

376

电子发烧友App

电子发烧友App

评论