赛灵思 PCI Express IP 随附以下集成调试功能。

JTAG 调试器

启用 In-System IBERT

第三代模式解扰器

“JTAG 调试器 (JTAG Debugger)”可提供以下信息来帮助调试 PCI Express 链接训练问题:

LTSSM 状态的图形化视图

PHY RST 状态机的状态

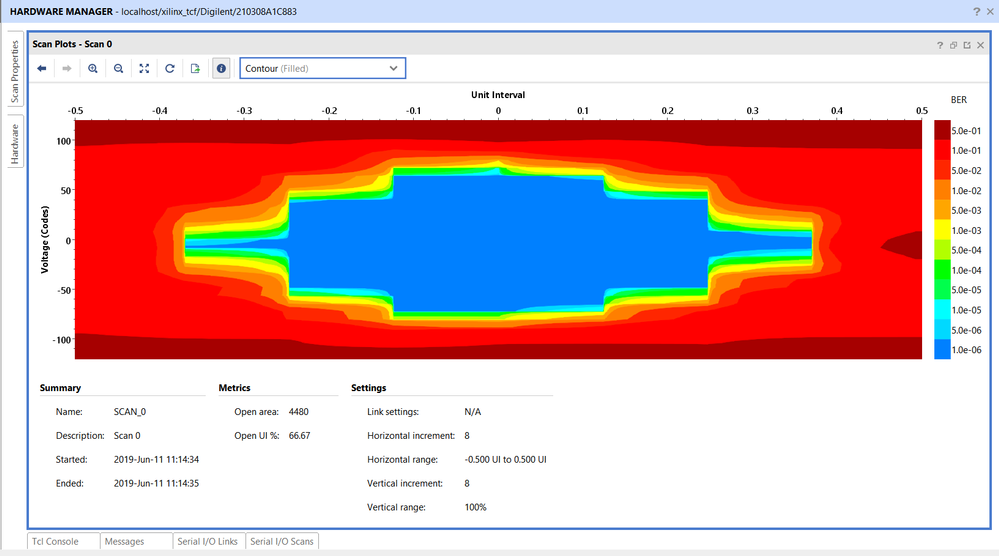

In-system IBERT 可提供 PCIe 链接眼图。“JTAG Debugger”和“In-system IBERT”功能结合在一起即可提供即时信息,用于判断链接训练问题的可能原因。在本篇博文中,我们将讲解如何使用这些功能。本篇博文基于赛灵思 VCU118 开发板随附的 UltraScale+ 器件。

“第三代模式解扰器 (Gen3 Mode Descrambler)”选项可提供发生扰码的 PIPE 数据的解码接口。它允许用户查看 PCIe 链接上的数据包。如需了解有关该功能以及数据包解码方法的详细信息,请参阅博文(链接如下)。

https://forums.xilinx.com/t5/Design-and-Debug-Techniques-Blog/Demystifying-PIPE-interface-packets-using-the-in-built/ba-p/980246

IP 配置 GUI 包含“添加调试选项 (Add. Debug Options)”选项卡。请选中“启用 JTAG 调试器 (Enable JTAG Debugger)”。

在GUI 中配置其它 IP 参数后,生成 IP 并打开示例设计。

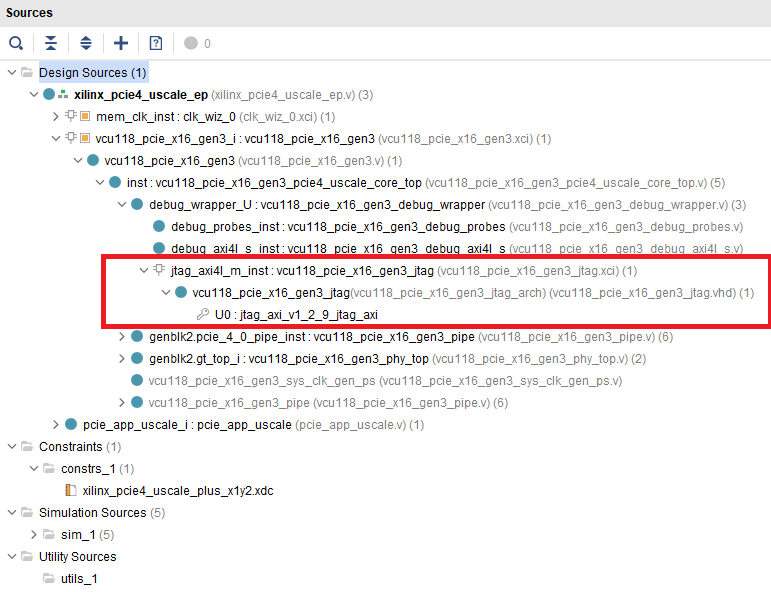

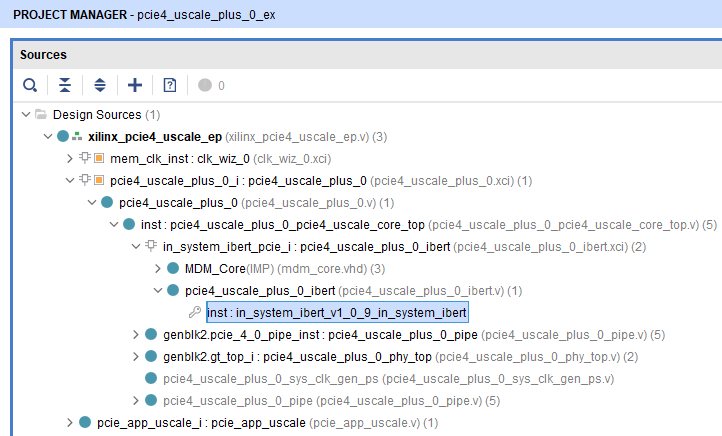

请确保在设计示例的“Design Sources”层级中包含调试封装模块,如下所示:

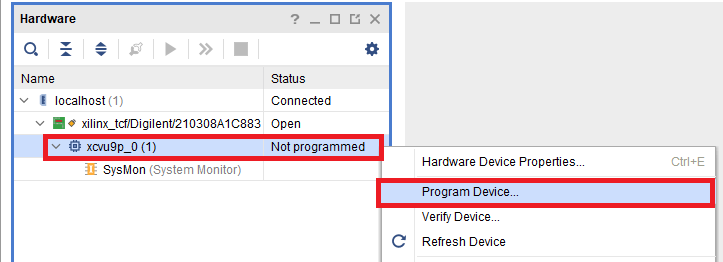

请选择正确的比特文件和 .ltx 文件,以生成比特流并对器件进行编程。

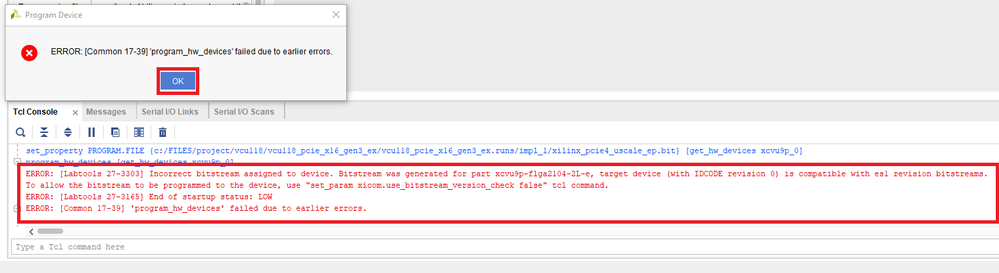

根据所使用的 Vivado 工具版本,您可能会看到如下错误。

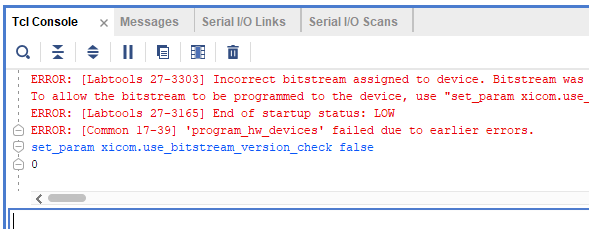

如果看到以上错误消息,请在 Vivado Tcl Console 中运行以下命令。

set_param xicom.use_bitstream_version_check false

对器件重新进行编程。

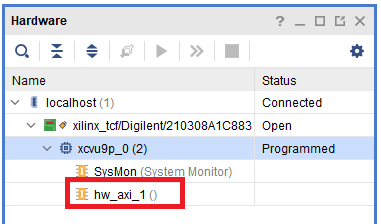

成功完成目标器件编程后,应在硬件窗口中显示 AXI 核“hw_axi_1”。

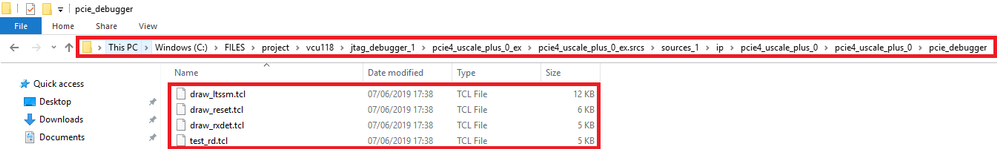

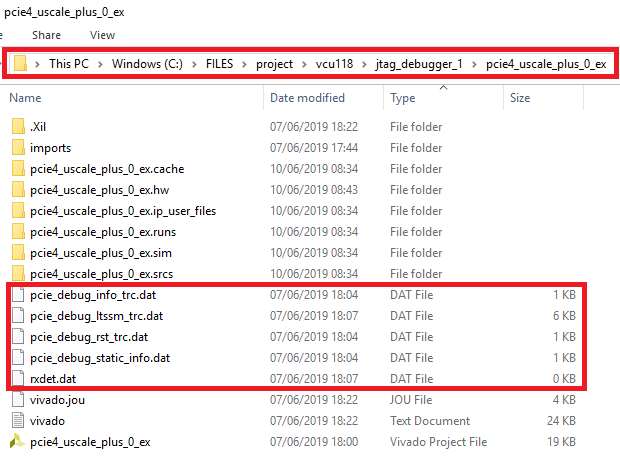

在工程目录中如下所示位置下,您将找到 4 个 .tcl 文件。

“test_rd.tcl”文件可读取 BRAM 中存储的调试数据,并输出 *.dat 文件,如下所示。其它 Tcl 文件可读取这些 *.dat 文件,以分别绘制 LTSSM、PHY RST 状态机和“接收器检测 (Receiver Detect)”的图形化视图。

draw_ltssm.tcl、draw_reset.tcl 和 draw_rxdet.tcl 脚本将使用 ActiveTcl 来执行。

如果您尝试在 Vivado Tcl Console 中执行这些脚本,那么 Vivado 工具将出错并退出。

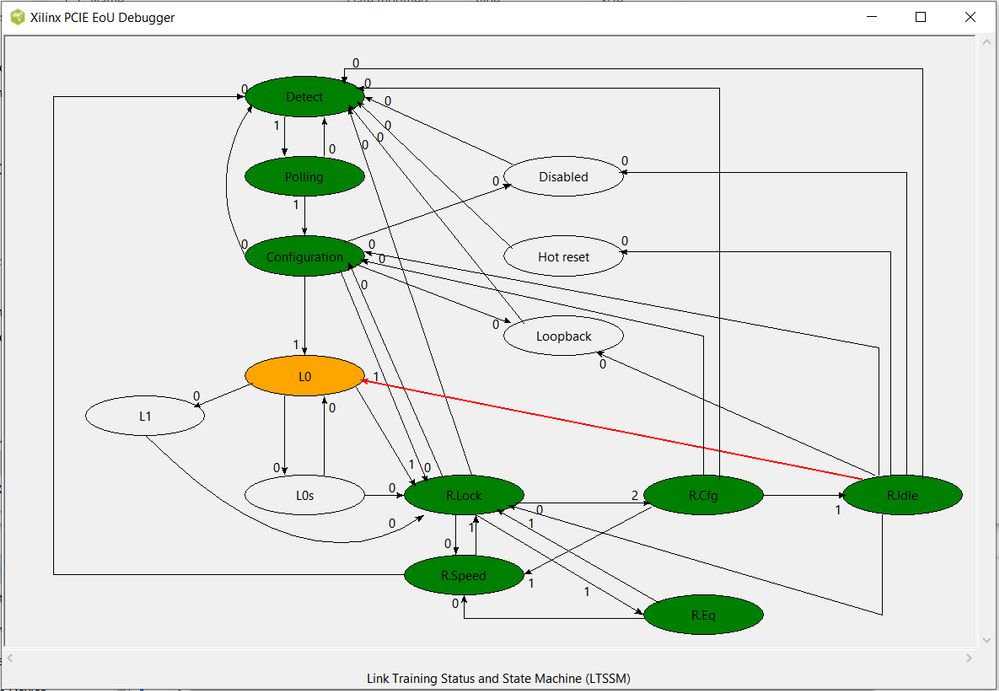

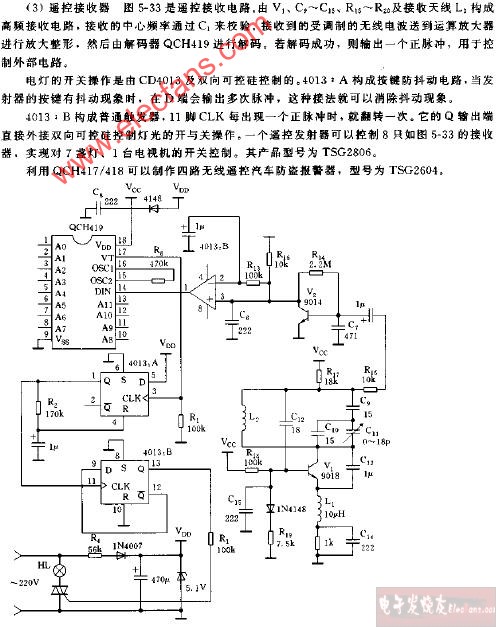

下图显示了通过“draw_ltssm.tcl”脚本生成的 LTSSM 图示:

•绿色 - 采集窗口期间转换的状态

•橙色 - 最终状态

•红色箭头 - 最终转换状态

•箭头旁的数字 - 表示两个状态之间发生的转换次数

上图来自于某个有效的案例场景,其中链接训练正确无误并达成稳定的“L0”状态。当链接训练失败时,“Detect”气泡可能为橙色,表明 IP 无法检测到接收器。同样,您可能看到某一箭头旁的数字较大,表明可能存在不稳定的链接。

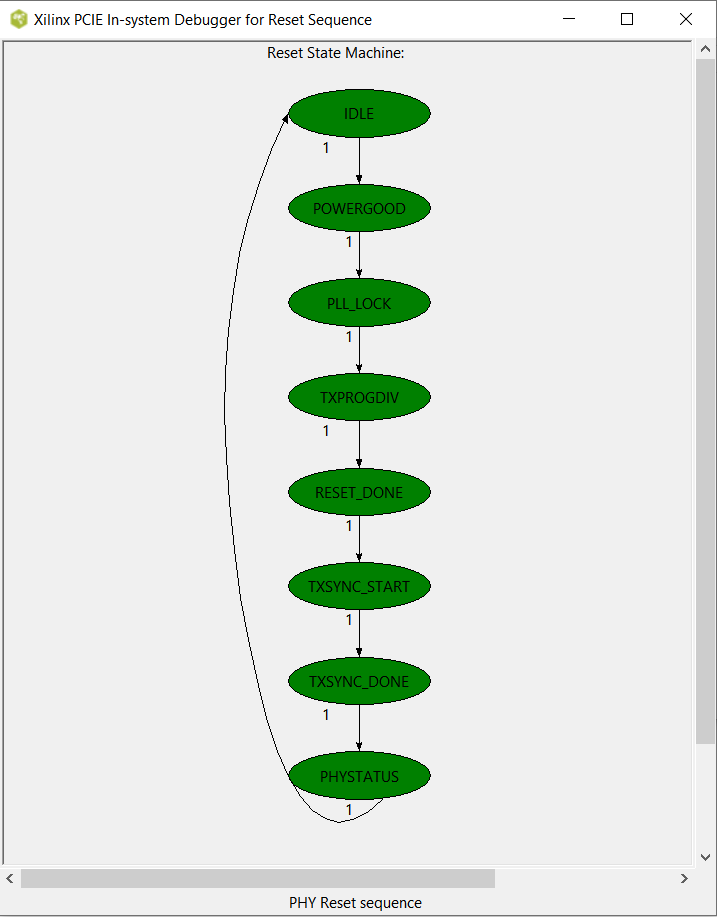

下图显示了使用“draw_reset.tcl”脚本生成的 PHY RST 状态机。

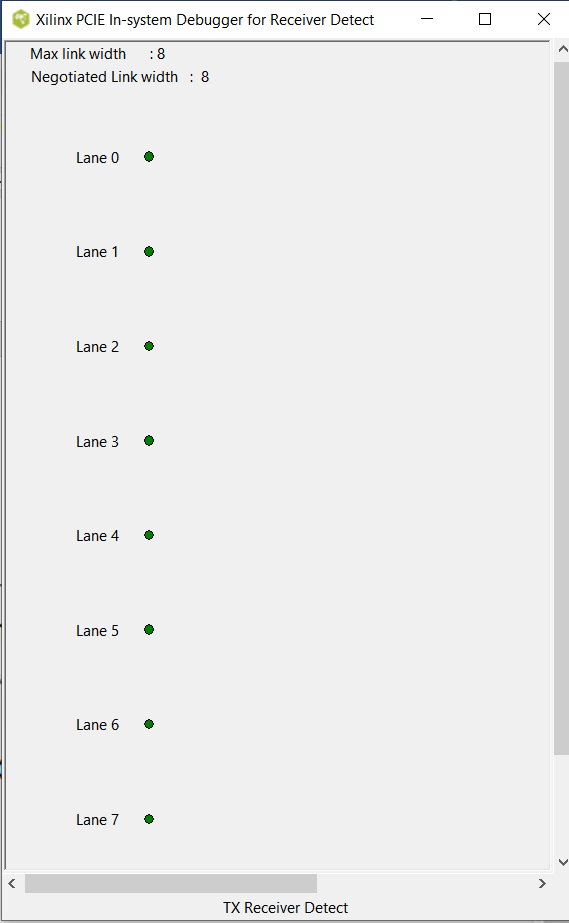

下图显示了使用“draw_rxdet.tcl”脚本生成的“Receiver Detect”状态:

如上所示,绿色点表明对应通道内成功完成接收器检测。GUI 还可提供有关协商的链接宽度的信息。

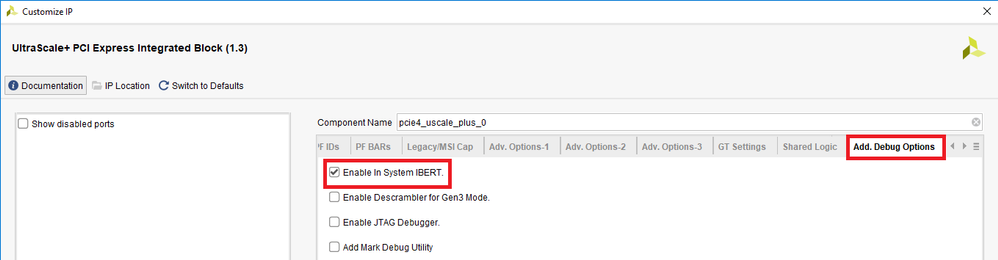

要采集 PCIe 链接眼图,请在 IP 配置 GUI 的“Add. Debug Options”选项卡中选择“启用 In-System IBERT (Enable In-System IBERT)”选项。

与使用“JTAG Debugger”选项时相似,生成 IP 并打开示例设计。

确保在示例设计的“Design Sources”层级中可以看到“System IBERT”模块。

生成比特流并用比特文件和 .ltx 文件进行编程。

请参阅 https://china.xilinx.com/support/answers/72471.html,

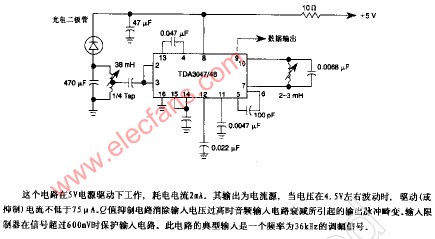

以获取有关 IBERT 扫描必需配置的详细信息。下图显示了通过“In-System IBERT”功能生成的眼图。

以上扫描中的眼图来自于正常运行的 PCIe 链接。在无效链接中,您可能会看到蓝色区域极小,表明链接中可能存在信号完整性问题。

责任编辑:pj

电子发烧友App

电子发烧友App

评论