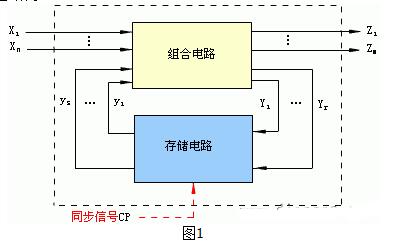

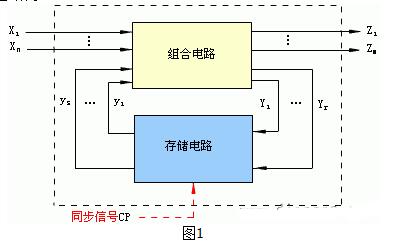

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 53525

53525

了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

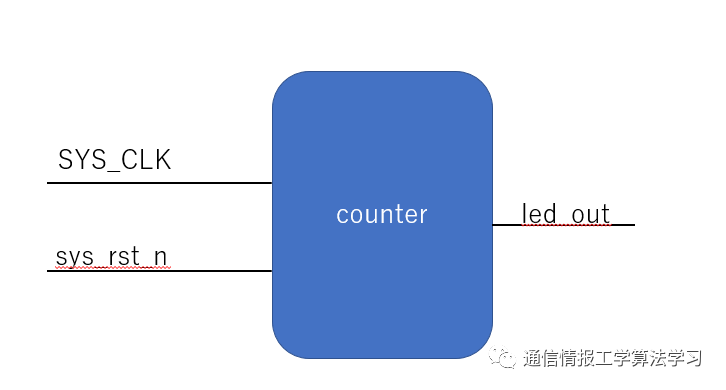

时序逻辑电路的精华——计数器

2022-12-29 09:23:56 1011

1011 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

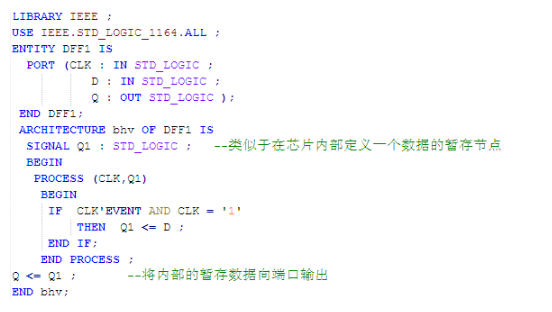

476 VHDL硬件描述语言与和数字逻辑电路设计.侯伯亭&顾新

2020-05-11 09:22:18

VHDL硬件描述语言与和数字逻辑电路设计.侯伯亭&顾新.扫描版

2020-05-03 09:46:42

时序逻辑电路一、实验目的 1.掌握D、JK触发器的逻辑功能和使用 2.掌握中规模集成计数器74LS161

2009-09-16 15:08:37

时序逻辑电路的特点

2019-10-08 05:34:53

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

时序逻辑电路自启动功能怎么判断呢?求大神解答

2023-05-10 14:46:33

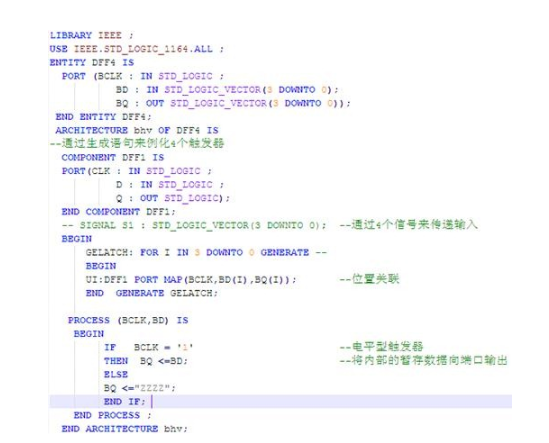

时序逻辑电路设计6.1 基本D触发器的设计6.2 JK触发器6.3 带异步复位/置位端的使能T触发器6.4 基本计数器的设计6.5 同步清零的计数器6.6 同步清零的可逆计数器6.7 同步预置数的计数器

2009-03-20 10:04:53

什么是中断?为什么CPU要用时序电路?时序电路与普通逻辑电路有什么区别呢?

2021-10-29 07:03:45

[VHDL硬件描述语言与和数字逻辑电路设计].侯伯亭&顾新.扫描版

2020-05-21 09:25:46

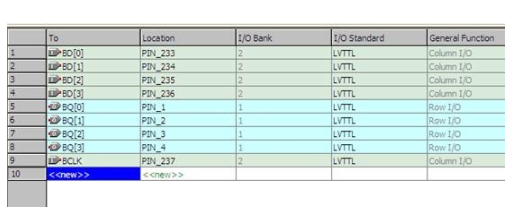

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

华为 逻辑电路设计规范自己选择下载阅读!

2015-08-04 14:46:14

器件CPLD/FPGAn-构成的数字电路,取代了常规的组合和时序逻辑电路,实现了单片化,使体积、重量、功耗减小,提高了可靠性。 目前EDA技术在一般的数字系统、数字信号处理系统等领域获得广泛应用,它将成为今后

2018-11-20 10:39:39

Verilog程序模块的结构是由哪些部分组成的?如何去实现时序逻辑电路和组合逻辑电路的设计呢?

2021-11-03 06:35:57

数字电子电路技术--时序逻辑电路

2017-05-01 21:23:36

数字电子技术-- 时序逻辑电路[hide][/hide]

2017-05-01 21:51:53

你了解如何分析组合逻辑电路与时序逻辑电路吗?数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。逻辑电路的特点组合逻辑电路在

2021-11-18 06:30:00

设计时序逻辑电路时,如何解决电路不能自启动的问题?

是如何解决电路不能自启动,不是‘不能自启动’的定义

2023-05-10 14:44:22

多输入时序电路的基本原理是什么?基于数据选择器和D触发器的多输入时序逻辑电路设计

2021-04-29 07:04:38

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

基本逻辑电路: 组合逻辑电路、&

2008-09-12 16:35:29 40

40 组合逻辑电路设计一、实验目的1. 熟悉组合逻辑电路的基本设计方法;2. 练习用门电路、译码器、数据选择器设计组合逻辑电路。二、实验设备1.

2008-09-12 16:41:23 0

0 1 进一步强化EDA仿真软件的使用;2 掌握利用MSI、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4&

2009-03-18 20:06:31 47

47 时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 0

0 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 用Protel 99实现逻辑电路设计:介绍可鳊程逻辑器件(PLD)应用和相应软件的发展;使用EDA 工具Protel 99的PLD设计简单逻辑电路的一般方法。关键词Protel 99 PLD CUPL语言

众所周知,

2009-11-01 10:13:34 0

0 VHDL硬件描述语言与数字逻辑电路设计:本书系统地介绍了一种硬件描述语言,即VHDL语言设计数字逻辑电路和数字系统的新方法。这是电子电路设计方法上一次革命性的变化,也是迈

2010-02-06 16:55:22 359

359 提出了从状态转换图中直接求得触发器的置位和复位函数,从而确定触发器的驱动方程这样一种设计同步时序逻辑电路的新方法.设计原理简单,易于理解,适合于所有同步时序

2010-02-28 19:23:02 15

15 摘要:通过实际例子,阐述了次态卡诺图在分析和设计时序逻辑电路中的使用方法。该方法的使用可以使时序逻辑电路的分析和设计得到一定的简化,过程中思路清晰,状态转换直

2010-04-28 10:03:10 21

21 摘要:本文对数字逻辑电路关于同步时序逻辑电路设计的关键步骤中,引入代数理论辅助设计作了一些探讨,并用实例表明这样的努力使设计过程得到了大大的简化。关键词:同

2010-04-29 09:35:20 12

12 讲述组合逻辑电路设计基础

2010-05-06 10:29:15 0

0 数字逻辑电路设计课程

数字逻辑电路的设计包括两个方面:基本逻辑功能电路设计和逻辑电路系统设计。关于基本逻辑功能电路设计一般在《数字电路技术基础

2010-05-24 16:05:50 0

0 摘要:文章介绍了Multisim9仿真软件在数字电子技术中时序逻辑电路中的应用,从时序逻辑电路分析、计数器、寄存器等方面介绍了Multisim9仿真软件的优点,提出了Multisim9仿真软件的

2010-05-30 08:21:04 73

73 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 本章内容:q 镜像电路q 准nMOS电路q 三态电路q 钟控CMOS电路q 动态CMOS电路q 双轨逻辑电路q 时序电路

2010-08-13 14:44:30 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

69 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 实验十六 时序逻辑电路? 实验(1) 计数器?一、实验目的?⒈ 熟悉计数器的设计方法及工作原理。?⒉ 了解同步计数器与异步计数器的区别。?⒊ 应用

2008-09-24 22:17:08 3210

3210

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3438

3438

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 8146

8146

时序逻辑电路分析实例

例1 分析图所示电路的逻辑功能。设起始状态是

2009-04-07 23:20:25 4398

4398

时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 9900

9900

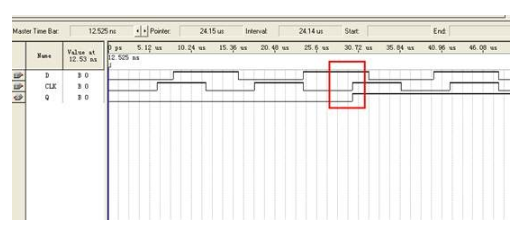

Verilog HDL语言实现时序逻辑电路

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器

2010-02-08 11:46:43 4468

4468 时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 5041

5041 通过介绍Multisim软件的功能和特点,结合格雷玛计数器的设计实例,叙述了在Multisim软件平台进行时序逻辑电路的设计原理及构成方法,并利用软件对设计进行仿真。

2012-02-10 16:43:10 133

133 电子发烧友网站提供《[VHDL硬件描述语言与和数字逻辑电路设计].侯伯亭&顾新.扫描版.txt》资料免费下载

2012-07-10 18:32:33 0

0 电子发烧友网站提供《经典教材-VHDL硬件描述语言与数字逻辑电路设计(第三版).txt》资料免费下载

2014-08-27 11:41:09 0

0 数字逻辑电路设计实践_电工电子实验中心实验报告。

2015-10-29 16:25:13 0

0 定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计

2015-12-17 18:18:50 0

0 主要讲了时序逻辑电路的相关知识,能够方便大家学习使用

2016-02-29 14:25:53 0

0 数字电子钟逻辑电路设计,我自己编写的,里面有横多实用的东西

2016-06-22 16:12:01 54

54 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 0

0 VHDL硬件描述语言与数字逻辑电路设计,感兴趣的小伙伴们可以瞧一瞧。

2016-11-10 14:20:34 0

0 数字电子技术--时序逻辑电路

2016-12-12 22:07:22 0

0 数字电子技术-- 时序逻辑电路

2016-12-12 21:54:28 0

0 一种设计同步时序逻辑电路的新方法

2017-02-07 15:05:00 29

29 逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。

2017-05-22 15:15:59 70760

70760

时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 5673

5673

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 91327

91327

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 123040

123040

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 63962

63962

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 106881

106881

本文档的主要内容详细介绍的是数字电路基础教程之时序逻辑电路的详细资料概述。内容包括了:1.时序逻辑电路分析2.若干常用时序逻辑电路3.时序逻辑电路设计

2018-10-17 08:00:00 0

0 本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 8

8 本文档的主要内容详细介绍的是数字电路教程之时序逻辑电路课件的详细资料免费下载主要内容包括了:一 概述,二 时序逻辑电路的分析方法,三 若干常用的时序逻辑电路,四 时序逻辑电路的设计方法,五 时序逻辑电路中的竞争冒险现象

2018-12-28 08:00:00 12

12 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 30485

30485 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 49628

49628 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 62616

62616 将驱动方程代入相应触发器的特性方程中,便得到该触发器的次态方程。时序逻辑电路的状态方程由各触发器次态的逻辑表达式组成。

2019-02-28 14:06:14 23502

23502 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7636

7636

掌握时序逻辑电路的设计方法及调试技巧,熟练掌握触发器的功能及应用,熟练掌握常用MSI时序逻辑芯片的功能及应用

2020-05-20 08:00:00 20

20 本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 31

31 可规划逻辑电路设计与实习报告

2021-12-23 17:28:52 5

5 从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39:01 875

875 避免常见的逻辑电路设计问题

2022-11-04 09:50:16 0

0 数字电路的分类

(1)按电路结构分类

组合逻辑电路

时序逻辑电路:。

(2)按集成电路规模分:小规模、中规模和大规模。

2022-12-05 14:54:47 12

12 时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

2022-12-05 14:49:30 7

7 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 4816

4816

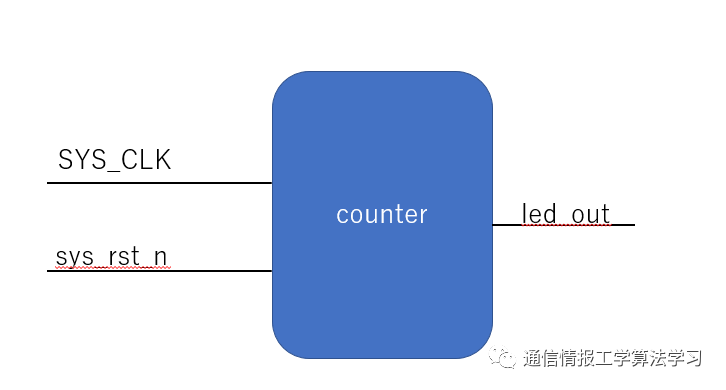

前面已经学习了时序逻辑电路中的基本单元:触发器,这次就用其来整点活,实现计数器的设计,计数器可以说是任何和时序有关的设计都会用到他。

2023-05-22 16:54:50 2503

2503

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1882

1882

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 1983

1983

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 2539

2539

时序逻辑电路 一 : 触发器 1:D 触发器 : 时序逻辑电路最小单元 。 (1):D 触发器工作原理 忽略清零端情况下 : 当使能条件 ( 往往为时钟的触发沿 : 上升沿 / 下降沿 ) 满足

2023-11-02 12:00:01 308

308

电子发烧友网站提供《时序逻辑电路电子课件.ppt》资料免费下载

2023-11-21 14:43:40 0

0 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 499

499

电子发烧友App

电子发烧友App

评论