本文主要介绍了采样保持电路图大全(五款采样保持电路设计原理图详解),采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路。

2018-02-23 09:59:44 95716

95716

如今大多数ADC芯片里都集成了采样保持功能,以便更好地处理交流信号,这种类型的ADC我们叫做采样ADC,可是早些时候的ADC并非采样类型,而只是一个简单的编码器。 非采样ADC的一个缺点是,如果在

2021-04-28 11:02:50 24116

24116

主要是关于:采样保持名词解释、采样保持电路工作原理、采样保持电路功能、采样保持电路作用以及采样保持电路设计。

2022-10-20 09:37:34 5059

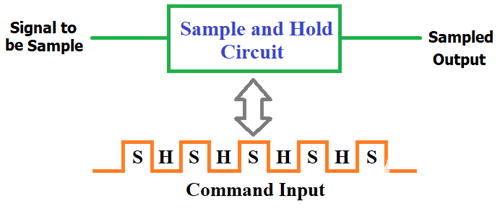

5059 采样保持电路从模拟输入信号中获取样本并保持特定时间段,然后输出输入信号的采样部分。该电路仅对几微秒的输入信号进行采样。

2022-11-08 17:29:18 6704

6704

有大神知道12位ADC采样保持器里面的电容量级是多少吗?因为设计电路的时候要使用抗混叠滤波器,需要考虑采样保持器电容与抗混叠滤波电容的大小关系

2023-11-02 06:27:44

适应相控阵架构、直接射频采样、波束成形和 5G 无线电等应用。Alphacore 采用 GlobalFoundries 的 22nm FD-SOI 工艺设计了一款名为 A11B5G 的混合 ADC

2023-02-07 14:11:25

CMOS工艺锂电池保护电路图的实现

2012-08-06 11:06:35

工艺库TSMC0.18um和TSMC0.18umrf有什么区别呢?求大神解答

2021-06-23 07:33:12

本帖最后由 gk320830 于 2015-3-7 19:04 编辑

采样保持电路

2012-08-14 09:40:39

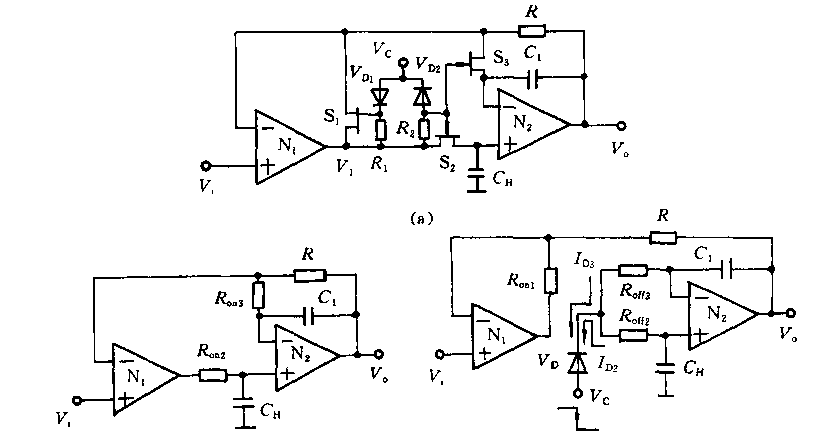

SHA图17:开环SHA实现方案图18所示的SHA电路是经典的闭环设计,已被许多CMOS采样ADC采用。由于开关始终在虚地工作,因此开关上不存在共模信号。图18:基于反相积分器的闭环SHA,在求和点切换

2022-04-06 14:04:47

的 A/D转换器滤除高频干扰,此时可不加采样/保持器。总之,是否加采样/保持电路,完全取决于使用对象。当然,如果用户设计的是通用型数据采集系统,为满足不同信号的输入,建议在 A/D转换前加上采样/保持电路

2018-01-08 14:23:45

电路,前端信号为阶梯上升信号。同时基于采样保持电路设计了峰值保持电路,电路自动识别输入信号的峰值供后端ADC信号采集。

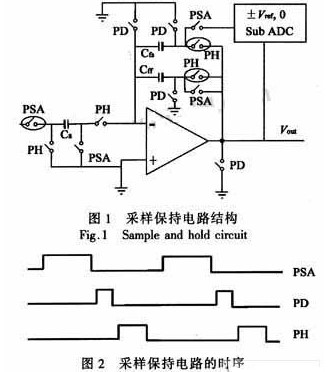

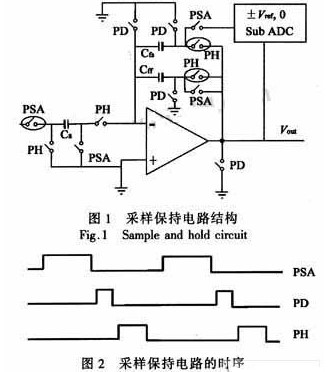

课题中设计的采样保持电路如下图:

基于AD781设计的峰值保持电路如下图所示

2023-11-23 07:05:20

称为RF采样ADC)利用尖端65 nm CMOS技术实现,可以集成许多数字处理功能来增强ADC的性能。这些增加的特性使得ADC能够在ADC芯片中快速执行大量数字处理,分担FPGA的一些数字处理负荷。这就

2018-09-06 11:36:35

少,主要用于纠错和数字驱动器。新一代GSPS(每秒千兆样本)转换器(也称为RF采样ADC)利用尖端65nm CMOS技术实现,可以集成许多数字处理功能来增强ADC的性能。这样,数据转换器便从20世纪

2021-12-17 06:30:00

项目名称:高速脉冲电流采样保持电路研究试用计划:申请理由:在调试采样保持电路过程采用整合模拟前端部分的整板进行调试费时费力,需要连接一大堆外围设备,ADI M2K作为一款口袋仪器,其产品定位非常符合

2019-12-19 09:34:23

(LowDrop-Out)系统的过流关断功耗。本电路基于TSMC 0.6μ m CMOS 工艺设计,进行了应用于LDO 的Spectra 仿真,结果表明该过流保护电路可靠性高、过流关断功耗低。 [hide][/hide]

2009-12-02 17:11:12

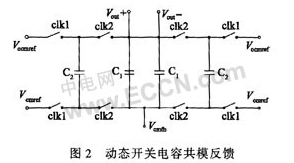

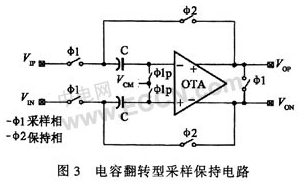

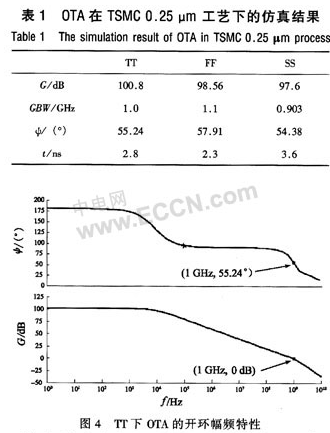

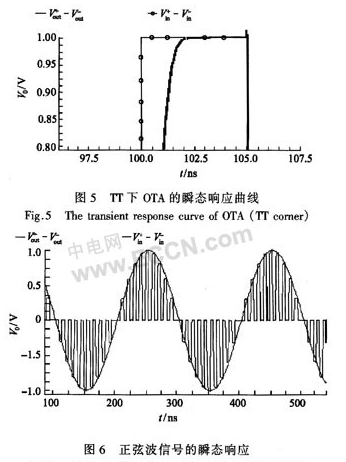

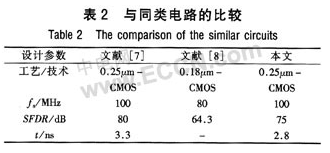

电路是整个系统的关键模块电路之一。设计一个性能优异的采样保持电路是避免采样歪斜(timing skew)最直接的方法。 本文基于TSMC 0.25μm CMOS工艺,设计了一个具有高增益、高带宽

2018-10-08 15:47:53

你好,我使用的样品&;持有部分在我的高我需要来样来signald从传感器接收由一个非常短的光来自LED脉冲光。问题是,当我使用采样保持电路我得到一个含噪信号相比,一个我得到抽样时没有H

2019-08-14 11:41:15

要求远远小于对整个电路的精度要求。在局部模块的精度较低时也能正常工作。Delta-Sigma A/D主要应用于中低带宽的音频信号,讨论采用AMS 0.35μm PDK实现模数转换电路。该电路核心

2010-04-24 09:06:17

了视野,但为了达到X波段(12 GHz频率),仍然需要更多带宽。在信号链中运用采样保持放大器 (THA),可以从根本上扩展带宽,使其远远超出ADC采样带宽,满足苛刻高带宽的应用的需求。本文将证明,针对RF市场开发的最新转换器前增加一个THA,便可实现超过10 GHz带宽。

2019-07-22 08:01:03

如何利用0.18μm CMOS工艺去设计16:1复用器?以及怎样去验证这种复用器?

2021-04-09 06:39:47

怎么在O.5μm CMOS工艺条件下设计一种采用电流反馈实现迟滞功能的旁路电压控制电路?

2021-04-14 06:53:08

本文研究了一个用0.6μm CMOS工艺实现的功率放大器, E型功率放大器具有很高的效率,它工作在开关状态,电路结构简单,理想功率效率为 100%,适应于恒包络信号的放大,例如FM和GMSK等通信系统。

2021-04-23 07:04:31

本文设计了一个可用于12 bit,20 MS/s流水线ADC中的采样/保持电路。该电路使用CSMC公司的0.5μm CMOS工艺库,在20 MS/s采样频率下,当输入信号的频率为9.8193 MHz

2021-04-20 06:45:33

本文采用0.18 μm CMOS工艺设计了一种适用于TI-ADC的高速、低功耗开环T&H电路。

2021-04-20 06:58:59

本文给出了使用CMOS工艺设计的单片集成超高速4:1复接器。

2021-04-12 06:55:55

(使用放大器)也可以是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎选择元器件,以便实现在目标频段的最优ADC性能。射频采样ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理

2018-11-01 11:25:01

怎么实现高速采样保持电路的设计?

2021-10-11 07:42:17

本文选择了SoC芯片广泛使用的深亚微米CMOS工艺,实现了一个10位的高速DAC。该DAC可作为SoC设计中的IP硬核,在多种不同应用领域的系统设计中实现复用。

2021-04-14 06:22:33

近年来,有关将CMOS工艺在射频(RF)技术中应用的可能性的研究大量增多。深亚微米技术允许CMOS电路的工作频率超过1GHz,这无疑推动了集成CMOS射频电路的发展。目前,几个研究组已利用标准

2019-08-22 06:24:40

你好,我在我的项目中使用样本和保持组件,因为我需要从一个光传感器采样信号,它接收来自一个LED的非常短的光脉冲。问题是,当我使用采样保持电路时,与没有H&AMS的采样时相比,我得到了一个有噪声的信号

2019-08-15 11:19:14

0.25mm CMOS超高速分接电路。这些均充分说明了标准CMOS工艺技术具有制作GHz以上工作频率芯片的能力。 (2)优化芯片间及芯片内的互连,解决连线延时问题,速度可以进一步提高。 芯片间互连已经成为

2018-11-26 16:45:00

求TSMC90nm的工艺库,请问可以分享一下吗?

2021-06-22 06:21:52

各位大牛好

我想选择一款采样保持芯片来实现对脉宽1ns的周期脉冲信号进行等效采样,后端ADC的采样频率为10MSPS。

1)AD783的Acquisition time典型值是250ns,是不是

2023-11-17 07:55:46

什么元器件吗?还是跟平时低频的一样,直接连接就好?总结问题:1.用168M的单片机如何采集200MHz的信号2.200Msps的ADC由CMOS和DDR LVDS输出,怎么接收输出信号,硬件电路上需要加电阻吗?感谢各位大佬。

2020-12-06 22:26:35

哪位大侠有umc0.25um bcd工艺?

2021-06-22 06:51:23

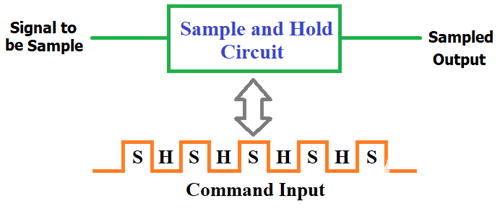

采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路

2011-07-28 10:21:06

引言影响接收机速度、性能的一个重要电路单元AD转换部分就显得愈发重要。影响接收机速度、性能的一个重要电路单元AD转换部分是非常重要的,而AD转换前端的采样保持电路又直接关系到AD芯片的转换

2021-07-27 06:12:53

介绍了一种利用双采样技术的高性能采样/保持电路结构,电路应用于10bits50MS/s 流水线ADC 设计中。电路结构主要包含了增益自举运算放大电路和栅压自举开关电路。增自举运算放大

2009-12-26 16:39:10 28

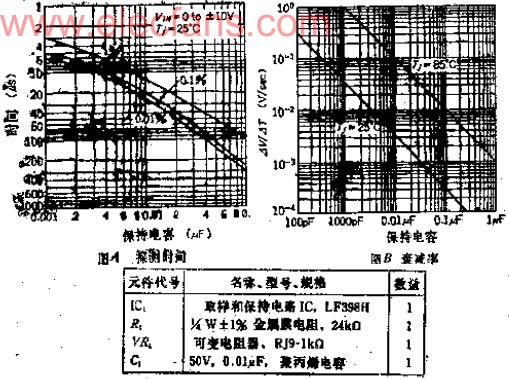

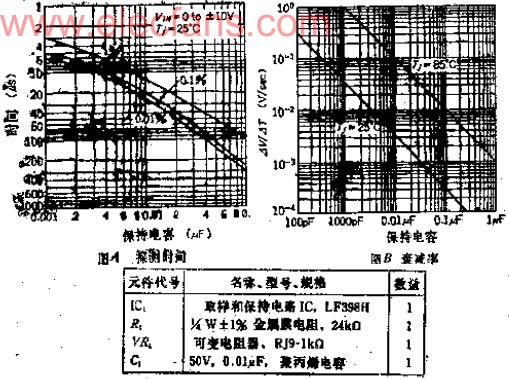

28 对采样保持电路的原理、工作方式、电路的参数以及保持电容器电容量大小的选定进行了分析。关键词:采样;保持;电容

Abstract:This paper analyses the principle of~mapling a

2010-04-13 08:54:05 64

64 在常规高速采样保持电路(SHC)中采样速率主要受到保持电容器被充电到输入电平期间的采集时间的限制。本文描述一种新的电路结构,其采样速率仅仅由保持时间决定。就时钟馈通而

2010-04-28 09:57:45 63

63 一种新型高速采样保持电路摘要 : 本文提出了一种新型的基于运算放大器的开关电容采样保持电路结构。采用速度补偿解决了高速高分辨采样保持电

2010-05-24 15:44:21 49

49 一种100MHz采样频率CMOS采样/保持电路

摘要: 设计了一种高速采样保持电路。该电路采用套筒级联增益自举运算放大器,可在达到高增益高带宽的同时最大程度地减

2010-05-24 15:52:26 38

38 摘要: 讨论了目前存在的基于米勒电容的采样/保持电路,在此基础上设计了一种简化形式。该电路利用简单的CMOS反相器代替米勒反馈电路中的运算放大器,在保证采样速度和精度

2010-07-31 17:24:53 0

0 采样保持电路

2009-01-02 01:06:50 1471

1471

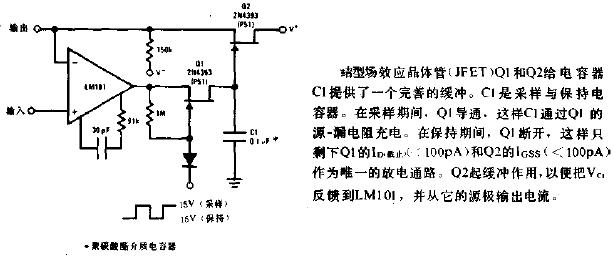

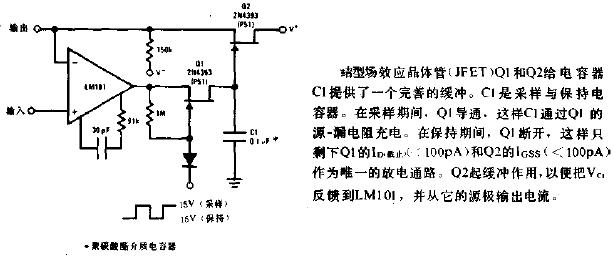

采样保持放大器

采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这

2009-03-11 18:29:56 3785

3785

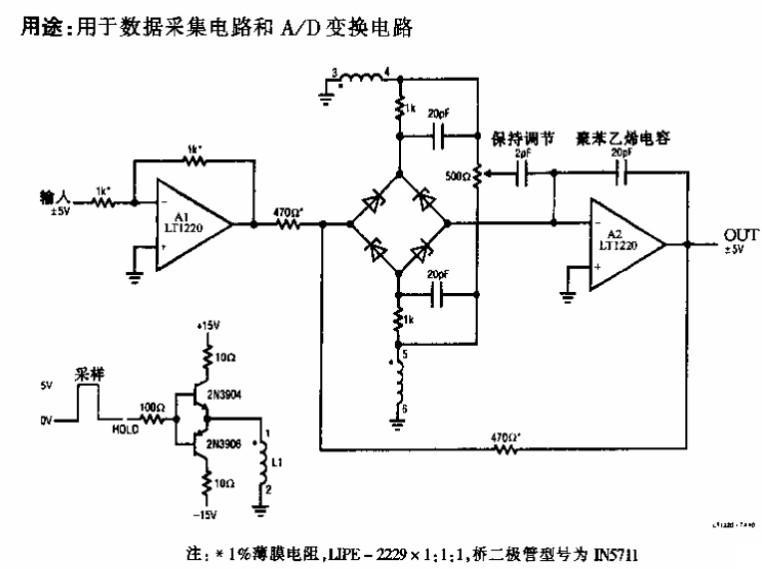

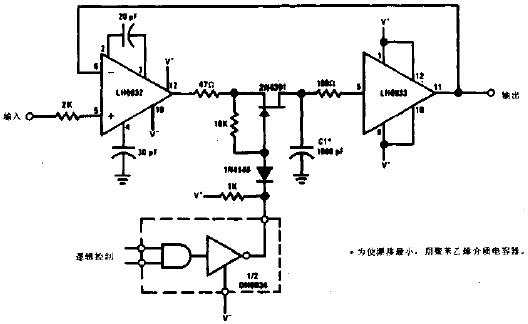

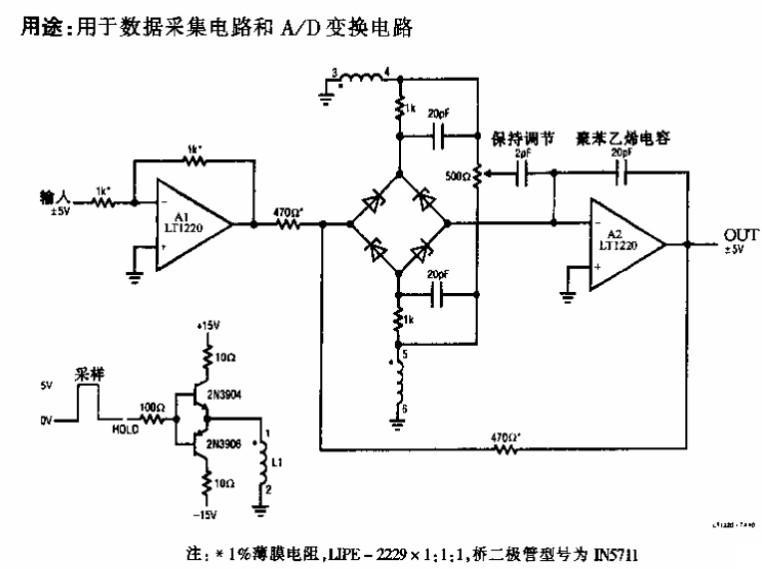

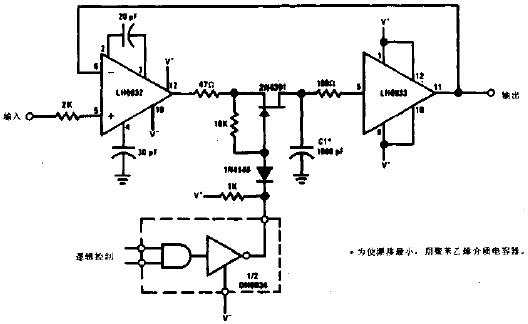

×1000采样与保持电路图

2009-04-09 09:23:26 799

799

采样与保持电路图

2009-04-09 09:23:54 1253

1253

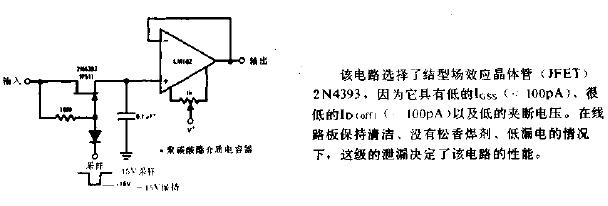

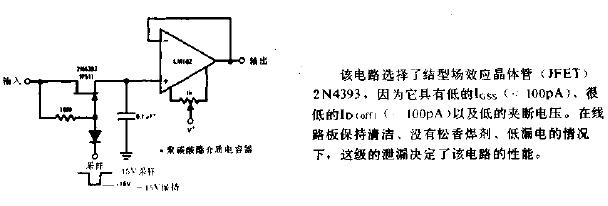

低漂移采样与保持电路图

2009-04-09 09:24:27 568

568

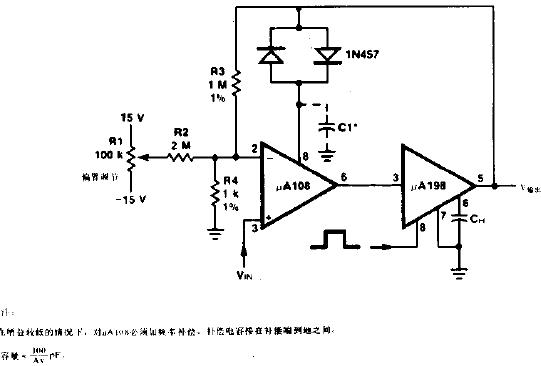

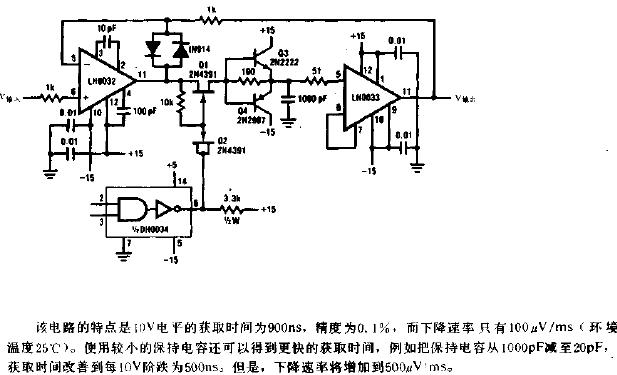

高精度采样与保持电路图

2009-04-09 09:25:48 1428

1428

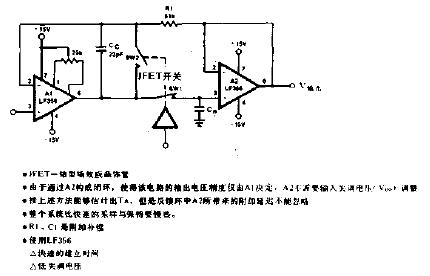

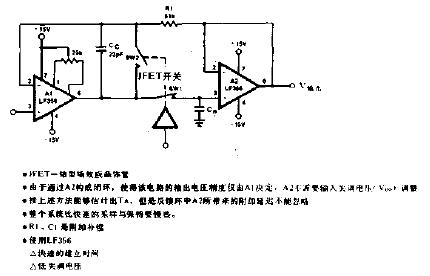

高速采样与保持电路图1

2009-04-09 09:26:15 667

667

高速采样与保持电路图2

2009-04-09 09:26:58 612

612

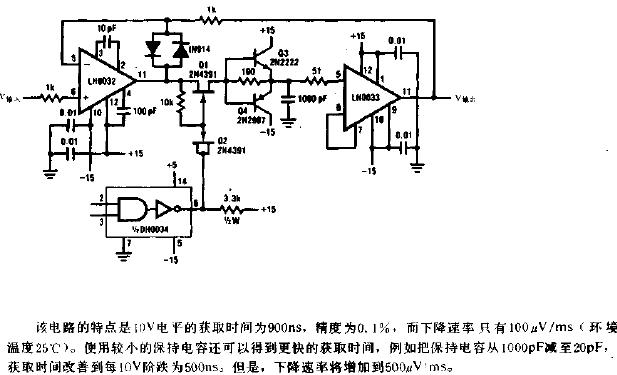

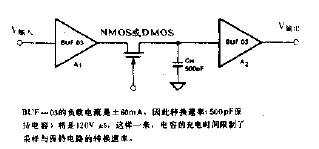

高速采样与保持电路图3

2009-04-09 09:27:24 619

619

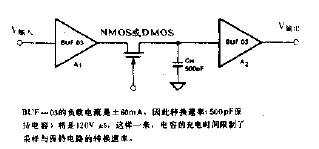

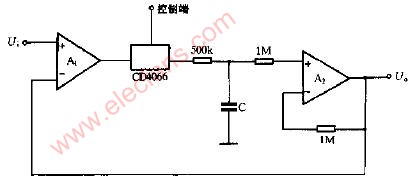

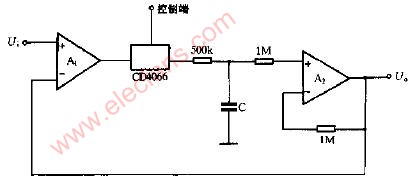

失调量可调的采样与保持电路图

2009-04-09 09:28:47 386

386

采样保持电路(S/H)原理

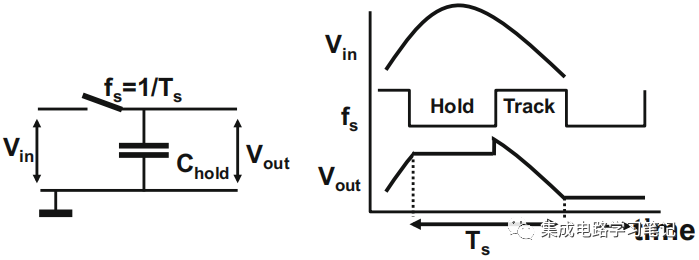

A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。为此,在ADC前加入采样保持电路,如图8-30所示。采样保持电路有两种

2009-04-12 12:01:35 22785

22785

采样信号保持电路图

2009-05-08 14:28:55 1034

1034

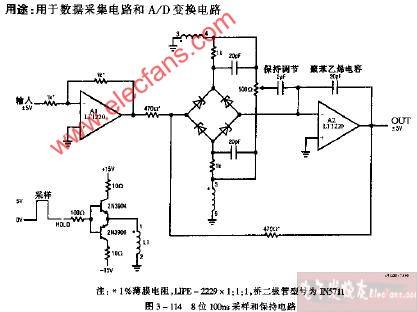

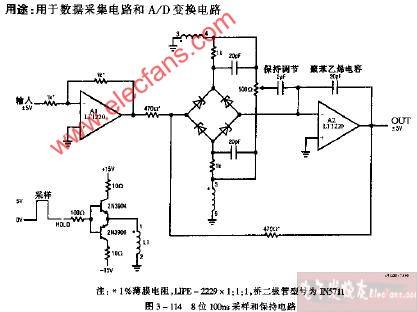

8位100ms采样和保持电路图

2009-06-29 09:56:42 613

613

采样保持电路图

2009-07-08 11:40:58 976

976

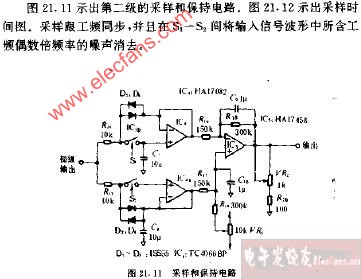

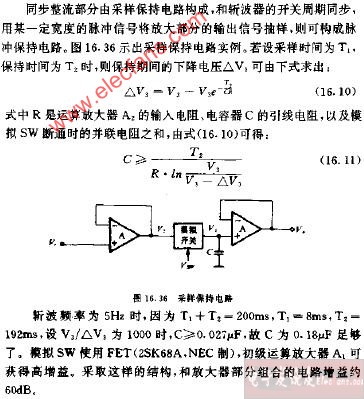

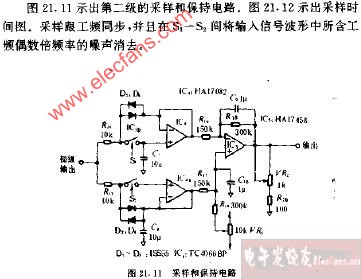

第二级采样和保持电路图

2009-07-09 12:26:15 514

514

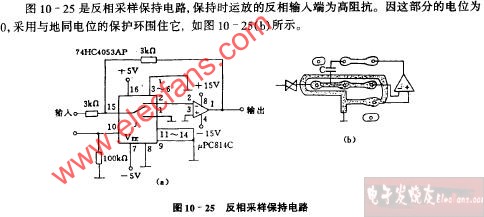

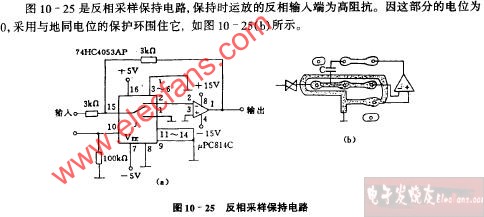

反相采样保持电路图

2009-07-17 14:43:55 647

647

同相采样保持电路图

2009-07-17 14:51:13 712

712

DS1843 高速采样/保持电路

DS1843是一款采样/保持电路,对于电路板空间受限的快速信号采集

2009-11-16 17:57:24 1318

1318

TSMC推出高整合度LED驱动集成电路工艺,降低零组件数量

TSMC推出模组化BCD(Bipolar, CMOS DMOS)工艺,将可为客户生产高电压之整合LED驱动集成电路产品。此一新的BCD工艺特色

2009-12-19 09:29:51 678

678 高通携手TSMC,继续28纳米工艺上合作

高通公司(Qualcomm Incorporated)与其专业集成电路制造服务伙伴-TSMC前不久日共同宣布,双方正在28纳米工艺技术进行密切合作。此

2010-01-13 08:59:23 910

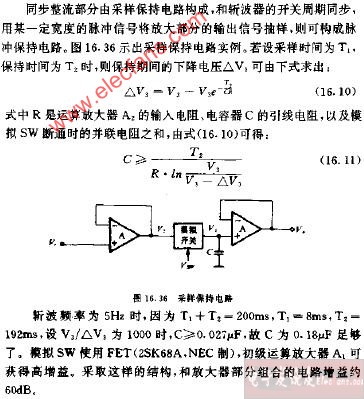

910 采样时间为20US的中速采样和保持电路

电路的功能

所谓采样和保持

2010-05-05 15:53:51 1382

1382

单片采样保持电路

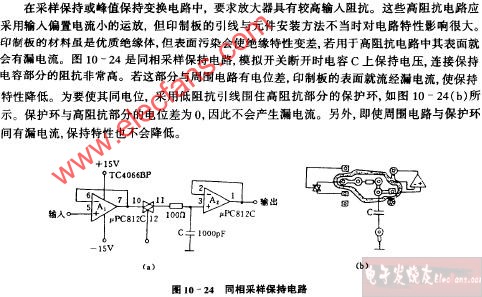

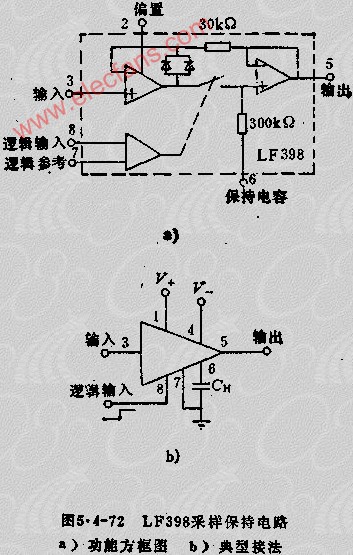

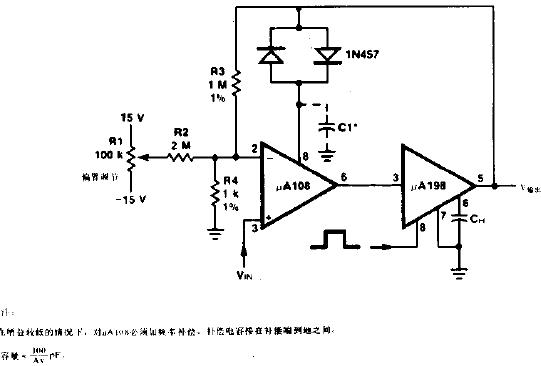

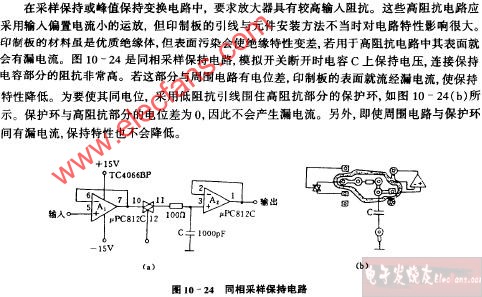

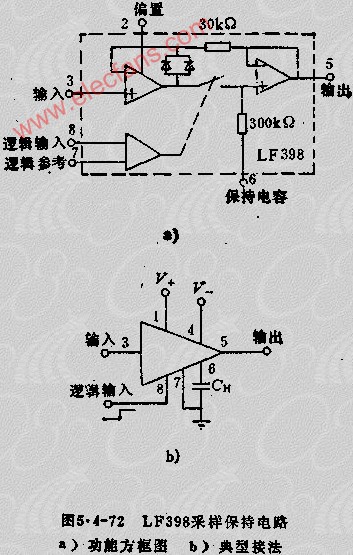

现在已有多种单片采样保持电路的产品。图5.4-72是单片采样保持电路LF398。该电路在作为单位增益跟随器使用时,其DC增益精度为0.002%到0.01

2010-05-23 18:19:30 2995

2995

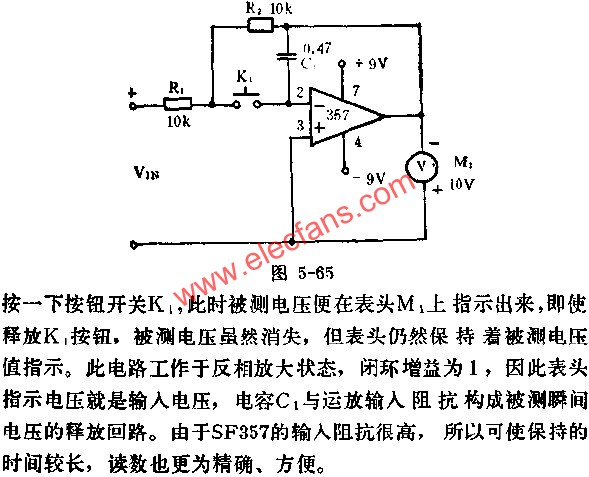

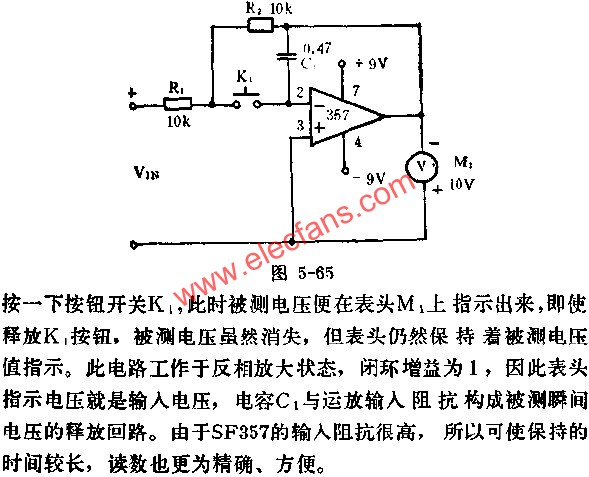

图中所示是用SF357运放组成的电压采样保持电路.这种电压采样保持电路可以方便地观察任一时间内的被测瞬间电

2010-10-08 12:53:57 12120

12120

本文应用ADS 软件设计了一个4GSps 4bit GaAs 基超高速ADC,该ADC 芯片采用折叠内插结构实现。文中详细描述了采样保持电路(T/H)与折叠内插电路设计与仿真,芯片最终采用GaAs HBT 工艺实现

2011-07-05 15:45:24 48

48 将一个经典的模拟累加器与一个采样保持放大器级联对一组模拟电压的采样进行保持。经典的模拟累加器是一个运放加上至少三只精密电阻。这些电阻的值应尽可能低,以避免影响累加

2012-04-01 10:53:12 4864

4864

C8051F020实现C8051F020实现ADC采样芯片外的模拟电压ADC采样芯片外的模拟电压通过LCD显示,并通过串口发送到PC机

2015-11-12 14:23:11 29

29 Monolithic Sample-and-Hold Circuits采样保持电路SHC

2015-11-30 18:31:05 112

112 的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在高速低功耗的ADC应用中也成为一个比较常用的结构。 作为流水线ADC前端的采样保持电路是整个系统的关键模块电路

2017-11-16 15:23:31 1

1 是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎选择元器件,以便实现在目标频段的最优ADC性能。 简介 射频采样ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理特性表明较小的晶体管尺寸支持的最大电压也较低

2017-11-22 17:46:05 1009

1009

的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在高速低功耗的ADC应用中也成为一个比较常用的结构。 作为流水线ADC前端的采样保持电路是整个系统的关键模块电路

2017-12-07 10:45:23 5

5 的模块,采样保持电路的性能直接决定了整个ADC的性能,在以上系统中对功耗的要求十分严格。本设计在实现高速高精度采样保持功能的同时,还实现了MDAC功能,这样既能降低ADC功耗又能减少芯片面积。

2019-06-13 08:19:00 4768

4768

关键词:AD9101 , 采样保持放大器 , 接口电路 如图所示为AD9101用于快速(Flash)采样的接口电路。当信号频率增加时,传统的快速采样电路不得不牺牲动态范围以换取整体性能的稳定。图中

2019-01-28 18:48:01 347

347 的基本特点与AD781相同。AD783采用模拟器件公司的ABCMOS制造工艺,ABCMOS工艺综合了高性能、低噪声双极性电路和低功率CMOS逻辑,提供一个精确、高速和低功率的SHA。AD783有J级、A级、S级3个温度等级,其引脚排列如图所示。

2019-01-31 07:40:01 1374

1374 AD7875和AD7876采用高密度线性兼容双极/ CMOS工艺(LC 2 MOS)组合12位A / D转换器(ADC),采样/保持(SHA) ),单个单片芯片上的参考和接口逻辑。

2019-04-12 17:59:57 2330

2330

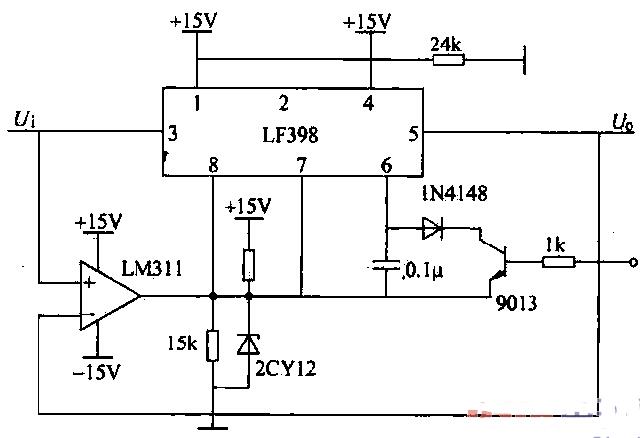

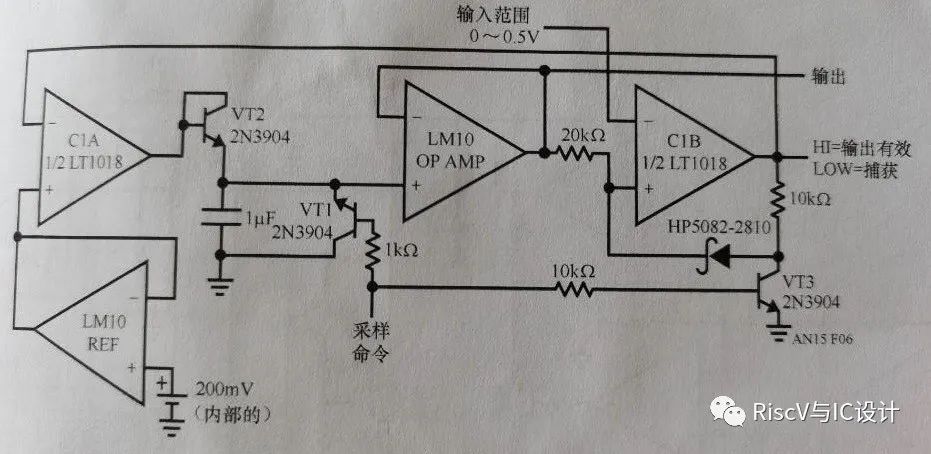

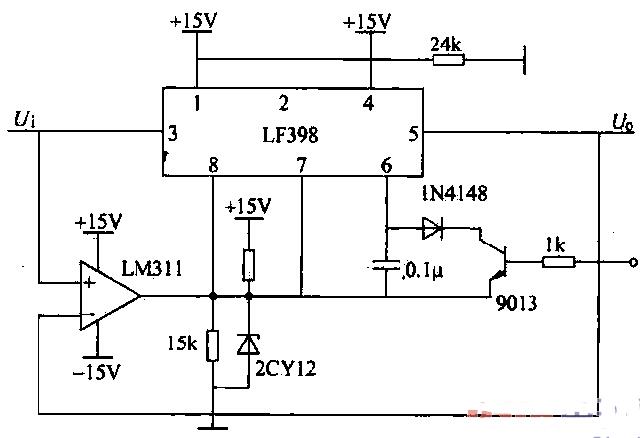

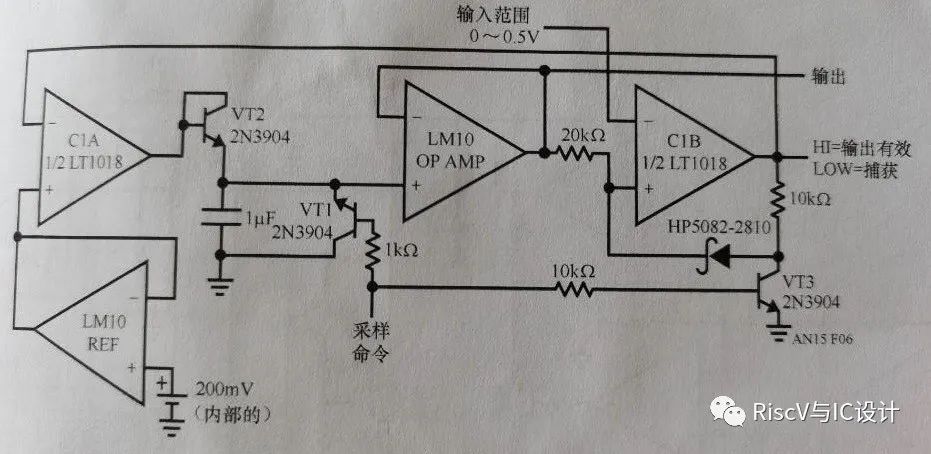

峰值电压采样保持电路:峰值电压采样保持电路如图12-50所示。峰值电压采样保持电路南一片采样保持器芯片LF398和一块电压比较器LM311构成。LF398的输出电压和输入电压通过LM3J1进行比较t当U.》Uo时.

2020-01-21 17:21:00 14502

14502

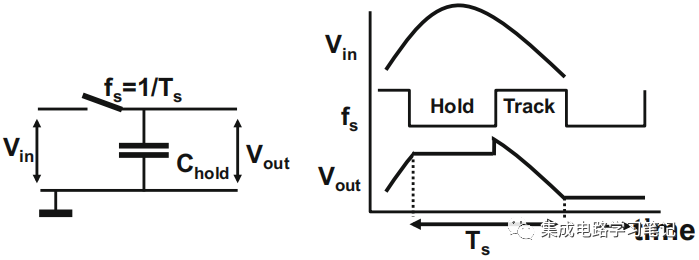

采样保持电路能够跟踪或者保持输入模拟信号的电平值。在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化。

2020-03-31 16:48:01 1306

1306

的一个非常重要的组成部分。在这些应用中,如何在保持高采样频率下降低功耗是一个很重要的设计要点。整体而言,流水线型结构A/D转换器是同时实现低功耗、高采样率和高分辨率的合理选择。

2020-10-22 08:08:00 858

858

AD7880:CMOS,单+5 V电源,低功耗,12位采样ADC数据表

2021-04-17 09:00:23 10

10 AD9260:2.5 MHz输出字率下16位分辨率的高速过采样CMOS ADC数据表

2021-04-17 17:07:26 14

14 AN-284:用模拟输入/输出端口实现无限采样保持电路

2021-04-22 16:19:39 12

12 AD7870A:CMOS,完整,12位,100 kHz,采样ADC数据表

2021-04-29 10:51:10 3

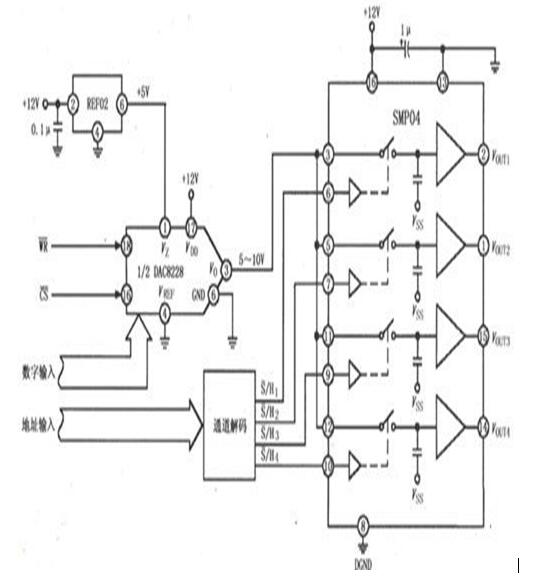

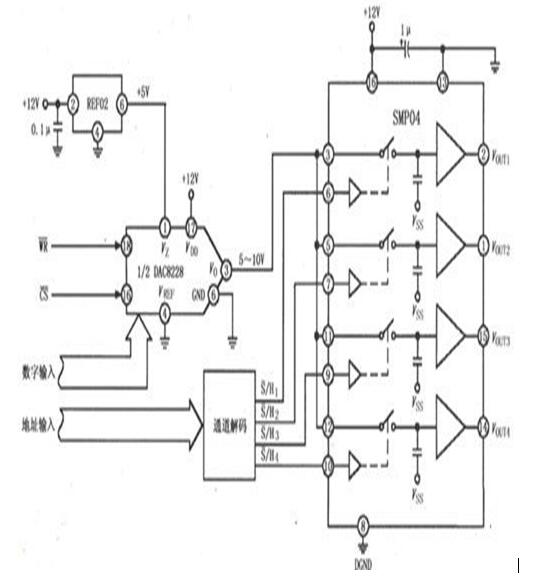

3 SMP04:CMOS四路采样保持放大器数据表

2021-05-26 10:28:11 7

7 CMOS 集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区

2022-11-14 09:34:51 6645

6645 AD9653是一款4通道、16位、125 MSPS模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。

2022-11-24 10:43:08 881

881 采样保持电路是模数转换器(ADC)中最重要的电路之一。其电路中存在的寄生电容会引入时钟馈通、沟道电荷注入等非理想因素严重影响ADC的整体性能。鉴于此,本文将介绍这些非理想因素产生的原因及常见的解决方法。

2023-07-17 16:16:19 1031

1031

与ADC转換器相伴出现的逻辑器件是采样保持放大器。 对于1.5V工作的电路来说,采样保持电路是最难设计的电路之一

2023-10-13 14:23:46 464

464

![]() ,即0.488 mV。因此该采样保持电路可以应用于10位ADC中。

,即0.488 mV。因此该采样保持电路可以应用于10位ADC中。

电子发烧友App

电子发烧友App

评论