有大神知道12位ADC采样保持器里面的电容量级是多少吗?因为设计电路的时候要使用抗混叠滤波器,需要考虑采样保持器电容与抗混叠滤波电容的大小关系

2023-11-02 06:27:44

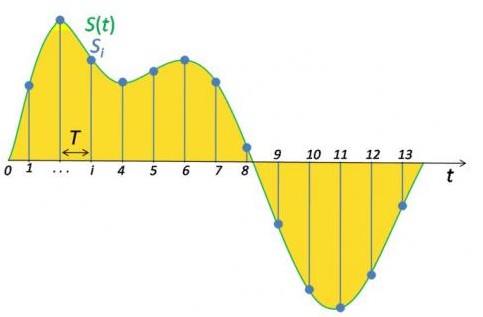

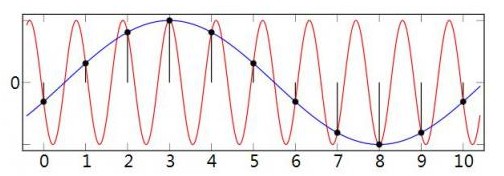

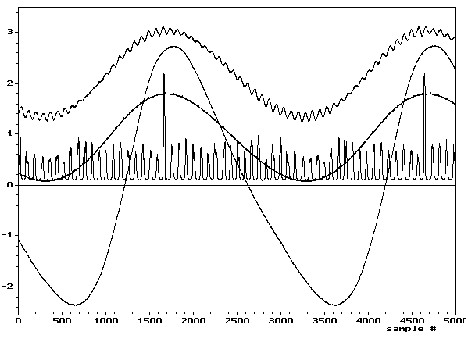

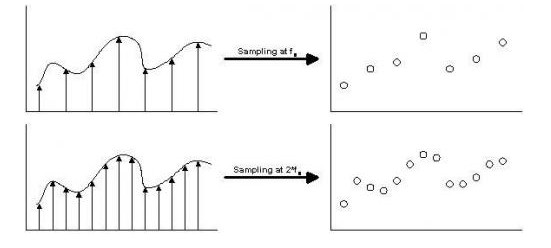

、量化、编码。前置滤波器由于采样信号输出的是窄脉冲信号需要抗混叠滤波器来避免高频信号影响基带信号。采样是将连续的模拟信号转换成时间上离散的采样信号;需要注意的是;根据奈奎斯特采样定理,采样频率必须大...

2022-02-25 06:54:14

为了取得较好的信号带内平坦度,引入了ADC 前端匹配电路的设计,特别是对于non-input buffer的ADC在高负载抗混叠滤波器应用场景下,前端匹配电路的设计在超宽带的应用中就更显得尤为重要。本文将以ADS58H40为例介绍ADC前端匹配电路的设计。

2021-04-19 09:32:26

针对此问题的解决方案:那就是抗混叠滤波器。抗混叠滤波器大多数ADC之前都会有一个抗混叠滤波器,而这个滤波器与衰减信号(超过了所需带宽)的低通滤波器没有什么不同。如图4所示,一个理想抗混叠滤波器的响应

2018-09-06 16:00:00

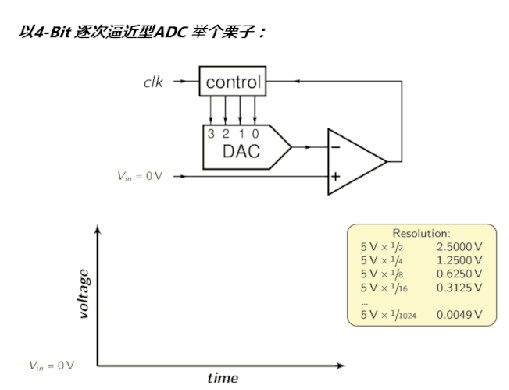

ADC(analog to digital converter)的转换过程ADC的基本转换原理分为四个过程:①抗混叠滤波(Anti-aliasing),可以理解为一个低通滤波器②采样保持电路

2021-07-22 06:25:31

提升信噪比,二是可以放宽对位于ADC之前的抗混叠模拟滤波器的要求。抗混叠滤波器:分区困境理想情况下,与ADC相关的滤波器,特别是那些负责解决频谱混叠问题的滤波器,相比其精度,其幅度响应带宽必须尽可能

2021-08-04 07:00:00

知道,在高精度ADC应用中使用抗混叠滤波器是有益的,不过,设计合适的抗混叠滤波器也同样重要—如果你不小心的话,就像把有害误差从系统中消除一样,很容易将有害误差引入到你的系统中。在为你的应用设计抗混叠

2018-09-05 14:52:59

成为带宽限制。这是抗混叠滤波器的目的。通过在采样之前使信号通过低通滤波器,我们可以衰减指定频率以上的频谱内容,从而创建一个上限频率。 由于现实生活中的滤波器不会在截止频率以上产生无限的衰减,因此信号将不

2020-09-18 10:12:55

灵活设计、模拟/数字兼用、群延迟时间偏差和频率选择特性优良、输入输出阻抗误差小。近年来已将SAW滤波器片式化,重约0.2g;另外由于采用了新的晶体材料和最新精细加工技术,致使SAW器件的使用上限频率

2019-05-20 04:39:41

滤波器在抗EMI中的应用及发展,看完你就懂了

2021-05-25 06:35:36

基于第 3 步由模拟滤波器向数字滤波器的转化方式,IIR 滤波器设计方法分为“脉冲响应不变法”和“双线性变换法”,由于“脉冲响应不变法”存在混叠误差的缺陷,因此一般我们多选“双线性变换法”,而对于第

2023-09-26 07:22:10

容易驱动。对频带特定IF抗混叠滤波器的要求可以显著放宽,原因是内部环路滤波器具有通带优势,从而简化系统架构。一些缺点:需要超高频时钟以实现有效过采样比(OSR)。例如,OSR为16的100MHz带宽

2018-10-31 10:48:38

产品中需要用到AD7606,回波模拟信号的幅度最小在零点几伏,考虑到ADC的输入范围为-5~5,有没有必要在ADC前面加一个运放,将回波信号适当放大一下?看到手册中说内部有抗混叠滤波器且输入阻抗为

2018-09-12 11:15:54

阅读手册,AD7606内部有一个抗混叠滤波器,在-5~+5V范围下的-3db带宽为15khz,在-10~10V范围内-3db带宽是22KHZ,下降沿大约在10khz左右开始。

我的回波信号

2023-12-18 06:22:57

缓冲和无缓冲输入ADC的输入阻抗模型 无缓冲CMOS ADC(AD9236 12 位、80 MSPS )在采样模式和保持模式下的串联输入阻抗 谐振匹配的基本原理 添加匹配模拟抗混叠滤波器网络前后

2018-10-26 09:34:36

使用环境:

之前使用ADL5565设计过通信系统中的抗混叠滤波器。接收机通道中假信号为ADC基带信号中的高频噪声,如果不能有效的阻止,将在ADC输出的结果中引入混叠误差。ADC中的频谱混叠由以下

2023-11-23 06:01:47

HiADS1675 ,内部有2种滤波器 ,delta-sigma (ΔΣ) 是用做抗混叠滤波器吗?或者还用作其他? 有没有相关的详细文章介绍?

2019-05-22 06:17:18

喜 我有几个问题。 1. Acc的顺序抗混叠滤波器是什么? 2.陀螺的顺序抗混叠滤波器是什么? 3.如果截止频率高于nyquist频率,DLPF1滤波器如何帮助我? 谢谢, 阿米尔

2018-09-11 16:41:19

DSP的ADC前端除了有抗混叠滤波器还有什么??

2012-10-14 21:02:50

内部抗混叠滤波器的Bode图?编辑:antony_css于2015年2月17日8:26 PM编辑:antony_css于2015年2月17日下午8:27 以上来自于谷歌翻译 以下为原文I am

2018-10-24 11:28:42

你好,我正在使用 LIS2DTW12,但我不太了解截止频率是多少。我很困惑,抗混叠滤波器已切断固定为 400 Hz 的频率:那么在这张表中,LPF1 和 LPF2 之后的截止频率似乎是 ODR/2

2022-12-27 08:10:16

如下图所示,PLL中,滤波器带宽和环路带宽的关系是什么?以及滤波器中att是干啥的,请指教~谢谢!

2021-06-24 06:54:46

衰减特性,其对抗混叠滤波器的设计要求要低很多,多数情况下一阶RC电路能够满足抗混叠需求。)其次是模拟输入与基准输入的驱动问题。不同于大学课本上讲到的,现在市面上流行的大部分SAR型ADC不再是通过分压电

2019-08-06 04:45:15

我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR)的因子抽取调制器采样频率

2018-08-30 15:05:47

通带数字滤波器。正如我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR

2018-08-30 14:51:23

各位好!想请教如下问题:在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。我想请教的是:用RC低通滤波的话,转折频率是可以满足,但是RC

2019-05-17 13:30:09

AD7606简介:AD7606/AD7606-6/AD7606-4为16位同步采样模数数据采集系统(DAS),分别有 8、6、4个采集通道。片上集成模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器

2018-11-01 09:25:42

理解抗混叠滤波器(AAF)和OF的要求,则需理解PSD。考虑通过激励信号将输入信号同步扩大+1和–1倍的PSD。这等效于输入信号乘以相同频率的方波。图2a显示的是输入信号、基准电压源和PSD输出的时域

2019-10-16 08:30:00

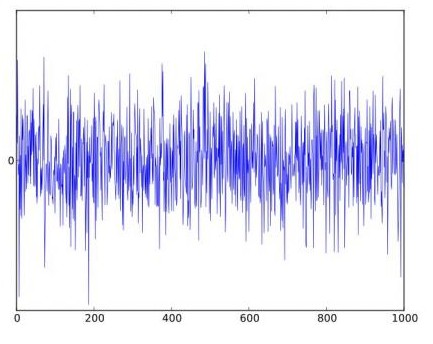

一般在ADC前端都会加抗混叠滤波器。但是,如果不加抗混叠滤波器的话,ADC采集到的信号频谱是不是由无限宽的频谱叠加得到的?比如我拿一个50MHz的ADC采集空中信号,是不是3GHz的信号也会混叠到我采集到的信号中?希望有大神能解答一下,谢谢啦~

2016-11-17 15:22:15

,计划采用5v单电源模式,在信号输入级增加一级无源低通滤波器是不是可以提高一定的指标?

疑问2:如果使用差分驱动器的输入级加上了50欧姆匹配的低通滤波器,输出级是不是不用考虑抗混叠滤波器?

PCB部分

2023-12-22 08:19:31

不同滤波器频率响应的比较通用的A/D转换器有:用于中等速率的SAR (逐次逼近) ADC;用于高速到超高速率的闪速ADC;用于低速系统的Σ-Δ ADC。它们都需要抗混叠滤波器,对滤波器的要求取决于转换

2019-01-02 19:03:43

滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。而对于程控

2019-09-04 08:34:31

LTC1569简介LTC1569的引脚功能LTC1569的工作模式利用LTC1569实现抗混叠滤波应用LTC1569设计低通滤波器的注意事项

2021-04-07 06:33:38

,ADS127L01具有用于更高频率应用的宽带宽平通带数字滤波器。正如我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低

2018-06-05 10:04:54

)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号到达ADC之前或者离开DAC之后,消除叠加在信号上面的高频噪声。如果ADC的输入信号

2019-07-31 06:24:00

AFAIK IIS2DH 没有模拟抗混叠滤波器。如果我使用低 ODR 设置并且输入信号频率高于 ODR/2,是否会出现混叠?因为在我们的测试中,我们经常在信号输出信号中出现尖峰。如果是这种情况,我们只能提高采样率吗?

2022-12-16 06:38:27

传统的窄带无线接收机,DVGA+抗混叠滤波器+ADC 链路的设计中,我们默认ADC 为高阻态,在仿真抗混叠滤波器的时候忽略ADC 内阻带来的影响。但随着无线技术的日新月异,所需支持的信号带宽越来越宽,相应的信号频率也越来越高,在这样的情况下ADC 随频率变化的内阻将无法被忽视。

2019-08-20 07:30:05

我想用AD9467进行射频信号的欠采样处理,如何设计前端的调理电路来保证其抗混叠和阻抗匹配呢?前端射频信号是500MHz±5MHz的信号,经过500±6MHz的带通滤波器和射频放大器对信号进行滤波

2023-12-11 06:14:17

1/2倍采样频率的分量时,数字滤波器因为频谱的混叠而不能正常工作。如果超过1/2采样频率的频率分量不占主要地位,通常的解决办法是在模/数转换电路之前放置一个低通滤波器(即抗混叠滤波器)将超过的高频

2017-11-10 16:43:22

(即抗混叠滤波器)将超过的高频成分滤除,否则就必须用模拟滤波器实现要求的功能。7)数字滤波器与模拟滤波器的使用方式不同对于电子工程设计人员来讲,使用模拟滤波器时通常是通过直接购买满足性能的滤波器件,或

2017-05-25 09:25:37

用欠采样,混叠使得AD系统作为混频器工作。 本应用笔记讨论数据采样系统的不同滤波要求,介绍混叠以及用于抗混叠的不同类型滤波器。滤波是一种我们往往视为当然的常见过程。我们在打电话时,接收器滤除其它所有信道

2019-07-30 06:11:02

可编程二阶低通滤波器电路。在数据采集系统信号路径中发现的最常见的滤波器是低通滤波器。这种类型的滤波器通常用于减少A / D转换器混叠误差。如果通过多路复用器向A / D转换器施加多个信号,则每个信号源可能有其自己的一组滤波器要求,即建立时间,快速过渡区域

2019-08-21 08:53:11

输入85MHZ中频,带宽20MHZ(起始频率:75MHZ;截止频率:95MHZ)的中频信号给AD9649;想设计一个无源抗混叠滤波器;请高手给予指点!

2015-04-23 15:19:28

本文对有源抗混叠滤波电路对驱动运放的要求,进行了分析,分别从高频参数单位增益带宽和高速参数建立时间,压摆率以及运放的电流驱动能力,分析了系统对驱动放大器的要求。

2021-04-07 06:09:16

调谐特定频率并消除其它频率。为了使高频信号衰减,所有数据采集系统都在模数转换器(ADC)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号

2019-07-29 07:15:50

(ADC)前面有一个抗锯齿(低通)滤波器,或者在数模转换器(DAC)后面有一个抗镜像(低通)滤波器。这种模拟滤波还可以在信号到达ADC之前或者离开DAC之后,消除叠加在信号上面的高频噪声。如果ADC的输入

2019-08-20 07:46:51

模拟电路1.有源滤波器和无源滤波器的区别无源滤波器:这种电路主要有无源元件R、L和C组成有源滤波器:集成运放和R、C组成。具有不用电感、体积小、重量轻等优点。集成运放的开环电压增益和输入阻抗均很高

2021-07-22 08:19:19

模拟滤波器在电子信号合成系统中应用广泛,可为ADC提供抗混叠和降噪,为DAC提供信号重建滤波1。不同的设计要求需要使用不同的滤波器架构,常用的滤波器有贝塞尔、巴特沃思以及椭圆滤波器。

2019-08-14 06:14:56

高性能模式下使用 3.3kHz ODR,模拟抗混叠滤波器带宽设置为 1.5kHz,数字滤波器设置为 ODR/2。在生成的频谱图中,频率扫描信号在多次穿过 ODR/2、ODR 和 1.5*ODR 后混叠

2022-12-15 08:14:24

DN16- 用于抗混叠应用的开关电容低通滤波器

2019-07-08 09:21:14

若要理解抗混叠滤波器(AAF)和OF的要求,则需理解PSD。考虑通过激励信号将输入信号同步扩大+1和–1倍的PSD。这等效于输入信号乘以相同频率的方波。图2a显示的是输入信号、基准电压源和PSD输出

2021-09-10 07:00:00

) 的输入前放置一个抗混叠滤波器,以防止频率分量交叉进入上部那奎斯特区域。然而,有时候这是一个好事情。在运行于超高频模式下的射频 (RF) 系统中,处理器(或者一个现场可编程门阵列 [FPGA

2018-09-05 15:54:06

的输入噪声、电源噪声、基准源噪声、 数字接口馈通噪声、ADC 芯片热噪声或量化噪声。表1简要列出了模拟滤波器与数字滤波器的优点和缺点。表1.模拟滤波器与数字滤波器模拟滤波器考虑抗混叠滤波器放在ADC

2018-10-16 18:45:40

。高性能运放和PC上的专用软件方便了宽带有源滤波器的设计,但这并未解决任意特定应用的问题。对视频滤波器而言,特定的应用与信号制式给每个电路设计都带来了细微的差别。以下是两类主要的视频应用:抗混叠滤波器:这一

2021-05-14 07:55:00

无源抗混叠滤波器的驱动有源抗混叠滤波器的驱动

2021-04-21 06:53:00

设计IIR滤波器的双线性变换法1、脉冲响应不变法的主要缺点:对时域的采样会造成频域的“混叠效应”,故有可能使所设计数字滤波器的频率响应与原来模拟滤波器的频率响应相差很大,而且不能用来设计高

2008-08-01 17:02:57

大家好!我看一些电能电量分析采集的文献中提到对信号进行FFT,所以要在ADC前端设计抗混叠滤波器,以避免产生延拓频率的噪声。一般采样频率为fs时,滤波器截止频率为fs/2。如果我不对信号进行

2018-10-09 16:08:19

阅读手册,AD7606内部有一个抗混叠滤波器,在-5~+5V范围下的-3db带宽为15khz,在-10~10V范围内-3db带宽是22KHZ,下降沿大约在10khz左右开始。 我的回波信号

2018-09-11 09:54:07

,在信号输入级增加一级无源低通滤波器是不是可以提高一定的指标?疑问2:如果使用差分驱动器的输入级加上了50欧姆匹配的低通滤波器,输出级是不是不用考虑抗混叠滤波器? PCB部分:疑问1:同时在

2018-11-07 09:35:54

如何利用开关电容滤波器实现抗混叠滤波?

2021-04-23 06:12:02

再设计电路时,差分信号在介入差分ADC时,需要在AINN和AINP输入引脚前加入一阶抗混叠滤波器,滤除高频干扰,请问专家应该如何设计,或则有什么参考资料,第一次设计抗混叠滤波器!谢谢

2018-11-14 11:07:35

无源元件R、L和C组成模拟滤波器,六十年代以来,集成运放获得了迅速地发展,由它和R、C组成的源滤波器,具有不用电感、体积小、重量轻等优点。此外,由于集成运放的开环电压增益和输入阻抗均很高,而输出阻抗又很低

2011-07-28 10:01:48

输入,其比开关电容输入更容易驱动。

对频带特定IF抗混叠滤波器的要求可以显著放宽,原因是内部环路滤波器具有通带优势,从而简化系统架构。

一些缺点:

需要超高频时钟以实现有效过采样比(OSR)。例如

2023-12-11 08:14:37

ADC电路需要在前端设计专用的多阶有源滤波器,滤掉频率超过fs/2的信号。(注:Σ-Δ型ADC理论上也需要抗混叠滤波器,但是由于其过采样特性及内部数字滤波器的带外衰减特性,其对抗混叠滤波器的设计要求要低

2022-11-07 06:09:13

高精度SAR模数转换器的抗混叠滤波考虑因素

2021-01-11 07:53:43

连接,这就会引起失真。务必将AAF的阻带区间规定为平坦的,因为宽带噪声仍有可能折回带内(见图8)。

图8. 抗混叠滤波器

多数转换器具有很宽的模拟输入带宽。如果不使用AAF,混叠会降低动态范围。AAF

2023-12-18 07:42:00

ADC的全部额定带宽内,输入阻抗都是恒定的。 设计抗混叠滤波器(AAF)时应当注意,过多的元件可能会导致容差不匹配,进而产生偶数阶失真。电感并非特性相同,不同电感的响应可能大不相同。廉价、低质量的电感一般

2018-01-23 16:01:44

良好的焊接连接,这就会引起失真。务必将AAF的阻带区间规定为平坦的,因为宽带噪声仍有可能折回带内(见图8)。图8. 抗混叠滤波器 多数转换器具有很宽的模拟输入带宽。如果不使用AAF,混叠会降低动态范围

2018-09-17 15:38:24

连接,这就会引起失真。务必将AAF的阻带区间规定为平坦的,因为宽带噪声仍有可能折回带内(见图8)。图8. 抗混叠滤波器多数转换器具有很宽的模拟输入带宽。如果不使用AAF,混叠会降低动态范围。AAF应按照等于

2018-10-18 11:23:57

如何使用模拟滤波器注入噪声

例如,您 Δ-Σ ADC 输入端 RC 滤波器或放大器的低通滤波器会产生更大噪声的数字输出。难道您没有设计过降低噪声的

2010-03-23 08:57:02 749

749

电子发烧友App

电子发烧友App

评论