随着微电子技术的快速发展,数模转换器(DAC)作为连接数字世界和模拟信号之间的桥梁正发挥着越来越重要的作用,而且现代计算机、无线通讯等信息产业的不断进步,对DAC的速度、精度等性能指标也不断提出更高的要求。

为满足现代航天高科技产业对高速高精度DAC芯片的需求,本文基于Mixed-Signal(混合信号)CMOS工艺技术,设计了一个采用分段式电流舵结构的16位400MSPS的D/A转换器,论文第二节在理论分析和电路设计基础上确定了该DAC的系统结构及工作原理,第三节给出了电路中采用的自校准技术及其设计实现,流片后电路的实测结果在第四节予以说明,最后给出论文研究工作的简要总结。

16位400M DAC的系统构架

在目前常用的DAC结构中普遍采用的是电流输出型DAC,这是因为电流输出有着速度快、电源利用率高、应用广泛、输出范围宽等特点,使得该结构的DAC适合于高速高精度的设计要求。

要实现高速高分辨率的DAC,通常采用分段电流舵的结构,即温度计码和二进制码相结合的控制结构。温度计码具有优良的单调性但其复杂度、面积和功耗会随着位数的增加而急剧增大,二进制码具有结构简单的特点但会影响DAC单调性和动态性能,所以需要在面积、功耗、复杂度和性能之间进行折衷。本论文所采用的分段电流舵DAC电路结构也是基于面积和电流源开关布线复杂性与电路性能之间的考虑,我们首先利用MATLAB仿真工具仔细研究了温度计码和二进制码对整个电路系统性能的影响,并确定了整个DAC转换器的分段比例,即在本论文所设计的DAC电路中采用了“7+4+5”的分段结构,其中高7位和中间4位分别采用单位电流源结构,而低5位则采用二进制加权电流源结构。

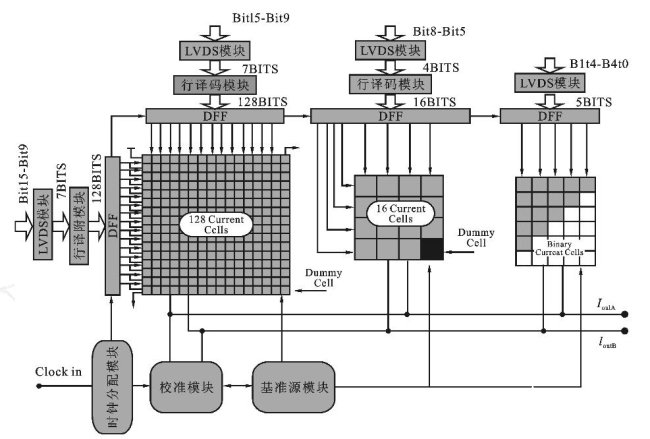

图1 16位400M DAC的功能结构框图

图1所示为基于上述分段电流舵而设计的16位400M DAC的系统构架框图。该电路主要由LVDS模块、行译码与列译码模块、带隙基准源模块、校准模块、偏置电路、时钟分配驱动模块以及模拟开关与电流源阵列等部分组成。

在图1中,Bit15~Bit0首先通过LVDS接收器转化成标准的CMOS信号,然后将其中的高7位二进制信号Bit15-Bit9通过译码器生成127路温度计码信号经控制线去控制电流源;中间4位二进制信号Bit8-Bit5则通过译码器生成15路温度计码信号去控制相应电流源阵列;低5位二进制信号Bit4~Bit0则直接通过同步锁存逻辑(DFF)去控制5个二进制电流源。

带隙基准源模块为整个电路系统提供了一个几乎与环境温度和电源电压无关的精准电压源。为了更好地与外部数据进行同步且确保转换器具有16bit的精度,电路设计中还采用了电流校准模块,利用电流校准模块对高7位二进制信号Bit15-Bit9所控制的127个单位电流源进行必要的校准以确保其输出电流的准确性。

如图1所示,电路输出电流的总量是由两部分相加而成,即单位电流源和五个二进制加权电流相加组成。若最低位电流源的输出电流为ILSB,则第二、三、四、五位的输出电流依次为:2ILSB、4ILSB、8ILSB、16ILSB,即每高一位的电流源输出电流分别为低一位的2倍,因此整个DAC低五位的总电流输出为31ILSB,而高7位所控制的127个电流源中的每个电流源的输出电流由下式给出:

Iunit=512ILSB (1)

由此可得到该DAC能够输出的总电流为:

Itotal=ILSB+2ILSB+4ILSB+8ILSB+16ILSB+32ILSB+…+127×512ILSB=65535ILSB (2)

在图1中,IoutA和IoutB分别为DAC的两个互补电流输出端,当输入的16位数字码全为0时,IoutA输出为0,而互补端IoutB输出为满量程电流Itotal,当16位输入数字码全为1时,IoutA为满量程输出,而互补端IoutB输出为0,通过公式(3)和(4)我们可以求出不同输入数字码时所对应的模拟电流输出值。

IoutA=(DAC INPUT CODE/65536)×Itotal (3)

IoutB=(65535-DAC INPUT CODE/65536)×Itotal (4)

在上式中,DAC INPUT CODE=0~65535。ILSB和Iunit的大小通常由基准电压源和电流输出管的尺寸来共同决定。如果把DAC的电流输出端接电阻负载,那么可以直接将电流转换成电压输出,由式(5)和(6)可以得到互补端的电压输出值。

VOUTA=IoutA×RLOAD (5)

VOUTB=IoutB×RLOAD (6)

最后总的差分输出电压为:

VDIFF=(IoutA-IoutB)×RLOAD (7)

由式(7)可以看出,采用差分电流输出时,当把差分变单端应用时,可使输出信号的幅度增加一倍,同时差分输出可提高DAC转换速度和动态特性。

本文下一页:校准电路设计

校准电路设计

长期以来,由于CMOS工艺中存在匹配误差,完全依靠工艺本征匹配实现电流型CMOS DAC将很难超过10位精度,同时DAC的动态特性也会随着时钟频率和信号频率的增加而变差。

通过减小寄生电容、缩短建立时间仍是解决DAC电路中动态特性最直接有效的方法。但是为了保证DAC静态特性,减少梯度误差和随机失配就需要增大晶体管尺寸和复杂的布局,这样就会增大寄生电容和电阻,在提高静态特性的同时会限制DAC采样率和高频性能。

为了能够较好解决上述问题,我们可以采用校准技术,既能在保证电路高精度的同时减小电流源矩阵在DAC中所占的面积,又缓解了电路对版图和工艺的严格要求。因此,校准技术在保证DAC静态特性的同时能有效提高动态特性,同时还能降低电路对工艺、温度的敏感性,保证DAC长期稳定地工作。

图2 自校准流程图

本论文采用了一种新的适合高精度、高速度DAC电路的自校准技术。这种自校准技术能够有效地校正各个电流源的失配,并降低对电流源输出电阻的要求。图2所示为我们采用的数字自校准方案的流程图。从该流程图中可见,在这个自校准的过程中,我们首先将待校准量与参考值进行比较,比较后的结果经一个ADC转换后存储到静态数据存储器(RAM)中,由此形成一个唯一对应的数字校准信号再送到一个校准的DAC中,最后完成待校准量的自校准。

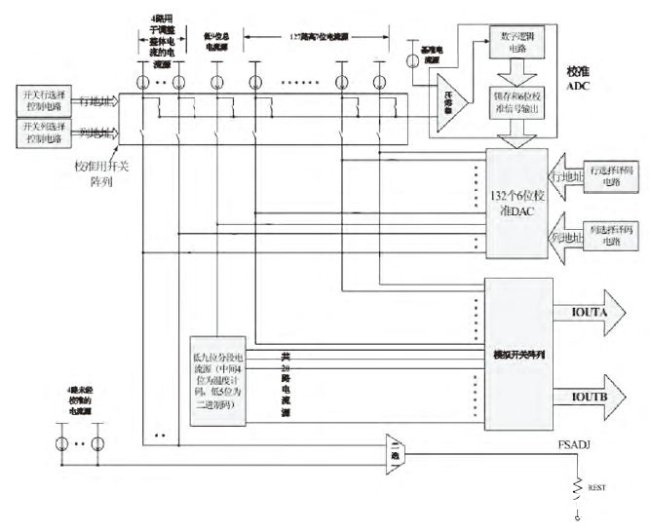

图3 自校准电路原理图

图3所示为实现上述自校准过程的电路原理图,为了保证整个DAC电路具有16位的线性度,芯片设计中内置了132个用来校准电流源输出线性度的DAC,它们分别是图中的127路高7位电流源,1路低9位的总电流源和4路用于调整输出增益的电流源,另外还有一路基准电流源。当进行自校准时,开关的行列选择电路将每一路电流源按顺序选通到比较器的输入端和基准电流源进行比较,比较后的结果经数字逻辑处理后将6位数字信号输入到相应的校准DAC的6个输入端。每路电流源都有一个校准DAC与其唯一对应,当选择相应电流源时也就对应选上了相应的校准DAC,选择DAC也需要相应的行列选择电路进行按顺序的选定。当一路电流源完成校准后,其唯一对应的校准DAC的6位数字值也已经确定并存在了静态存储器中,也就是所需调整的电流量已经加在了相应的电流源上。高7位中的每路电流源都有一个校准DAC来进行输出电流调整,低9位则是进行整体的电流调整,高7位和低9位电流源输出的电流经校准DAC校准后通过模拟开关阵列最终输出到差分电流输出端。另外还有4路电流源是用于设定整个电路输出电流范围的,这4路电流源经相应的4个增益校准DAC校准后,其总输出电流流过电阻RESET后可调整整个DAC的输出电流增益。

图4 自校准过程仿真波形图

图4给出了上述自校准过程的仿真波形,从图中的仿真结果我们可以看到,待校准电流源的输出在不断趋近基准电流源的输出,并且这个过程在不断地重复,直至所有的电流源均校准完毕为止。所有校准完毕的电流源最后经电流源开关阵列输出到差分电流输出端,这样就完成了整个电流源的校准过程。通过上述自校准过程,既保证了整个电路输出的线性度,同时也调整了电路输出的增益误差,优化了输出特性。

整体测试结果和电路概貌

基于0.25微米混合信号CMOS工艺技术,并采用上述自校准电路设计方案,我们完成了一个采用分段式电流舵结构的16位400MSPS的D/A转换器芯片的版图设计,如图5所示,该电路芯片尺寸为4.9×4.9mm2,整个DAC电路一共有110个压焊块。目前该电路已经成功完成工艺流片,电路测试评估板的实物照片如图6所示。

图5 DAC芯片的版图示意图

图6 电路测试评估板

图7 系统的SFDR结果图(不带校准)

图8 系统的SFDR结果图(带校准)

对封装后的DAC电路进行的初步测试结果表明,该DAC电路工作正常。图7为系统不带校准的实测SFDR,图8为系统带校准后的实测SFDR。可见经过自校准后,电路的SFDR提升了十几个dB,并且谐波也明显减小。

表1 400MHz时钟下,自校准后的转换测试结果统计表

我们对该DAC芯片还进行了其它各项指标的测试,电路在400MHz时钟频率下经过自校准后的测试结果如下表1所示。由表中各项测试数据可见,该芯片的各项性能参数指标优异,表明整个DAC芯片的性能良好。

总结

基于0.25微米Mixed-Signal CMOS制造工艺,本文设计并实现了一个高速高精度单片集成化的数模转换器(DAC)。论文中的DAC电路采用分段式电流舵结构,其时钟的采样频率为400MHz,分辨率为16Bit。电路设计中还采用了电流校准技术,既保证了DAC电路的高精度,也减小了梯度误差的影响。实际流片后的测试结果表明,自校准技术的采用可使DAC

电路的精度和性能得到大幅度的提升,芯片的输出谐波也明显减小。本DAC产品是我们在高速高精度DAC电路研制方面的一次尝试,它的研制成功为我们今后研制开发性能更加优异的数模转换器产品打下了良好的技术基础。

责任编辑:gt

电子发烧友App

电子发烧友App

评论