抗混叠滤波器的设计包括一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号带宽的位置上,而数字抽取滤波器衰减大多数有害的带外信号。当把二者组合在一起时,它们可以实现更加自由的抗混叠滤波器响应,只需几个分立式组件即可实现这一功能。

2015-12-22 09:26:50 1531

1531 有大神知道12位ADC采样保持器里面的电容量级是多少吗?因为设计电路的时候要使用抗混叠滤波器,需要考虑采样保持器电容与抗混叠滤波电容的大小关系

2023-11-02 06:27:44

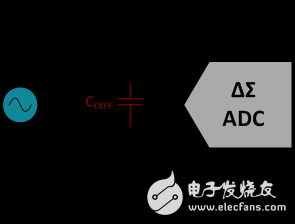

滤波器时,请考虑以下3个通用指导原则:选择你的滤波器截止频率最简单的抗混叠滤波器是一个单极、低通滤波器,如图2所示,它使用一个串联电阻器 (R) 和共模电容器 (CCM)。设计这个滤波器的第一步就是选择

2018-09-05 14:52:59

本文研究了Nyquist-Shannon采样定理的一个重要方面,并解释了它与模数转换中抗混叠滤波器需求的联系。到目前为止,我们已经探索了Nyquist-Shannon定理的理论基础,包括频域对采样

2020-09-18 10:12:55

锐敏的片式电磁干扰滤波器。根据电路特性选择适当的滤波器可以得到令人十分满意的抗EMI效果,特别适用于抑制数字电子设备及高速数据总线产生的噪声。EMI滤波器按构成元件可分为电感器、电容器、LC复合型

2019-05-20 04:39:41

滤波器在抗EMI中的应用及发展,看完你就懂了

2021-05-25 06:35:36

的layout布局和布线后,使用最多的方法是用共模滤波器来滤除共模干扰。本文主要介绍滤波器的选型原则,希望对大家有所帮助。

2020-11-02 08:40:45

产品中需要用到AD7606,回波模拟信号的幅度最小在零点几伏,考虑到ADC的输入范围为-5~5,有没有必要在ADC前面加一个运放,将回波信号适当放大一下?看到手册中说内部有抗混叠滤波器且输入阻抗为

2018-09-12 11:15:54

阅读手册,AD7606内部有一个抗混叠滤波器,在-5~+5V范围下的-3db带宽为15khz,在-10~10V范围内-3db带宽是22KHZ,下降沿大约在10khz左右开始。

我的回波信号

2023-12-18 06:22:57

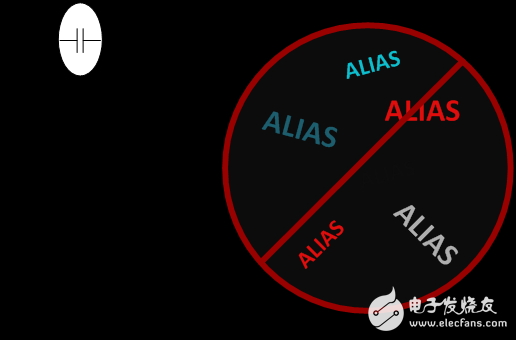

针对此问题的解决方案:那就是抗混叠滤波器。抗混叠滤波器大多数ADC之前都会有一个抗混叠滤波器,而这个滤波器与衰减信号(超过了所需带宽)的低通滤波器没有什么不同。如图4所示,一个理想抗混叠滤波器的响应

2018-09-06 16:00:00

100dBFS(满量程)的神奇屏障,用户面临的真正挑战体现在为要数字化的信号设计模拟调理电路,以及相关抗混叠滤波器的设计两个方面。在过去的二十年中,采样速率和滤波技术已经有了很大的发展,现在我们可以结合

2021-08-04 07:00:00

性能, 采用三阶巴特沃斯滤波器和低噪声超宽带宽差分放大器ADL5565 设计出用于高频信号直接采样系统中的抗混叠滤波器。

为了抵消三阶巴特沃斯滤波器插入损耗, 需对流过滤波器信号放大。在本系统中使

2023-11-23 06:01:47

HiADS1675 ,内部有2种滤波器 ,delta-sigma (ΔΣ) 是用做抗混叠滤波器吗?或者还用作其他? 有没有相关的详细文章介绍?

2019-05-22 06:17:18

喜 我有几个问题。 1. Acc的顺序抗混叠滤波器是什么? 2.陀螺的顺序抗混叠滤波器是什么? 3.如果截止频率高于nyquist频率,DLPF1滤波器如何帮助我? 谢谢, 阿米尔

2018-09-11 16:41:19

CIC抽取滤波器MATLAB仿真和FPGA实现(1)设计理想滤波器目标:1、滤波器在有效频段内纹波满足设计要求。2、抽取或内插处理后在有效频段内不产生混叠。3、滤波器实现简单,需要资源较少。这个

2021-08-17 08:27:40

DSP的ADC前端除了有抗混叠滤波器还有什么??

2012-10-14 21:02:50

内部抗混叠滤波器的Bode图?编辑:antony_css于2015年2月17日8:26 PM编辑:antony_css于2015年2月17日下午8:27 以上来自于谷歌翻译 以下为原文I am

2018-10-24 11:28:42

你好,我正在使用 LIS2DTW12,但我不太了解截止频率是多少。我很困惑,抗混叠滤波器已切断固定为 400 Hz 的频率:那么在这张表中,LPF1 和 LPF2 之后的截止频率似乎是 ODR/2

2022-12-27 08:10:16

我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR)的因子抽取调制器采样频率

2018-08-30 15:05:47

通带数字滤波器。正如我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR

2018-08-30 14:51:23

各位好!想请教如下问题:在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。我想请教的是:用RC低通滤波的话,转折频率是可以满足,但是RC

2019-05-17 13:30:09

问题:传感器频响为3k,采集系统中的上限频率设为10k(应该是抗混滤波器的频率),采样频率设为50k。采集到的传感器信号中,为什么有大于10k的频率?采样前,滤波器不是已经滤掉大于10k的信号了吗。

2017-05-05 23:57:14

做一个FIR数字低通滤波器,信号源是正弦信号加均匀白噪声,显示混叠信号和经过滤波后信号波形 以及频谱分析,

2014-05-10 00:05:31

一般在ADC前端都会加抗混叠滤波器。但是,如果不加抗混叠滤波器的话,ADC采集到的信号频谱是不是由无限宽的频谱叠加得到的?比如我拿一个50MHz的ADC采集空中信号,是不是3GHz的信号也会混叠到我采集到的信号中?希望有大神能解答一下,谢谢啦~

2016-11-17 15:22:15

关于有源滤波器的设计,这里有几个问题请教各位前辈,求前辈指导!1.有源高通滤波器的增益是不是不会小于0dB,我用滤波器软件设计时,无法把增益设置为小于0dB的值;2.如何判断一个有源高通滤波器是否

2017-11-15 12:39:35

。抗混叠滤波器采用了MAX7418-21系列产品,该系列滤波器提供各种滤波器类型,如贝塞尔、巴特沃斯、椭圆等。角频率设置为1/100 fClk。考虑到DSP控制转换器的采样(只需要一个定时器),同一

2019-01-02 19:03:43

的关系CIC滤波器通常用于抗混叠抽取/内插滤波器(抽取与内插结构见本文开头的链接)。考虑抽取/内插的过程、CIC滤波器的特性(系数为1的特殊FIR滤波器)以及FIR滤波器的实现结构,就会发现,当CIC

2020-09-28 09:36:54

滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。而对于程控

2019-09-04 08:34:31

LTC1569简介LTC1569的引脚功能LTC1569的工作模式利用LTC1569实现抗混叠滤波应用LTC1569设计低通滤波器的注意事项

2021-04-07 06:33:38

AFAIK IIS2DH 没有模拟抗混叠滤波器。如果我使用低 ODR 设置并且输入信号频率高于 ODR/2,是否会出现混叠?因为在我们的测试中,我们经常在信号输出信号中出现尖峰。如果是这种情况,我们只能提高采样率吗?

2022-12-16 06:38:27

分析了开关电容滤波器的“共振”现象及其产生机理,针对该现象提出了解决办法,并结合信号处理仪器系统给出了采用MAX293制作抗混滤波器的方案。

2021-03-30 07:36:29

传统的窄带无线接收机,DVGA+抗混叠滤波器+ADC 链路的设计中,我们默认ADC 为高阻态,在仿真抗混叠滤波器的时候忽略ADC 内阻带来的影响。但随着无线技术的日新月异,所需支持的信号带宽越来越宽,相应的信号频率也越来越高,在这样的情况下ADC 随频率变化的内阻将无法被忽视。

2019-08-20 07:30:05

、如何设计一个可靠的抗混叠滤波,使其抗混叠效果明显,因为我的前端已经加入了带通滤波器,可是效果依旧不是很理想,很多次谐波分量?

3、如果有更好的方案推荐的话,会非常感激您的!

2023-12-11 06:14:17

1/2倍采样频率的分量时,数字滤波器因为频谱的混叠而不能正常工作。如果超过1/2采样频率的频率分量不占主要地位,通常的解决办法是在模/数转换电路之前放置一个低通滤波器(即抗混叠滤波器)将超过的高频

2017-11-10 16:43:22

。如果输入信号的频率分量包含超过滤波器1/2倍采样频率的分量时,数字滤波器因为频谱的混叠而不能正常工作。如果超过1/2采样频率的频率分量不占主要地位,通常的解决办法是在模/数转换电路之前放置一个低通滤波器

2017-05-25 09:25:37

消除频率的混叠 缺点: 时域到频域的变换是非线性的,在高频处有较大的失真。 三、数字高通滤波器的设计步骤: ①数字高通滤波器的技术指标为:通带截止频率ωp阻带截止频率ωs通带衰减频率αP阻带

2019-03-13 06:30:00

用欠采样,混叠使得AD系统作为混频器工作。 本应用笔记讨论数据采样系统的不同滤波要求,介绍混叠以及用于抗混叠的不同类型滤波器。滤波是一种我们往往视为当然的常见过程。我们在打电话时,接收器滤除其它所有信道

2019-07-30 06:11:02

可编程二阶低通滤波器电路。在数据采集系统信号路径中发现的最常见的滤波器是低通滤波器。这种类型的滤波器通常用于减少A / D转换器混叠误差。如果通过多路复用器向A / D转换器施加多个信号,则每个信号源可能有其自己的一组滤波器要求,即建立时间,快速过渡区域

2019-08-21 08:53:11

0 引言随着无线局域网(WLAN)和全球微波接入互操作(Wimax)的迅速发展,多频通信系统将成为今后无线通信的主导发展方向。本文提出了一种新型的三频带通滤波器设计方法,构成该滤波器的谐振腔是通过在通常的开环谐振腔内加载一个倒F型枝节,通过调节该枝节的各段长度及位置就可以实现所需要的三个谐振频率。

2019-06-24 07:42:19

输入85MHZ中频,带宽20MHZ(起始频率:75MHZ;截止频率:95MHZ)的中频信号给AD9649;想设计一个无源抗混叠滤波器;请高手给予指点!

2015-04-23 15:19:28

本文对有源抗混叠滤波电路对驱动运放的要求,进行了分析,分别从高频参数单位增益带宽和高速参数建立时间,压摆率以及运放的电流驱动能力,分析了系统对驱动放大器的要求。

2021-04-07 06:09:16

模拟滤波器在电子信号合成系统中应用广泛,可为ADC提供抗混叠和降噪,为DAC提供信号重建滤波1。不同的设计要求需要使用不同的滤波器架构,常用的滤波器有贝塞尔、巴特沃思以及椭圆滤波器。

2019-08-14 06:14:56

高性能模式下使用 3.3kHz ODR,模拟抗混叠滤波器带宽设置为 1.5kHz,数字滤波器设置为 ODR/2。在生成的频谱图中,频率扫描信号在多次穿过 ODR/2、ODR 和 1.5*ODR 后混叠

2022-12-15 08:14:24

在语音数字系统的设计中, 为了防止在数据采集后发生混叠失真, 同时因为前端一般会混入50 Hz 的交流电源噪声, 为了阻止语音频带外的噪声, 在A/D 转换之前要设置一个滤波器。并且, 为了在接收端

2009-01-24 00:01:49

DN16- 用于抗混叠应用的开关电容低通滤波器

2019-07-08 09:21:14

状态,使EMI信号产生反射。即滤波器设什应遵循下列原则:源内阻是高阻,则滤波器输人阻抗就应该是低阻,反之亦然;负载是高阻,则滤波器输出阻抗就应该是低阻,反之亦然。对于EMI信号,电感是高阻,电容是低阻

2020-10-29 09:02:19

的设计原则、网络结构、参数选择<br/>1设计原则——满足最大阻抗失配插入损耗要尽可能增大,即尽可能增大信号的反射。设电源的输出阻抗和与之端接的滤波器的输人阻抗分别为ZO

2009-10-10 13:07:57

) 的输入前放置一个抗混叠滤波器,以防止频率分量交叉进入上部那奎斯特区域。然而,有时候这是一个好事情。在运行于超高频模式下的射频 (RF) 系统中,处理器(或者一个现场可编程门阵列 [FPGA

2018-09-05 15:54:06

一个–10 dBFS 混叠镜像。因此,若ADC 之前没有合格的抗混叠 模拟滤波器,当使用过采样时,数字滤波器就可能会因为抽取而 引起混叠镜像。应使用模拟抗混叠滤波器来消除这种叠加于模拟 信号上的噪声

2018-10-16 18:45:40

以FMS6403为例来说明视频滤波器的原理,它是飞兆半导体公司针对电视、机顶盒和DVD播放机对扩展滤波器的需要而设计的新一代滤波器,具有逐行扫描能力。它由三个截止频率分别为30MHz、15MHz和8MHz的6阶滤波器构成。这些滤波器可旁路,这样带宽只受输出放大器的限制。

2019-09-30 09:02:20

。高性能运放和PC上的专用软件方便了宽带有源滤波器的设计,但这并未解决任意特定应用的问题。对视频滤波器而言,特定的应用与信号制式给每个电路设计都带来了细微的差别。以下是两类主要的视频应用:抗混叠滤波器:这一

2021-05-14 07:55:00

无源抗混叠滤波器的驱动有源抗混叠滤波器的驱动

2021-04-21 06:53:00

设计IIR滤波器的双线性变换法1、脉冲响应不变法的主要缺点:对时域的采样会造成频域的“混叠效应”,故有可能使所设计数字滤波器的频率响应与原来模拟滤波器的频率响应相差很大,而且不能用来设计高

2008-08-01 17:02:57

ISD2532采用28脚封装。该 CMOS 设备包括一个片上振荡器,麦克风前置放大器,自动增益控制,抗混叠滤波器,平滑滤波器,扬声器放大器,和高密度的多级存储阵列。

2021-04-14 06:10:59

ISD2540采用28脚封装。该 CMOS 设备包括一个片上振荡器,麦克风前置放大器,自动增益控制,抗混叠滤波器,平滑滤波器,扬声器放大器,和高密度的多级存储阵列。

2021-04-14 06:25:59

概述:ISD2564采用28脚封装。该CMOS设备包括一个片上振荡器,麦克风前置放大器,自动增益控制,抗混叠滤波器,平滑滤波器,扬声器放大器,和高密度的多级存储阵列。

2021-04-14 07:00:45

大家好!我看一些电能电量分析采集的文献中提到对信号进行FFT,所以要在ADC前端设计抗混叠滤波器,以避免产生延拓频率的噪声。一般采样频率为fs时,滤波器截止频率为fs/2。如果我不对信号进行

2018-10-09 16:08:19

阅读手册,AD7606内部有一个抗混叠滤波器,在-5~+5V范围下的-3db带宽为15khz,在-10~10V范围内-3db带宽是22KHZ,下降沿大约在10khz左右开始。 我的回波信号

2018-09-11 09:54:07

如何利用开关电容滤波器实现抗混叠滤波?

2021-04-23 06:12:02

再设计电路时,差分信号在介入差分ADC时,需要在AINN和AINP输入引脚前加入一阶抗混叠滤波器,滤除高频干扰,请问专家应该如何设计,或则有什么参考资料,第一次设计抗混叠滤波器!谢谢

2018-11-14 11:07:35

对应的数域频率是π,因此我们得出,抗混叠低通滤波器的截止频率是π/M三、内插抽取的过程是降低采样率的过程,那么插值的过程当然就是提高采样率的过程。大体的思路可以这么理解,我们将经f1抽样下得

2015-08-29 15:25:38

与干扰信号在频率上的差别:有用信号与干扰信号的频率相差越小,需要滤波器的器件数量越多。3. 使用滤波器的电路的阻抗:一个基本的原则是,滤波器中的电容对着高阻抗电路,电感对着低阻抗电路。这里的所谓高低,可以以50Ω为参考。

2011-07-05 17:48:07

ADC电路需要在前端设计专用的多阶有源滤波器,滤掉频率超过fs/2的信号。(注:Σ-Δ型ADC理论上也需要抗混叠滤波器,但是由于其过采样特性及内部数字滤波器的带外衰减特性,其对抗混叠滤波器的设计要求要低

2022-11-07 06:09:13

高精度SAR模数转换器的抗混叠滤波考虑因素

2021-01-11 07:53:43

技术在计算机测控技术、通信、数据采集等领域均有广泛的应用。如在通信领域中为获得最高信噪比所设置的匹配滤波器和为减少基带传输过程中的码间串扰所设置的均衡器;在数据采集中设置的限带抗混迭滤波和D/A 转换

2009-12-05 09:08:06

混叠

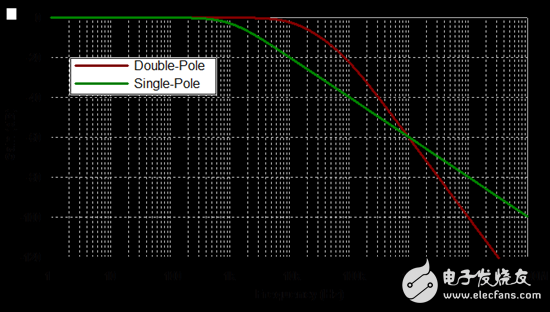

我们知道,在高精度ADC应用中使用抗混叠滤波器是有益的,不过,设计合适的抗混叠滤波器也同样重要—如果你不小心的话,就像把有害误差从系统中消除一样,很容易将有害误差引入到你的系统中。在为你的应用设计抗混叠滤波器时,请考虑以下3个通用指导原则:

选择你的滤波器截止频率

最简单的抗混叠滤波器是一

2021-11-10 09:40:51 587

587 我们知道,在高精度ADC应用中使用抗混叠滤波器是有益的,不过,设计合适的抗混叠滤波器也同样重要—如果你不小心的话,就像把有害误差从系统中消除一样,很容易将有害误差引入到你的系统中。在为你的应用设计抗混叠滤波器时,请考虑以下3个通用指导原则:

2023-04-17 09:17:43 997

997 交流滤波器可以让直流系统在运行时消除直流系统产生的谐波,此外还可以补偿直流控制系统消耗的无功功率。在不同的换流站中使用的交流滤波器也不尽相同,那么在不同换流站中交流滤波器的配置原则是什么呢?下面就由萨顿斯来为您解答这个问题。

2023-05-22 10:46:09 438

438 安装电源滤波器要遵循的原则有哪些? 安装电源滤波器是一项关键的任务,旨在净化传输到设备的电源,并保护其免受电源干扰的影响。以下是安装电源滤波器时应遵循的原则: 了解电源滤波器的类型和功能: 在开始

2024-01-11 15:59:09 93

93

电子发烧友App

电子发烧友App

评论