完整的单端 75Ω 输入阻抗至差分输出、2.5V 输入至 1.25V 差分共模电平移位、以及采用外部电阻器实现单端至差分增益 = 2 的电路实例。

2013-11-05 09:17:33 1641

1641

25MHz的时钟源如何得到4路200MHz的时钟信号

2019-01-10 10:19:05

十六进制非反相高电平到低电平移位器

2023-03-24 14:58:43

出LTC1555IGN,SZA2044Z,TMS320F280200PTT等现货IC,能找到规格的都有整理上传,仅供大家作参考,要货请联系明佳达电子。LTC1555IGN逻辑器件 - 转换器,电平移位

2019-05-20 17:08:39

LTC6948-2的输入参考时钟的电平标准是什么,谢谢

2024-01-08 08:23:12

。LTC2400的三线接口线分别是数据输出(SDO)、时钟(SCK)和片选(CS)。其工作流程如图3所示。LTC2400完成转换就进入睡眠状态。睡眠状态的供电电流仅为20μA。若CS一直为高电平,芯片将

2018-12-12 10:25:29

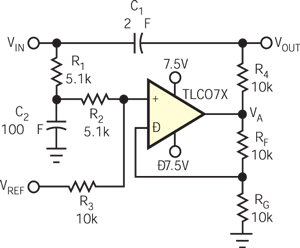

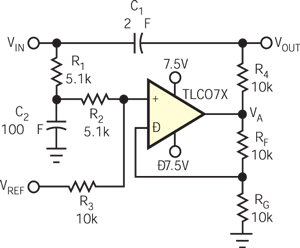

。 该电路基本原理是图1所示的简单的电平移动电路。在Vs和信号源之间连接两个串联电阻器,将信号衰减到一半并偏置到Vs/2。中心抽头被缓冲,然后可由单边电源电路处理。在信号源端和数值相等的负电源之间也连接两个串联电阻器以抵消来自信号源端的DC偏置电流。 图1. AC信号电平移动电路

2011-01-02 14:03:03

关于AD9740我有两个问题。

1、它的时钟可以用200MHz吗?

2、它的两个互补输出,我只需要用一个。原输出引脚我接到高速运放的同相端的一个49.9欧姆电阻上,这样20mA可以产生0到1V变化的输出,而互补引脚我直接接一个小电阻上,反正也不使用它。这样可以吗?

2023-12-06 06:07:34

AD9958/9规格书上推荐最高输出为200MHz,我想问一下,我输出200.3MHz应该没什么问题吧?还有输出到210MHz可以吗?

2018-12-21 09:31:30

我利用CYCLONE IV EP4CE-15F的PLL,输入时钟50MHz,输出时钟200MHz,后面这个200MHz 时钟还在FPGA内部进行了一些逻辑采样和分配,但是从FPGA中引出这个

2014-05-28 13:15:53

2输入或门/CMOS逻辑电平移位器

2022-11-04 17:22:44

我不太清楚OCLK想连接的是什么?说我运行200mhz DDR,CLK端口连接到oserde转发的200mhz clk,CLB反转,CLKDIV是我在fpga 100mhz的并行clk,OCLK与并行clk 100mhz或200mhz相同?

2020-06-08 08:58:51

电平移位器 TSSOP-14

2024-01-23 18:28:31

电平移位器 TSSOP-20

2024-01-23 18:31:59

单电源逆变门CMOS逻辑电平移位器

2023-03-23 08:09:46

单电源2输入正或门CMOS逻辑电平移位器

2023-03-28 18:29:22

单电源单缓冲门CMOS逻辑电平移位器

2023-03-24 14:49:19

).Is无论如何要改善这个?请查找问题的快照(1)电平移位器图(2)波形@ 5Mhz(蓝色= GPIO_HEADER_0_LS,黄色= GPIO_HEADER_0)(3)波形@ 2.5Mhz(蓝色

2020-03-26 09:26:51

电平移位I2C总线中继器

2023-03-28 15:01:35

四通道单向电平移位器

2023-03-28 13:05:57

demo的代码里面将AHB 时钟设置到200MHz但是 数据手册 手册里标明 最高只能到166Mhz,这是很么情况到底哪个是对的,电机系统和ADC也是AHB 总线上的 到底哪个时钟参数

2023-06-13 07:13:58

cubemx在系统时钟为400MHz时无法配置ADC同步时钟模式,但是使用200MHz或者480MHz都可以,为什么?我的 cubemx 版本是 6.3.0这是我的 ioc 文件

2022-12-26 08:39:52

配置情况方便地耦合400MHz数据,但是数据率取决于由R4和被驱动电路输入阻抗所构成的时间常数。图1本电路是一种通用的交流信号电平移位器;它符合任何一种接口标准。

2021-05-14 06:43:13

DN20- 六角水平移位缩小了电路板空间

2019-08-09 14:13:03

LTC6362 以接受一个±3.28V 真正双极单端输入信号并将该信号电平移位至 LTC2378-20 之缩减的输入范围。当与 LTC6655-4.096 配对用于基准时,整个信号链路解决方案可由单 5V 电源

2018-10-31 10:20:33

嗨,我一直在文档中搜索如何在virtex-5 FPGA中生成400MHz时钟,但我找不到它。我现在正在使用200MHz,如何使用400MHz时钟?问候。

2019-10-31 09:56:48

我正在使用planahead 14.4在VC707上添加7系列MIG(IP版本1.07a)。当我使用第一个具有200MHz振荡器输入的时钟发生器驱动MIG时,我的设计可以完全路由,我尝试

2020-08-11 10:07:25

我正在使用斯巴达3E入门套件。请帮助我在XILINX的原理图编辑器中生成200MHZ时钟信号。以上来自于谷歌翻译以下为原文I AM USING SPARTAN 3E STARTER KIT.

2019-06-28 08:39:17

HI,我正在使用sp605板,我需要为我的设计生成125 MHz时钟和250 MHz时钟。 板上有一个27MHz晶体和一个200mhz差分时钟。 我已经阅读了ug382文档,但由于我是这个领域的新手,因此无法理解。 老年人请建议我如何生成两个时钟以及如何进一步明确该主题sskhati

2019-08-28 09:04:25

亲爱的朋友们, 我有一个多锁设计。时钟为50MHz,200MHz和400Mhz。如果仅使用400MHz时钟并使用时钟使能产生200Mhz和50Mhz时钟域。现在我需要将信号从一个时钟域传递到另一个

2019-03-11 08:55:24

LTC2949,请协助确认是否可以使用LTC29498MHz 晶体作为外部时钟输入的外部时钟吗 ? 非常感谢

2024-01-04 08:00:14

嗨,我想用Fpga编程AD9914芯片。我需要200MHz的IO速度才能进行写入和读取。1)哪个Fpga在价格和性能方面对我最好?2)Spartan3能否提供200MHz的IO速度?还是spartan6系列?3)是否有一般文档显示所有Xilinx fpga IO速度?

2019-08-01 10:33:28

EVALZ-ADN2915,ADN2915用于ADN2915 6.5至11300 MHz时钟和数据恢复的评估板设置和应用。 ADN2915提供量化,信号电平检测和时钟/数据恢复的接收器功能,可实现

2019-02-21 09:47:49

请教:6713DSP,主频200MHz,emif时钟设为200MHz可以吗?如果不行,有哪些约束?

2019-01-17 10:41:21

LTC6948-2的输入参考时钟的电平标准是什么,谢谢

2018-07-27 08:54:03

LSF010X是否带有自动方向感测?能否转换5MHz到200MHz的信号?看到数据手册中提到支持高速转换,但不知道能高到哪个范围。数据手册中也有在50MHz时,1.8 to 3.3v的转换图,有小幅

2019-05-14 11:17:05

嗨!我想知道在SP605上生成低于3MHz的时钟的正确方法是什么,具有200MHz差分和27MHz单端时钟源。使用单个DCM,我只能获得3.125MHz,而不建议使用两个串联DCM。你可以帮我吗?谢谢。

2019-09-10 09:41:33

已经有一个TTL信号,所以我可以将它降低到适当的电压水平。当我正在寻找电平转换器时,我注意到有电压电平转换器和混合信号电平转换器。电压转换器似乎给了我想要的电压变化,但混合信号移位器给了我我想要的标准

2020-08-11 09:25:10

最近在看《OP放大器应用技巧100例》,里面提到 单电源运放工作中不能完全0V输出时可采用电平移动 ,但是没有提到具体的应用。哪位大佬使用过这种电路或者知道有什么用?

2017-12-07 17:14:38

的控制核心。但利用中低端FPGA还没有可以达到100MHz以上的时钟数据恢复电路。由于上面的原因,许多利用FPGA实现的高速通信系统中必须使用额外的专用时钟数据恢复IC,这样不仅增加了成本,而且裸露

2009-10-24 08:38:08

FStd16450是fairchild公司最新推出的电平移位式总线开关集成电路" 它功能强大Œ使用灵活Œ而且阻抗很低"可以配置成4位5位10位和20位总线开关,且与高速CMOS和TTL电平兼容"文中

2008-09-02 11:28:50 3

3 FSTD16450是Fairchild公司最新推出的电平移位式总线开关集成电路.它功能强大,使用灵活,而且阻抗很低.可以配置成4位位5、位和20位总线开关,且与高速CMOS和TTL电平兼容.文中介绍了它的基

2009-04-30 15:48:18 30

30 精密参考时钟在时钟与数据恢复电路中的应用

2009-05-04 13:36:44 35

35 BSN20系列双向电平移位器在IIC总线和其他系统中的应用

With a single MOS-FET a bi-directional level shifter circuit can

2009-05-12 08:50:06 45

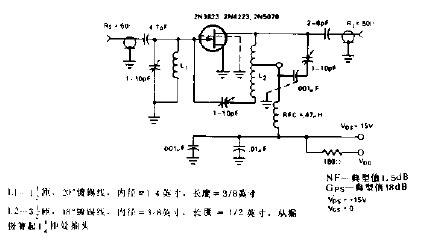

45 介绍采用AD7672和采样保持放大器获得200MHz的采样率:

2009-06-11 14:37:50 30

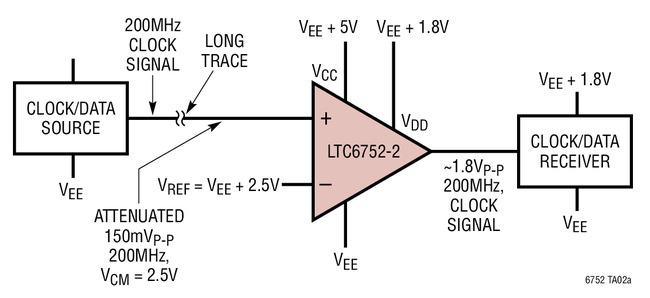

30 LTC®6752 是一个非常高速比较器系列,其能够支持高达 280MHz 的切换速率。这些比较器具有 2.9ns 的低传播延迟和 1.2ns 的快速上升 / 下降时间。LTC6752 系列共有 5

2023-06-30 09:58:35

电平移位电路(采用运放TLC07X)

交流信号可由多种信号源产生,其中不少信号源与诸如TTL等最常用的接口电压不兼容

2007-12-06 13:05:27 8151

8151

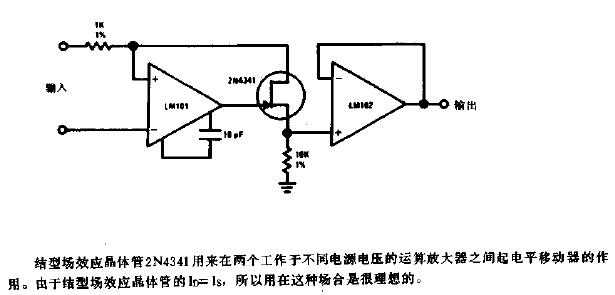

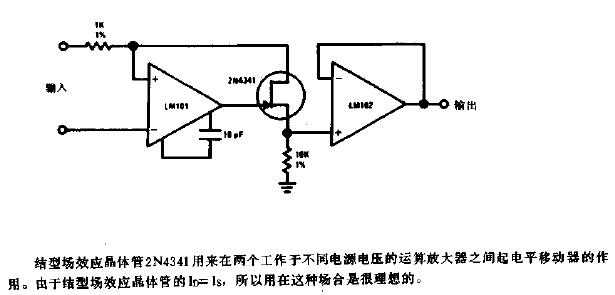

电平移动的隔离放大器电路图

2009-04-01 08:55:46 1263

1263

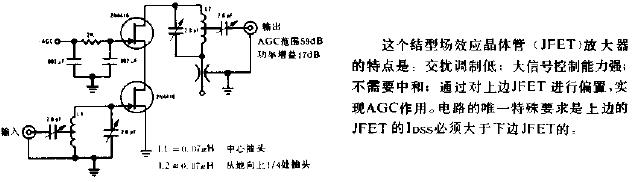

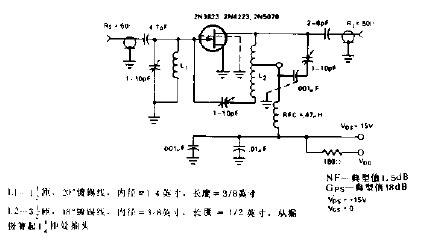

200MHz共源放大器电路图

2009-04-08 09:12:26 1278

1278

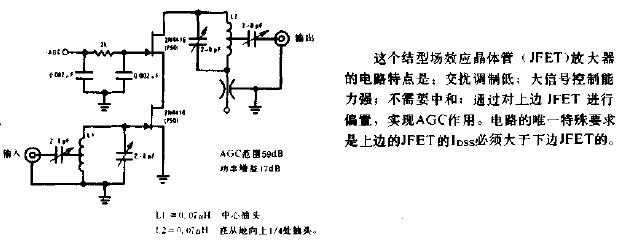

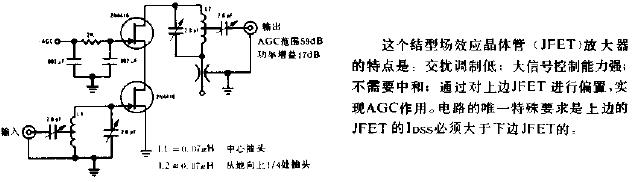

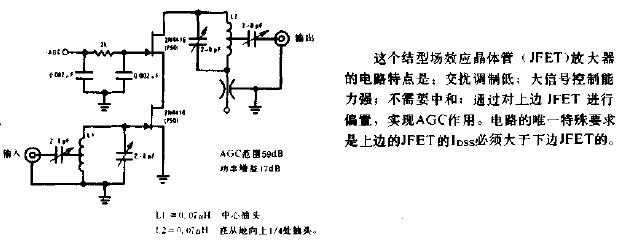

200MHz共源共栅放大器电路图1

2009-04-08 09:12:49 1067

1067

200MHz共源共栅放大器电路图2

2009-04-08 09:13:12 979

979

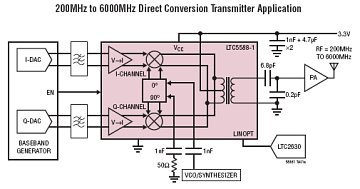

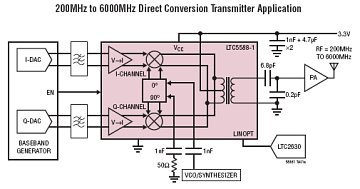

LTC5588-1:200MHz至6GHz直接转换I/Q调制器实现30.9dBm输出三阶截取

Milpitas, California – September 14, 2010

加利福尼亚州

2010-09-22 10:01:50 1071

1071

针对高压驱动电路控制提出了新的具有很大驱动电流和很小静态功耗电平移位栅电压控制电路。该电路主要利用二极管的反向工作特性,结合正反馈电路,分别为输出级PMOS管和NMOS管提

2011-06-13 16:03:20 57

57 LTC6409是一款非常高速度的低失真差分放大器。该器件的输入共模范围包括地电位,因此可对一个参考于地的输入信号实施 DC 耦合、电平移位和转换、以对一个 ADC 进行差分驱动。增益和

2012-09-21 11:21:38 53

53 200MHz实时采样系统的设计与实现,下来看看。

2016-02-19 16:39:58 0

0 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2017-11-16 01:01:29 20783

20783

本例示出了一款单端至差分放大器,该放大器具有至一个 75Ω 信号源的匹配以及从一个 2.5V 输入共模电压至一个 1.25V 输出共模电压的电平移位 (这是从一个 5V 单端电路至一个 3V

2018-06-29 18:38:55 220

220

完整的单端 75Ω 输入阻抗至差分输出、2.5V 输入至 1.25V 差分共模电平移位、以及采用外部电阻器实现单端至差分增益 = 2 的电路实例。

2018-06-29 18:41:30 230

230 (见 LTC1062 的产品手册)。采用 5V 电源来运行的 O1 提供了时钟,利用 Q1 对其进行电平移位以驱动由 ±5V 电源供电的 LTC1062。在该场合中,列出了 3 种常见的陷波频率;其他的陷波频率则可根据所列的等式通过调谐 O1 来选择。

2018-06-29 18:43:30 274

274

LTC6752 可与一个高速、高性能 FET 输入运算放大器 (比如:LTC6268) 一起用于实现一个如上所示的光接收器。该图示出了 LTC6268 的输出驱动 LTC

2018-06-29 19:08:01 599

599 成为目前可用的最快 CMOS 输出比较器。LTC6752 用来驱动 3.3V 直至 1.8V 的逻辑电平,产生仅为 2.9ns 的传播延迟和仅为 1.8ns 的过驱动离散。就 10mVPP、100MHz

2018-08-30 17:03:00 2418

2418 移位运算符在程序设计中,是位操作运算符的一种。移位运算符可以在二进制的基础上对数字进行平移。按照平移的方向和填充数字的规则分为三种:(带符号右移)和>>>(无符号右移)。

2019-11-19 07:04:00 3220

3220

3月27日,河南联通携手华为在郑州开通联通集团首个5G 200MHz LampSite 4T4R数字化室分系统,同时对室内5G 200MHz载波聚合能力做了充分验证。开通5G 200MHz载波聚合

2020-04-07 14:50:46 2739

2739 LTC4308/LTC4309 - 电平移位热插拔缓冲器改善了 I2C 和 SMBus 总线性能

2021-03-21 08:14:17 7

7 LTC6752 Demo Circuit - Pulse Stretcher Circuit/Monostable Multivibrator

2021-03-24 10:46:46 9

9 ADF4001:200MHz Clock发电机PLL数据Sheet

2021-04-14 10:57:44 6

6 LT1468-2:200MHz,30V/PC-16-AV-AV-OP数据Sheet

2021-04-15 10:44:31 8

8 AD8384:带电平移位器的10位、6通道抽取LCD DecDriver®数据表

2021-04-19 18:29:46 2

2 AD8385:带电平移位器的10位、12通道抽取LCD DECDRIVER®数据表

2021-04-20 08:14:48 0

0 LTC4307-1:高清晰度多媒体接口(HDMI)电平移位2线总线缓冲器数据表

2021-04-24 12:50:33 9

9 ADSY8401:带VCOM、NRS缓冲器和高压边沿检测器的LCD电平移位器数据表

2021-04-30 09:55:16 10

10 LTC6752:280 MHz、2.9 ns、带轨对轨输入和CMOS输出的比较器系列数据表

2021-05-16 12:06:45 1

1 AN-224:利用AD7769实现输入/输出电平移位

2021-05-20 16:30:32 4

4 LTC4308:低电压、电平移位热插拔2线总线缓冲器,带卡住总线恢复数据表

2021-05-23 18:45:10 2

2 LTC4309:电平移位低偏移量热插拔2线总线缓冲器,带卡住总线恢复数据表

2021-05-23 19:28:03 1

1 LTC5577:300 MHz至6 GHz高信号电平有源下变频混频器产品手册

2021-05-26 09:23:48 6

6 LTC6752演示电路-脉冲展宽电路-单稳态多谐振荡器

2021-06-01 17:11:25 20

20 LTC6406阻抗匹配电平移位演示电路差动放大器

2021-06-07 12:21:50 3

3 Capstone CS5218AN 是一款单端口 HDMI/DVI 电平移位器/中继器,具有重新定时功能。它支持交流和直流耦合 TMDS 信号高达 3.0-Gbps 的操作与可编程均衡和抖动清洗

2021-06-30 10:04:07 9

9 Capstone CS5218AN是一款单端口HDMI/DVI电平移位器/中继器,具有重新定时功能。它支持交流和直流耦合信号高达3.0-Gbps的操作与可编程均衡和抖动清洗。它包括2路双模DP电缆

2021-07-14 15:54:23 485

485 单端口HDMI/DVI电平移位器CS5218AN

2021-08-10 17:48:01 9

9 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

2022-02-09 10:43:43 6

6 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2022-02-11 15:05:26 8

8 单端口HDMI/DVI电平移位器/中继器CS5218中文数据手册

2022-03-07 17:35:46 7

7 CS5218_DP转HDMI(4k@30Hz)方案

Capstone CS5218AN是一款单端口HDMI/DVI电平移位器/中继器,具有重新定时功能。它支持交流和直流耦合过渡调制差分信号高达3.0-Gbps的操作与可编程均衡和抖动清洗。它包括2路双模DP电缆适配器寄存器

2022-05-23 16:33:18 0

0 级联和异步复位MR输入。MR上的LOW(低)将重置移位寄存器。数据在SHCP输入的低电平到高电平转换时移位。移位寄存器中的数据在STCP输入的低电平到高电平转换时传输到存储寄存器。如果两个时钟连接在一起,移位寄存器将始终比存储寄存器提前一个时钟脉冲。每当输

2023-02-13 16:53:16 0

0 电子发烧友网站提供《具有栅极电压整形和放电功能的9通道电平移位器TPS65192数据表.pdf》资料免费下载

2024-03-07 11:22:04 0

0

电子发烧友App

电子发烧友App

评论