本文主要带领大家来了解一下分频器的计算和调整,首先来了解一下分频器原理及是分频点,其次详细了解分频器计算的顺序以及调整方法。

2018-05-29 09:59:00 137864

137864

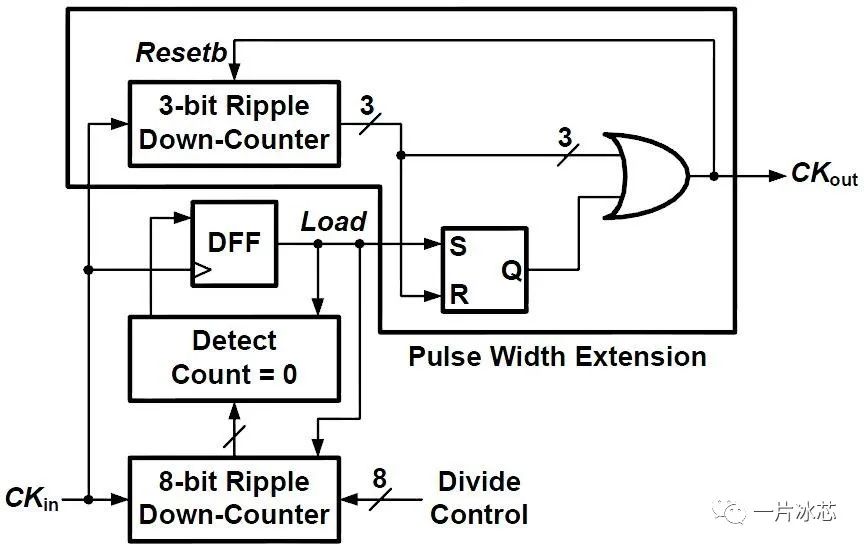

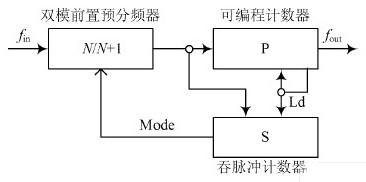

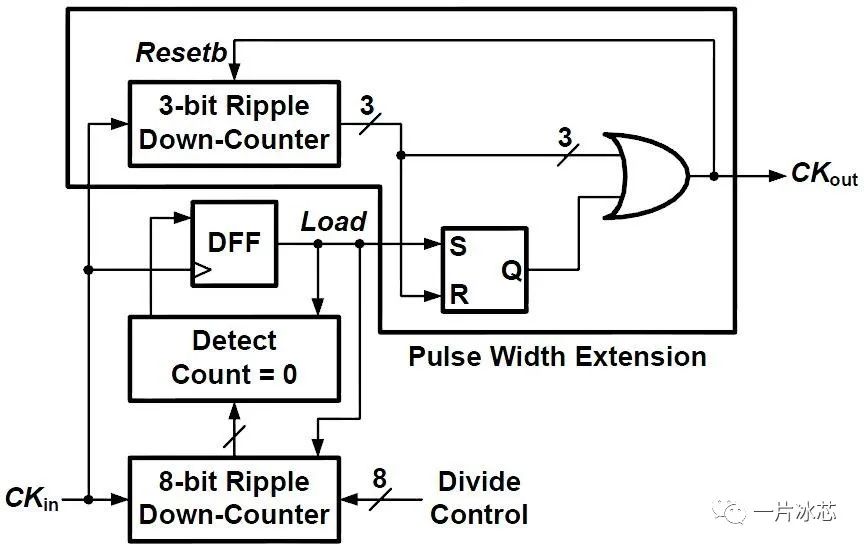

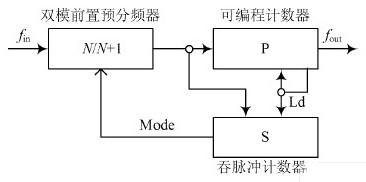

文献给出的分频器结构如图1所示。该分频器最高输入频率(f~in~)为16.3GHz,也就是一个周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

2023-10-31 12:54:56 4227

4227

如题,这样一来,pwm的时钟哪怕是来自HCLK(029不支持PLL作为pwm时钟)最高50MHZ,经预分频器最少2分频的话,时钟最高只有25Mhz了?M0518pwm的预分频器可以设为0,不分频,并且可以用PLL作为时钟,最高频率可以达到100Mhz,相差4倍?

2023-06-19 08:14:45

有没有用使能信号控制的时钟发生器芯片,当使能信号有效是开始产生上升沿,时钟频率要达到100MHz

2014-12-09 20:21:02

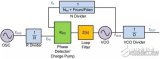

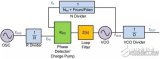

查询了一些资料,知道了分频器是锁相环电路中的基本单元.是锁相环中工作在最高频率的单元电路。传统分频器常用先进的高速工艺技术实现。如双极、GaAs、SiGe工艺等。随着CMOS器件的尺寸越来越小,可用

2021-04-07 06:17:39

分频器模块实现的基本原理就是设计一个工作在系统时钟下的计数器,循环地递减或者递加计数,在某个计数的固定值将输出翻转,即可实现时钟分频的功能。例如,实验板上的系统时钟是 50MHz,而所需的读写周期

2018-11-15 09:25:35

在使用同步从属FIFO写模式时,在100MHz下使用GPIF时,我遇到了一个问题。该方案如下:PCLK为100MHz,SLWR写入16KB到GPIF,并切换FIFO ADDR。但是在SLWR发送

2019-06-12 07:09:36

BiCMOS低噪声可编程分频器,采用3x3 mm无引脚表贴封装。 在400 MHz至6 GHz 输入频率范围内,该电路可编程并采用N = 1至N = 4分频。 该器件具有高电平输出功率(最高为6 dBm单端

2018-10-17 15:46:51

低噪声可编程分频器,采用3x3 mm无引脚表贴封装。 在400 MHz至6 GHz 输入频率范围内,该电路可编程并采用N = 1至N = 4分频。 该器件具有高电平输出功率(为6 dBm单端)、极低

2018-10-17 15:49:04

本帖最后由 weihu_lu 于 2014-6-19 16:25 编辑

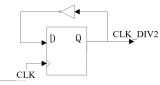

作者:卢威虎1、前言 分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如

2014-06-19 16:15:28

我已经使用 PLL2_PFD2 (396 Mhz) 将 FLEXSPI 设置为 99 Mhz 时钟,所以我期望使用 4 分频器获得 99 MHz 总线时钟,或者分频器为 132 MHz 总线时钟3

2023-03-29 06:19:53

嗨,我会延迟PWM带宽为100MHz,周期为2e-6秒(2微秒)。总延迟时间为1e-6秒。我将使用具有250 MHz或320 MHz时钟的FPGA来构建这样的移位寄存器:PWM输入为“数据输入

2019-02-14 11:29:37

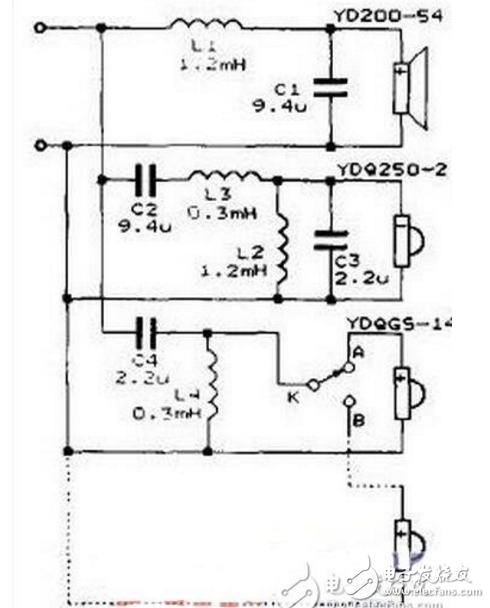

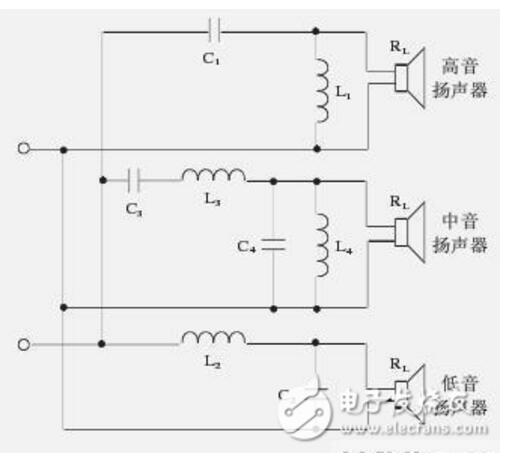

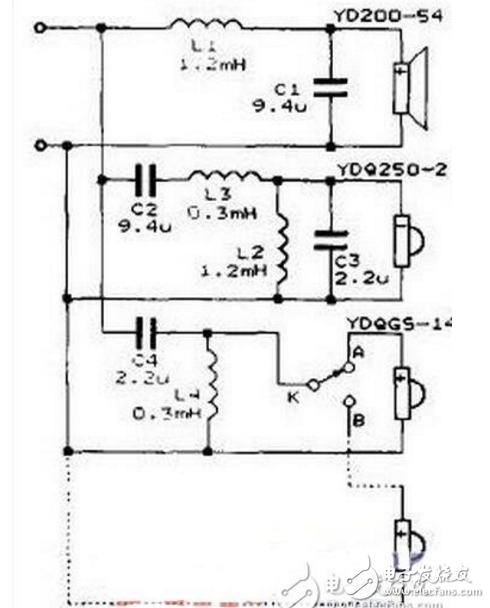

中音喇叭频率范围600-8500Hz,分频器的电容和电感如何计算获得其值?

2022-09-30 14:10:33

)分频器、预分频器与计数器两大类,覆盖的频率范围都包含我需要的2GHz,我想知道,(1)和(2)这两类分频器有什么不同吗?是否是输入信号格式要求不同?第(1)的手册中没有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

想知道哪里有公司可以研制10GHz,100分频的分频器?谢谢!

2018-09-11 10:42:51

定阻型功率分频器的设计与制作(四)-分频器元器件的选取与制作:制作分频器所需的电阻,一律用金属膜电阻为宜,但要根据不同的需要适当选取相应大小的额定功率。2 电容器的

2009-12-02 15:46:59 73

73 定阻型功率分频器的设计与制作(三)-二阶功率分频器

2009-12-02 15:48:19 88

88 分频器设计与制作 (电子书):分频器的基本原理,分频器设计,分频频率和截止带衰减率的选择与使用,元件的选配及要求等内容,电感线圈的设计与制作。

2010-03-29 10:53:02 722

722 2.4GHz频率合成器可编程分频器设计与实现摘要: 介绍了一种应用于802. 11b 的频率合成器中的可编程分频器. 采用级联的异步2 分频电路配合相位开关技术,消除了在

2010-05-11 12:01:28 43

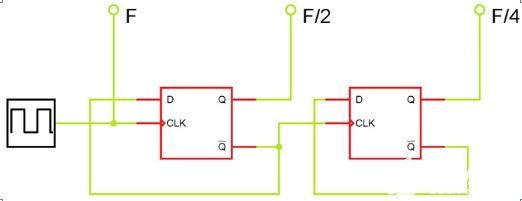

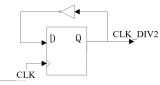

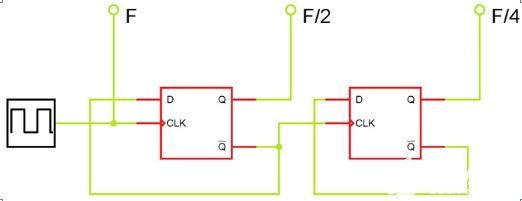

43 给出基于0.13μm CMOS工艺、采用单时钟动态负载锁存器设计的四分频器。该四分频器由两级二分频器级联而成,级间采用缓冲电路实现隔离和电平匹配。后仿真结果表明其最高工作频

2010-12-29 18:00:34 34

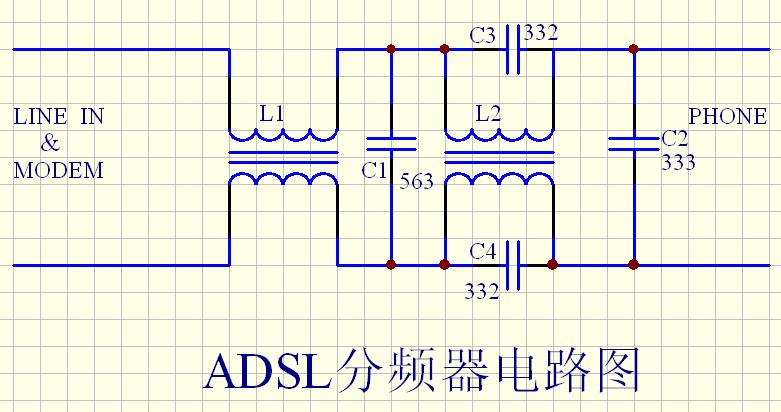

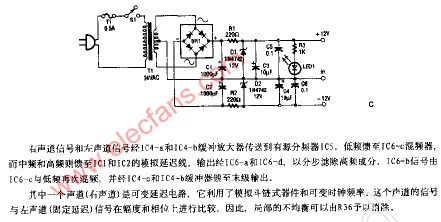

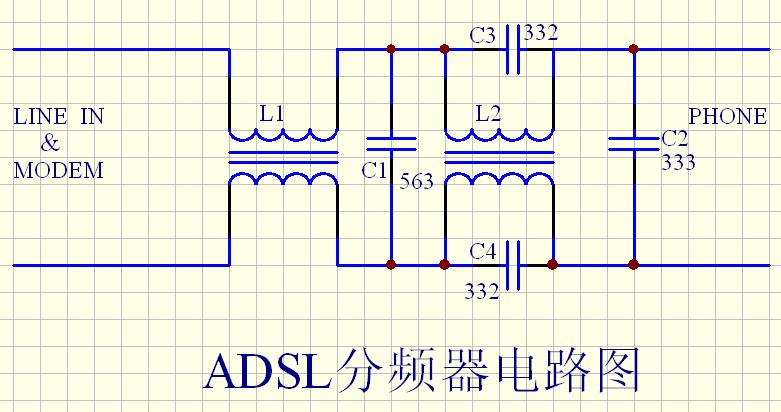

34 ADSL分频器电路图从电路上可以看出,该分频器的作用只是针对电话座机,而非针对MODEM。在一般

2007-09-30 19:53:24 2567

2567

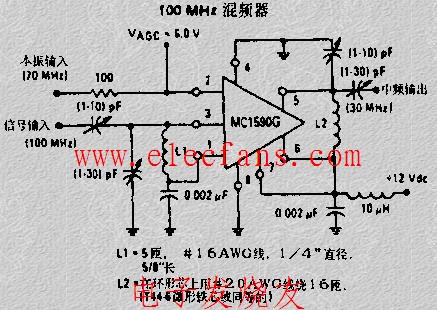

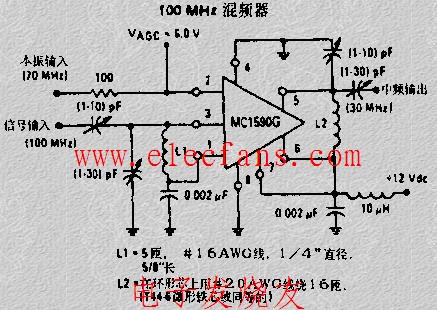

100MHZ混频器电路

2008-06-12 23:15:39 2540

2540

100MHz混频器电路图

2009-04-03 08:49:36 1701

1701

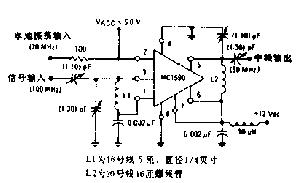

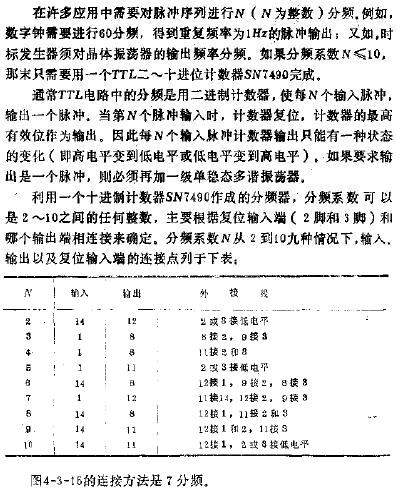

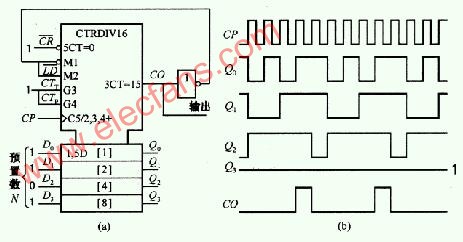

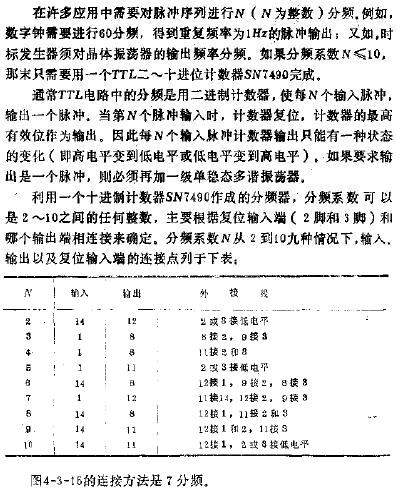

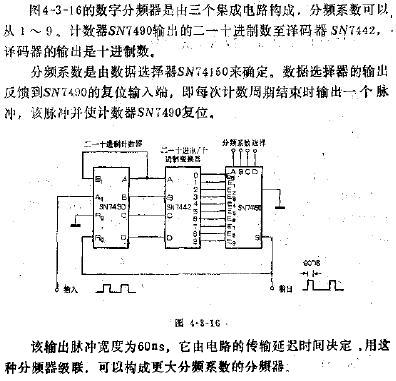

TTL十进位计数器构成的分频器

2009-04-11 10:14:57 1426

1426

分频系数可变的分频器

2009-04-11 10:18:26 1553

1553

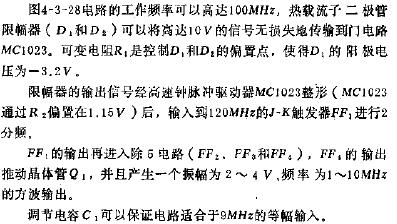

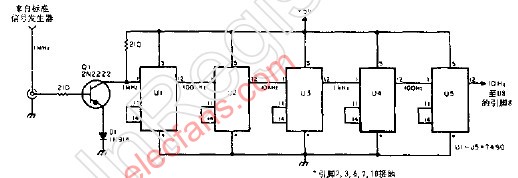

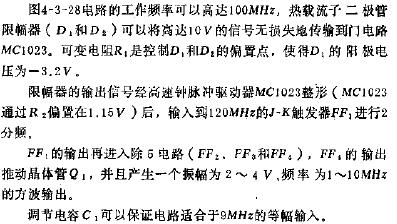

工作频率为10MHz~100MHz的分频器

2009-04-11 10:19:16 2731

2731

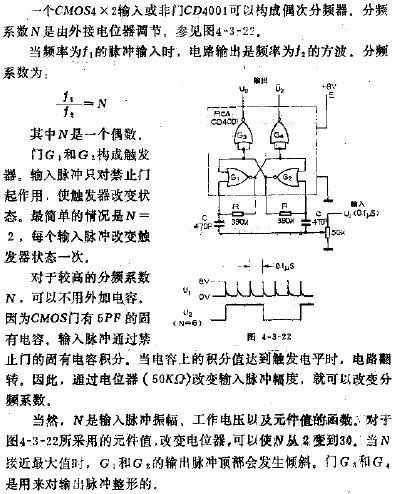

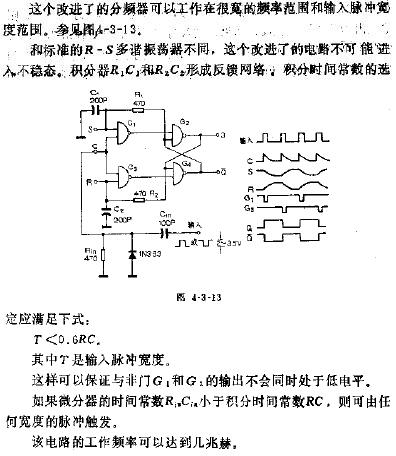

具有奇次和偶次分频的分频器

2009-04-11 10:22:12 1141

1141

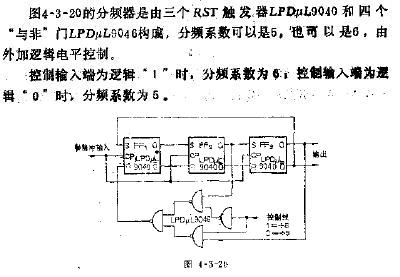

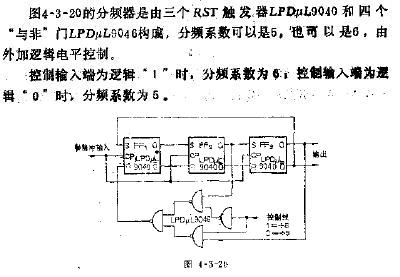

可由逻辑电平控制分频系数的分频器

2009-04-11 10:23:09 1463

1463

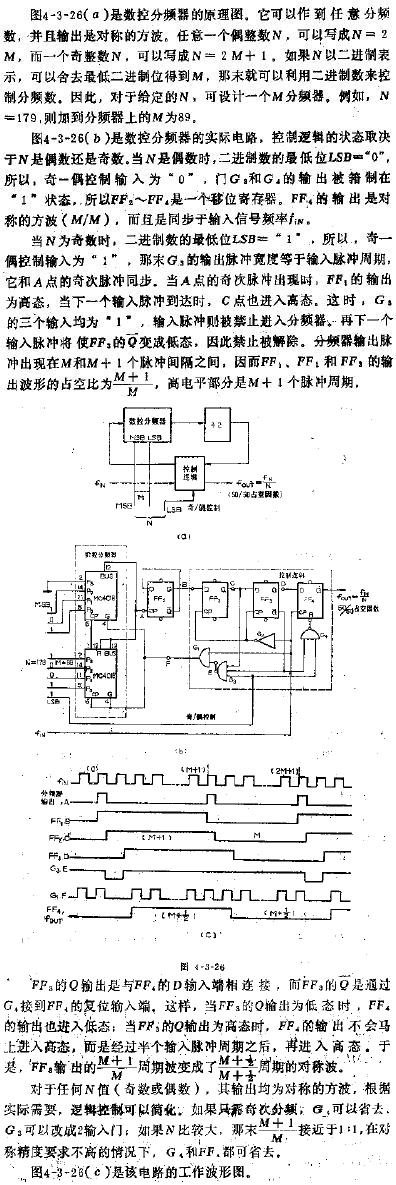

数控分频器

2009-04-11 10:25:27 1507

1507

数字分频器

2009-04-11 10:26:21 3464

3464

由CMOS门构成的可调分频器

2009-04-11 10:28:20 1228

1228

由R-S触发器构成的分频器

2009-04-11 10:28:43 1364

1364

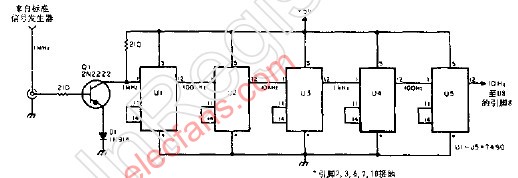

供测量用的分频器

笨电路可由幅度为几伏的1MHz标准

2009-09-25 11:51:44 1222

1222

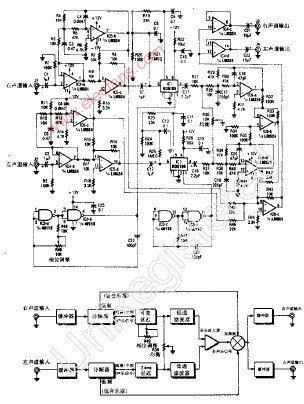

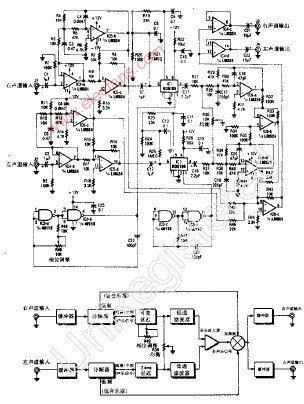

声乐分频器

2009-10-07 11:54:17 928

928

声乐分频器(续)

2009-10-07 11:55:27 664

664

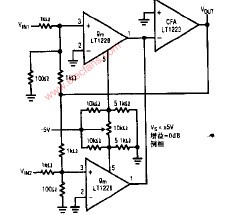

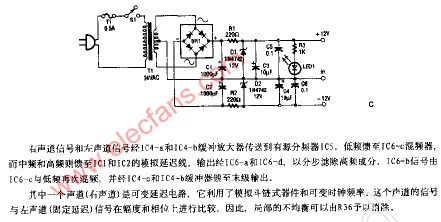

视频分频器

在电流反馈

2009-10-10 15:37:17 1291

1291

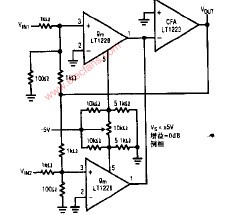

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1599

1599

可编程分频器电路

可编程分频器:计数器可以对计数脉冲分频,改变计数器的模便可以改变分频比。根据这个原理,可以用集成计数

2010-01-12 13:58:07 3927

3927

什么是分频器 分频器介绍

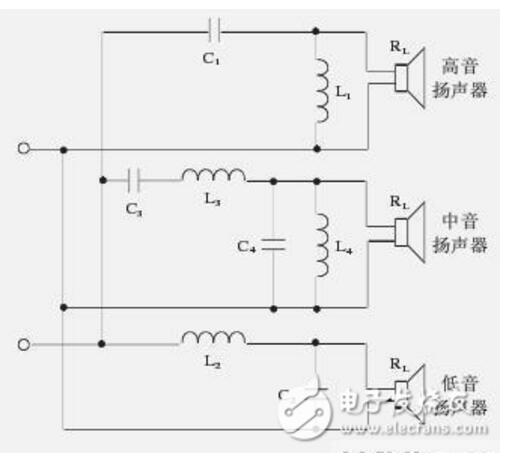

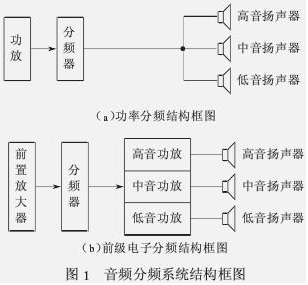

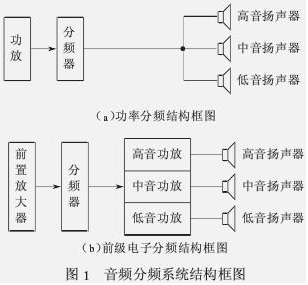

分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放

2010-02-05 17:51:10 5001

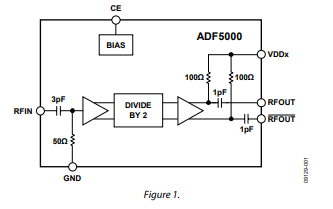

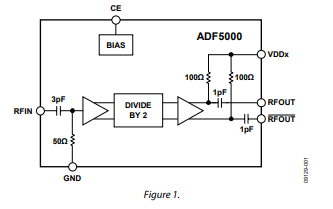

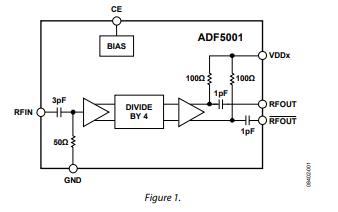

5001 ADI 公司推出低功耗射频预分频器-- ADF500x 射频预分频器电路工作频率可达 18GHz,功耗非常低,可与业界领先的 ADI PLL 合成器配套使用

&nbs

2010-05-11 16:27:21 764

764 分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍

2011-08-17 16:50:45 2408

2408

介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 分频器是一种产生的振荡频率为其输入频率整约数的非线性器件。 是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放。在高质量声音重放时

2012-09-06 16:47:27 16667

16667 △∑小数频率合成器中的小数分频器设计设计方案、技术指标、调试等。

2016-05-24 10:03:05 9

9 音响分频器原理,感兴趣的可以看看。

2016-09-27 15:19:03 15

15 分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频。实现分频的电路或装置称为“分频器”。这里的分频上针对单频信号而言的。如把33MHZ的信号2分频得到16.5MHZ的信号,3分频得到11MHZ的信号,10分频得到3.3MHZ的信号。

2017-11-15 10:41:47 75736

75736

。模拟分频器可由注进锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用

2017-11-17 15:54:22 8

8 分频器一般常用于拥有高音和低音的单元,或者带有中音单元的音箱中,若缺少分频器这种拥有多单元的音箱就不能将不同频段的声音进行回放。而且分频器的种类以及质量的差异,也同时影响到音箱能否回放出更好的声音表现。

2017-11-24 14:16:18 18707

18707 分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

2018-01-10 15:36:20 15986

15986 本文为大家带来电子分频器的各功能旋钮、调节方法及注意事项。

2018-01-10 15:47:58 25954

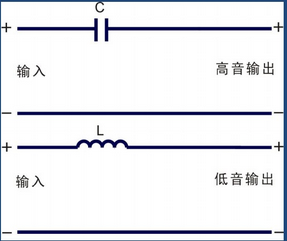

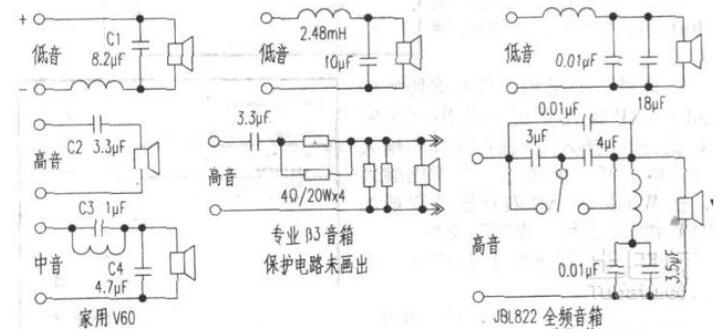

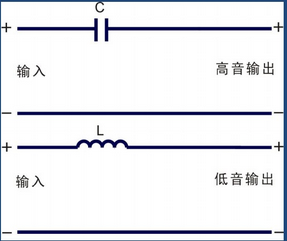

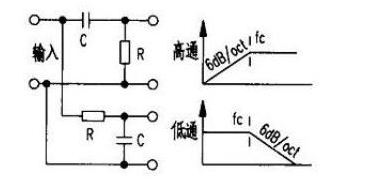

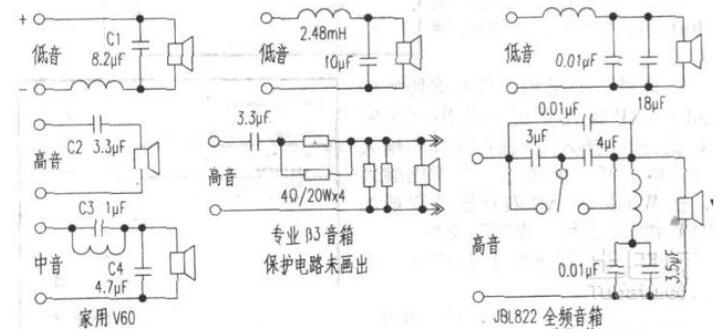

25954 音箱分频器可以将声音信号分成若干个频段。如二分频器就是由一个高通滤波器和一个低通滤波器组成。三分频则又增加了一个带通滤波器。分频器是音箱中的“大脑”,对音质的好坏至关重要。可以看出,分频器充分利用的电容器和线圈的特性达到分频。

2018-02-06 10:54:03 17853

17853 音箱分频器可以将声音信号分成若干个频段。如二分频器就是由一个高通滤波器和一个低通滤波器组成。三分频则又增加了一个带通滤波器。分频器是音箱中的“大脑”,对音质的好坏至关重要。

2018-03-01 16:25:54 49465

49465 本文主要介绍了电子分频器电路图大全(六款电子分频器电路设计原理图详解)。从工作原理看,分频器就是一个由电容器和电感线圈构成的滤波网。高音通道只让高频信号经过而阻止低频信号;低音通道正好相反,只让低音

2018-03-02 09:41:17 147084

147084

本文首先介绍了音箱分频器概念,其次介绍了音箱分频器结构与作用,最后介绍了_音箱分频器制作方法与图解。

2018-04-13 08:50:18 196012

196012 本文开始介绍了音箱分频器原理,其次介绍了音箱分频器分类与特点以及音箱分频器电路及作用,最后介绍了音箱分频器接线方法图解。

2018-04-13 09:32:27 121473

121473 现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围,如图1所示。比如ADI的HMC832,其VCO的频率为1500~3000MHz,利用其后的分频器(1/2/4/6/…60/62),最终获得25MHz~3000MHz的频率覆盖范围。

2018-05-25 09:54:00 8705

8705

本文首先介绍了为什么要使用电子分频器,其次阐述了电子分频器工作原理及作用、特点,最后介绍了电子分频器的调整方法、使用注意事项及发展趋势。

2018-05-24 14:46:53 28408

28408 本文首先介绍了什么是分频器,其次阐述了音箱箱体及音箱分频器结构和原理,最后介绍了音箱分频器特点和作用。

2018-05-25 17:47:16 15575

15575

本文主要介绍的是汽车音响的分频器,首先介绍了汽车音响的分频器的种类,其次介绍了分频器的作用及分频点的选择,最后分析了汽车音响分频器安装位置,具体的跟随小编一起来了解一下。

2018-05-28 11:54:38 14359

14359 本文首先介绍了分频器的分类及电子分频器的工作原理,其次介绍了主动分频器的优缺点,最后介绍了被动分频器的优缺点,具体的跟随小编一起来了解一下。

2018-05-28 14:52:31 53340

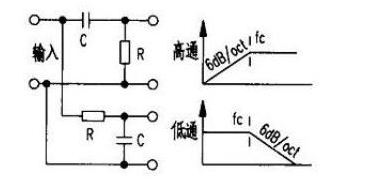

53340 电子分频器根据是否采用放大器件分为无源型与有源型。其中无源型由阻容件构成,其结构简单并且无其他附加失真,从综合指标来看是音响电子分频器中的佼佼者。

2018-08-10 15:45:37 10908

10908

采用有源分频器可以降低对功放带宽的要求;省去了大功率的LC元件;分频点也易于调整,且可以获得比功率分频更佳的效果。这里介绍两种有源二分频器电路。如图9-4所示为有源二分频器组成的功放电路

2018-08-10 16:19:37 25920

25920

汽车使用的叫分频器 家庭以及其它场合用的叫分音器,其实质基本相同——功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过

2018-08-13 08:33:37 9552

9552 高速、宽分频范围的可编程频率分频器设计一直是射频频率综合器设计中的难点,它的工作速度限制了频率合成器输出信号的最高频率,它的相位噪声影响频率合成器的带内相位噪声。文中设计的可编程分频器应用于移动

2019-06-06 08:05:00 7190

7190

关键词:SP6168 , 分频器 如图所示为1GHz前置分频电路。该分频器由 15V单电源供电,其灵敏度为30mVrms,具有40dB的动态范围,工作频率为100~1000MHz。图中,输入信号

2018-10-03 18:16:01 620

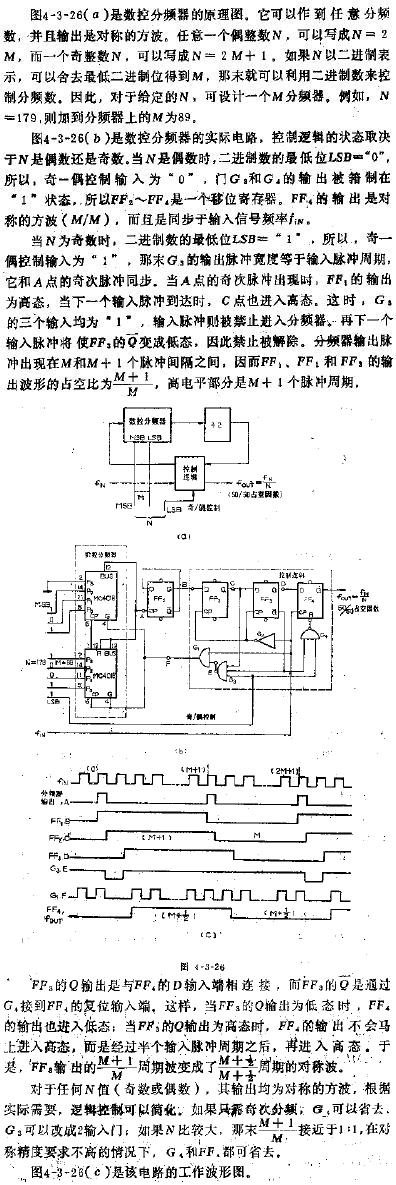

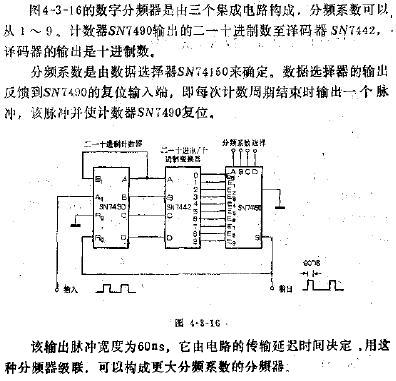

620 关键词:MC4018 , 分频器 如图所示为数控分频电路。 图(a)为数控分频器原理图。它可以做到任意分频系数且输出为对称方波。对于任意一个偶数N,可以写成N=2M,而对于任意一个奇数N,则可写成N

2018-10-03 18:23:01 948

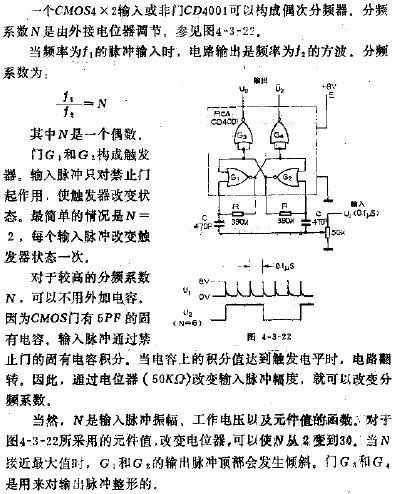

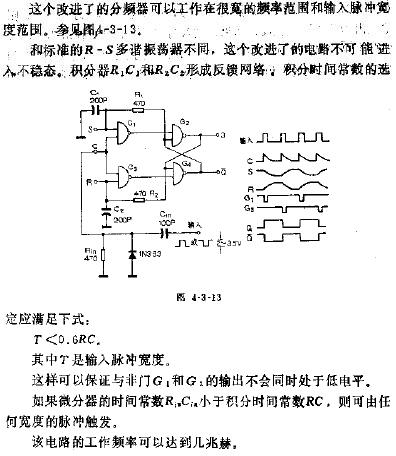

948 关键词:CD4001 , CMOS , 分频器 如图所示为由CMOS门构成的可调分频电路。该电路是一个由CMOS 4×2输入或非门CD4001构成的偶次分频器,分频系数由外接电位器进行调节。当频率为

2018-10-03 18:28:02 2988

2988 ,S8424是两组RS T触发器.S8480是4×2输入与非门。二-八进制拨盘开关用来确定分频器的分频系数,以保证触发器复位。如果采用二-十进制拨盘开关,另外再加一个触发器和两个二极管。则可构成分频系数为1~10的分频器。

2018-10-03 18:37:02 818

818 关键词:TTL , 分频器 , 计数器 , 十进制 如图所示为由TTL十进制计数器构成的分频电路。在许多情况下。需要对脉冲序列进行N(N为整数)分频。例如,数字钟需要进行60分频,得到重复频率为

2018-10-03 18:46:02 4068

4068 缺点:当分频倍数很大时,需要的寄存器也是倍增。当然你也可以采用复用的方式去减少所需寄存器数目,例如,36分频,可以做两个6分频器相连,则所需寄存器为6个,需要的寄存器数大大减少。

2018-12-08 10:40:57 10750

10750

根据高音喇叭的频率范围和低音喇叭的频率范围来选择的,高低音喇叭单元组合时,为了使他们工作时各负其责;高音单元只发高音部分,低音单元只发低音部分,所以要加一个分频器、选择好分频点,使他们的交叉频率变得比较平坦,这样声音在重放时就变得更加完美,动听。

2019-01-04 16:22:03 118156

118156 音箱分频器可以将声音信号分成若干个频段。如二分频器就是由一个高通滤波器和一个低通滤波器组成。三分频则又增加了一个带通滤波器。分频器是音箱中的“大脑”,对音质的好坏至关重要。

2019-10-08 10:11:32 9989

9989 优点是在于多路扬声器中,每一只都可视为独立的部分。如果采用了串联式的分频器,任一个零件都可能会影响到高通与低通的特性。汽车音响里所应用的都是并联式分频器。

2019-10-09 09:12:56 5894

5894

频带优势,以保证不同工作频段的扬声器充分发挥,使各频率的放音特性更加均衡。所以不难看出设计优良的分频器能够更好的发挥出单元的特性,来使得声音发挥出更好的素质。

2019-12-02 08:47:27 22061

22061 在实际的分频器中,有时为了平衡高、低音单元之间的灵敏度差异,还要加入衰减电阻;另外,有些分频器中还加入了由电阻、电容构成的阻抗补偿网络,其目的是使音箱的阻抗曲线心理平坦一些,以便于功放驱动。

2020-03-28 11:04:33 35893

35893 本文主要阐述看音箱分频器的维修方法及音箱分频器接喇叭的方法。

2020-03-28 11:09:59 19022

19022

现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围,如图1所示。比如ADI的HMC832,其VCO的频率为1500~3000MHz,利用其后的分频器(1/2/4/6/…60/62),最终获得25MHz~3000MHz的频率覆盖范围。

2020-10-30 10:40:00 3

3 分频器又称为分频网络。分频器的主要作用就是在音频系统中把全频带音频信号分为不同的频段后送到对应的工作频率的扬声器,使它们得到合适频带的激励信号,再进行重放。例如,在二分频的音箱中,通过高通滤波器分类出较高的频率供给高音扬声器,通过低通滤波器分离出较低的频率供给低音扬声器。

2022-04-12 15:24:50 8702

8702 电子发烧友网站提供《带预分频器的Arduino射频频率计数器.zip》资料免费下载

2022-07-06 09:26:04 1

1 分频电路是一种重要的电路,在许多电子设备中,例如音响设备、频率合成器等,需要各种不同频率的信号进行协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到各种频率信号,其中,分频器是一种主要变换手段。

2022-10-31 16:14:41 9629

9629

15 级分频器和振荡器-74AHC1G4215_Q100

2023-02-14 19:05:50 0

0 14 级分频器和振荡器-74AHC1G4214_Q100

2023-02-14 19:06:17 3

3 12 级分频器和振荡器-74AHC1G4212_Q100

2023-02-14 19:06:49 0

0 10 级分频器和振荡器-74AHC1G4210_Q100

2023-02-14 19:10:14 1

1 10 级分频器和振荡器-74AHC1G4210

2023-02-14 19:10:25 0

0 8 级分频器和振荡器-74AHC1G4208_Q100

2023-02-14 19:10:53 0

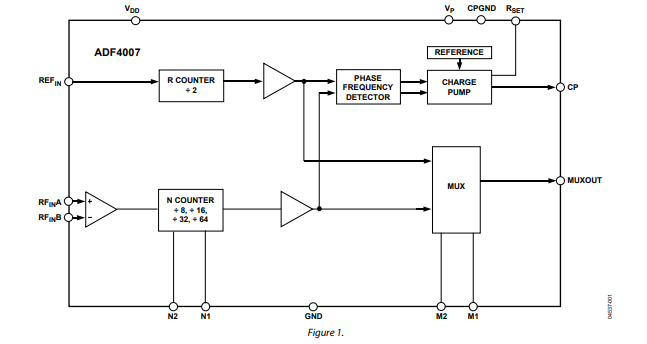

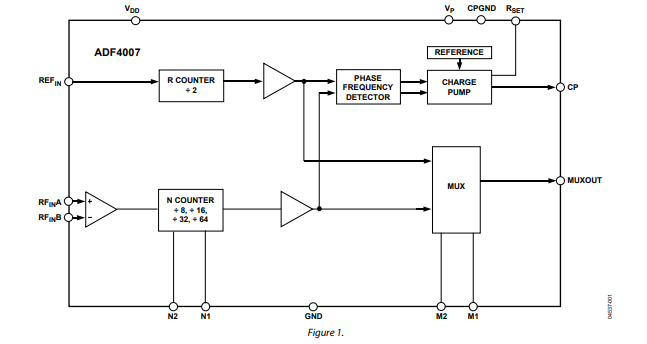

0 ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和分频器

2023-02-24 17:39:54 1921

1921 所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 3014

3014

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 3266

3266

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

2024-02-01 11:19:51 6197

6197 ADF5000预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18 GHz的频率分频至适合输入到[ADF4156]等PLL IC的较低频率。ADF5000提供2分频功能,采用3.3 V

2025-04-16 15:16:57 1026

1026

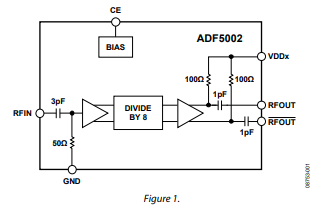

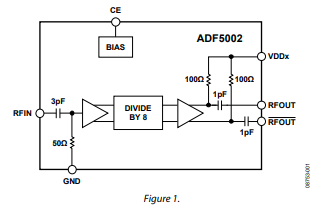

ADF5002预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到 [ADF4156]或[ADF4106]等PLL IC的较低频率。ADF5002提供8分频

2025-04-16 15:46:49 939

939

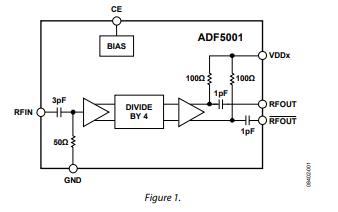

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块 ,可用来将高达18GHz的频率分频至适合输入到[ADF4156]或 [ADF4106]等PLL IC的较低频率。ADF5001提供4

2025-04-16 15:50:29 859

859

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和分频器

2025-04-27 15:23:56 883

883

电子发烧友App

电子发烧友App

评论