前言: 偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去

2020-12-28 15:49:20 2620

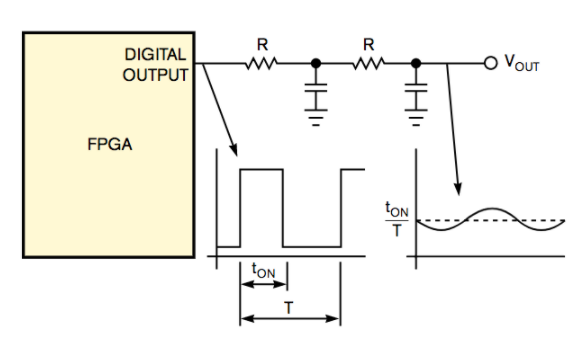

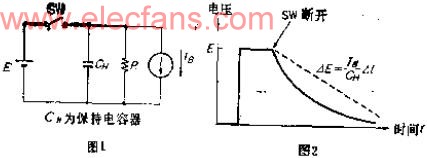

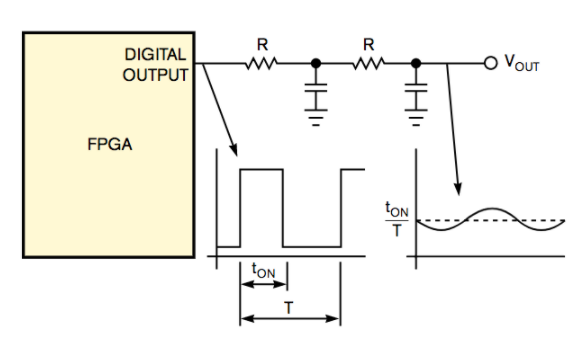

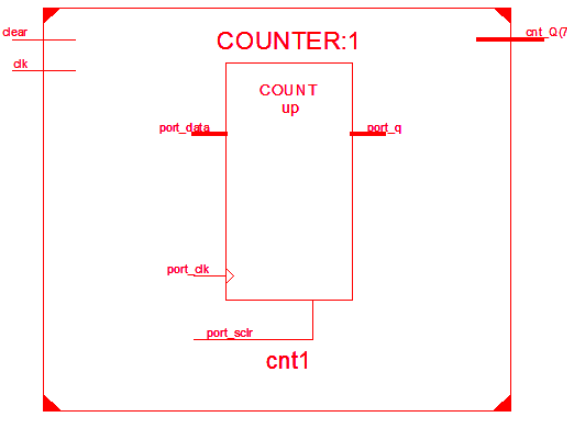

2620 当您需要一些模拟输出并且您的系统中有FPGA时,您可能选择使用PWM模块和简单的低通滤波器,如图1所示 。FPGA的输出通常是具有固定频率,可变占空比的波形,由计数器和数字比较器生成(清单

2021-05-13 16:22:44 4592

4592

假设时钟分频是N,则设置一个计数器,计数长度是N(即从0计数到N-1),然后在计数器为计数到(N-1)/2的时候,翻转一下分频时钟信号。

2020-11-06 13:59:47 9658

9658

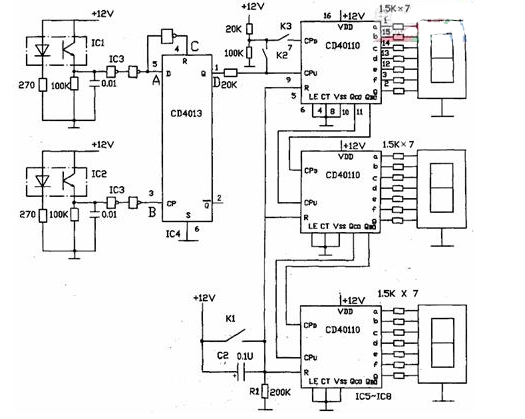

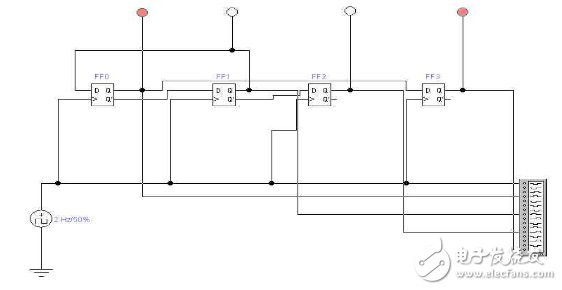

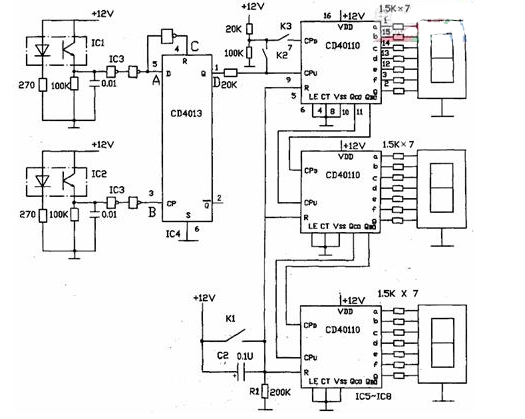

1.1 方波产生电路 555定时器构成多谐振荡电路。电路幅值与占空比可调,产生的方波为单极性,波形上升沿较陡 1.2 分频电路 由十六进制计数器74LS163和触发器HEF4013构成分频电路

2020-11-18 10:41:01 9065

9065

偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给

2013-05-01 08:44:05

奇N分频代码分享

2016-06-30 22:25:38

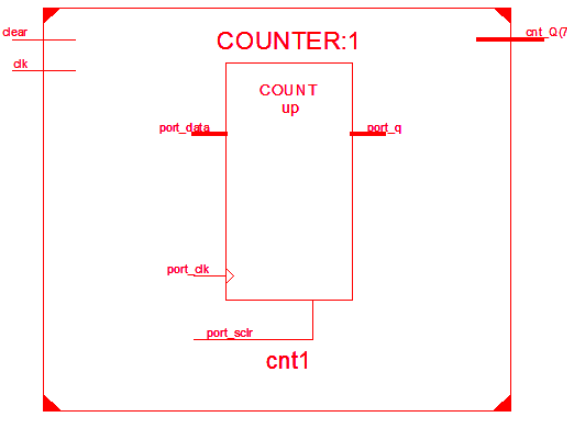

使用计数器计数不成功,有个老师指导说“每次是能计数器, 计数器值会清零 "就说了这几句,奈何我太菜了 无法理解怎么弄。有大神指导下如何实现计数操作

2020-05-31 22:35:28

计数器是什么?如何使用计数器?计数器有哪些应用呢?

2022-02-28 11:08:08

; 2、掌握中规模集成计数器的使用及功能测试方法 3、运用集成计数计构成1/N分频器二、 实验原理计数器是一个用以实现计数

2009-10-11 10:00:11

DAQ通道属性,只有计数器输出,没有计数器输出,不知道原因出在哪里

2022-08-13 22:10:32

,分享给大家吧。——高手应该是这样做时钟信号的。禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式。否则这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性。时钟

2018-08-08 11:13:26

#(25_000_000, 25) clk_div_inst(// 分频实例, 25M 分频,25的计数器位宽.clk_in (clk_in) , .out_pulse (led_clk

2019-03-13 04:25:51

模块用来对外来的计数时钟进行分频,这里有个分频计数器,通过它来实现对时钟的分频功能。与之对应的有个分频器寄存器TIMx_PSC,用来配置和存放分频比、分频系数。计数模块用来对来自分频器输出的计数脉冲

2020-05-27 08:00:00

原语只用用全局时钟处理,不能作为接口使用。也不知道有什么办法可以解决??(2)在用计数器分频后的信号做为下级的时钟信号时间好像也会有警告 生成了 门控时钟,这个问题好像在与计数器分频后的信号不能在做分支同时给于下面几级做时钟信号,这样可能会在级点上产生逻辑门电路吧。

2015-06-16 19:34:01

观察输出波形并加以记录。电路有用到:74ls90 pdf .三分频电路d触发器构成2分频电路用多级2进计数器的分频电路脉冲分频电路双稳态分频电路图任意分频电路图1/60分频电路用VHDL语言实现3分频电路SN7474N构成简单的分频电路[此贴子已经被作者于2009-6-22 8:04:20编辑过]

2009-06-22 08:02:10

参考计数器第一次溢出。当这种情况发生时,输入信号的下一个下降沿停止两个计数器。然后,可以使用参考值和输入计数器的计数值来计算输入频率。为了开始测量CycLy,使用一个控制寄存器,它重置DFFS并重新加载

2018-11-02 14:47:59

最近在看《现代操作系统》,他提到了时钟维持实际时间,在每个时钟滴答将计数器加1即可实现。但要注意位溢出(32位计数器),可以通过以下方法解决:使用64位计数器:缺点是这种方法使得计数器加一操作的代价很高,1s内维护很多次计数器。我不太懂红色字体的意思

2018-05-04 11:36:41

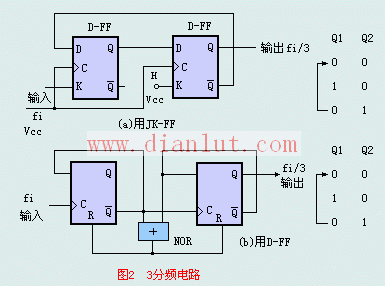

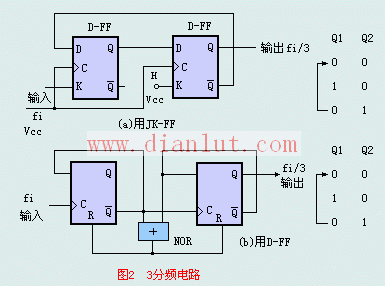

上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。即是在计数值在邻近的1和2进行了两次翻转。这样实现的三分频占空比为1

2019-06-14 06:30:00

CLK,经过分频器后输出标准秒脉冲CLK1,作为计数器的计数时钟。计数器按照“00-01-02…22-23-00-01”的规律计数,每增加1秒,计数器加1,信号Result[7:4]代表计数器输出结果

2022-07-05 15:14:27

的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。以此循环,就可以实现偶数倍分频。以10分频为例,相应的verilog

2014-06-19 16:15:28

–是一个定时器,供能–计数。每隔一段时间就喂狗–计数清零,重新计时,程序出错不能喂狗,得复位。独立看门狗独立看门狗是基于一个12位的递减计数器和一个8位的预分频器。他有一个内部独立的40KHz的RC

2021-07-30 07:24:12

我想知道我们如何使用代码而不是 UI 更改 STM32 中定时器的预分频器和计数器周期的值。请帮忙。

2023-02-02 08:17:12

上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。即是在计数值在邻近的1和2进行了两次翻转。这样实现的三分频占空比为1

2019-07-09 09:11:47

定时 / 计数器的功能计数:记录脉冲的个数,从而可以测量位移、速度、流量等物理量。计时:通过已知频率的脉冲进行计数,可以实现精确计时。产生PWM波:产生不同占空比的PWM波,实现数 / 模转换,从而

2021-10-27 07:36:03

的干预情况下根据触发条件捕捉定时器计数值或自动产生输出波形。定时/计数器部分:输入的时钟源具有4种选择,所选定的时中源又可以1、2、4或8分频作为计数频率,Timer_A可从通过选择4种工作模式灵活的完成定时/计数功能捕获/比较器:用于捕获事件发生的时间或产生时间间隔,获比较功能的引入主要是为

2022-02-15 06:30:58

描述带预分频器的 Arduino 射频频率计数器SAB6456 预分频器用于除以 64/256,上限为 1 GHz。固件可在:https ://github.com/imsaiguy/Frequency-Counter-Board

2022-07-04 07:02:14

时序逻辑电路设计之计数器实验目的:以计数器为例学会简单的时序逻辑电路设计实验平台:芯航线FPGA核心板实验原理: 时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成

2019-01-24 06:35:16

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-12-08 08:32:28

)分频器、预分频器与计数器两大类,覆盖的频率范围都包含我需要的2GHz,我想知道,(1)和(2)这两类分频器有什么不同吗?是否是输入信号格式要求不同?第(1)的手册中没有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

) 输出比较单元A(OCR1A) 的一个特质是定义T/C 的TOP 值( 即计数器的分辨率)。 TOP 值还用来定义通过波形发生器产生的波形的周期。 由于在任意模式下写TCNT1 都将在下一个定时器

2018-06-26 01:35:21

谁能说说计数器和分频器有什么异同呢?

2013-06-20 16:55:20

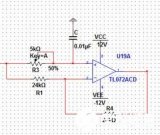

最近在学习DAQ方面内容,尝试写了一个通过计数器I/O产生PWM波形的程序。上次做的好像有点问题,这次做了点修改,并附上程序,望大神帮忙看下。

2017-08-19 14:10:08

④ 构成脉冲分频器集成十进制计数器【74LS290】集成十进制计数器【74LS390】1. 集成四位二进制计数器【74LVC161】(1) 逻辑符号CR:CR:CR: 异步置0端。优先级最高。PE:PE:PE:并行置数端。次高优先级。TC:TC:TC:进位信号。CEP,CET:CEP

2021-07-29 07:20:09

面试官问道针对一个大数分频器(比如1千分频1万分频)的计数器,有什么好方法可以节省一点资源? 当时想了很久,就说按实际分频用到多少位就分配几位,避免一些无用寄存器的使用。然后他摇了摇头,我向他请教

2016-08-16 16:39:47

32位的计数器。内部计数器对触点信号的计数,是在触点每通断一次时,其当前值就+1或-1(32位双向计数器)如下图16-1所示,触点X0每通断一次,内部计数器C0的当前值就+1,如图中的“4”。所以

2022-02-16 07:47:32

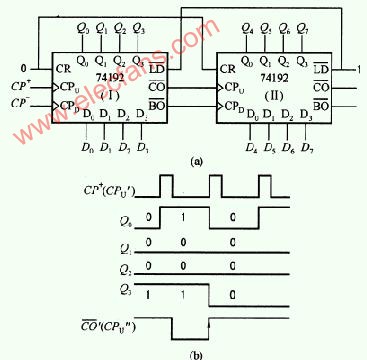

计数器的级连使用

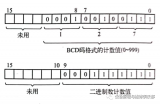

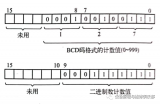

一个十进制计数器只能显示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级连使用。

2007-11-22 12:53:25 3379

3379

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的

2008-06-30 00:00:41 15785

15785

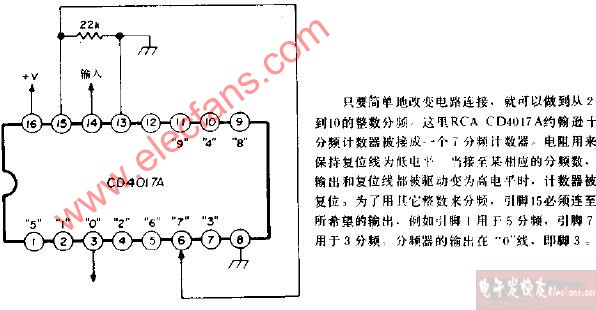

CMOS可编程N分频计数器电路图

2009-03-29 09:55:36 808

808

有对称输出的计数器

2009-04-10 10:28:41 590

590

TTL十进位计数器构成的分频器

2009-04-11 10:14:57 1163

1163

输出波形对称的奇次分频计数器

2009-04-11 10:24:22 654

654

用CMOS集成电路构成的数控分频计数器

2009-04-11 10:27:52 697

697

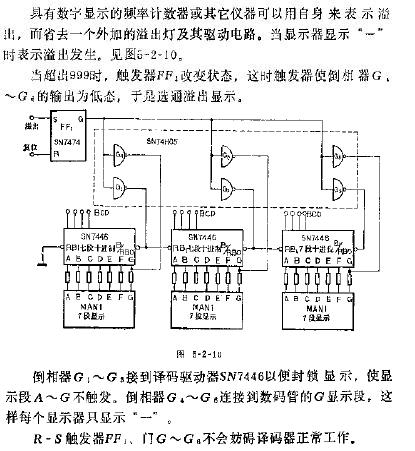

利用计数器的输出显示溢出状态

2009-04-11 10:42:23 1320

1320

用多级2进计数器的分频电路

2009-06-12 14:30:26 1193

1193

图3是可逆、可预置计数器CD4029构成的任意N分频减法计数电路,U/D接“L”电平进行减法计数,B/D接“L”电平按BCD输出码进行计数,低位的Co进位到高位的CT输

2009-06-22 07:44:38 4899

4899

计数器

计数器的作用与分类

计数器(Counter)用于计算输入脉冲个数,还常用于分频、定时等。

2009-09-30 18:30:15 1414

1414

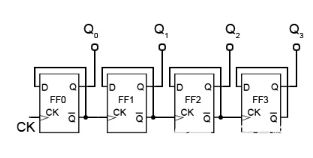

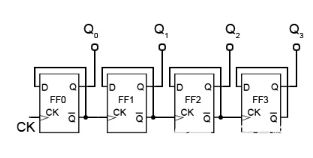

同步二进制计数器

1. 同步与异步二进制加法计数器比较态序表和工作波形一样电路结构不同: 异步二进制加法

2009-09-30 18:37:29 11186

11186

计数器级联及波形图

2010-01-12 13:56:56 4299

4299

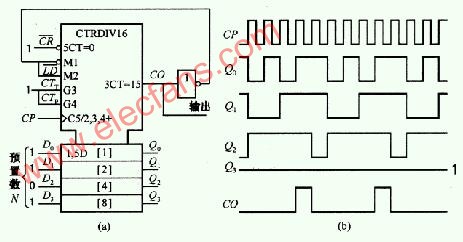

可编程分频器电路

可编程分频器:计数器可以对计数脉冲分频,改变计数器的模便可以改变分频比。根据这个原理,可以用集成计数

2010-01-12 13:58:07 3187

3187

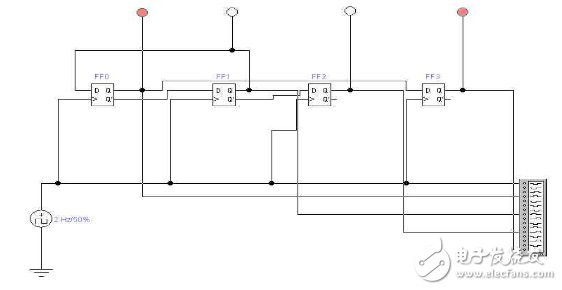

环形计数器和扭环形计数器

移位寄存器也可以构成计数器,称为移位型计数器。它有两种结构:环形计数器和扭环形计数器。

2010-01-12 14:07:46 9173

9173 计数器,计数器的工作原理是什么?

在数字系统中使用最多的时序电路是计数器。计数器不仅能用于对时钟脉冲进行计数还可以用于分频、定时,产生

2010-03-08 13:50:14 59934

59934 正负不对称波形的双极性峰值输出电路

电路的功能

这是一种输入为

2010-05-05 14:52:06 2185

2185

一、定时/计数器PWM设计要点 根据 PWM 是利用微处理器的数字输出来对模拟电路进行控制的特点,在使用ATmega128的定时/计数器设计输出PWM时应注意以下几点: 1.首先应根据实际的情况,

2011-09-06 11:36:20 1929

1929 计数器原理图介绍。计数器原理图介绍。计数器原理图介绍

2015-12-25 09:37:05 14

14 HL配套C实验例程分频器1(计数器实现),配合开发板学习效果更好。

2016-04-11 17:14:06 7

7 计数器是用来累计和寄存输入脉冲个数得时序逻辑部件,是数字系统中用途最广泛的基本部件。计数器不仅能用于时钟脉冲的计数,还可以用于分频,定时,产生节拍脉冲及进位数字运算等,是数字系统、计算机系统必不可缺少的部件。

2016-05-05 17:40:59 0

0 集成计数器实现N进制计数集成计数器实现N进制计数集成计数器实现N进制计数

2016-06-08 14:28:43 0

0 约翰逊MC14017B是五级十进制计数器内置代码转换器。 高速运行和约翰逊spike-free输出是通过使用十进制计数器的设计。 十个解码输出通常是低,只在适当的十进制时间走高。 输出的正向变化的时钟脉冲。 这部分可用于分频应用程序以及十进制计数器或十进制译码显示应用程序。

2017-04-06 09:03:48 28

28 HL开发板配套C实验例程100例之分频器1(计数器实现),很好的单片机C语言资料。

2017-09-01 09:28:27 4

4 计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-09-25 10:13:37 8

8 计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-10-23 17:48:48 15

15 环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

2018-01-16 14:54:44 42895

42895

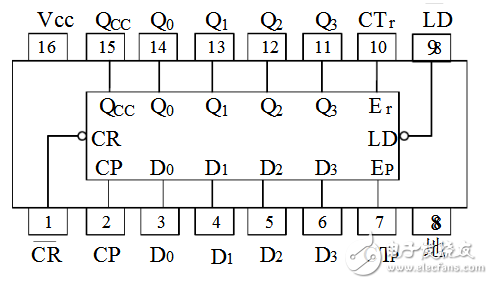

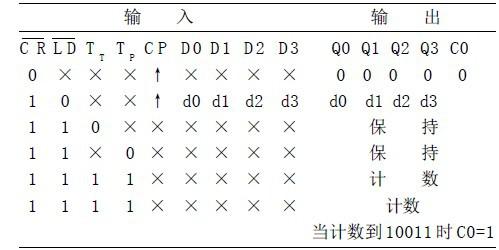

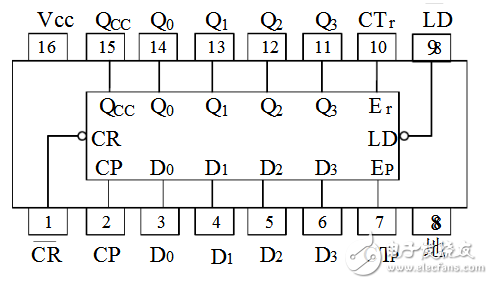

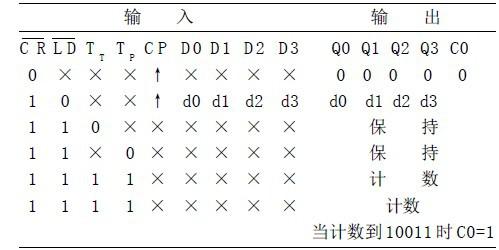

本文主要介绍了计数器74ls161工作原理(分频电路、真值表、逻辑功能)。74LS161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。CP是时钟脉冲信号端,CLK是异步清零端,LD

2018-01-17 19:14:24 317507

317507

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2018-02-24 15:31:08 45454

45454 本文主要介绍了cd40110计数器电路图大全(七款cd40110计数器电路设计原理图详解)。利用交流电源50Hz的输出频率通过分频,可以取得各种不同频率的时基脉冲。该电路选用lmin的时间长度作为

2018-03-04 11:09:50 34417

34417

功能,并且具有进位信号输出,可串接计数使用。重点分析了构成N进制计数器、以74LS163为基础设计一个6分频电路等。

2018-05-08 14:27:23 59407

59407

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 102553

102553

三分频电路,在电路图中,在一般的利用常规计数器对数字脉冲进行奇数分频时,即使输入是对称信号, 输出也得不到占空比为50%的分频输出,其原因是内部触发器采用的是统一的上升沿(或下降沿)进行触发。

2018-08-13 11:08:34 110927

110927

计数器是数字逻辑系统中的基本部件, 它是数字系统中用得最多的时序逻辑电路,其主要功能就是用计数器的不同状态来记忆输入脉冲的个数。除此以外还具有定时、分频、运算等逻辑功能。 计数器不仅能用于对时钟脉冲的计数, 还可使用于定时、分频、产生节拍脉冲以及进行数字运算等。只要是稍微复杂一些的

2019-05-30 08:24:00 14106

14106

关键词:74LS109 , 74LS113 , 分频电路 如图所示为对称输出的三分频电路。在一般的利用常规计数器对数字脉冲进行奇数分频时.即使输入是对称信号,输出也得不到占空比为50%的分频输出

2018-09-28 09:47:01 1726

1726 关键词:SN74193 , 分频器 如图所示为具有奇次和偶次分频的分频电路。 该电路可进行2~32(包括奇次和偶次)分频。同步计数器SN74193的计数输入是由多路调制器SN74153的输出1Y供给

2018-10-03 18:34:01 589

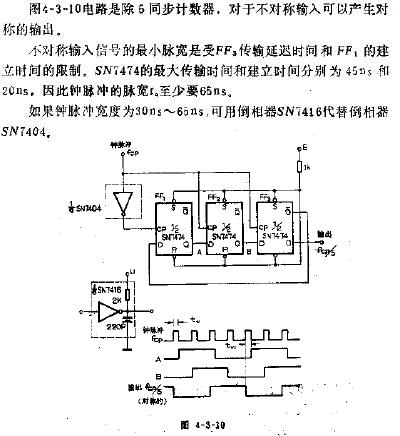

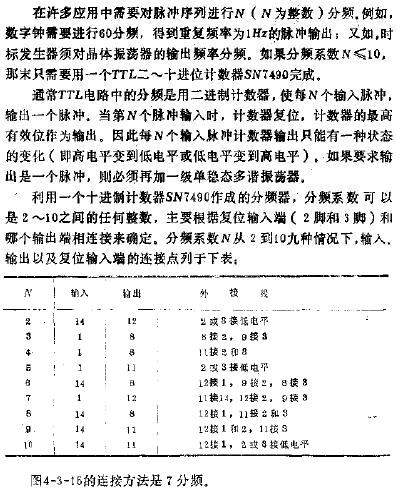

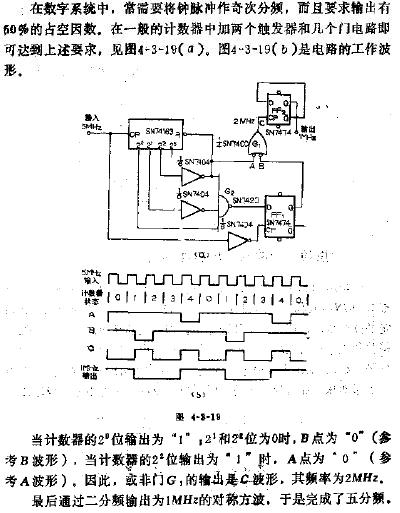

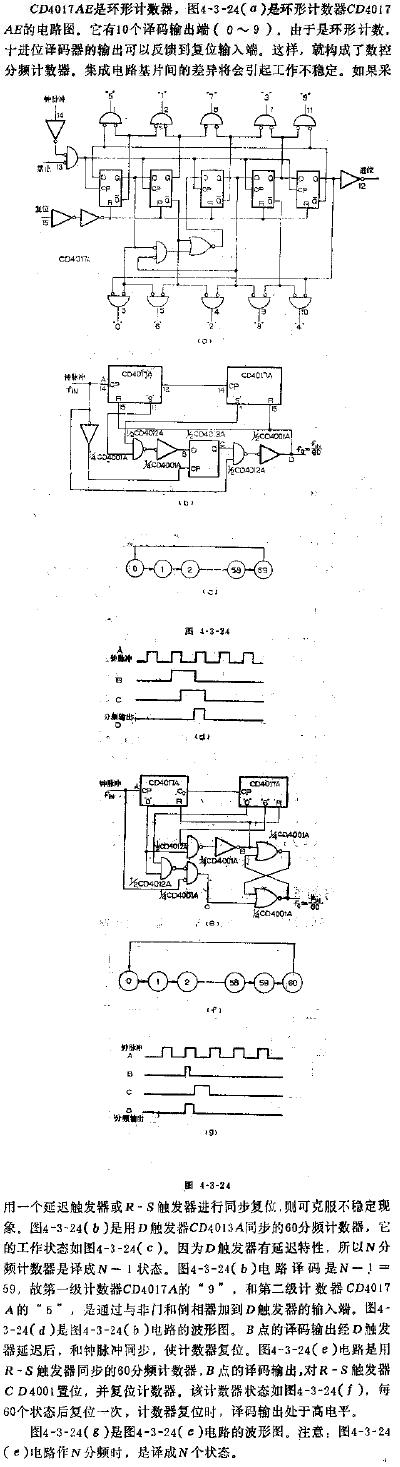

589 频率为1Hz的脉冲输出;又如,时标发生器需对晶体振荡器的输出频率进行分频。如果分频系数N≤10,则只需用一块TTL二-十进制计数器SN7490即可实现。通常的TTL电路中的分频是用二进制计数器,使每N个输入脉冲输出一个脉冲。当第N个脉冲输入时,计数器复位,计数器的最高有

2018-10-03 18:46:02 2984

2984 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2019-02-01 01:49:00 1029

1029

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2019-01-24 14:35:40 63344

63344 计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

2019-12-23 07:07:00 1354

1354

计数器的工作是通过每个时钟脉冲将计数器的内容提前一个计数来计数。当被时钟输入激活时推进其数字或状态序列的计数器被称为以“递增计数”模式操作。同样,当被时钟输入激活时减少其数字或状态序列的计数器被称为以“倒计数”模式操作。在UP和DOWN模式下工作的计数器称为双向计数器。

2019-06-23 07:47:00 12721

12721

使用计数器来做分频,首先计数。例如采用16计数器。每来一次外部时钟,记一次数,当计数到16时,计数器输出一个方波。然后重新计数。当再次达到16时再次输出,这样就形成了16分频。

2019-10-08 10:44:10 36237

36237 所谓非对称PWM输出模式它是相对基于中心对称计数时的对称PWM输出而言的。当计数模式为中心对齐,某个输出通道利用一个比较寄存器做PWM输出时,其对应的PWM输出波形呈中心对称,如下图所示:

2020-05-14 09:21:58 8759

8759

计数器与分频电路实验课件下载

2021-05-25 10:22:09 7

7 什么是计数器芯片? 一般来说,计数器芯片就是用来实现计数这种最基础运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数

2021-07-13 14:09:37 12367

12367 计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器

2021-11-25 18:06:07 32

32 实时计数器(RTC)对计数器寄存器中的(预分频)时钟周期进行计数,并将计数器寄存器的内容与周期寄存器和比较寄存器进行比较。RTC 可以在比较匹配或溢出时产生中断和事件。它将在计数器值等于比较寄存器

2022-01-26 13:45:36 4398

4398 电子发烧友网站提供《带预分频器的Arduino射频频率计数器.zip》资料免费下载

2022-07-06 09:26:04 0

0 电子发烧友网站提供《内插倒数频率计数器FC510预分频器(LMX2324)开源.zip》资料免费下载

2022-08-08 11:32:02 0

0 异步计数器是那些输出不受时钟信号影响的计数器。由于异步计数器中的触发器提供有不同的时钟信号,因此在产生输出时可能会有延迟。设计异步计数器所需的逻辑门数量非常少,所以它们的设计很简单。异步计数器的另一个名称是“波纹计数器”。

2022-10-11 17:16:44 3994

3994

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2022-11-21 09:41:24 751

751 S7-1200的计数器为IEC计数器,用户程序中可以使用的计数器数量仅受CPU的存储器容量限制。

2023-01-29 09:31:56 6124

6124 在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 18647

18647

加计数器(S_CU)在计数初始值预置输入端S上有上升沿时,PV装入预置值,输入端CU每检测到一次上升沿,当前计数值CV加1(前提是CV 小于999);当前计数值大于0时,Q输出为高电平“1”;当R端子的状态为“1”时,计数器复位,当前计数值CV为“0”,输出也为“0”。加计数器指令和参数见图2

2023-04-27 15:38:22 1437

1437

基于51单片机的分频器1(计数器实现)例程源代码

2023-05-18 09:54:09 0

0 电子发烧友网站提供《在Verilog HDL中使用分频器的8位计数器的设计.zip》资料免费下载

2023-06-15 10:14:44 0

0 计数是一种简单的运算,计数器就是让这种运算实现的电路。计数器主要是对脉冲数进行计数,从而达到测量、计数、分频以及控制的目的。智能计数器使用的是全贴片的封装工艺,抗干扰力强,沐渥科技研发的智能计数器

2022-08-08 17:39:27 294

294

4017计数器是一种广泛应用于数字电路中的集成电路,它可以用来计数和控制电子设备。4017计数器有10个输出引脚,可以依次输出从0到9的十个数字,因此也被称为“十进制计数器”或“分频计数器”。在本文

2023-12-15 09:24:28 729

729 计数器是一种被广泛应用于各个领域的实用工具,在我们的日常生活中随处可见。无论是进行时间统计,协助工作任务的完成,还是用于科学研究和编程技术,在各个领域都起到了重要的作用。本文将详细介绍计数器

2024-02-03 10:04:14 589

589

电子发烧友App

电子发烧友App

硬声App

硬声App

2620

2620 4592

4592

9658

9658

9065

9065

4899

4899

59934

59934 1929

1929 0

0 28

28 8

8 15

15 42895

42895

317507

317507

45454

45454 34417

34417

59407

59407

102553

102553

110927

110927

14106

14106

1726

1726 589

589 2984

2984 1029

1029

63344

63344 1354

1354

12721

12721

36237

36237 8759

8759

12367

12367 32

32 4398

4398 3994

3994

751

751 18647

18647

1437

1437

294

294

729

729 589

589

评论