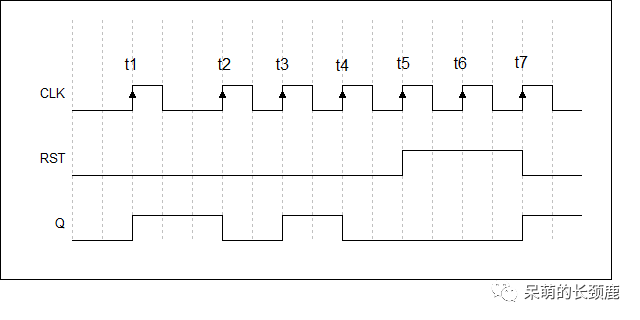

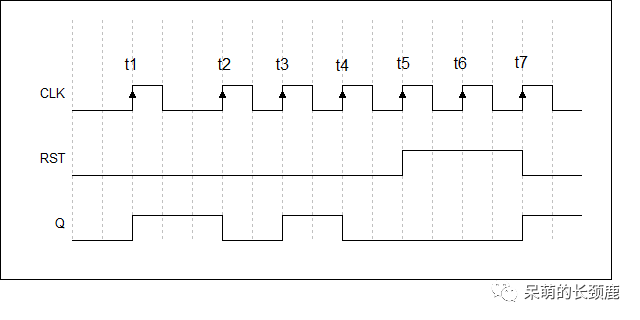

T触发器(Toggle Flip-Flop)Toggle是一个边缘触发的切换触发器,输出Q在输入CLK的每个上升沿时发生变化,在输入CLK的上升沿时翻转输出Q。输入RST为1时输出Q输出值为0且保持不变。

2023-12-04 15:20:15 1524

1524

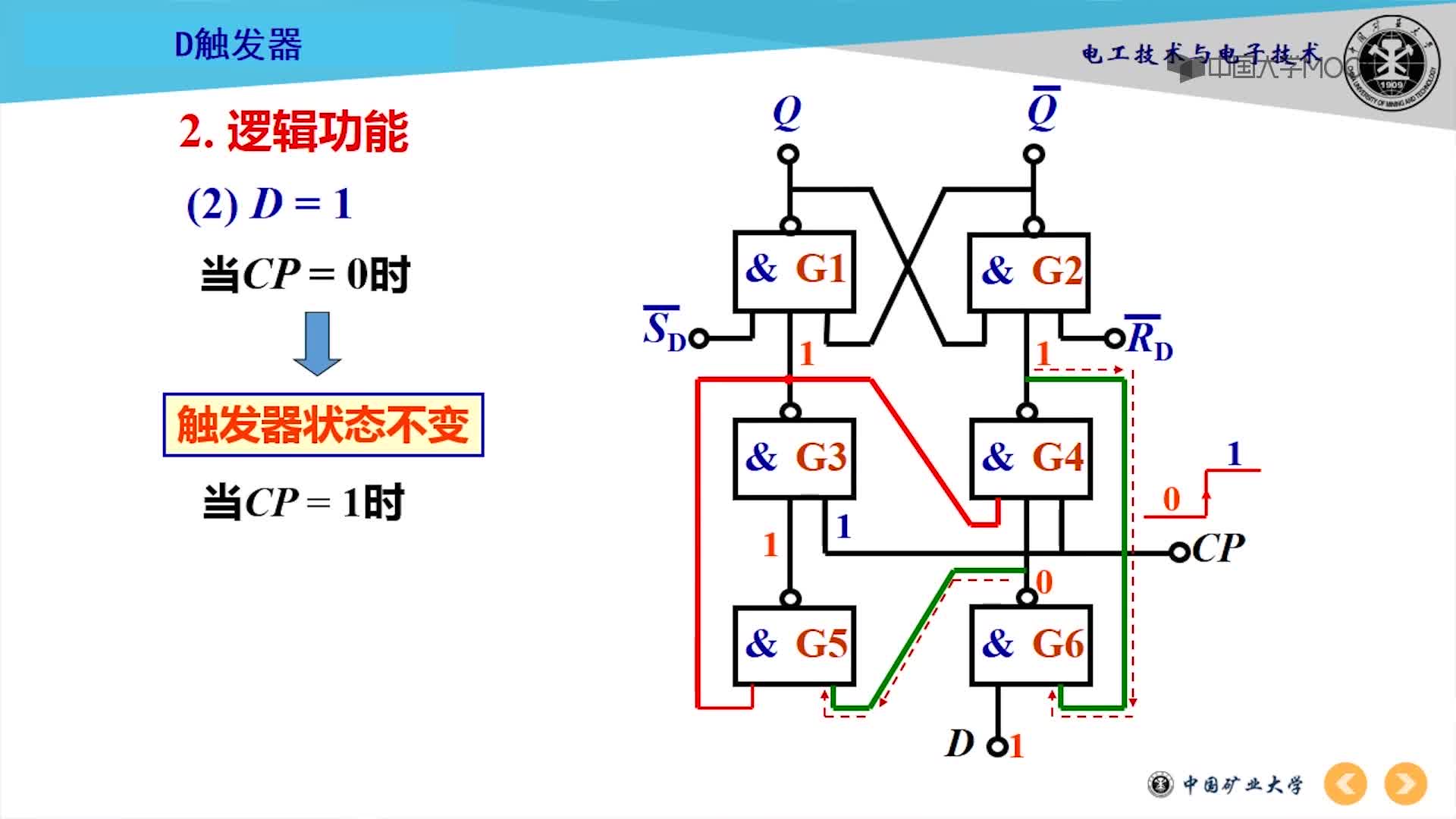

7w74D触发器的功能是什么?怎么控制?

2014-05-05 13:31:57

,呵呵。。。上半年,由于Boss项目,学习了FPGA,学的有点急,也断断续续的,才过几个月,似乎知识已经远去,打开电脑,速览以前的资料,记忆又回来了。。。简单记录下这道题,权当回忆。。。//基本D触发器

2012-02-22 13:54:40

D触发器中PRN、CLRN区别在Quartus II当中查看RTL视图会有PRN和CLRN(CLR)两个引脚的区别PRN是异步置位,可以将输出Q置为输入D(输出Q立马变成输入D)CLRN(CLR)是异步复位,将输出Q置地。

2022-01-11 06:43:53

本帖最后由 gk320830 于 2015-3-7 11:16 编辑

Ti的D触发器SN74LVC2G74,想做一个按键开关机电路,即二分频电路,但是调试过程中老是有问题,请大家帮忙分析分析

2013-10-30 15:44:27

D触发器实现二分频电路(D触发器构成的2分频电路)

2020-03-02 11:05:49

做了一个仿真:key_in作为D触发器的输入,led_out作为触发器输出,时钟周期20ns,key_in每10ns随机变化一次,这样的设置下,key_in信号的变化沿有时会和时钟上升沿重合,根据

2022-01-25 22:41:02

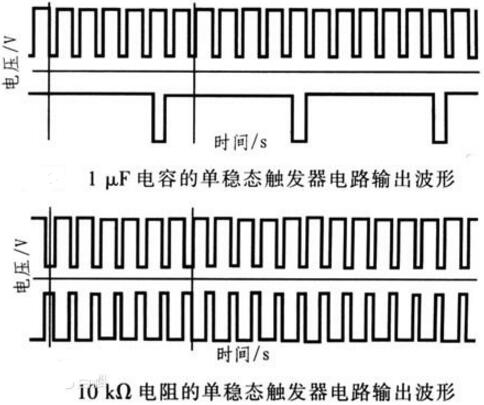

做个单稳态电路、后端做个双稳态电路,按下并松开一次按键实现输出状态翻转一次。现在有个问题:按下去马上松开按键,很正常;但假如按下去的时间比较长,超过单稳态电路中,电容积分复位第一个D触发器的时间,在松开

2014-09-25 16:47:34

双D型触发器构成的振荡器电路实致上是一个可以灵活控制的波形信号发生器,其结构为图1所示的一个由双D型触发器构成的振荡器。该振荡器的起振、停止可以控制,输出波形的相位和占空比也可以调节,其工作波形如图2所示。图2 波形发生器工作逻辑图

2009-05-25 00:41:49

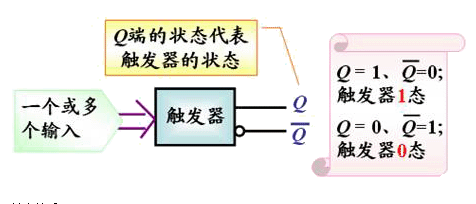

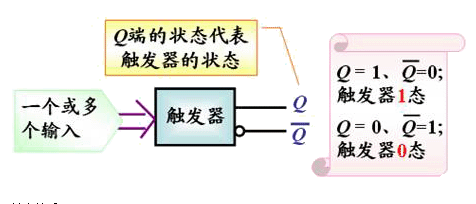

不变。所以,触发器可以记忆1位二值信号。根据逻辑功能的不同,触发器可以分为RS触发器、D触发器、JK触发器、T和T′触发器;按照结构形式的不同,又可分为基本RS触发器、同步触发器、主从触发器和边沿触发器。

2009-09-16 16:06:45

一、实验的目的1、掌握触发器功能的测试方法。2、掌握基本RS触发器的组成及工作原理。3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。4、掌握几种主要触发器之间相互

2009-10-10 11:32:55

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。按触发方式不同分为:电平触发器、边沿触发器和主从触发器。按电路结构不同分为:基本RS触发器和钟控触发器。按存储数据原理不同分为:静态

2012-06-18 11:42:43

D触发器都是边沿触发器么,有人帮忙解释一下么,谢谢了!!!

2016-05-03 20:24:57

触发器输入电路二极管D的作用是只把负的尖脉冲输入触发器,还可用来组成加速电路。

2009-09-22 08:28:30

在学习verilog之前,我们先学习一下D触发器以及它的代码。FPGA的设计基础是数字电路,因此很多同学会认为我们要先学好数字电路之后,才学习FPGA。但是,数字电路教材的内容很多.例如:JK触发器

2018-09-20 15:09:45

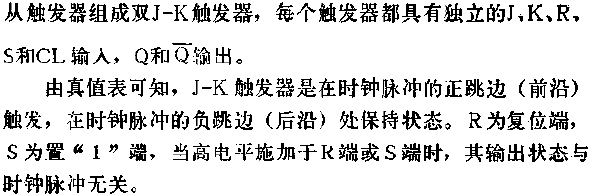

如图, 将j-k触发器用D触发器代替,刚入门 求教

2014-01-09 20:56:31

JK触发器和D触发器所使用的时钟脉冲能否用逻辑电平开关提供?为什么?

2023-05-10 11:38:04

导致两个部分,在时钟信号的相反半周期内使能主部分和从部分。TTL 74LS73是双JK触发器IC,在单个芯片中包含两个单独的JK型双稳态,可以制作单或主从触发器。其他JK触发器IC包括带清零功能

2021-02-01 09:15:31

谁能告诉我PRUTEUS 中D触发器在哪?怎么找啊?

2013-01-16 09:23:05

交通灯3个153的,上次没有上传好!还有另外一个用jk触发器的也上传了,同意的顶啊!

2013-12-15 23:05:21

jk触发器是什么原理jk触发器特性表和状态转换图

2021-02-26 08:18:24

jk触发器设计d触发器,根据原理图实现模8加1计数器,来源于西电慕课貌似这个软件只有5.0和5.12两个版本。在win10下拖曳器件会发生残影的现象,而且无法修改连线。虽然有自动连线功能但感觉线连

2021-07-22 08:39:47

求助谁能教设计一个D触发器

2014-12-24 22:54:35

在学习verilog之前,我们先学习一下D触发器以及它的代码。FPGA的设计基础是数字电路,因此很多同学会认为我们要先学好数字电路之后,才学习FPGA。但是,数字电路教材的内容很多.例如:JK触发器

2017-06-20 09:56:47

2020.3.26_学习笔记两个D触发器 最近发现一个问题,代码中会特地的新建一个D触发器用来锁存信号,让很多人都比较疑惑,明明一个D触发器就可以检测输入是上升沿和下降沿。两个触发器的目的主要

2021-07-30 06:44:48

两个非门电路是如何组成一个D触发器的?即可通俗说明下D触发器吗?

2023-05-10 10:32:03

”,分别称为置“1”端和置“0”端。常见的触发器有R-S触发器、D触发器和J-K触发器等三种,下面简单说明它们的工作原理。类型种类按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。按触发

2019-12-25 17:09:20

`如图所示,图中第一个触发器D接第二个触发器的非Q端,这个时序图,整不明白啊,我的看法是:当第一个时钟信号高电平来的时候,第一个触发器的输出状态Q是不能判断的啊,因为D接在第二个触发器的非Q端。求大佬指点一下 这个图,是如何工作的?`

2019-01-16 11:50:35

单路D型触发器有何功能呢?有哪些引脚?如何利用单路D型触发器去设计一种自锁开关?

2022-02-28 08:06:24

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

完整的脉冲(即0-1-0)施加到时钟输入时,输出Q才获取D的值。TTL和CMOS封装中提供了许多不同的D触发器IC,其中更常见的是74LS74,它是双D触发器IC,在单个芯片中包含两个单独的D型双稳态

2021-02-03 08:00:00

新课第五章 触发器5.1 概述1、触发器具有“记忆”功能,它是构成时序逻辑电路的基本单元。本章首先介绍基本RS触发器的组成原理、特点和逻辑功能。然后引出能够防止“空翻”现象的主从触发器和边沿触发器。同时,较详细地讨论RS触发器、JK触发器、D触发器、T触发器、T'触发器的逻辑功能及其描述方法。

2009-04-02 11:58:41

本帖最后由 郑青松001 于 2013-12-17 12:21 编辑

外部出入信号D触发器滤波 对于外部输出的信号,特别是按键类的比如旋转编码器等,在外部手动旋转的时候会输出的信号抖动很大

2013-12-17 12:19:46

如何用D触发器实现2分频 原理在线等

2016-07-03 19:37:58

本帖最后由 gk320830 于 2015-3-5 20:47 编辑

如何用JK触发器构成D触发器 电路图来人给个图吧..

2011-11-14 15:21:03

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

怎样去设计一种基于门电路的D触发器呢?如何对基于门电路的D触发器进行仿真?

2021-09-14 06:21:42

怎样去创建一个16路D触发器?怎样通过ena使能端去控制16路D触发器呢?

2021-09-15 06:53:13

新建两个D触发器的目的是什么?何谓亚稳态?解决亚稳态的方法是什么?

2021-11-09 07:15:01

[/td] §5、2触发器(第一页) 我们在学习触发器的时要注意以下几点:触发器的状态表、状态图、逻辑符号、特征方程以及各触发器的特点。常用的触发器有:R-S触发器、D触发器、T触发器和JK触发器

2018-08-23 10:36:20

在学习verilog之前,我们先学习一下D触发器以及它的代码。FPGA的设计基础是数字电路,因此很多同学会认为我们要先学好数字电路之后,才学习FPGA。但是,数字电路教材的内容很多.例如:JK触发器

2019-01-17 17:24:19

Jack Kilby)和D(延迟)。典型的触发器包括零个、一个或两个输入信号,以及时钟信号和输出信号。一些触发器还包括一个重置当前输出的明确输入信号。第一个电子触发器是在1919年由

2019-06-20 04:20:50

用CD4013双D触发器做的脉冲4分频器

2021-05-13 07:25:00

电后,与非门的1脚为低电平,故U1A输出端第3脚为高电平,3脚与与非门的12脚相连,故12脚也为高电平。 2、电路刚上电时,D触发器的RD引脚通过电容C1,电阻R2上电复位,使D触发器的输出Q=D

2023-03-20 15:33:48

概述:CD4013是一款由两个相同的、相互独立的数据型触发器构成的置/复位双D型触发器。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出,此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计算...

2021-04-08 06:08:10

D触发器结构的五分频器逻辑电路

2019-09-11 11:29:19

怎样去设计一个基于数字电路的D触发器?如何对基于数字电路的D触发器进行仿真?

2021-09-16 06:45:31

电平触发的D触发器型号有哪些?大部分都是边沿触发的,现在要用到电平触发器,不知道具体型号没法买到

2019-02-28 14:32:13

电平触发器和边沿触发器符号

2019-10-18 09:01:09

1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 0

0 D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 18427

18427 D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2222

2222

JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器为

2010-03-08 13:36:29 6142

6142 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 4395

4395 施密特触发器,施密特触发器是什么意思

施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发

2010-03-08 14:14:56 1844

1844 触发器的分类, 触发器的电路

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1554

1554 本次重点内容:1、触发器的概念和分类。2、同步触发器、主从触发器、边沿触发器的含义。

4.1.1 触发器概述一、触发

2010-08-19 08:57:47 19312

19312 图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 17220

17220

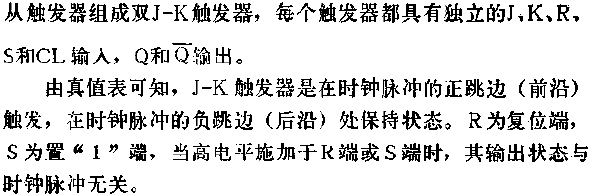

J-K触发器是一种多功能触发器,它既具有R-S触发器的功能,又具有D触发器和T触发器的功能,因此使用十分灵活

2010-09-24 00:12:06 1279

1279

图中所示是用J-K触发器组成的D触发器电路。

从J-K触发器的逻辑图已知在D触发器端增

2010-09-24 00:21:27 6900

6900

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 178012

178012

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 69651

69651

触发器分为电平触发和边沿触发两类。电平触发的触发器原理较简单,学习触发器时,一般先学习电平触发。电平触发的触发器主要是基本RS触发器基本RS触发器由电平触发,并且有一个重要的约束条件:/SD和/RD不能同时为零。即:/SD+/RD=1。

2018-01-31 10:26:26 5830

5830

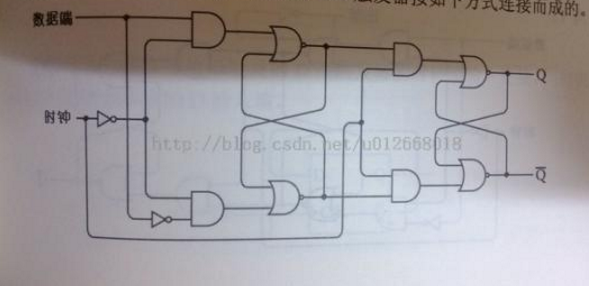

本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 71987

71987

本文开始介绍了单稳态触发器的概念,其次阐述了单稳态触发器工作特点和单稳态触发器的用途,最后介绍了单稳态触发器的应用。

2018-03-27 10:16:25 30508

30508

本文开始介绍了触发器的定义和触发器的特点,其次阐述了触发器的分类和触发器的作用,最后介绍了触发器的工作原理。

2018-03-27 17:35:52 20675

20675 本文开始阐述了单稳态触发器工作特点和单稳态触发器的分类,其次阐述了单稳态触发器工作原理,最后介绍了常用的CD4098单稳态触发器。

2018-03-28 15:41:35 38999

38999

触发器是一种用来保障参照完整性的特殊的存储过程,它维护不同表中数据间关系的有关规则。当对指定的表进行某种特定操作(如:Insert,Delete或Update)时,触发器产生作用。触发器可以调用存储过程。

2019-07-12 10:05:42 23612

23612

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 84376

84376

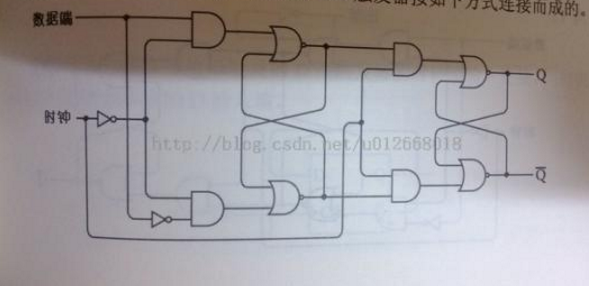

脉冲触发器由两个相同的电平触发的SR触发器组成,其中左SR触发器成为主触发器,右手侧称为从触发器。

2021-02-11 10:56:00 7953

7953

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 14168

14168

什么是触发器?触发器的作用是什么?触发器的触发方式 触发器是一种在数据库中执行自动化操作的工具。它是一种特殊的存储过程,可以监视数据库表的变化,并在满足特定条件时自动触发一系列操作。触发器通常

2023-08-24 15:50:15 3677

3677 不同类型的触发器可能有不同的执行顺序。例如,对于同一个表上的多个触发器,插入触发器(INSERT trigger)可能先于更新触发器(UPDATE trigger)执行。

2024-02-05 10:09:13 223

223

D触发器的稳态 D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输入D为高电平时,输出Q保持为高电平。 D触发器和RS触发器

2024-02-06 11:32:41 423

423 稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的触发器有不同的稳态。本文将详细描述几种常见的触发器及其稳态,并介绍如何判断触发器

2024-02-06 13:36:55 367

367 触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器和JK触发器的区别和联系。 一、T触发器 T触发器是一种

2024-02-06 14:04:55 419

419 如何用JK触发器构成T触发器 JK触发器是一种基本的触发器电路,由两个输入端J和K控制,以及两个输出端Q和Q'组成。JK触发器的输出可以持续性地保持其前一状态或由输入信号而改变。T触发器是一种特殊

2024-02-06 14:11:11 425

425 电平触发器、脉冲触发器、边缘触发器有什么不一样? 电平触发器、脉冲触发器和边缘触发器是数字电路中常用的触发器类型,它们在工作原理和触发方式上存在着一些不同之处。下面将详细介绍这三种触发器的特点

2024-02-06 15:51:44 365

365

电子发烧友App

电子发烧友App

评论