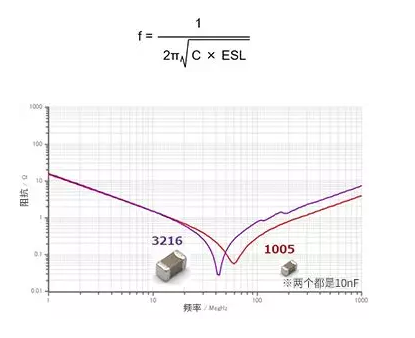

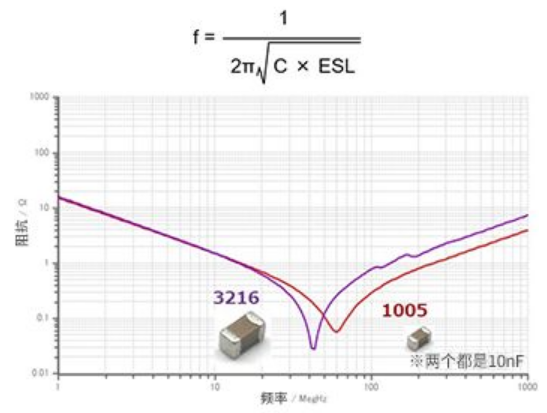

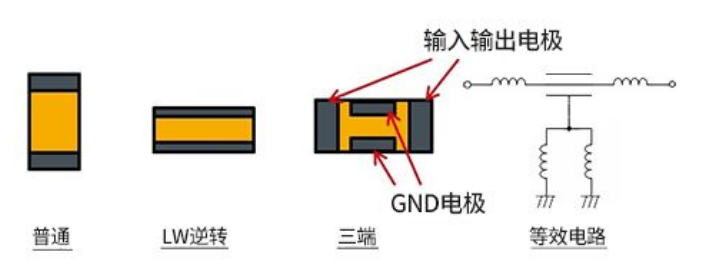

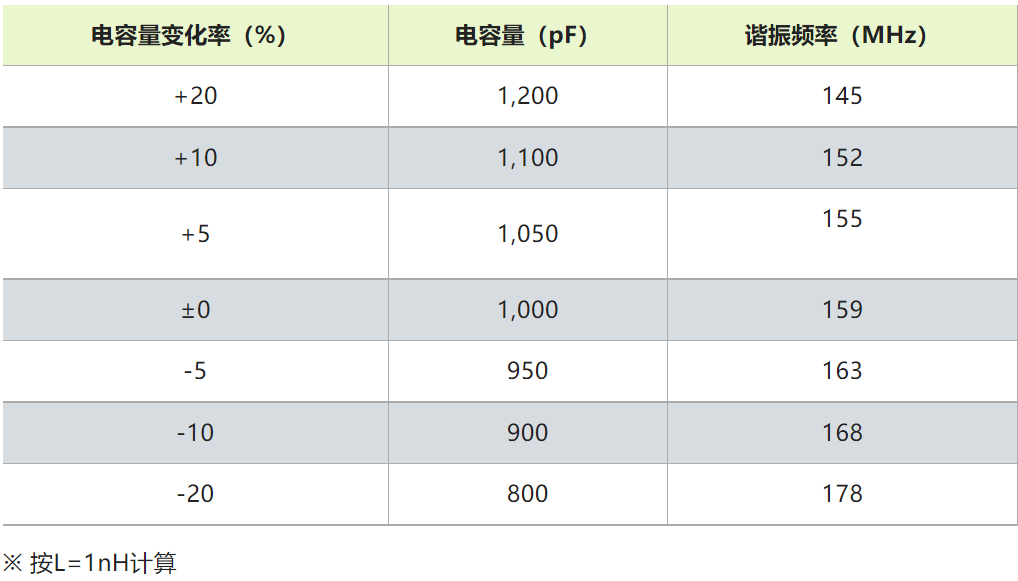

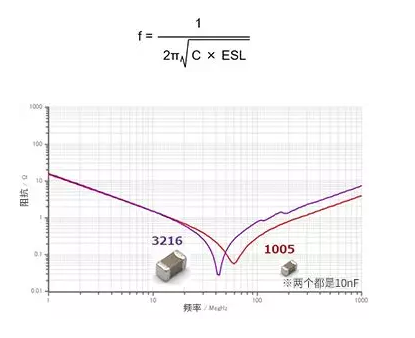

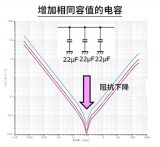

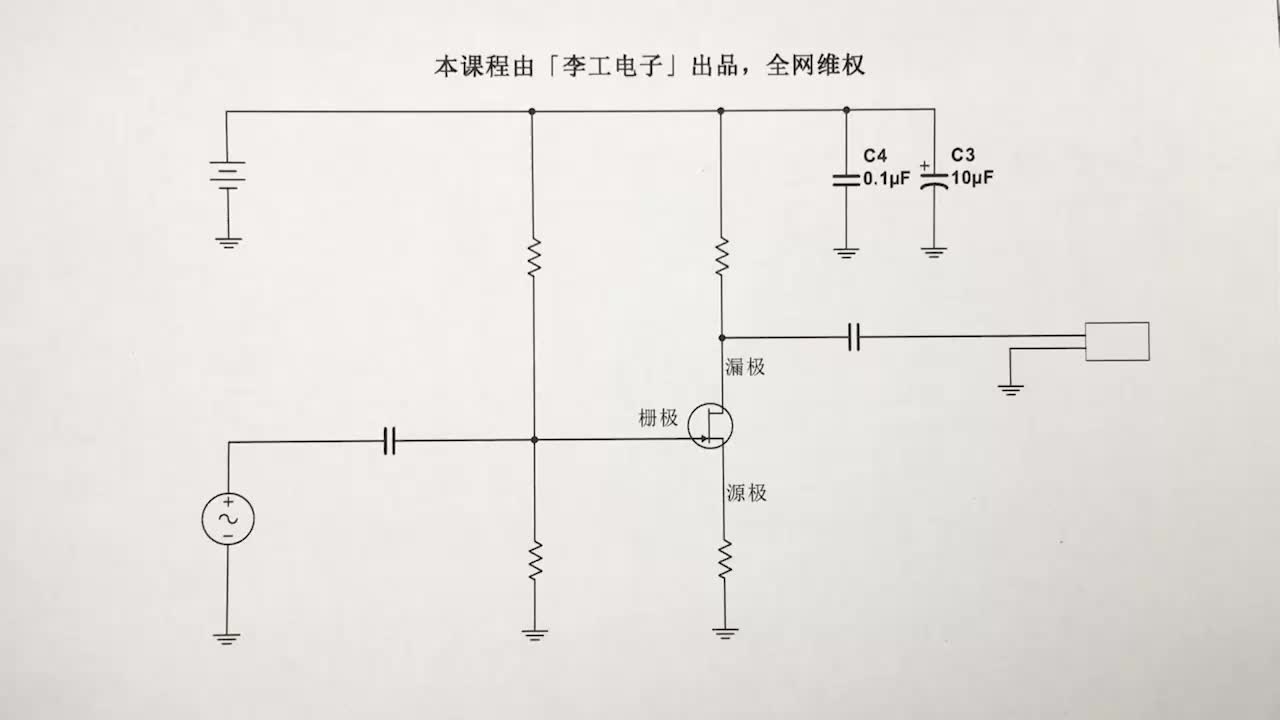

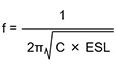

去耦电容的有效使用方法的第二个要点是降低电容的ESL(即等效串联电感)。虽说是“降低ESL”,但由于无法改变单个产品的ESL本身,因此这里是指“即使容值相同,也要使用ESL小的电容”。通过降低ESL,可改善高频特性,并可更有效地降低高频噪声。

2019-04-04 12:55:19 1504

1504

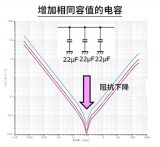

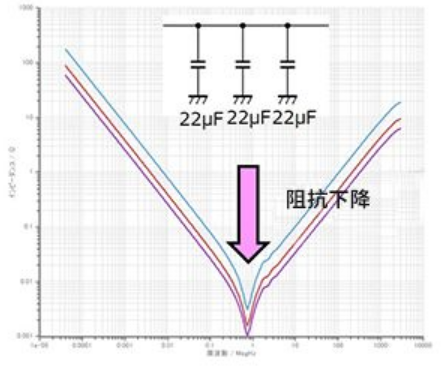

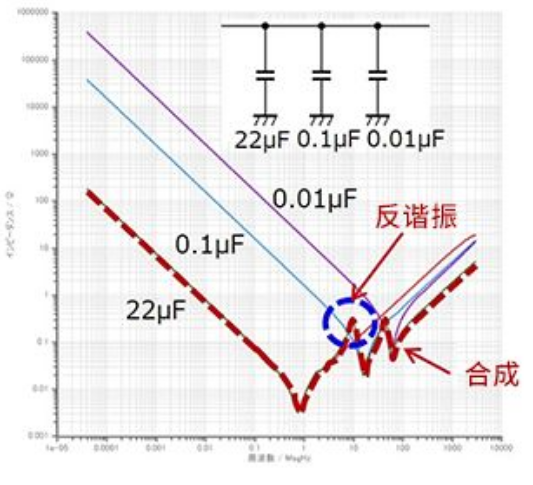

去耦电容的有效使用方法之一是用多个(而非1个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

2023-08-02 12:34:43 268

268

有两个500v 100uf的电容 串联在1000v直流电中,想要选取分压电阻,让每个电容分得500v电压,分压电阻阻值和功率如何选择?

补充内容 (2016-8-5 09:57):

在线等

2016-08-04 17:44:36

我这边在一个PCB设计上(汽车应用的)看到过一个两个相同值的电容串联并连接到电路上的情况,请问为什么不用一个单个等效的电容呢,非得两个串联还是有别的考量,希望大家能说说看法。

2018-10-26 11:50:13

谁能帮我解释一下 这两个电容是什么意思

2013-09-21 18:28:59

请问各位前辈这个图两个电源能共用一个电容器吗,也就是说一个电容器,两个电源能同时给其充电吗?

2022-02-27 17:24:25

采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。

2019-05-31 07:55:03

电容退耦原理

采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。

对于电容退耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部电荷

2018-06-24 06:27:56

是大电容靠近IC,这是为什么呢? 首先要明白,A和C处两个电容都是旁路电容,B处的两个电容是去耦电容(滤波加储能作用)。 其次芯片A是电源芯片,它的输出相对于B处的1uF电容来说,就是输入,所以先

2021-01-11 16:31:51

对于已经知道了电容的具体特性和适用范围,以及去耦原理,那么就知道了去耦的具体方法了吗?不是的,下面我们将讲解一下,具体安装到电路板上之后的去耦原理以及具体如何防止电容的准则!

2021-03-04 08:11:41

ADIS16 IMU2和ADIS1644X/FLEX在哪可以买到,自己做的话两个电容是多大的,两排管脚什么型号,有没有关于ADIS16IMU2的详细资料

2023-12-29 07:14:24

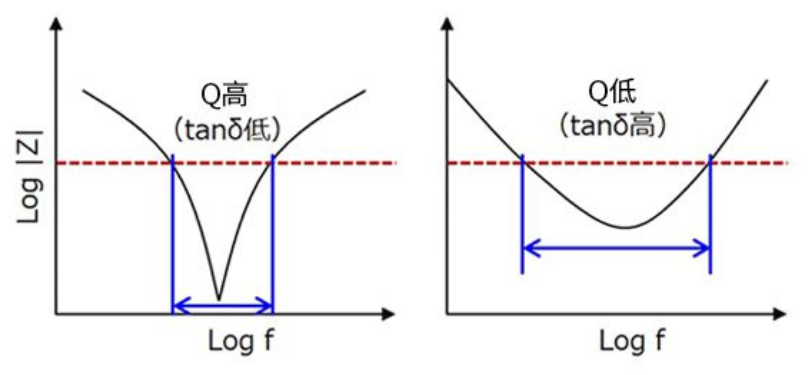

去耦电容的有效使用方法:其他注意事项①Q较高的陶瓷电容电容具有被称为“Q”的特性。下图即表示Q和频率-阻抗特性之间的关系。当Q值高时,阻抗在特定的窄带会变得非常低。当Q值低时,阻抗虽然不会极度下降

2021-03-27 08:00:00

想为cyclone V 系列的5CEFA7F27这款FPGA设计去耦电容电路,但是不知道该如何下手。参考了altera公司的一块开发板,给出的FPGA的去耦电容电路如下所示,但是感觉这个去耦电容电路

2016-07-09 10:11:21

的电容必须具有较低的引线和PC走线电感,因此,各电源电容必须非常靠近它去耦的IC的两个引脚。选择内部电感较低的电容也很重要,通常使用陶瓷电容。许多IC中的电路会在电源端产生高频噪声,这种噪声也必须通过跨接

2019-05-15 04:24:21

请较一下LDO(比如LT3045)和普通三端稳压(比如LT1083)输入电容与输出电容正确的计算方法,用书上的方法计算都感觉不对,我感觉用去耦的方式计算应该比较对一下,请教一下具体怎么配置吗

比如

2024-01-04 08:04:43

还要考虑电容的介质,一个比较保险的方法就是多并几个电容。去耦电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是0.1μF。

2019-08-26 09:41:50

。如果设计允许存在额外的层(上例中,从六层变为八层),则应将两个额外的接地层放在第一和第二电源层之间。在核心间距同样为 2 到 3 密尔的情况下,此时层叠结构的固有电容将加倍,示例见图 3。图 3.

2022-05-07 11:30:38

最大。如果设计允许存在额外的层(上例中,从六层变为八层),则应将两个额外的接地层放在第一和第二电源层之间。在核心间距同样为 2 到 3 密尔的情况下,此时层叠结构的固有电容将加倍,示例见图 3。图 3.

2020-11-18 09:18:02

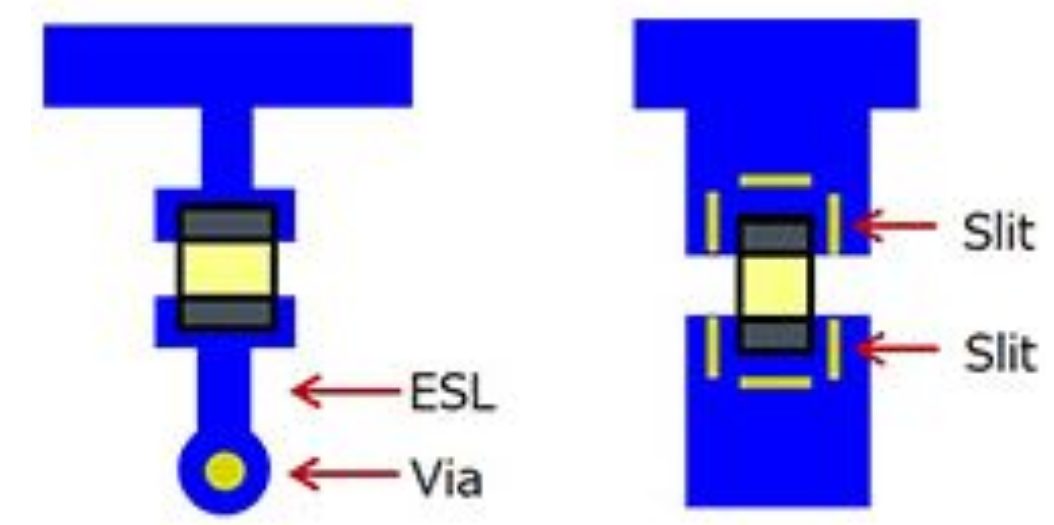

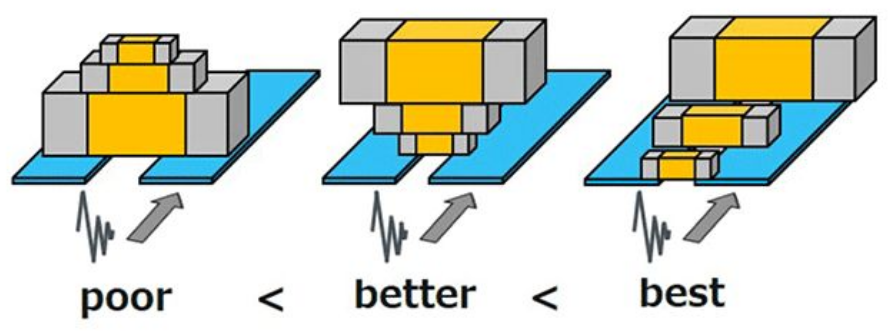

过孔,这会引入很大的寄生电感,一定要避免这样做,这是最糟糕的安装方式。第二种方法在焊盘的两个端点紧邻焊盘打孔,比第一种方法路面积小得多,寄生电感也较小,可以接受。 第三种在焊盘侧面打孔,进一步减小了回路

2018-09-18 15:56:26

看资料很快就能掌握的。直到被骂好几次后我们回去找相关资料,为什么设计PCB电容要就近摆放呢,等看了资料后就能了解一些,可是网上的资料很杂散,很少能找到一个很全方面讲解的。工作两年后,我看到了相关人士讲

2018-09-12 10:46:08

个很全方面讲解的。下面这些内容是我转载的一篇关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。 老师问: 为什么去耦电容就近摆放呢? 学生答: 因为它有有效半径哦,放的远了

2018-09-17 17:40:22

电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是 0.1μF。这个电容的分布电感的典型值是 5μH。0.1μF 的去耦

2011-02-24 14:30:32

布线上采取措施,使信号线的杂散电容降到最小; 2、 另一种方法是设法降低供电电源的内阻,使尖峰电流不至于引起过大的电源电压波动; 3、 通常的做法是使用去耦电容来滤波,一般是在电路板的电源入口处放

2023-04-11 16:26:00

不重要,能够解决问题才是关键。回归主题,去耦电容和旁路电容的区别是什么?编者勉强地从两个方面做了区分以便大家理解,但仅供参考,因为两者并没有明确的区别界限。三、去耦电容和旁路电容的2个主要区别1

2022-11-04 22:29:20

两个电容串联,并到直流电源上。假设直流电源电压10V,两个电容相同,每个电容会分压5V吗?

2023-03-27 14:35:25

请问一下,为什么天线要接两个串联电感再到电容,为什么不能直接接到电容呀?

2019-07-17 04:35:52

、在电路板布线上采取措施,使信号线的杂散电容降到最小;2、 另一种方法是设法降低供电电源的内阻,使尖峰电流不至于引起过大的电源电压波动;3、 通常的作法是使用去耦电容来滤波,一般是在电路板的电源入口处

2016-08-27 11:11:57

51单片机晶振旁边那两个微调电容怎么连接的,最好可以给我个图。。。还有那个复位脚是否一定要连接。。。{:1:}

2012-11-20 19:37:35

范围内有效,所以要用两个,一大一小。这只是一个很笼统的分析方法,这里我有个想不明白的地方就是它们的频率范围,如果它们的频率区域有一段没覆盖到,那么那段频率的噪声(或者说干扰)就会对电源产生影响

2013-03-06 19:58:49

由于电源线必须为交流地,最大程度减小交流地回路的寄生电感非常重要。元件布局或摆放方向可能会引起寄生电感,例如去耦电容的地方向。旁路电容有两种摆放方法,分别如图所示:这种配置下,将顶层上的VCC焊盘连接

2020-07-15 08:30:00

电源线必须为交流地,最大程度减小交流地回路的寄生电感非常重要。元件布局或摆放方向可能会引起寄生电感,例如去耦电容的地方向。旁路电容有两种摆放方法,分别如图所示:这种配置下,将顶层上的VCC焊盘连接至内层

2020-07-15 10:00:00

` 这两个电容叫晶振的负载电容,分别接在晶振的两个脚上和对地的电容,一般在几十皮发。它会影响到晶振的谐振频率和输出幅度,一般订购晶振时候供货方会问你负载电容是多少。 晶振的负载电容=[(Cd*Cg

2011-10-17 13:54:43

旁路电容是把电源或者输入信号中的交流分量的干扰作为滤除对象;去耦电容是芯片的电源管脚,两者有啥区别了?详细请看附件(内有福利哦~~)

2021-09-08 10:02:18

去耦电容分为哪几种?如何去放置去耦电容呢?在设计中如何防止上电及正常工作时出现总线冲突呢?

2021-11-03 07:17:04

的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是 0.1μF。这个电容的分布电感的典型值是5μH。0.1μF的去耦电容有5μH的分布电感,它的并行

2012-03-08 23:42:09

电子线路中的同一个电容,有时候会称它去耦电容,有时候又会称它为旁路电容。 电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,但是,当我们从不同的角度去看时,它所起的作用是不同的,所以才有

2021-05-25 06:14:19

时间仓促,我省去了比较麻烦的去耦电容器。谁会需要它呢,对吧?我收集数据大概有一个星期了,但获得的任何结果都无法与预期结果相匹配。于是我做了大量更改,试图提升性能,但都没有效果。最后,我决定添加一个去耦

2018-09-20 15:44:35

器。谁会需要它呢,对吧? 我收集数据大概有一个星期了,但获得的任何结果都无法与预期结果相匹配。于是我做了大量更改,试图提升性能,但都没有效果。最后,我决定添加一个去耦电容器,不出所料,问题解决了。 这让我

2018-12-26 14:19:56

去耦电容在PCB板设计中的应用在板设计中应充分考虑电磁兼容方面的问题,合理地使用去耦电容在PCB板防止电磁干扰中具有重要作用, 本文就去耦电容的容量及其具体应用作了较为全面、详细的叙述,同时还介绍了增强去耦电容效果的一些实用方法。[hide][/hide]

2009-12-09 14:08:29

去耦电容的有效使用方法之一是用多个(而非1个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

2019-08-02 06:56:29

影响,而且将两个去耦电容以相反走向放置在一起,从 而使它们的内部电流引起的磁通量相互抵消,能进一步降低 ESL。(此方法适用于任何数目的去耦电容,注意不要侵犯 DELL 公司的专利)如果相同

2015-08-26 21:56:00

1.电源附近去耦电容的选择很多IC管脚的VCC会增加一个0.1uf的去耦电容,因为电容的滤波曲线在谷底最低的位置滤波效果最好。当IC内部的逻辑门频率是是10MHz-50MHz的时候,0.1uf电容

2021-12-31 07:29:16

电容方程 在计算去耦电容之前,需要先画出戴维宁等效电路。总的阻抗值等于电路中两个电阻的并联。假定图2所示的戴维宁等效电路中,ZS=150Ω,ZL=1.0 kΩ,那么 图2戴维宁等效电路 方法一

2018-11-27 15:19:23

一个原型设计电路板省去了比较麻烦的去耦电容器;但获得的任何结果都无法与预期结果相匹配。最后,添加一个去耦电容器,问题解决了。什么我们需要使用去耦电容器?它的作用到底是什么?

2021-04-02 07:46:38

种解释对应的分别是低频和高频两种情况,但本质上都是希望减小PDN上的电压突变,这就是去耦。2.为什么要有那么多的去耦电容而不是选择一个等效的大电容?这个问题也是要分情况,对于低频来说,很多个小的去耦电容

2019-05-07 06:22:23

的电压波动。而去耦和旁路电容都是相对负载变化引起的噪声来说。所以它们两个没有必要做区分。而且实际上电容值的大小,数量也是有理论根据可循的,如果随意选择,可能会在某些情况下遇到去耦电容(旁路)和分布参数发生

2020-12-02 09:34:28

;elsif clock_falling_edge 去抖输入 - 使用最后读取值万一但实施失败我还修改了我的时钟pll配置,我创建了两个时钟输出,180度相移第一个时钟上升沿读取输入线,第二个时钟去抖动输入

2019-08-05 06:25:54

和滤波。认为这两个作用是一样的,其实他们两个是有那么点区别的。今天我先来讲一讲电容的去耦作用吧。在此之前,我先来说说电容的主要参数!电容等效模型如下图所示一:C,电容的容值,这是个最重要的参数,百度查

2015-09-27 15:29:48

为什么基本上信号对接都选择用两个光耦。图2 如图2是工业相机手册中给出的光耦输出电路,我在图2的右侧设计电路是否还需要加光耦?

2019-12-25 17:18:27

的噪声低于饱和CMOS逻辑。图7. 从数字电源去除去耦电容后AD9445评估板的SNR图这些实验表明,除去大多数或所有去耦电容会导致性能降低,但要分析或预测除去一两个去耦电容的影响是很困难的。当拿不定主意

2018-10-19 10:58:00

关于旁路电路和去耦电容,基本上有经验的都知道如何处理,不过估计没有几个人会去完整总结。看到网友的一篇博客比较完整的梳理整理了这两个概念,转发到这里供大家参考 写作原因:最近工作重心由软件渐渐向硬件

2018-12-07 09:39:59

很多人做MCU51单片机得时候,不明白晶体两边为什么要加两个电容,大小一般在15pF~33pF之间,有些特殊的,还需要在晶体上并联一个大电阻,一般老师的解释是提高晶体振荡电路的稳定性,有助于起振

2011-09-28 00:11:51

晶振的两个电容叫负载电容,分别接在晶振两个脚上的对地的电容,一般在几十PF。据松季电子介绍,它会影响到晶振的谐振频率和输出幅度。 各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器。晶振引脚

2013-12-23 17:32:13

```晶振旁的两个小电容是什么作用```

2012-11-29 17:49:43

了。 讲的通俗易懂一点,用一个曾经听过的笑话来比喻,大概意思就是本飞机被我劫持了,其他劫持者等下次吧。这个电容就是本次劫机者。 晶振电路其实是个电容三点式振荡电路,输出是正玄波晶体等效于电感,加两个槽路

2018-10-23 16:14:02

如何在两个电源接地不连通的情况下电路有效运行。

2016-07-01 10:52:54

集成电路的电源,地之间都要加一个去耦电容。去耦电容有两个作用:一方面是本集成电路的蓄能电容,提供和吸收该集成电路开门关门瞬间的充放电能;另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容为0.1uf

2013-03-08 16:33:18

的介质,一个比较保险的方法就是多并几个电容。去耦电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是0.1μF。这个电容

2018-02-05 15:13:14

滤波电容用在电源整流电路中,用来滤除交流成分。使输出的直流更平滑。 : 去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。 旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利

2012-04-04 23:29:40

今天看了一块电路板,在电源处并联了两个小电容,一个大电容。在论坛里和网上搜了一下,能明白原理图上并联多个相同的电容是为什么了,但是在PCB上同意电源引脚处这么连就不懂了,望论坛里的大大指点一下。

2020-04-01 09:01:22

品质的好坏已经成为我们判断板卡质量的一个很重要的方面。 ①电容的功能和表示方法。由两个金属极,中间夹有绝缘介质构成。电容的特性主要是隔直流通交流,因此多用于级间耦合、滤波、去耦、旁路及信号调谐。电容在

2019-08-05 04:36:09

`请问能否用下图这样两个光耦并联,实现双向信号的隔离?其中信号在一种应用下,固定为输入或输出。`

2021-03-25 10:09:39

4.电容退耦的两种解释采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。对于电容退耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部

2021-11-15 09:17:00

电容在集成电路电源和地之间的有两个作用: 一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。 数字电路中典型的去耦电容值是0.1μF。这个电容的分布电感的典型值是5μH。 0.1μF的去耦

2017-05-04 10:48:07

ADIS16IMU2和ADIS1644X/FLEX在哪可以买到,自己做的话两个电容是多大的,两排管脚什么型号,有没有关于ADIS16IMU2的详资料

2019-01-08 11:16:33

我知道在电源设计中,电源输入与输出都要滤波和去耦合,请问下怎么叫去耦电容?什么叫旁路电容啊??我知道概念,它们两者区别在于:旁路电容是把输入信号中的干扰信号去掉,而去耦电容是把输出信号中的干扰信号去掉;但是我不知道具体怎么区分?难道左边的是旁路电容,右边的是去耦电容吗?

2018-10-23 09:32:13

电源为两节5号电池,负载为两个550电机7v,电流2.7A,用超级电容充放电(只需要电机转10s左右)或者不需要超级电容的方法也行,急用采用必有重谢!

2023-07-29 09:20:51

、一道问题如下图所示,先抛出来一道问题:“ 电源上并联两个10uF和两个100nF,为什么不直接用一个22uF电容 **?**这样还可以节省PCB空间”。这个问题比较小众,面试中标的概率比较小,但实际使用

2022-09-09 11:34:08

这两个电压跟随器有什么区别呢?同时有几个问题需要请教,一是加入双电源的电压跟随器与不加电源的电压跟随器有什么区别呢;二是±12电源下面的电阻有什么用,是限流用的吗?两个电容并起来是滤波用还是去耦用?还是说前面说的不对,是电阻和电容组合起来用?

2019-10-17 15:17:34

; 1、等效串联电阻ESR(Resr):电容器的等效串联电阻是由电容器的引脚电阻与电容器两个极板的等效电阻相串联构成的。当有大的交流电流通过电容器,Resr使电容器消耗能量(从而产生损耗

2009-03-27 14:55:46

如题,问下大神,这两个分别是什么型号的电容?一个松下护眼台灯突然不亮了,拆开后测量各模块,应该是这个LED模块中的两个电容有问题,灯为12V。

2022-03-17 16:33:03

什么是去耦和旁路?去耦和旁路可以防止能量从一个电路传播到另一个电路上去,进而提高电源分配系统的质量。 回顾前面章节的介绍,可知数字逻辑电路通常涉及两个可能的状态,“0”和“I”(参考图3-1

2018-11-23 15:59:57

MAMF-011069集成双开关 - LNA 模块MAMF-011069 是一款双通道模块,包含两个 2 级低噪声放大器和两个高功率开关,采用 5 毫米 32 引脚 QFN 封装。该模块的工作频率为

2023-01-06 11:31:24

去耦电容的有效使用方法的第二个要点是降低电容的ESL(即等效串联电感)。虽说是“降低ESL”,但由于无法改变单个产品的ESL本身,因此这里是指“即使容值相同,也要使用ESL小的电容”。通过降低ESL,可改善高频特性,并可更有效地降低高频噪声。

2019-08-22 10:40:15 2982

2982

使用超级电容器实现备用电源的有效方法

2022-10-28 12:00:01 11

11 去耦电容有效使用方法的要点大致可以分为以下两种。另外,还有其他几点需要注意。

2022-11-23 09:41:45 645

645

电子发烧友App

电子发烧友App

评论