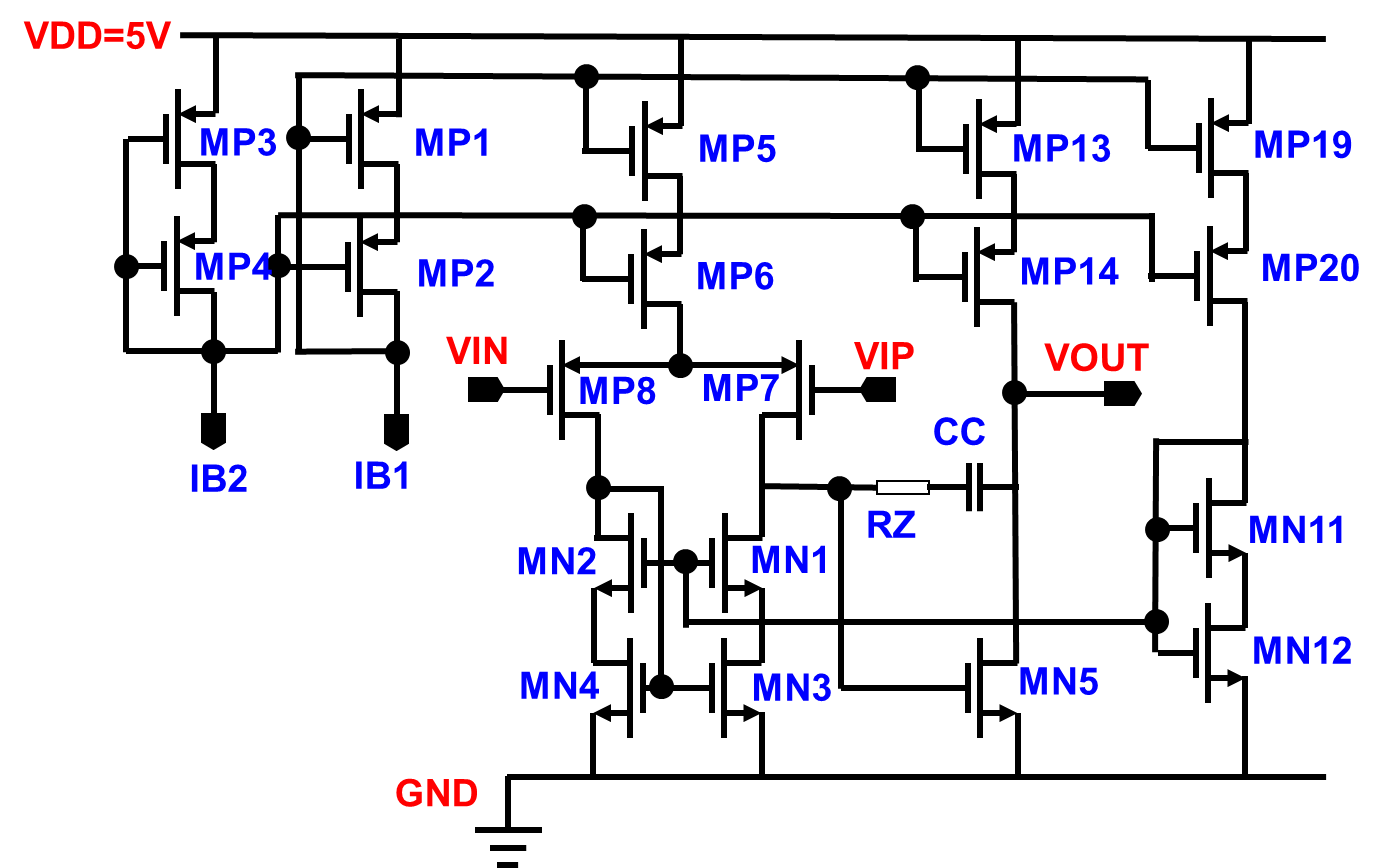

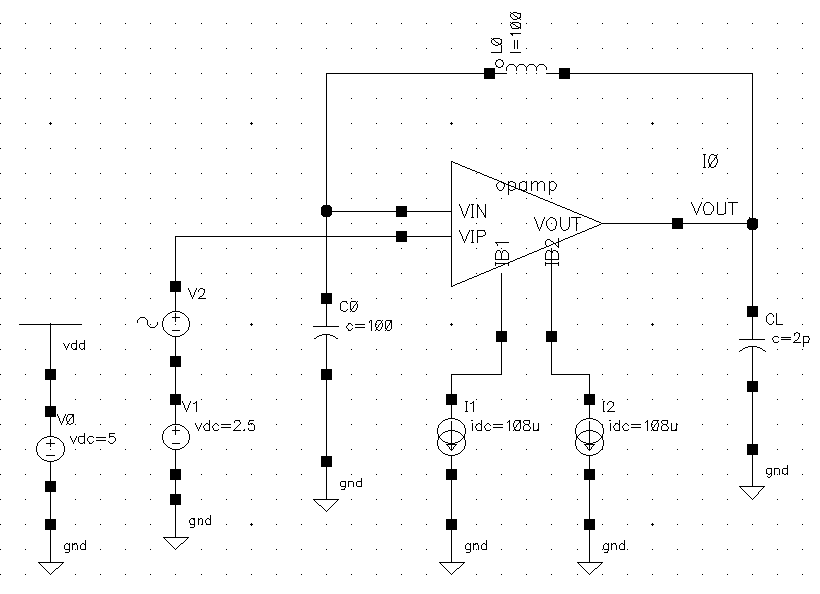

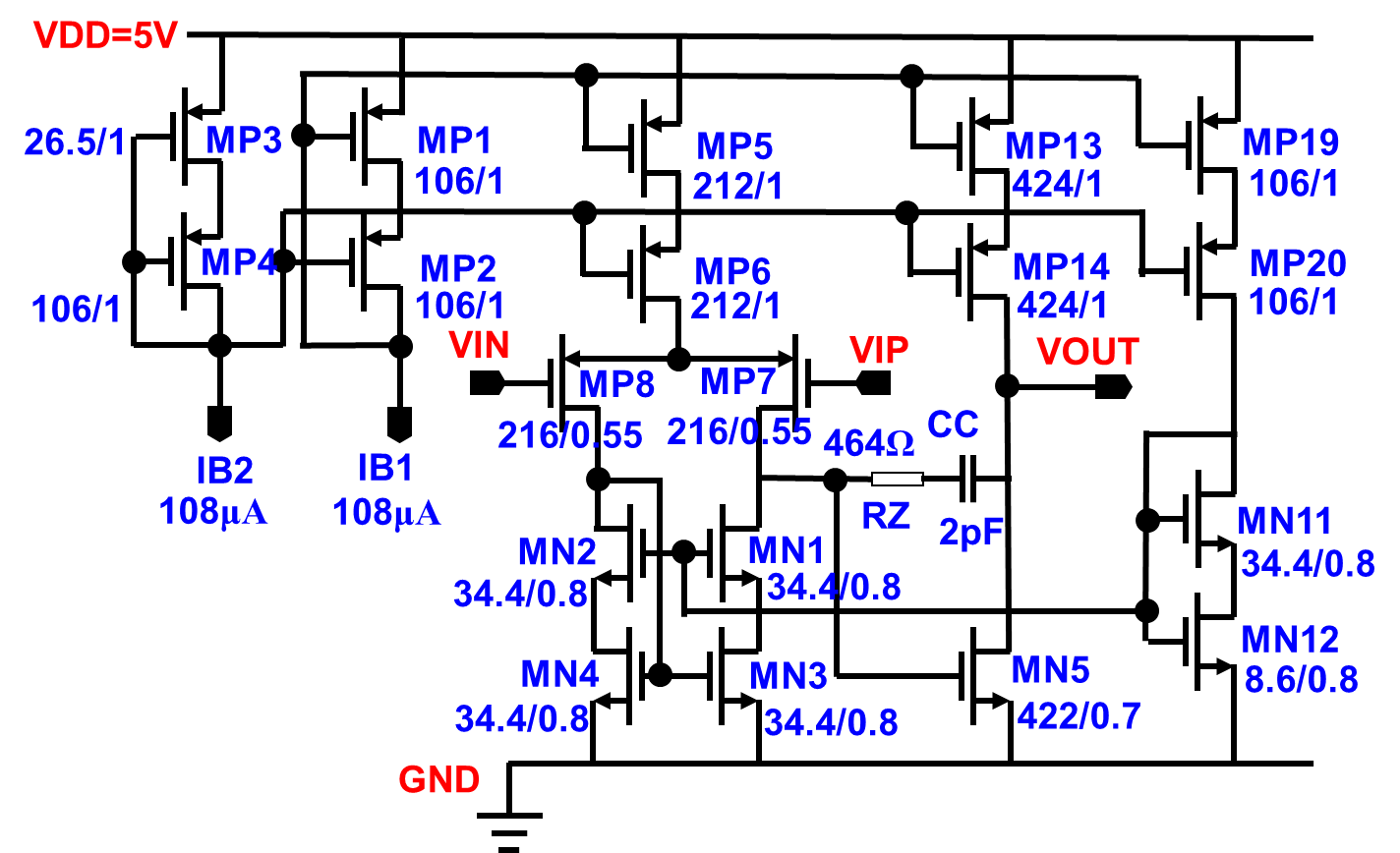

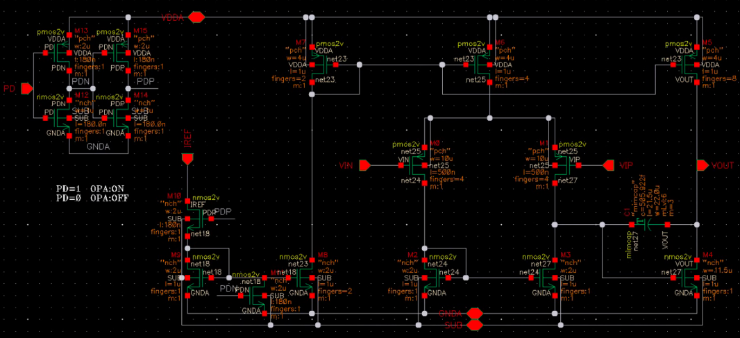

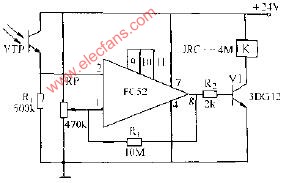

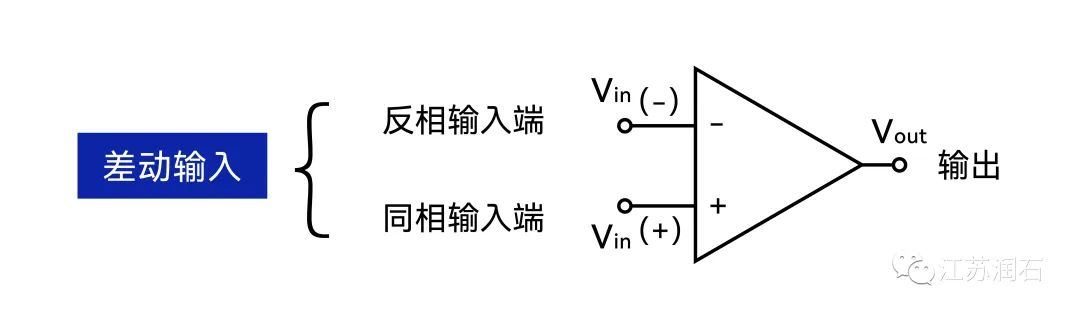

运算放大器采用图1所示的电路结构,电路中的电流源均采用共源共栅结构,可以获得较高的共模抑制比和电流复制精度。 其性能指标为增益带宽积GBW=100MHz,负载电容CL=2pF。 本设计采用的工艺库中NMOS的最小沟道长度为0.5μm,PMOS的最小沟道长度为0.55μm。

图1 二级运算放大器的电路结构

2 设计过程

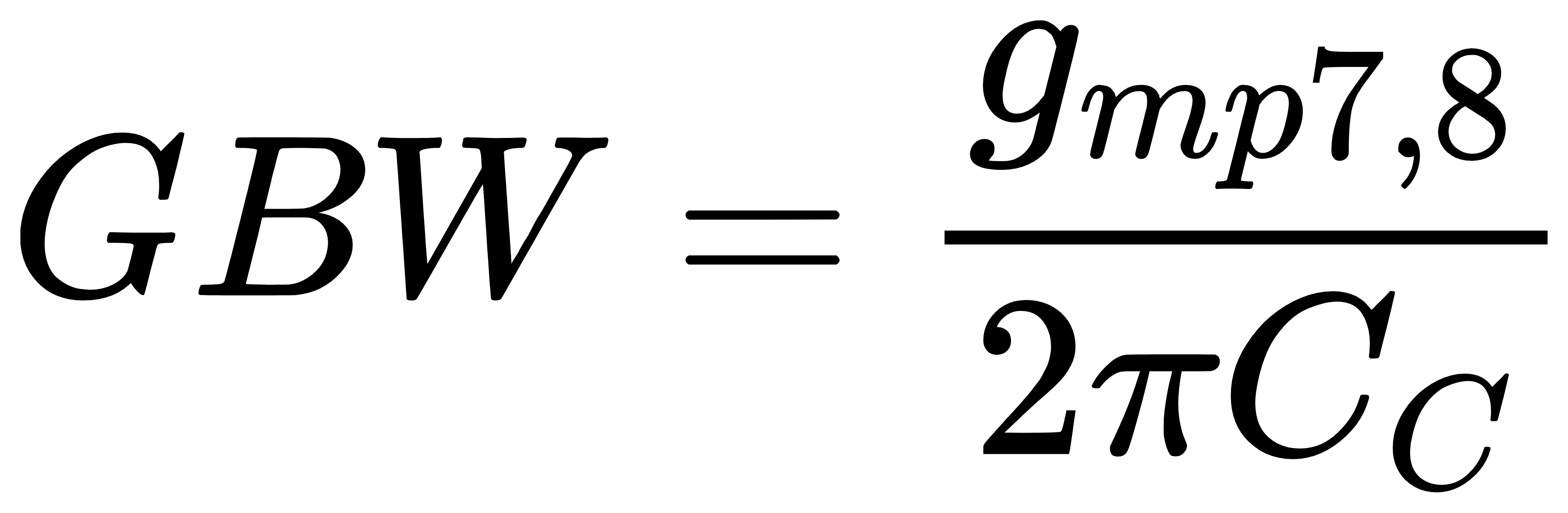

图1所示的运算放大器的增益带宽积

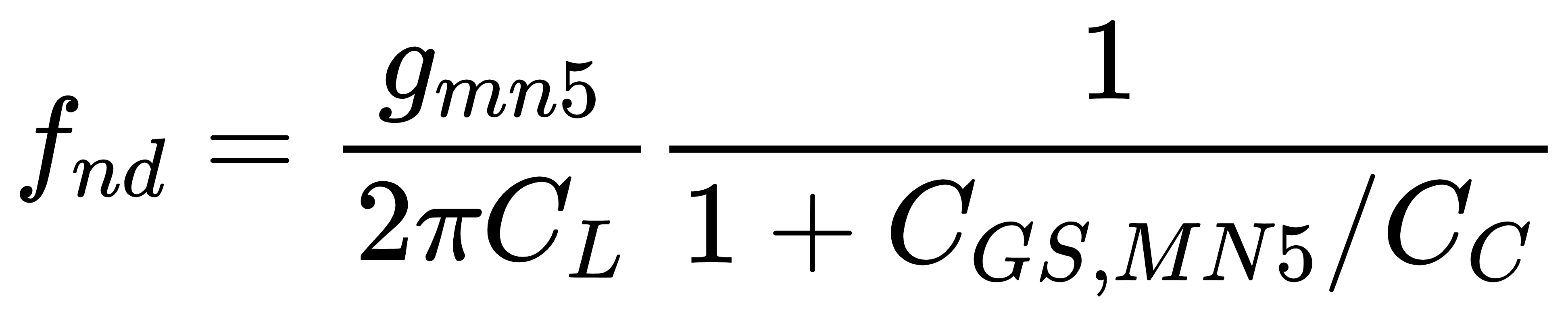

次主极点频率

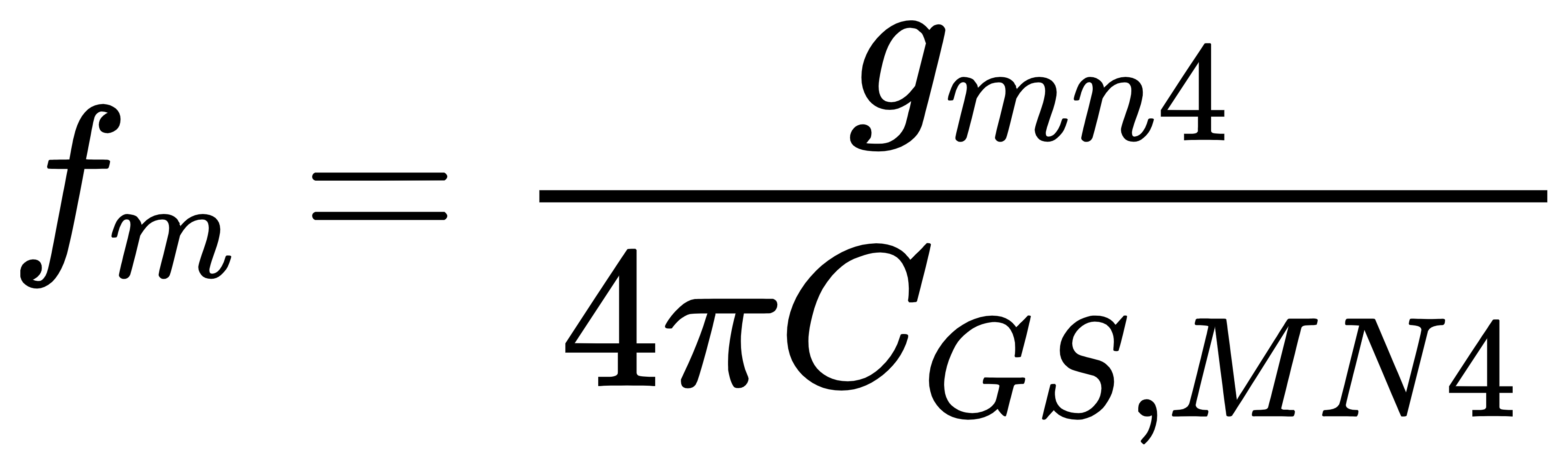

在第一级差分放大级的NMOS电流镜负载处引入了零极点对,极点频率为

零点在左半平面,其频率为2fm。

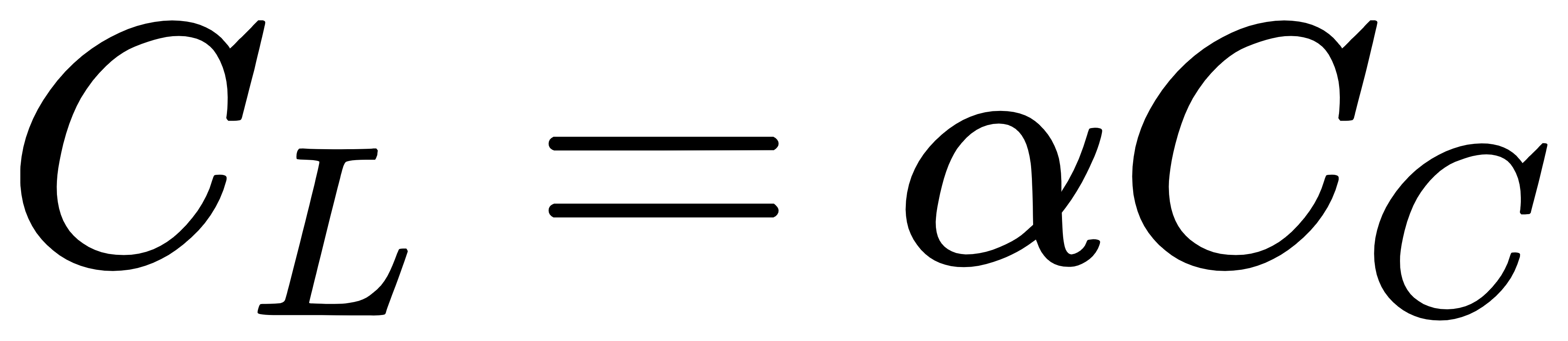

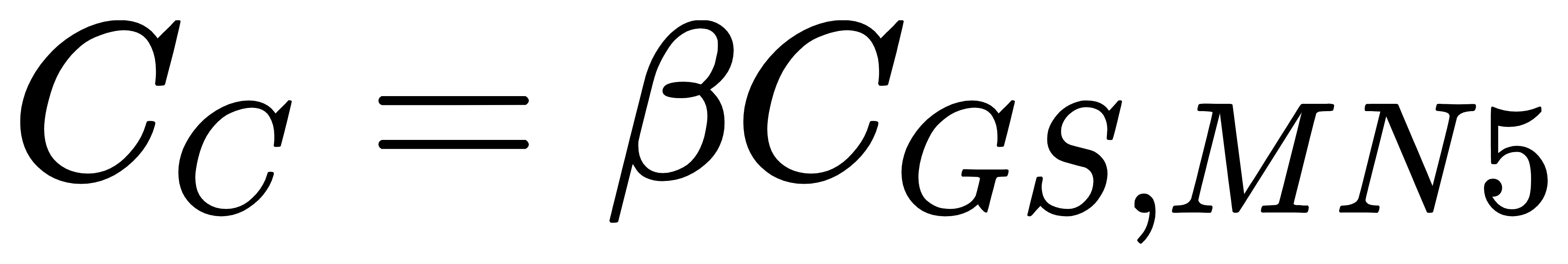

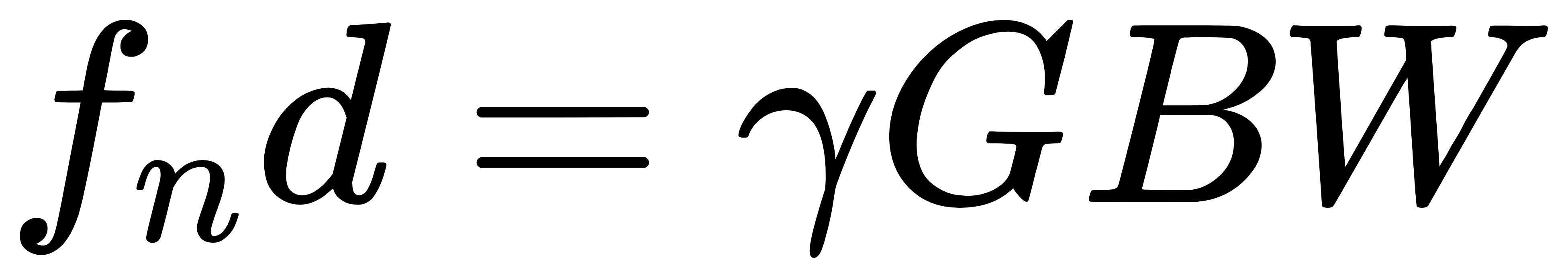

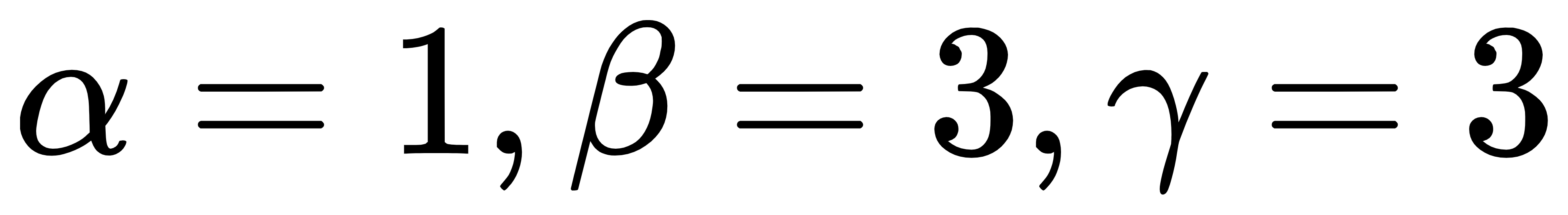

设有如下关系:

则可以取

2.1 确定MN5的L, W及ID

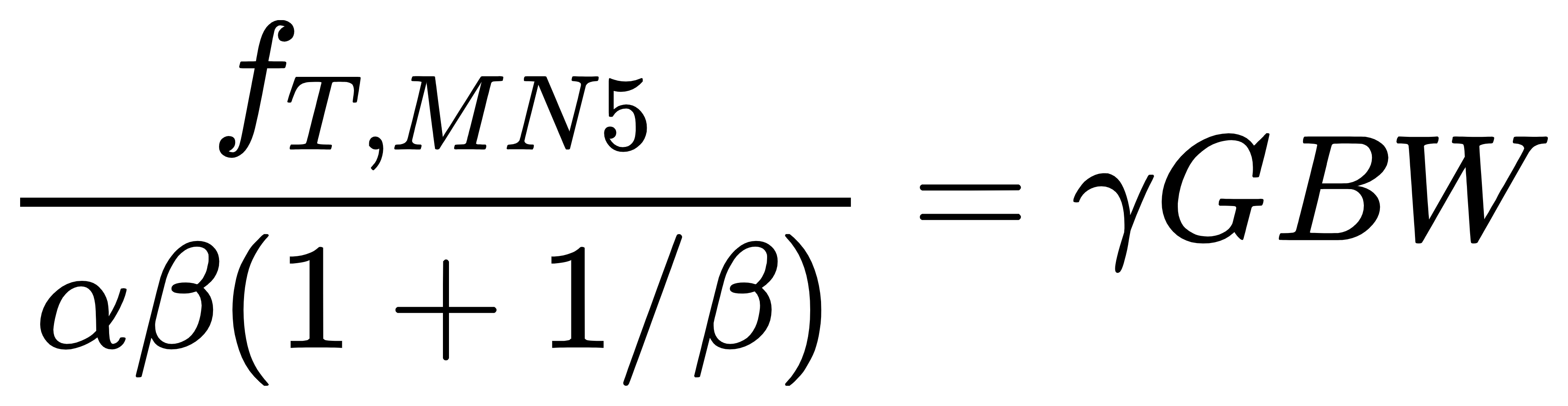

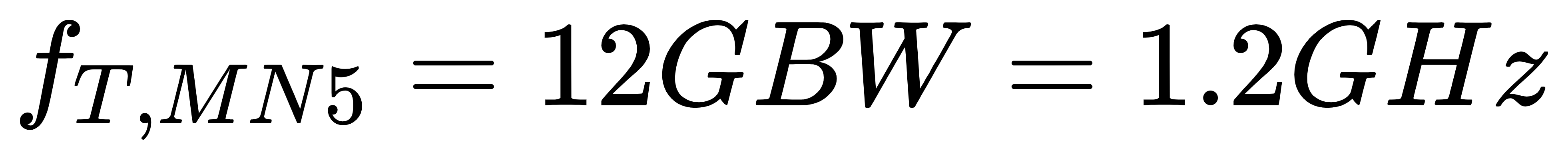

根据fnd的表达式和α、β、γ参数的定义可得

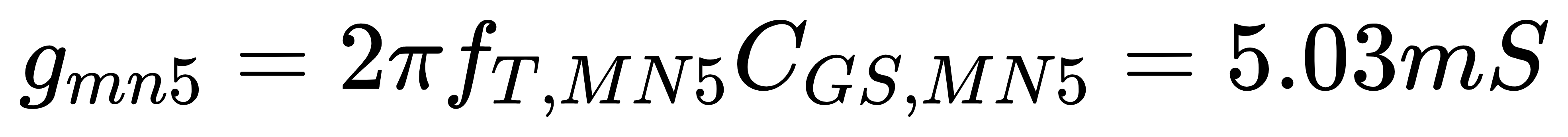

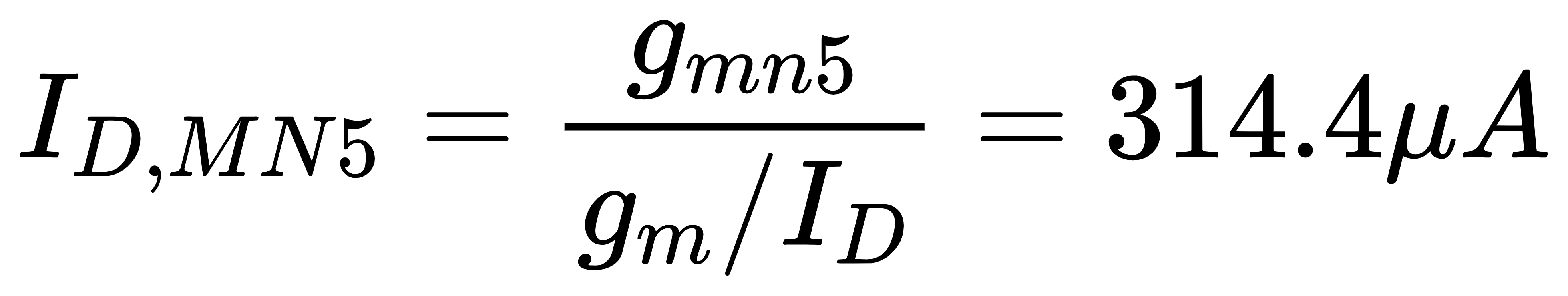

其中,fT,MN5为MN5晶体管的特征频率。 代入数据可得

且有

取gm/ID=16,可以得到

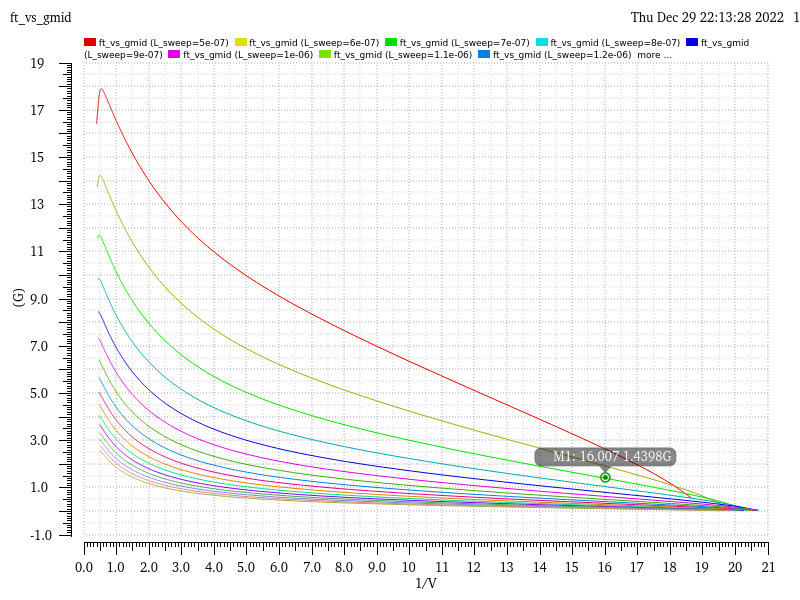

根据图2所示的fT与gm/ID的关系曲线,可以得到MN5的沟道长度为

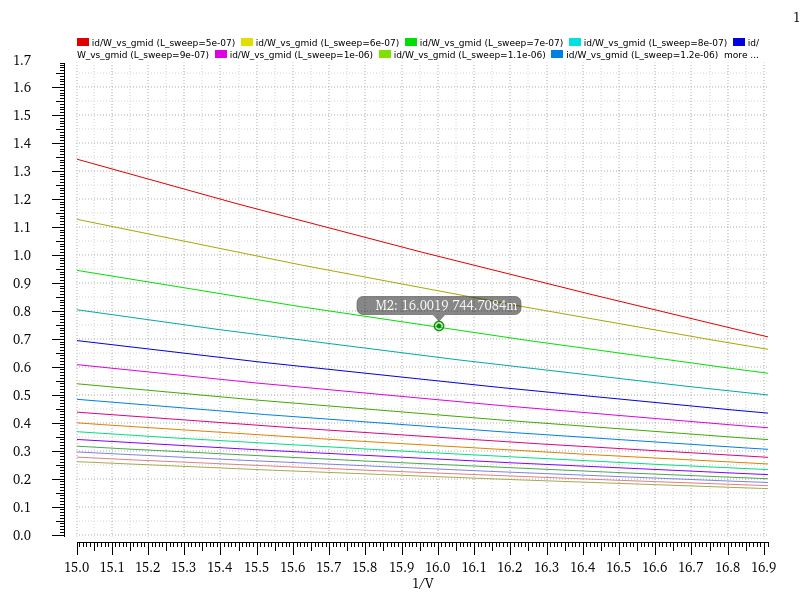

另外,根据图3所示的ID/W与gm/ID的关系曲线,可以得到MN5的沟道宽度为

图2 用于确定MN5沟道长度的fT-gm/ID曲线

图3 用于确定MN5沟道宽度的ID/W-gm/ID曲线

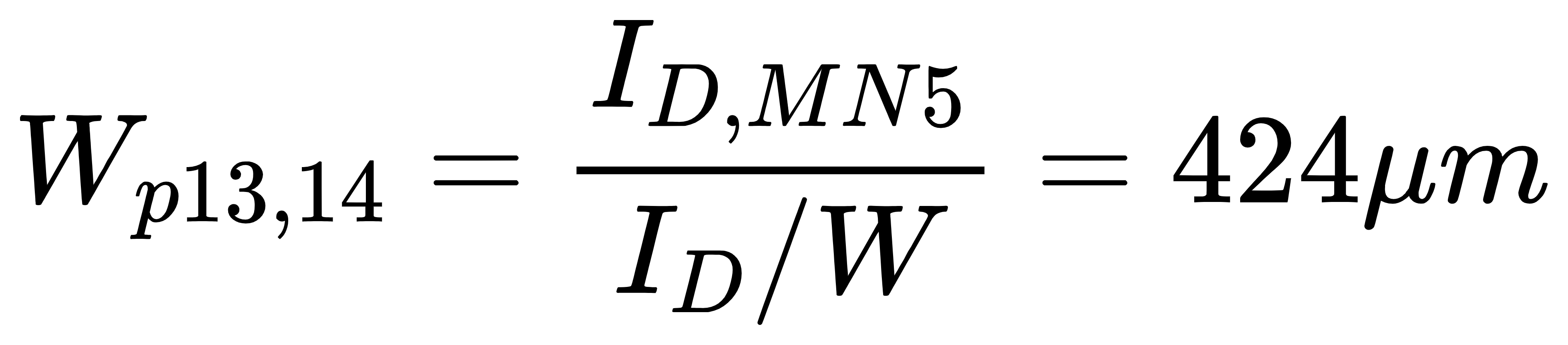

2.2 确定MP13和MP14的L及W

取所有PMOS电流源的gm/ID=10。 较小的gm/ID值有利于减小负载管的噪声和减小阈值电压失配引起的电流复制误差。 电路对于MP13和MP14的沟道长度没有严格的约束条件,可以选择沟道长度

根据图4所示的ID/W与gm/ID的关系曲线,可以得到

图4 用于确定MP13和MP14沟道宽度的ID/W-gm/ID曲线

2.3 确定MP7和MP8的L, W及ID

由GBW的表达式可以计算出MP7和MP8的跨导为

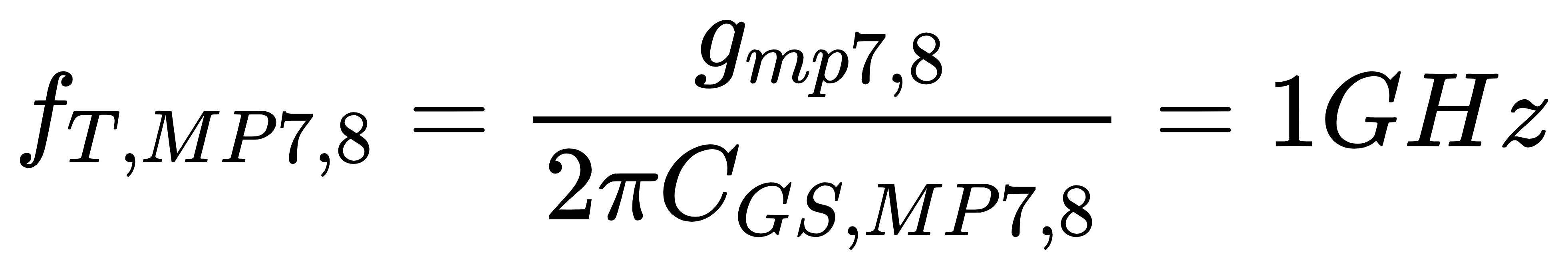

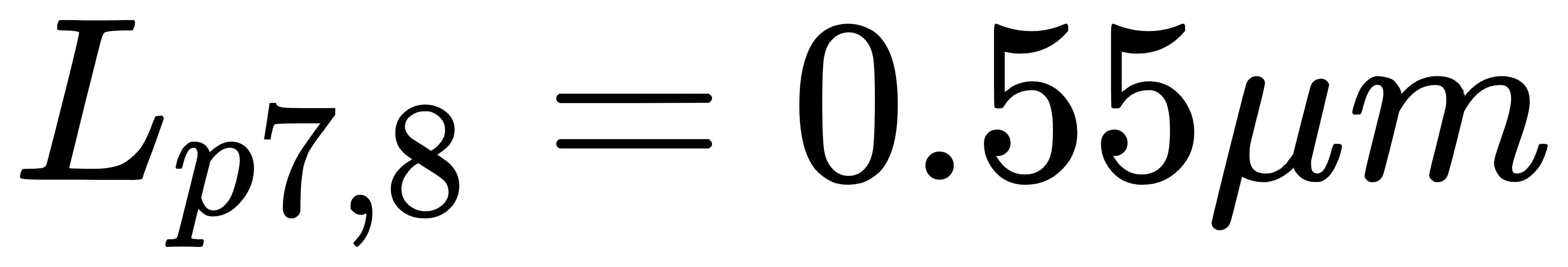

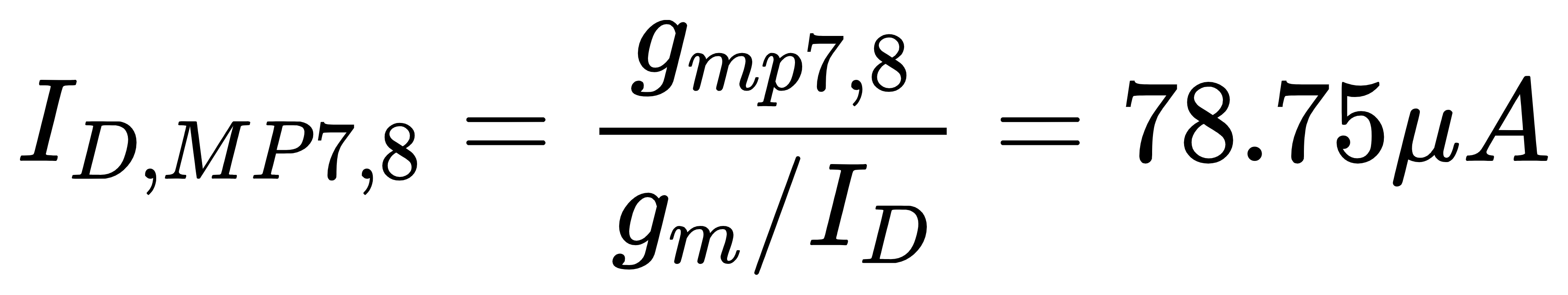

在运算放大器的单位负反馈应用中,由于输出端与反相输入端直接相连,使得CGS,MP8与CL并联,导致等效负载电容CL’=CL+CGS,MP8增大,增益带宽积和相位裕度减小。 为了减小CGS,MP8的影响,可以通过设计使得CGS,MP8<0.1CL。 取CGS,MP8=0.2pF,可以计算出MP7和MP8的特征频率为

取gm/ID=16,则根据图5所示的fT与gm/ID的关系曲线,可以得到MP7和MP8的沟道长度为

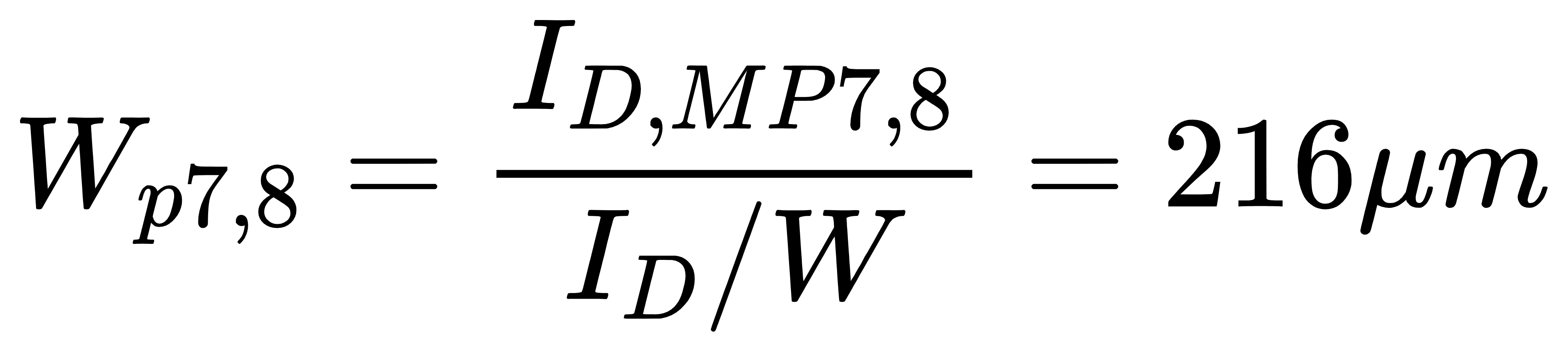

通过MP7和MP8的电流均为

根据图6所示的ID/W与gm/ID的关系曲线,可以得到MP7和MP8的沟道宽度为

图5 用于确定MP7和MP8沟道长度的fT-gm/ID曲线

图6 用于确定MP7和MP8沟道宽度的ID/W-gm/ID曲线

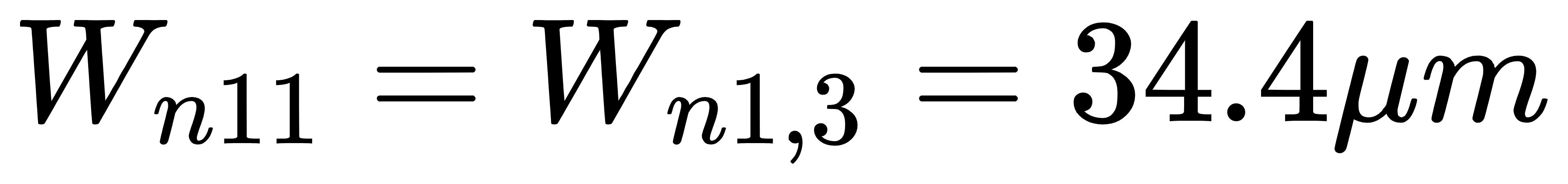

2.4 确定MN1~MN4的L及W

为了减小镜像零极点对对于运算放大器相位裕度的影响,可以将镜像极点频率设置到GBW的10倍处,即fm=10GBW。 据此,有

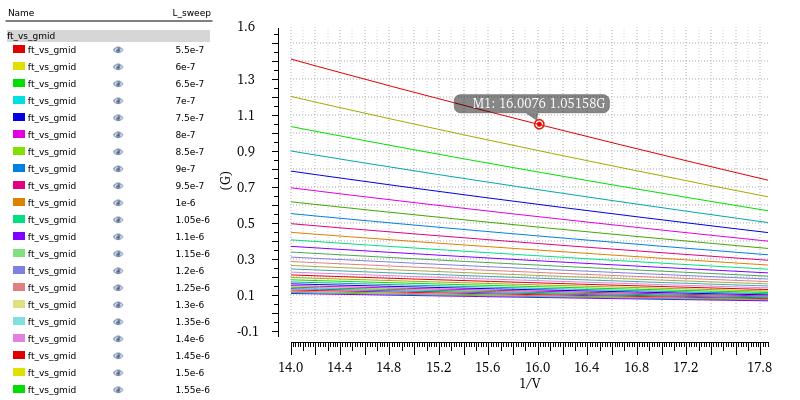

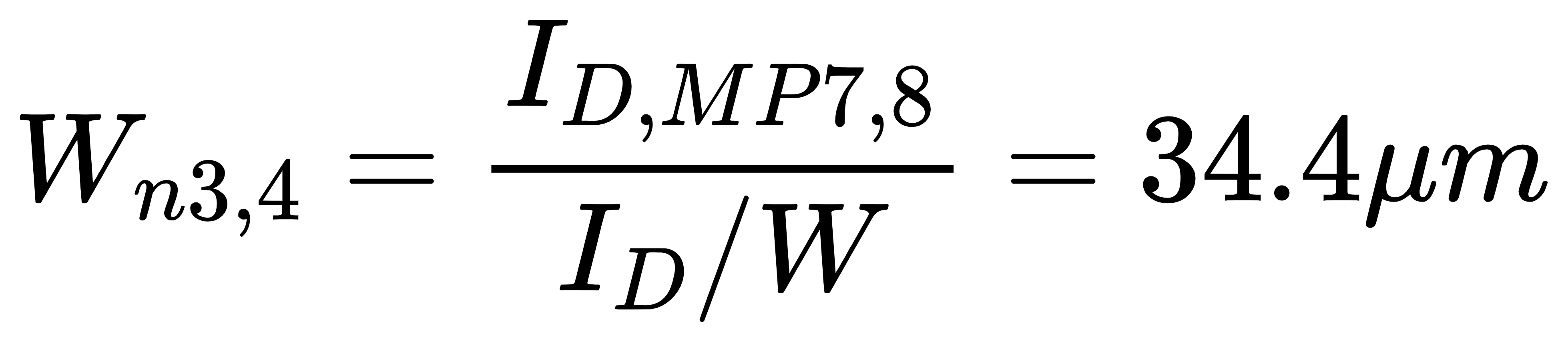

取gm/ID=10,根据图7所示的fT与gm/ID的关系曲线,可以得到MN3和MN4的沟道长度为

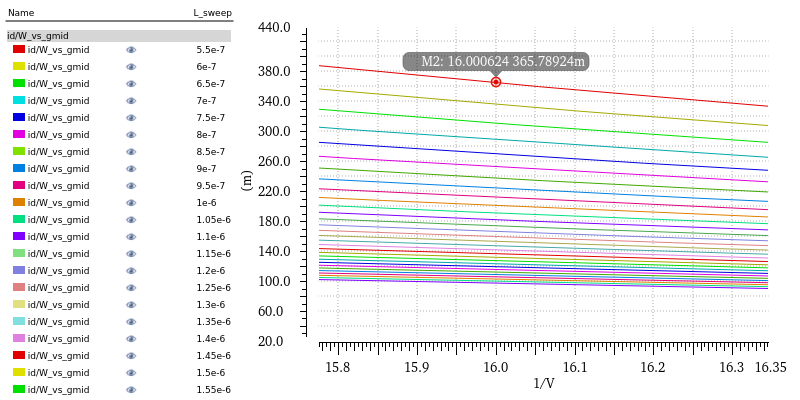

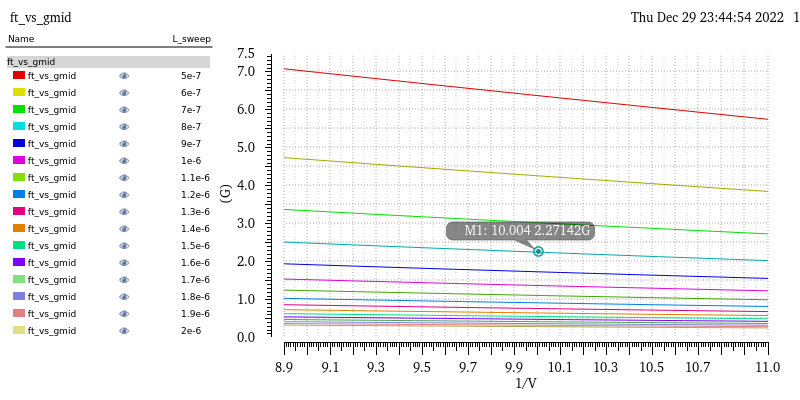

根据图8所示的ID/W与gm/ID的关系曲线,可以得到MN3和MN4的沟道宽度为

MN1和MN2的沟道长度和沟道宽度与MN3和MN4取相同值即可。

图7 用于确定MN3和MN4沟道长度的fT-gm/ID曲线

图8 用于确定MN3和MN4沟道宽度的ID/W-gm/ID曲线

2.5 确定MP5和MP6的L及W

MP5, 6的沟道长度取与MP13, 14相同的值,即

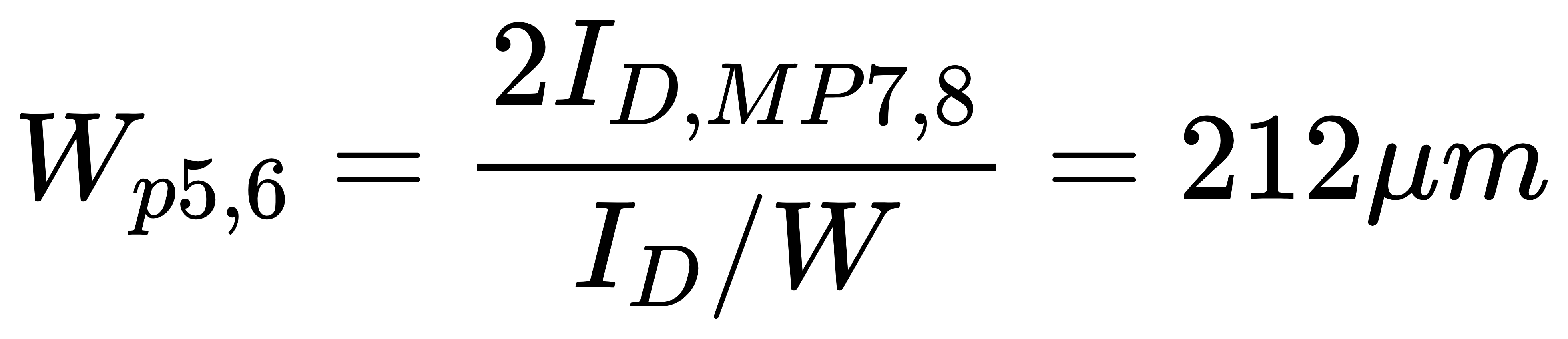

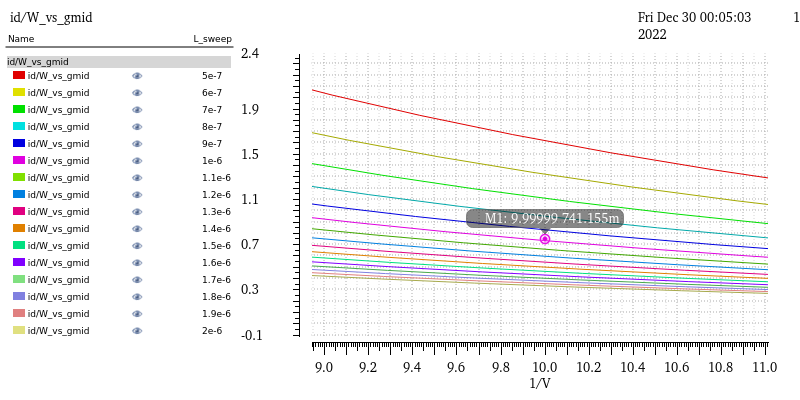

根据图9所示的ID/W与gm/ID的关系曲线,可以得到MP5和MP6的沟道宽度为

图9 用于确定MP5和MP6沟道宽度的ID/W-gm/ID曲线

2.6 确定偏置电路晶体管的尺寸

第一级差分对的尾电流源大小为ID,MP5=157.5μA,第二级的负载电流源大小为ID,MP13=314.4μA。 取IB1=IB2=78.75μA,则ID,MP5=2

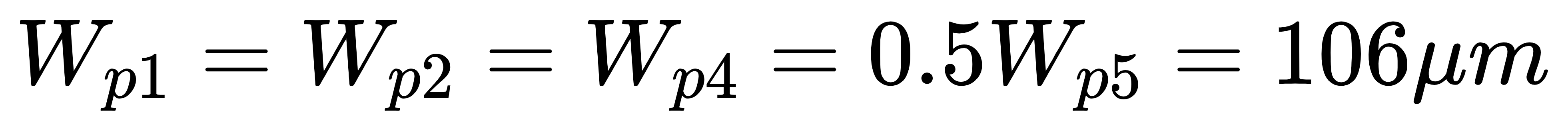

IB1,ID,MP13=4 IB1。 因此可以确定MP1~4的尺寸为

取ID,MP19=ID,MP7,8=0.5 ID,MP5=IB1,因此

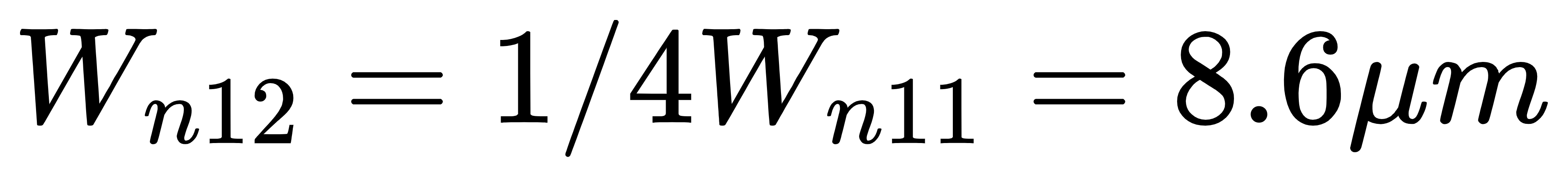

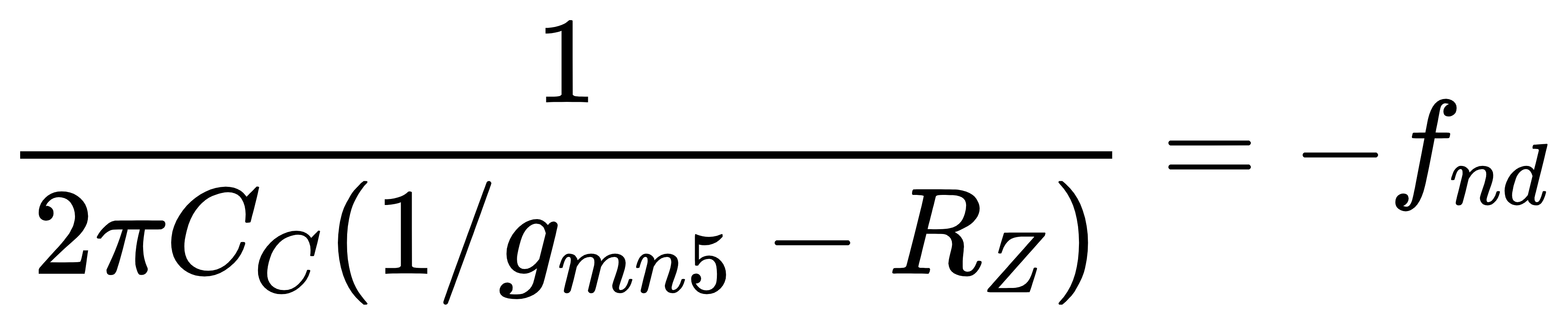

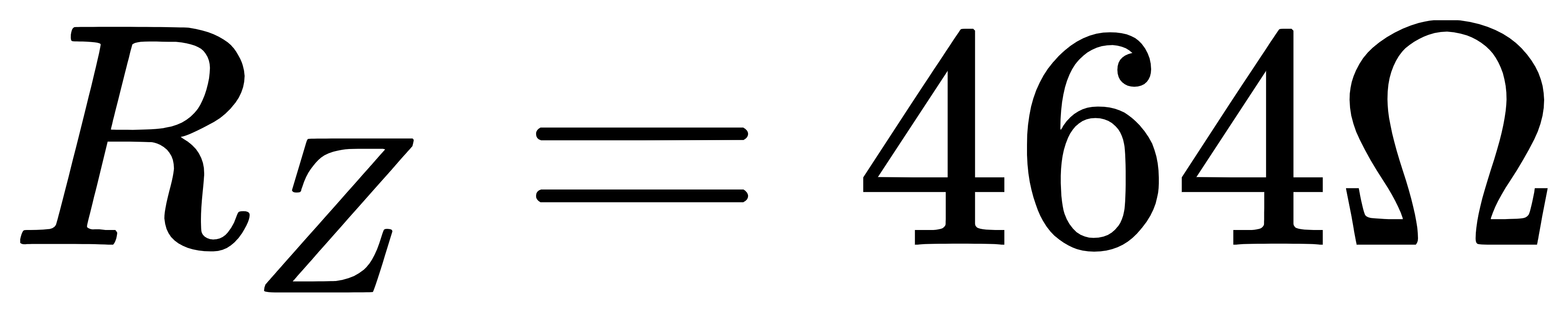

2.7 确定消零电阻RZ的大小

为了使消零电阻RZ可以将补偿电容CC引入的右半平面零点移动到左半平面,并且最好能够和次主极点相抵消,则有

代入数据可得

3 电路仿真

3.1 增益带宽积与相位裕度

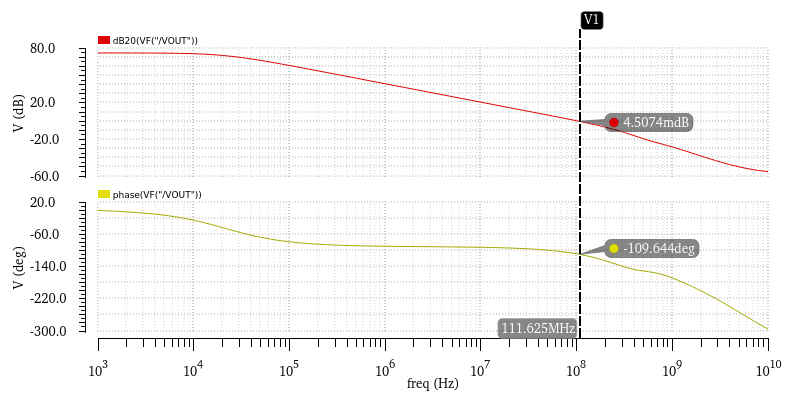

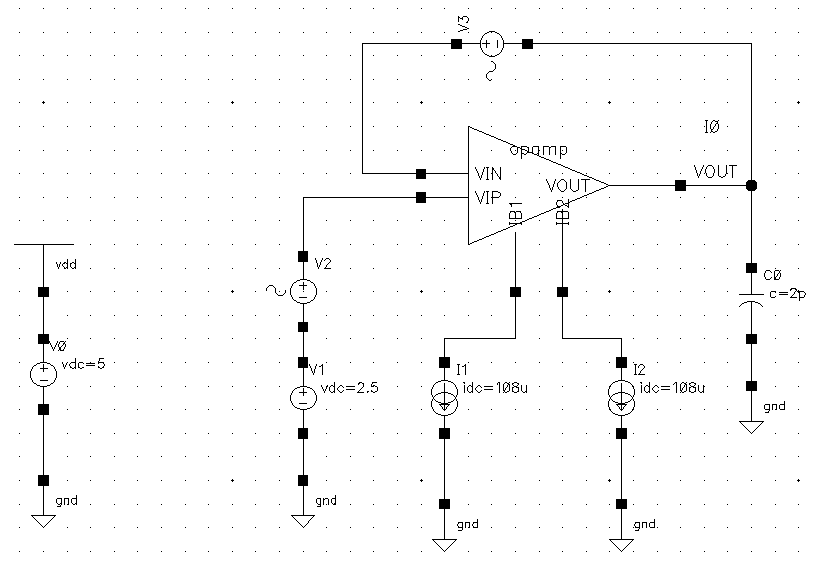

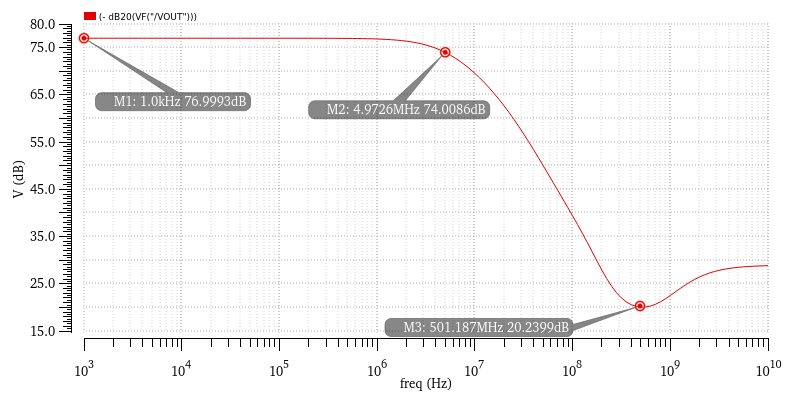

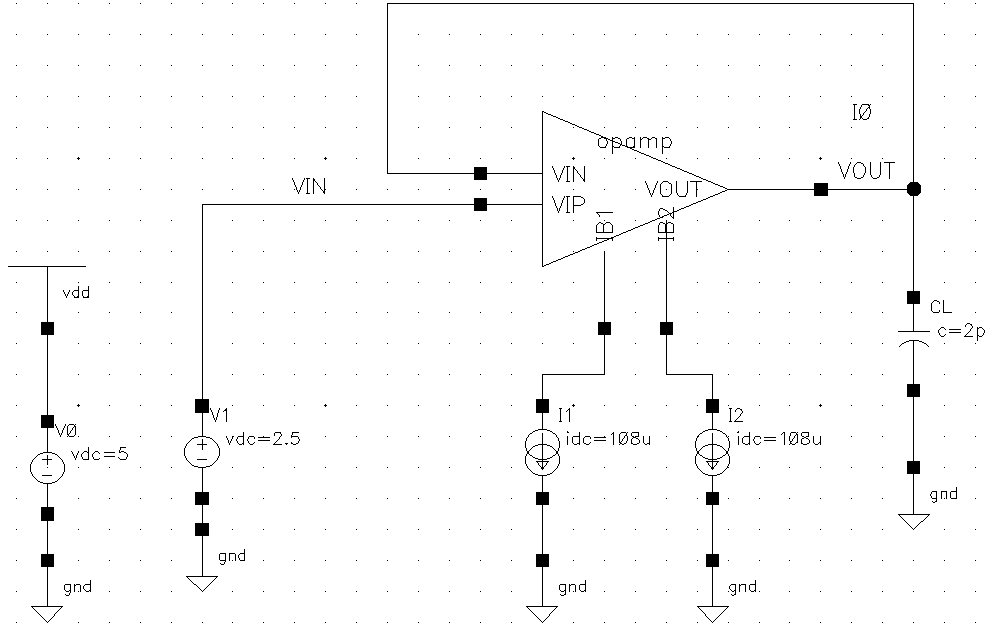

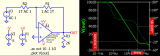

用于仿真GBW和PM的电路如图10所示,其中的运算放大器采用前文所设计的运算放大器,对其施加共模电压2.5V作为输入端的静态工作点电压,负载电容CL=2pF。 经过仿真,发现GBW只有82MHz,没有达到100MHz。 为此,将IB1和IB2提高至108μA。 仿真结果如图11所示,可以看出仿真结果为GBW=112MHz,PM=70˚,低频增益为75dB。

图10 用于仿真GBW和PM的电路图

图11 GBW和PM的仿真结果

3.2 共模输入范围

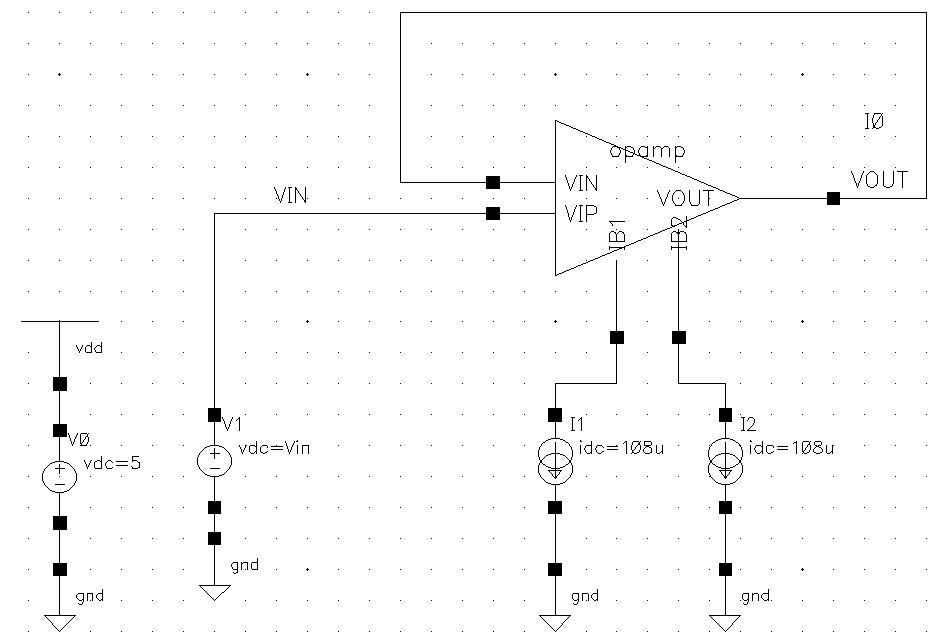

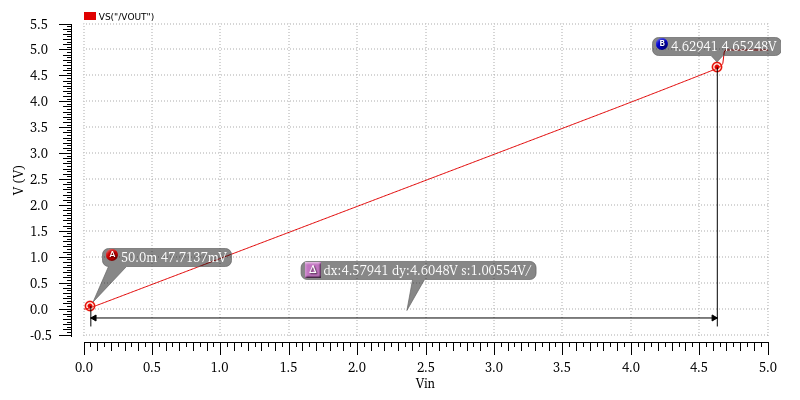

用于仿真共模输入范围的电路图如图12所示。 共模输入范围的仿真结果如图13所示,可以看出共模输入范围为0.05V至4.63V。 电压跟随器连接方式的运算放大器在此范围内可以展现出很好的电压跟随特性,其电压传输特性曲线的斜率为1。

图12 用于仿真共模输入范围的电路图

图13 共模输入范围的仿真结果

3.3 输出摆幅

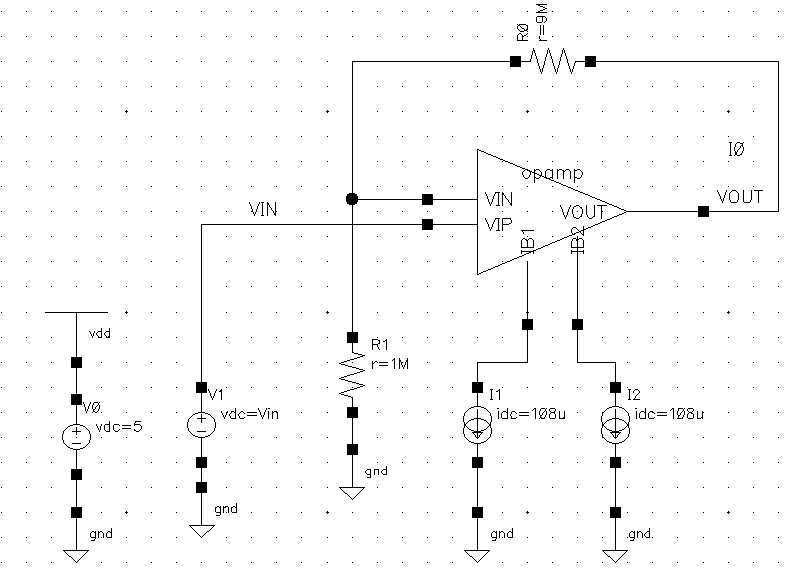

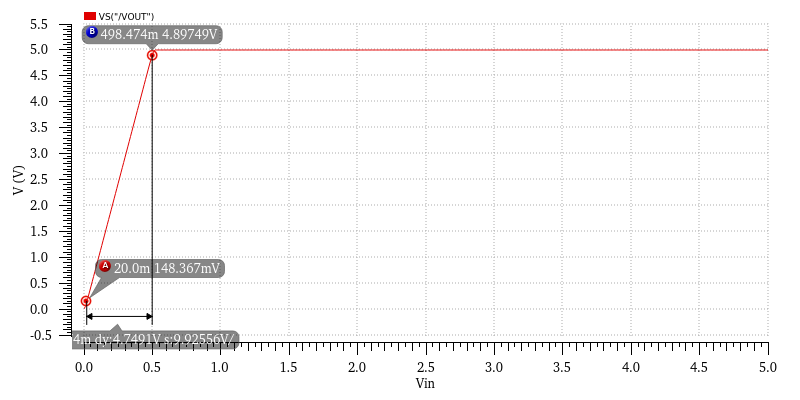

用于仿真输出摆幅的电路如图14所示。 在单位增益反馈结构中,电压传输曲线的线性受到共模输入范围的限制。 因此,若采用高增益反馈,传输曲线的线性部分与放大器输出电压摆幅一致。 图14采用增益为10的同相放大器。 输出摆幅的仿真结果如图15所示,可以看出输出电压摆幅为0.15V至4.9V。

图14 用于仿真输出摆幅的电路图

图15 输出摆幅的仿真结果

3.4 共模抑制比

用于仿真共模抑制比的电路如图16所示。 仿真结果如图17所示,可以看出低频时的CMRR=77dB; 在5MHz处CMRR下降3dB; 在1kHz至10GHz频段内,CMRR最小为20dB。

图16 用于仿真共模抑制比的电路图

图17 共模抑制比的仿真结果

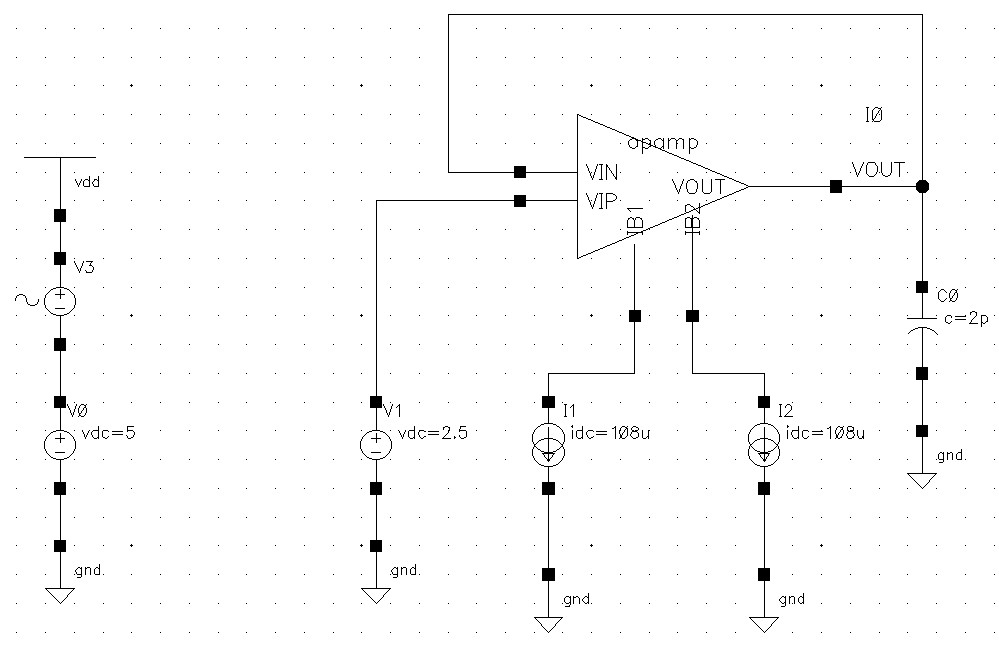

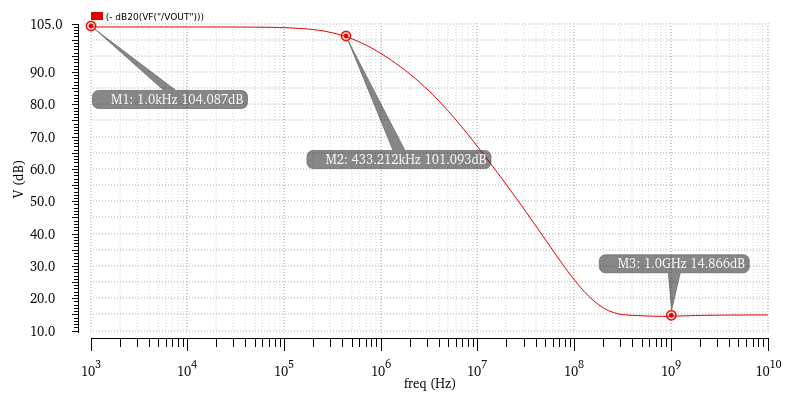

3.5 电源抑制比

用于仿真电源抑制比的电路如图18所示,在电源线上引入小信号电压波动。 电源抑制比的仿真结果如图19所示,可以看出,低频下的PSRR=104dB; 在433kHz处,PSRR下降3dB; 在1kHz至10GHz频段内,PSRR最小为15dB。

图18 用于仿真电源抑制比的电路图

图19 电源抑制比的仿真结果

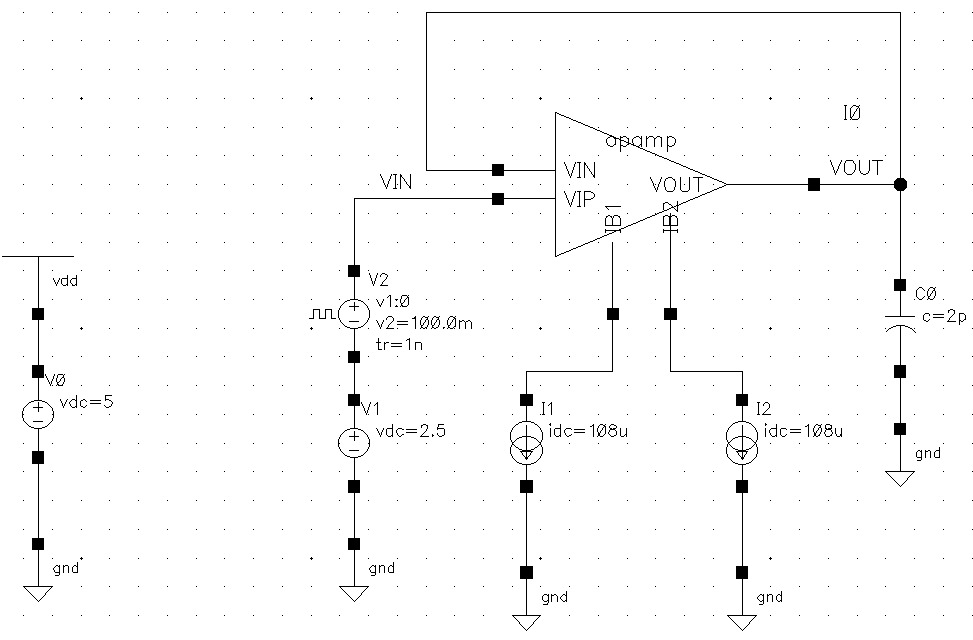

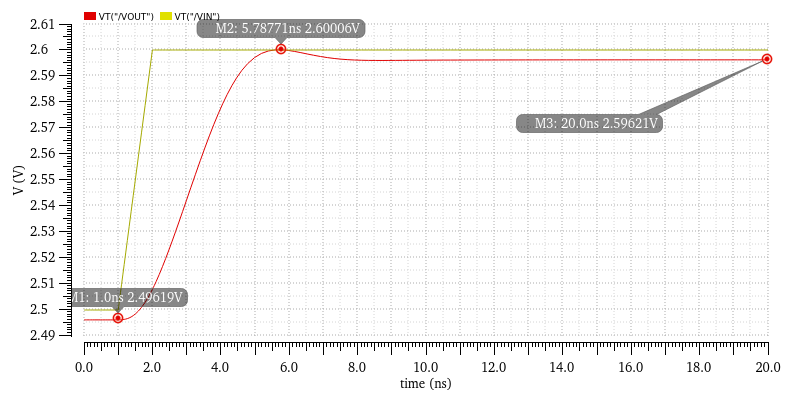

3.6 小信号建立特性

用于小信号建立特性仿真的电路图如图20所示,在输入端施加0.1V的阶跃小信号电压。 小信号建立特性的仿真结果如图21所示。 在图21中,黄色曲线为输入电压的波形,红色曲线为输出电压的波形。 从图21可以看出,峰值时间tp=5.8ns−1ns=4.8ns,最大超调σp=(2.600V−2.596V)/2.596V=0.15%,振荡次数N=1。

图20 用于仿真小信号建立特性的电路图

图21 小信号建立特性的仿真结果

3.7 等效输入噪声

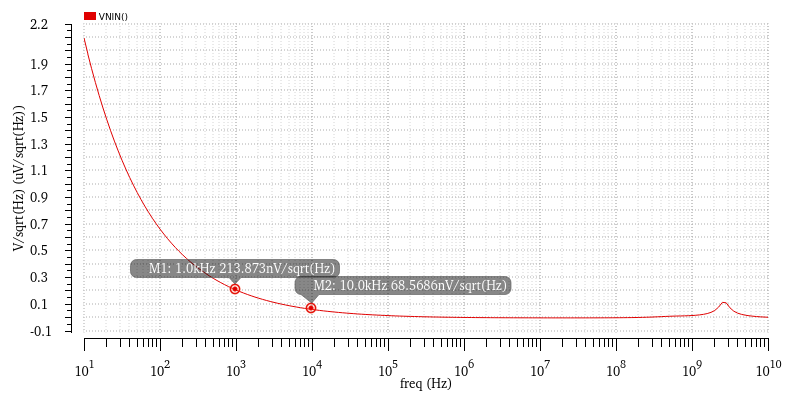

由于所设计的运算放大器输入端均为栅极,其输入电阻为无穷大,因此可以只考虑等效输入噪声电压,而忽略等效输入噪声电流。 用于仿真等效输入噪声的电路图如图22所示。 仿真结果如图23所示,可以看出,在1kHz处,等效输入噪声电压大小为214nV/√Hz; 在10kHz处,等效输入噪声电压大小为68nV/√Hz。

图22 用于仿真等效输入噪声的电路图

图23 等效输入噪声电压的仿真结果

3.8 非线性

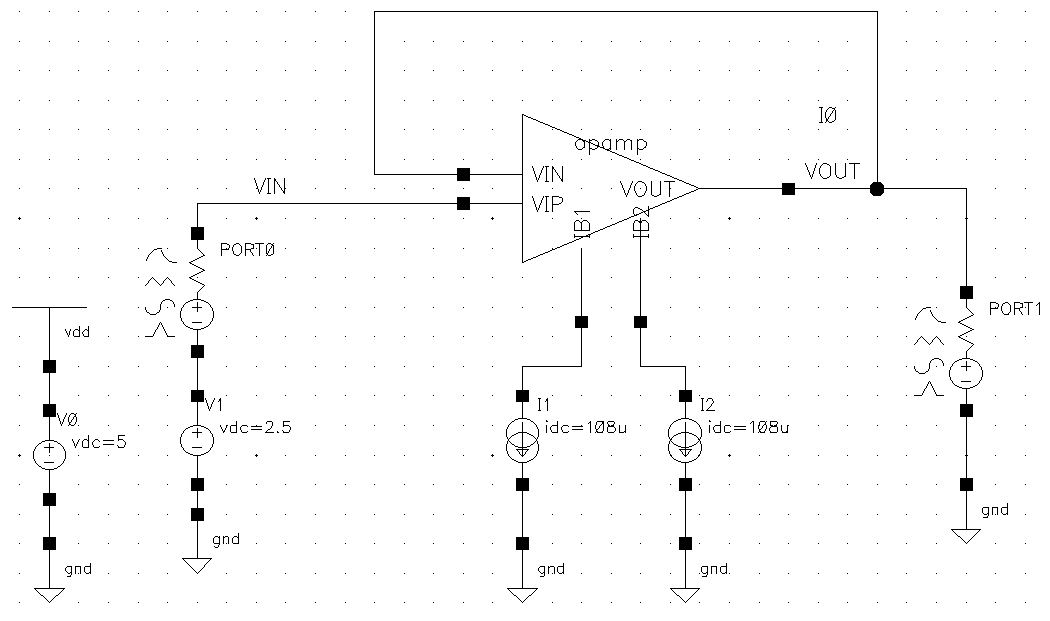

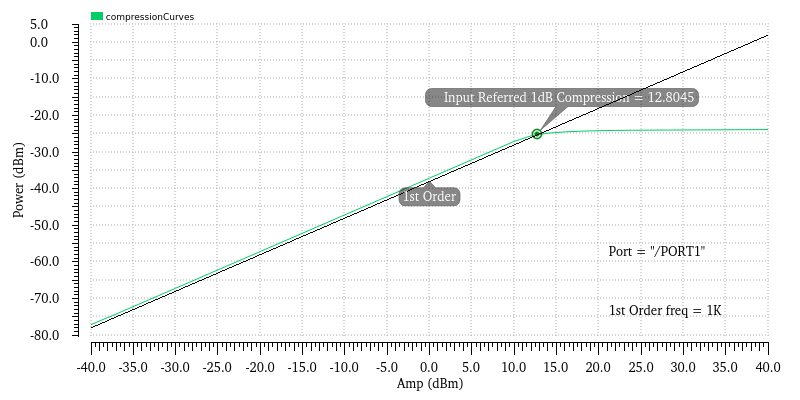

有许多性能指标可以反应电路的非线性,在这里选择输入1dB压缩点作为衡量非线性的指标。 用于仿真输入1dB压缩点的电路如图24所示,为单位增益负反馈结构,其中输入端口PORT0的频率设为1kHz,源阻抗设为50Ω,产生正弦波信号; 输出端口PORT1的阻抗设为1MΩ。 仿真结果如图25所示,可以看出输入1dB压缩点为+12.8dBm。

图24 用于输入1dB压缩点的电路图

图25 输入1dB压缩点的仿真结果

4 电路参数汇总

将第2节中计算所得的电路参数,以及在3.1节中调整的偏置电流IB1和IB2汇总到图26中。

图26 电路最终版本

电子发烧友App

电子发烧友App

评论