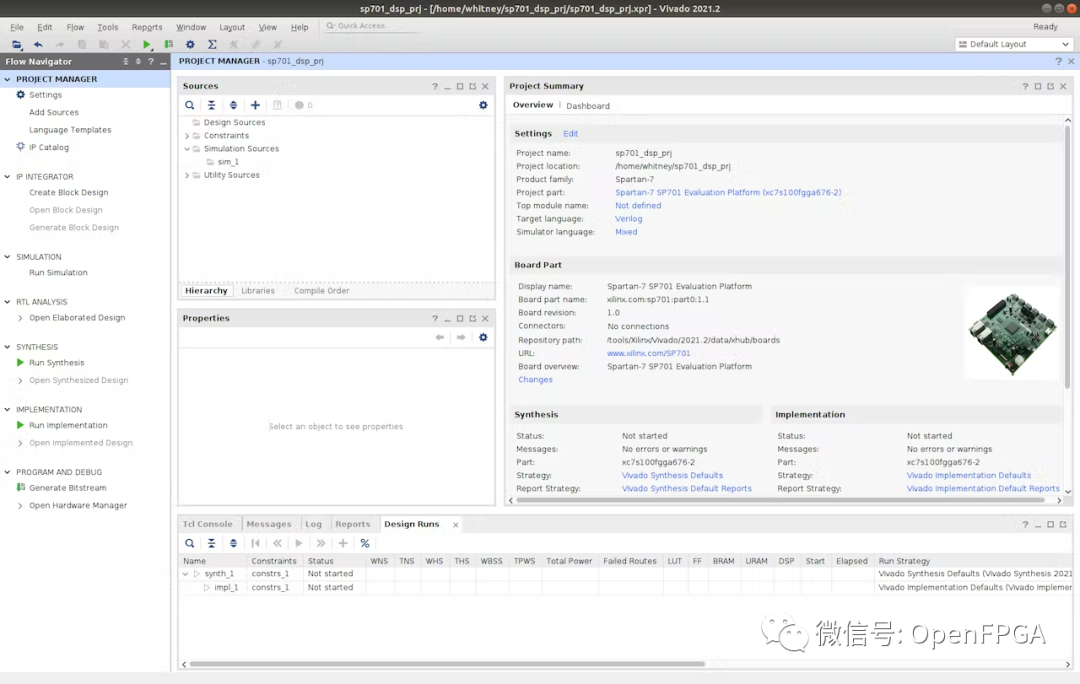

作者:Mculover666 1.实验目的 用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核 2.实验步骤 2.1.创建一个新的项目 2.2.调用Create

2020-12-21 16:34:14 3088

3088

的数据流标识符。xilinx封装的ip中没有此信号。 9.TDEST 用于提供路由信息,xilinx封装的ip中没有此信号。 10.TUSER AXI4协议留给用户自定义的。xilinx封装的ip中没有

2021-01-08 16:52:32

特定参数化视频IP配置参数在第3章的IP参数化中描述。AXI4S接口视频协议的具体参数在Table 1-3中列出。Table 1‐3: AXI4-Stream 特定参数化

2022-11-14 15:15:13

个恒定的6个32位字,所以必须注意帧数据或控制数据的缓冲区填满的条件。防止无序状况。“我还说在AXI4-Stream接口中“数据是以数据包的形式传输而不是连续流”。最大9Kb“帧”大小是否也适用于通过AXI4-Stream接口发送的最大“数据包大小”?问候。

2020-05-25 09:37:36

嗨, 当我在XPS中创建自定义AXI外设时,AXI ID(ARID,AWID)在生成的包装器中不可用。我如何获得这些ID?谢谢。以上来自于谷歌翻译以下为原文Hi, When I create a

2019-03-21 09:00:19

、 FIR(有限冲激响应)中的有限是冲激响应是有限的意味着在滤波器中没有发反馈.。 4、 FIR 滤波器外还有一类 IIR(无限冲激响应,Infinite Impulse Response),IIR

2011-09-24 16:05:53

相位,就是不同频率分量的信号经过FIR滤波器后他们的时间差不变。这是很好的性质。 另外有限的单位响应也有利于对数字信号的处理,便于编程,用于计算的时延也小,这对实时的信号处理很重要。图3 在

2016-08-08 08:49:32

,在这种结构中,由于运算过程中对序列的舍入处理,这种有限字长效应有时会引入寄生振荡。相反,FIR滤波器主要采用非递归结构,不论在理论上还是在实际的有限精度运算中都不存在稳定性问题,运算误差也较小。此外,FIR滤波器可以采用快速付里叶变换算法,在相同阶数的条件下,运算速度可以快得多。

2018-03-12 13:21:07

数字滤波器广泛应用于硬件电路设计,在离散系统中尤为常见,一般可以分为FIR滤波器和IIR滤波器,那么他们有什么区别和联系呢。FIR滤波器定义:FIR滤波器是有限长单位冲激响应滤波器,又称为非递归型

2019-06-27 04:20:31

数字滤波器的类型有FIR(有限长冲击与IIR(无限长。离散数字系统中,滤波器的表述为差分方程。FIRFIR基本特性:FIR 滤波器永远是稳定的(系统只有零点);FIR 滤波器的冲激响应是有限长序列

2021-08-17 06:19:17

第一个问题的基础上,我是设置unsigned还是signed?3、滤波器的设计,我要给他什么样子的输入,仿真看得出什么样子的结果?部分代码如下

2017-05-09 14:18:17

一、混响reverb效果1、实现的经典Schroeder混响模型,4个梳状滤波器(C1、C2、C3、C4)+2个全通滤波器(A1、A2)组合而成。2、实现较为复杂的Moorer混响模型,结构如下

2021-08-17 09:24:44

嗨,我已经创建了一个带有IP-Core的硬件设计。但它不能正常工作。对于我提到的调试问题,我创建了一个IP-Core,然后通过AXI Stream。所以我可以检查我的IP-Core是否不起作用

2020-04-14 09:25:10

AXI4-Streamslave接口上TDATA信号的宽度(以字节为单位)。 AXI4-Stream主接口TDATA宽度是此值乘以从属接口数参数。此参数是一个整数,可以在0到(512 /从站接口数)之间变化。设置为0以省略

2020-08-20 14:36:50

你好,大家好。我正在使用EMI14.4和xc6v315t。我正在尝试模拟IP CORE.It的axi4-stream interconnect.I配置ip为6siand 4mi。但是当我用ismI模拟它时发现s_tready很低,有什么问题?

2020-06-18 15:08:59

对于fir滤波器,已经在前面的文章中记录了仿制DIY&关于MATLAB中滤波器设计工具的使用心得记录),其设计和实现都非常简单。如果在嵌入式系统中可以满足且有必要实时iir运算,那么

2021-12-22 08:29:40

你好,我如何启用自定义IP的中断。我使用vivado HLS生成了IP。中断线连接到ZYNQ的中断端口。以下是设备树{amba_pl:amba_pl {#address-cells

2020-05-01 16:46:48

现在我在vivado中做了一个基于axi总线测量频率的ip核,不知道在sdk中怎么读出频率计数值,`timescale 1ns / 1ps

2019-07-22 17:16:26

你好专家当我在XPS 14.6中的Create或Import Peripheral ...向导之后添加一个简单的自定义IP时,它不会显示在Project Local PCores列表中。但是,我

2020-03-18 10:22:22

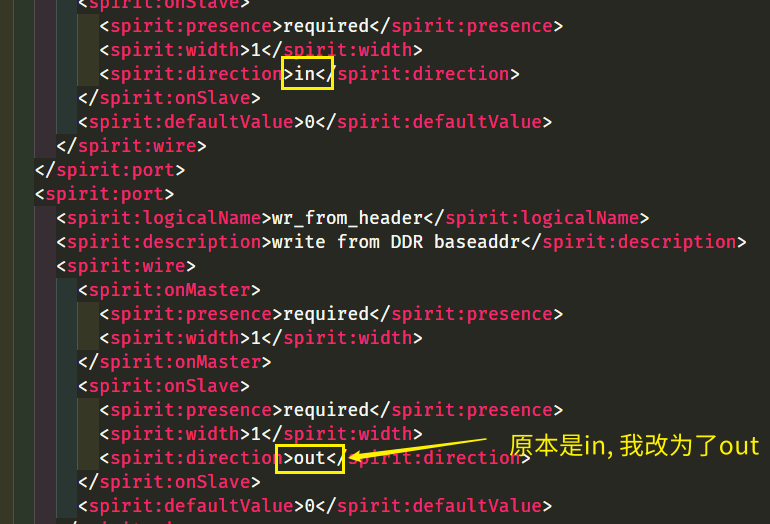

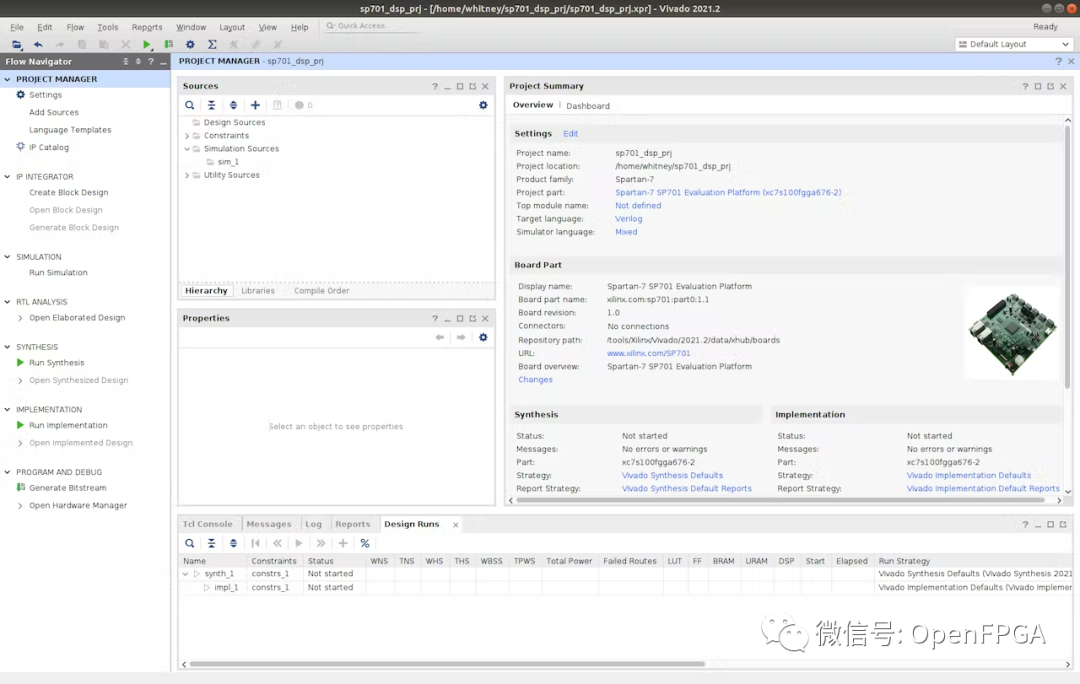

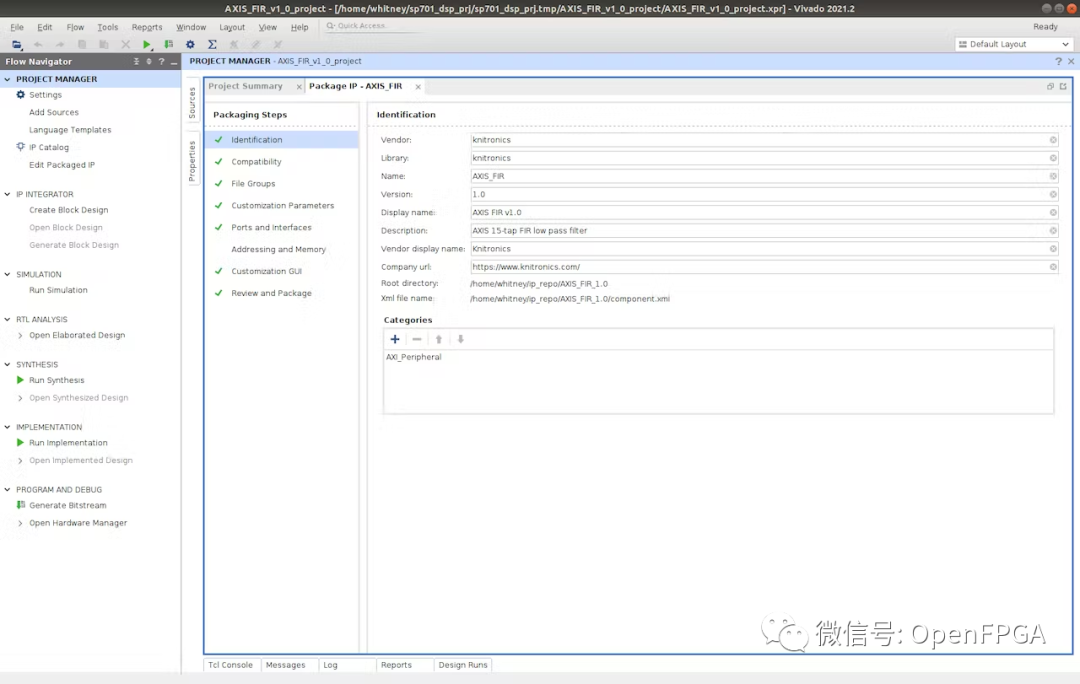

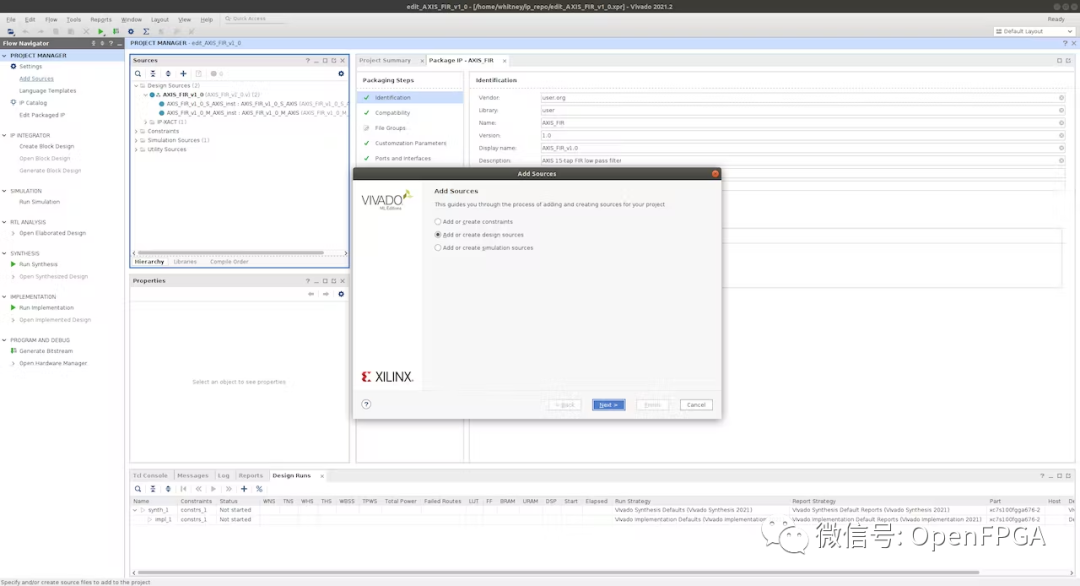

1、构建自定义AXI4-Stream FIR滤波器 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

2022-11-07 16:07:43

任何一个短缺这个问题。我尝试了很多,但无法在超级终端上获得结果。我已经通过fsl连接了4个microblaze,我测试我的设计,它的工作,fsl连接我检查它是否正常工作。但当我连接自定义IP与单个微型激光器时,我无法在超级终端上获得输出。所以请帮助我。

2020-03-11 09:59:27

开始,该装饰器支持在ArkTS卡片中使用。

装饰器使用说明

自定义组件内自定义构建函数

定义的语法:

@builder MyBuilderFunction() { ... }

@Builder

2023-09-26 16:36:23

和PCIE之间有什么联系,敬请关注我们的连载系列文章。在本篇文章中暂时先不讲解AXI4协议,先来分享例化AXI4的自定义IP核详细步骤。一、 新建工程为了节省篇幅,新建工程部分就不详细讲解,以下为我们

2019-12-13 17:10:42

makefile 文件。本文将介绍如何在 RT-Thread Studio 中构建工程前,执行用户自定义命令。1.右键工程,选择属性2.在 C/C++ 构建中,选择构建步骤:3.在构建前步骤,命令下添加用户自定义

2022-03-24 15:15:34

到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。 PS与PL内部通信(用户自定义IP)先要自定义一个AXI

2018-01-08 15:44:39

ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果一、前言 在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问

2020-04-23 11:16:13

sopc builder中添加自定义ip,编写自定义ip核的时候, avalon接口信号:clk、rst

2013-11-26 11:11:22

请教各位大师,quartus ii 中调用fir数字滤波器IP核,可不知道如何设置参数,比如如何设置滤波器的系数

2013-11-23 20:54:41

zynq的PS如何向一个基于AXI4-FULL协议的自定义IP批量传输数据?

2017-02-22 12:05:35

/3946208905)对正点原子FPGA感兴趣的同学可以加群讨论:876744900 6)关注正点原子公众号,获取最新资料第八章自定义IP核-呼吸灯实验在Vivado软件中,我们可以很方便的通过创建和封装IP向导

2020-10-17 11:52:28

的方式来自定义IP核,支持将当前工程、工程中的模块或者指定文件目录封装成IP核,当然也可以创建一个带有AXI4接口的IP核,用于MicroBlaze软核处理器和可编程逻辑的数据通信。本次实验选择常用的方式

2020-10-19 16:04:35

Vivado软件中,通过创建和封装IP向导的方式来自定义IP核,支持将当前工程、工程中的模块或者指定文件目录封装成IP核,当然也可以创建一个带有AXI4接口的IP核,用于PS和PL的数据通信。本次实验

2020-09-09 17:01:38

FIR滤波器如何定义?为什么要使用FIR滤波器?

2021-04-06 07:48:45

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

(不确定如果我连接它正确,请参阅附加的图片)。但是,要读取模块的输出,我需要一个AXI4Stream接口。在EDK中,我找不到AXI4Stream IP,或者可能是我之前没有使用过edk,之前,我

2019-02-28 13:47:30

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

基于FPGA的FIR滤波器IP仿真实例 AT7_Xilinx开发板(USB3.0+LVDS)资料共享 腾讯链接:https://share.weiyun.com/5GQyKKc 百度网盘链接

2019-07-16 17:24:22

DSPBuilder设计了一个4阶FIR滤波器,并用QuartusII进行硬件仿真,仿真结果表明设计FIR滤波器的正确性。同时使用IPCore开发基于FPGA的FIR数字滤波器,利用现有的IPCore在FPGA器件上实现滤波器设计。

2012-08-11 15:32:34

CyPress .FoMU/PSOC-3-架构/DigialFieldButter,它解释了如何做到这一点,但是我在我的自定义浮点滤波器系数(介于1和1之间)转换到FIL文件所需的UTI32 HEX值

2019-01-22 12:58:21

32,执行下面代码的前两行即可。第3~4行则是获取agent的读写深度,可以以此确认前面设置的读写深度是否有效。2.2自定义ready信号自带memory model的slave vip可以在

2022-10-09 16:08:45

大家好,我正在两个时钟域之间穿过AXI4-Stream,并尝试使用AXI4-Stream时钟转换器核心,使用tkeep端口但是在合成时它被Vivado 2015.2在实例化时删除了!这是综合警告

2020-05-08 08:56:14

我有SP605& ML506 Xilnx开发板。我想从FPGA驱动CH7301芯片。我正在寻找一些帖子或应用笔记,可以帮助我把这两件事放在一起。我一直在关注核心AXI4-Stream到视频

2020-03-20 09:04:51

此示例显示如何设计低通FIR滤波器。这里介绍的许多概念可以扩展到其他响应,如高通,带通等。FIR滤波器被广泛使用,因为它们具有强大的设计算法,以非递归形式实现时的固有稳定性,可以轻松实现线性

2018-08-23 10:00:16

嗨,我开始使用Vivado了。我正在尝试配置从Dram读取数据的自定义IP,处理它们然后将结果发送到Bram控制器。我想过使用AXI主接口制作自定义IP。但是,我不知道将AXI主信号连接到我的自定义逻辑,以便我可以从Dram读取数据并将结果发送到Bram。谢谢。

2020-05-14 06:41:47

。MATLAB设计虽然Quartus和Vivado的FIR IP核中都提供了设计FIR滤波器的功能,但远没有MATLAB设计便捷和强大。设计中通常都是在MATLAB中设计好FIR的单位脉冲响应h(n),或者说

2020-09-25 17:44:38

目前FIR滤波器的硬件实现的方式有哪几种?怎么在FPGA上实现FIR滤波器的设计?

2021-05-07 06:03:13

我在项目中添加了自定义链接器脚本,链接器文件是虚拟文件夹。现在我想知道哪个链接器脚本,默认的或者自定义的是用于构建项目的IDE。我如何检查?

2019-08-14 08:22:42

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-23 06:39:46

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-27 07:16:54

是video in to AXI4-Stream,接到DMA,而HLS生成的算法IP是AXI4-Stream in and out。我想把AXI-Stream信号输出接到HLS输出的IP,IP经过图像处理后

2017-01-16 09:22:25

无论我如何尝试,AIVO(视频,Vsync,Hsync,DE)的所有输出在模拟中始终保持为0。我检查了端口连接,并单独模拟VTC和TPG,它们都运行良好。有没有人有经验的AXI4-Stream到视频输出

2019-03-08 10:00:05

使用的是Vivado,希望使用其FIRIP核设计一个滤波器,该滤波器不是固定结构,而是可以根据项目中的变量filterselect的值选择其通带频率,例如filterselect=0,1,2,3

2017-08-10 05:49:04

具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。Vivado集成的FIR IP核可以实现如下公式所示的N

2020-01-14 09:39:45

的详细内容,话不多说,上货。

数字滤波器广泛应用于硬件电路设计,在离散系统中尤为常见,一般可以分为FIR滤波器和IIR滤波器,那么这两种滤波器有什么区别和联系呢,我们就来简单的聊一聊

2023-05-29 16:47:16

Out核心,以及(4)VTC核心实现为(1)的检测器和(3)的生成器。问题是,如果我将Video Scaler内核放入我的设计中,AXI4-Stream to Video Out(ASVO)内核

2019-11-08 09:53:46

你好,我希望实现带可变带宽的带通滤波器(如16k,32k,64k等)。我有各种带宽的滤波器系数。我有Vivado 2015和FIR编译器v7.2。我希望将多频段BPF协方系数用于单个IP。请指导构建此类过滤器所需的各个步骤。谢谢。

2020-05-07 08:24:48

嗨,我正在研究Spartan 6的设计。数据来自PCIe IP核,频率为62.5MHz,通过AXI4-Stream FIFO同步到100 MHz系统时钟。这是一个示例波形;m_axis_tvalid

2019-08-12 07:29:20

Xilinx FPGA工程例子源码:EDK中PS2自定义IP

2016-06-07 11:44:14 4

4 Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口: 所以要把标准的VESA信号 转为

2017-02-08 08:36:19 531

531

本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。 1AXI简介(本部分内容参考官网资料翻译) 自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用

2018-06-29 09:33:00 14957

14957

IP核的全称是: AXI4-STREAM FIFO 设置注意事项:一定要选择异步时钟,也就是双时钟,如下: 关于其他配置: TLAST 一般要选择的,作为边界界定。其他可以不选。深度不必太深,因为只起到穿越时钟区域的作用。

2018-03-26 14:40:00 4916

4916

了解如何使用Vivado的创建和封装IP功能创建可添加自定义逻辑的AXI外设,以创建自定义IP。

2018-11-29 06:48:00 6801

6801

自定义sobel滤波IP核 IP接口遵守AXI Stream协议

2019-08-06 06:04:00 3573

3573 Xilinx FIR IP的介绍与仿真 1 xilinx fir ip 简介 1)符合 AXI4-Stream 的接口 2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取

2020-10-30 12:29:01 511

511 AXI-Stream代码详解 AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据

2020-11-05 17:40:36 2826

2826

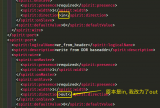

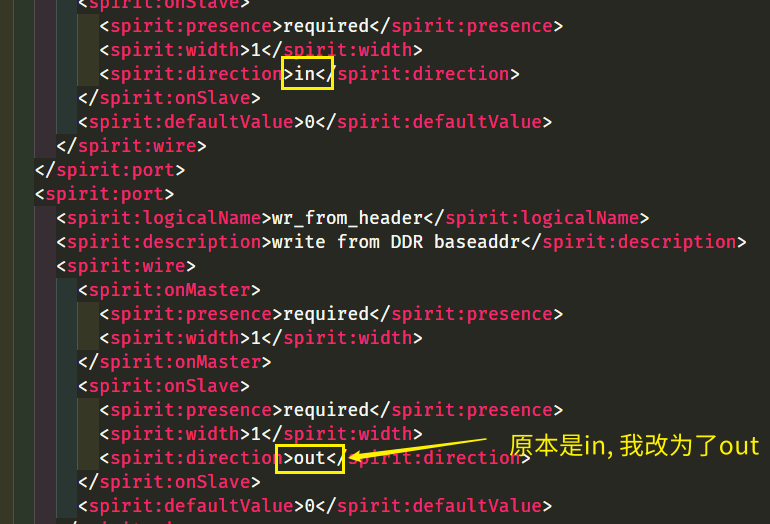

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

2021-03-30 15:49:47 4420

4420

XI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,

2022-06-23 10:08:47 1781

1781 本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 6846

6846 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

2022-08-02 09:49:46 2247

2247

为了方便用户进行相关设计,Vivado 提供了一个内置的 IP 封装编辑器工具,它可以为 AXI IP 生成框架,只需将自己的 RTL 代码插入其中。同时也提供了相关的驱动文件,可以在Vitis中方便调试。

2022-11-07 09:25:44 456

456 的图形表示进行设计,在block design中使用 RTL 模块的方便之处在于,它将自动检测某些类型的信号,例如时钟、复位和总线接口,然后,检测这些信号进行IP间的自动化连接。Vivado 中包含大量预构建 IP 模块(官方IP)。

2023-01-06 09:31:34 460

460 的图形表示进行设计,在block design中使用 RTL 模块的方便之处在于,它将自动检测某些类型的信号,例如时钟、复位和总线接口,然后,检测这些信号进行IP间的自动化连接。Vivado 中包含大量预构建 IP 模块(官方IP)。

2023-02-10 14:50:57 747

747

的图形表示进行设计,在block design中使用 RTL 模块的方便之处在于,它将自动检测某些类型的信号,例如时钟、复位和总线接口,然后,检测这些信号进行IP间的自动化连接。Vivado 中包含大量预构建 IP 模块(官方IP)。

2023-02-10 14:51:14 1581

1581

教程 3:构建自定义配置文件

2023-03-15 19:39:12 0

0 大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。

2023-05-18 14:55:16 966

966

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 1914

1914

教程 3:构建自定义配置文件

2023-07-06 18:49:28 0

0 RISC-V自定义计算 – 构建您的抱负演讲ppt分享

2023-07-14 17:15:32 0

0 电子发烧友网站提供《Vivado设计套件用户指南:创建和打包自定义IP.pdf》资料免费下载

2023-09-13 14:54:52 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:创建和打包自定义IP.pdf》资料免费下载

2023-09-13 11:34:50 0

0 LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

2023-09-25 10:55:33 497

497

正在加载...

电子发烧友App

电子发烧友App

评论