Barry Harvey

我正在测试一个电路,发现与我用来创建它的纸张设计存在许多差异。电路的动态有点出乎意料,噪声水平比要求的要大得多。我需要将电路带到模拟器上才能完全理解它。

该电路涉及模拟开关和运算放大器。所采用的运算放大器有很好的宏模型,但模拟开关宏模型不是为通用而设计的。在开关宏模型文件的标题中,有一条警告,指出建模参数仅对特定电源和温度有效。好吧,你不知道吗:我的电路与建模电路的工作条件不同。关于模拟开关的事情是,它们是如此通用,以至于一个工作点是不够的。现有的行业标准模型提供了一个良好的开端,但如果您进入模拟性能领域,则可能需要一种新的宏建模方法,将仿真提升到更高的水平。

当我开始浏览ADI公司和其他IC公司的各种模拟开关宏模型时,我注意到它们的所有标题都表明没有对电源或温度依赖性进行建模。因此,我将不得不制作自己的宏模型。

我在这项工作中的理念是,使用最简单的器件模型的模拟开关中的全晶体管提供了所有要仿真的行为,但从控制引脚到MOS门的接口应该是最简单的行为组件。

这里的所有工作都是通过LTspice模拟器完成的;该代码可以在其他模拟器上运行,并将LTspice行为设备转换为类似SPICE的多项式函数。

我们将按特定顺序开发模拟行为。

开发导通电阻的LTspice模型参数

我们将使用最简单的模型来运行真正的 MOS 设备。为了模拟阻力,我们将采用:

W/L,宽度 (W) 除以 MOS 器件的长度 (L)。W/L 是设备的尺寸或相对强度。

V自、阈值电压;和伽玛,它修改了 V自具有设备反向偏置。反向偏置是接通器件与其体电压之间的电压;主体经常连接到开关中 PMOS 的正电源和 NMOS 的负电源。

KP,在模型中,也称为 K' 或 K-素数。该参数模拟过程强度,并乘以W/L以标度MOS电流。对于给定的过程,NMOS 将具有 ~2.5×KP的 PMOS。

RD,器件漏极的寄生电阻。

不同的MOS工艺具有不同的内在参数。表1是常见CMOS工艺、其特性以及与导通电阻相关的估计内在参数的集合。

| 电压节点 (V) | 设备结构 | 栅氧化层厚度(m) | V自, 不适用, V | 伽玛, n/p, V0.5 | KP, 不适用, 微安/伏2 | L, μ | RD, 不适用, Ω |

| 40 | 漏极漂移区域 | 10–7 | 0.7/–0.9 | 0.4/–0.57 | 11/5 | 2 | ~80% RDS,ON |

| 15 | 软漏极扩散 | 4×10–8 | 0.7/–0.9 | 0.4/–0.57 | 22/10 | 1.5 | ~20% RDS,ON |

| 5 | 简单 | 1.4×10–8 | 0.7/–0.9 | 0.4/–0.57 | 80/28 | 0.5 | ~0 |

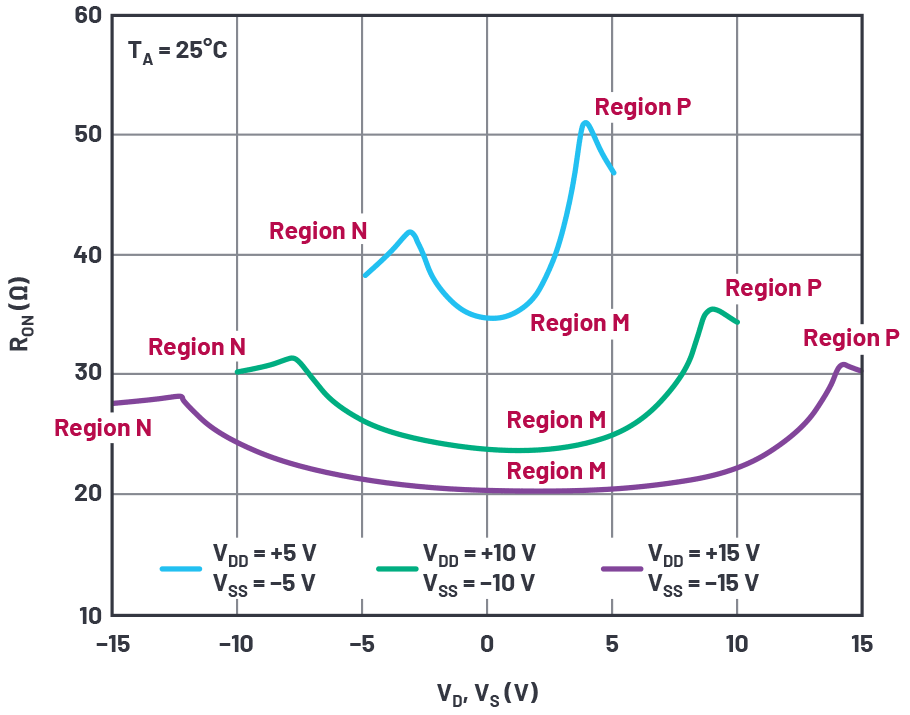

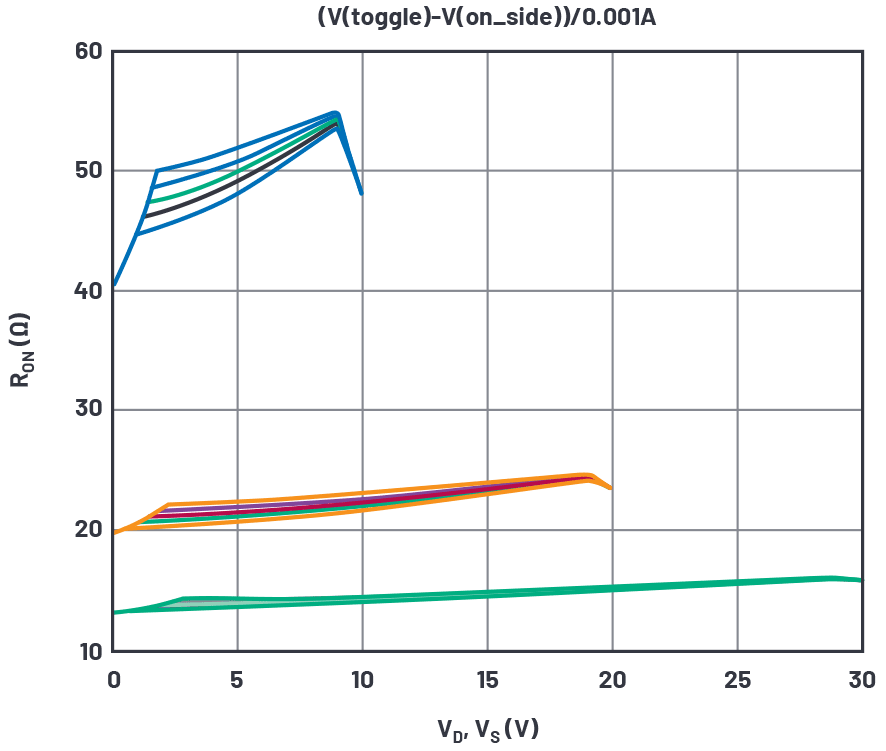

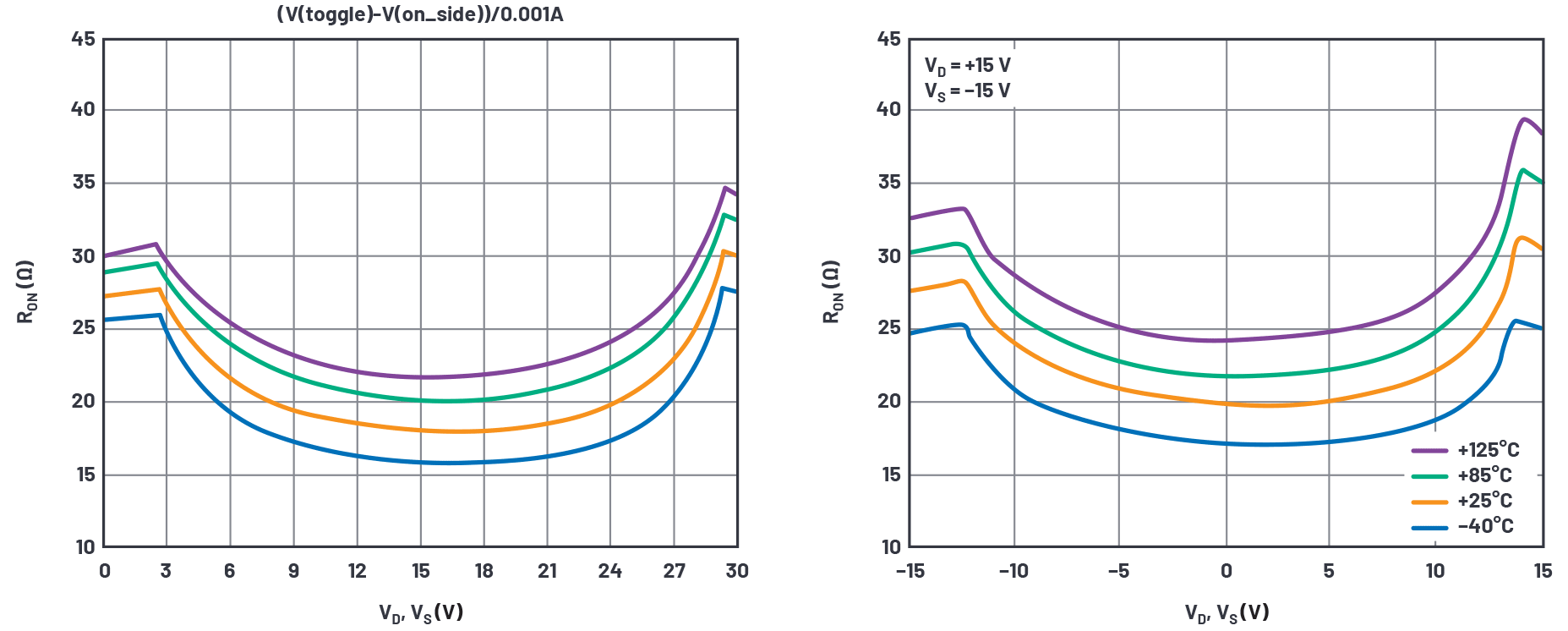

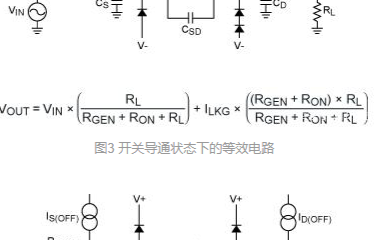

让我们看看ADG333A R上我们希望在图 1 中重现的曲线。

图1.R上作为 V 的函数D(五S),双电源。

我们看到此开关和任何其他模拟开关的总体趋势是,较高的电源电压会降低导通电阻。随着对开关MOS栅极施加的电压增加,导通电阻降低。我们还看到导通电阻随模拟电平的明显变化。在N个区域中,开关中的NMOS晶体管完全导通,当模拟电压上升到负电源轨以上时,PMOS晶体管导通并有助于降低整体导通电阻。区域 N 的拐点大致为 PMOS V自高于负电源。

类似地,在区域P中,开关的PMOS器件完全打开,NMOS开始协助PMOS晶体管,大致为NMOS V自低于正供应。

区域M位于N和P区域的中间,NMOS和PMOS并行工作,但每个区域的导通电阻都根据电源之间的模拟信号电平而变化。

为了开始曲线拟合过程,我们首先估计每个晶体管的尺寸。低电压曲线为晶体管R提供了最佳曲线拟合DS,ON.在区域 N 中,当模拟信号为负电源时,PMOS 器件关闭且 R上的零件等于 R上的 NMOS 晶体管。跟

使用 40 V NMOS 典型过程值,我们设置 RDS,ON= 距图 38 曲线 1 Ω,使用给定的过程量发现 WNMOS = 2 μA/(38 Ω × (11 × 10-6微安/伏2) × (10 V – 0.7 V)) = 514 μm。PMOS开关的导通电阻为上述曲线的47 Ω,因此宽度为936 μm。

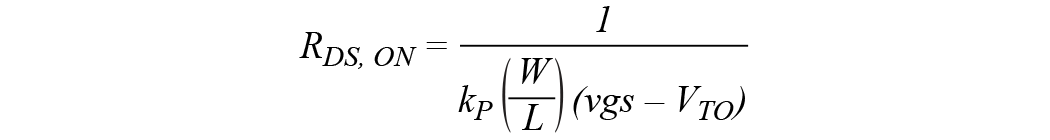

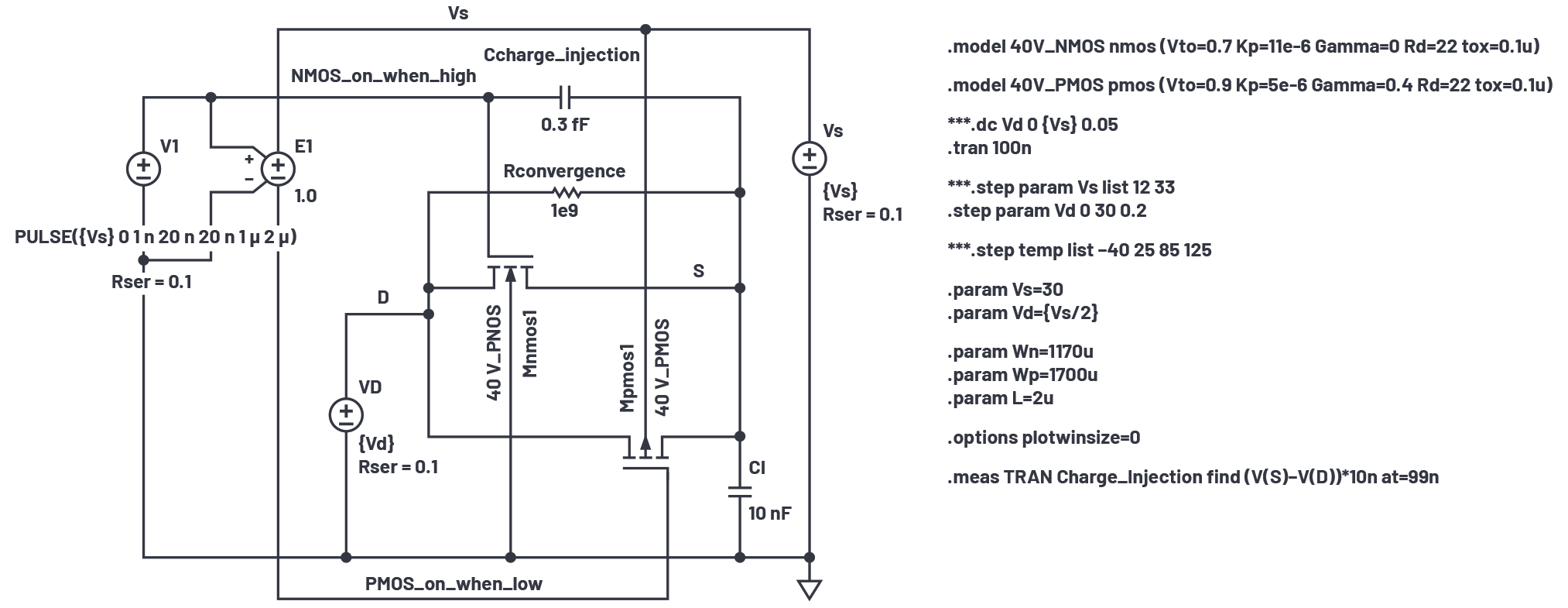

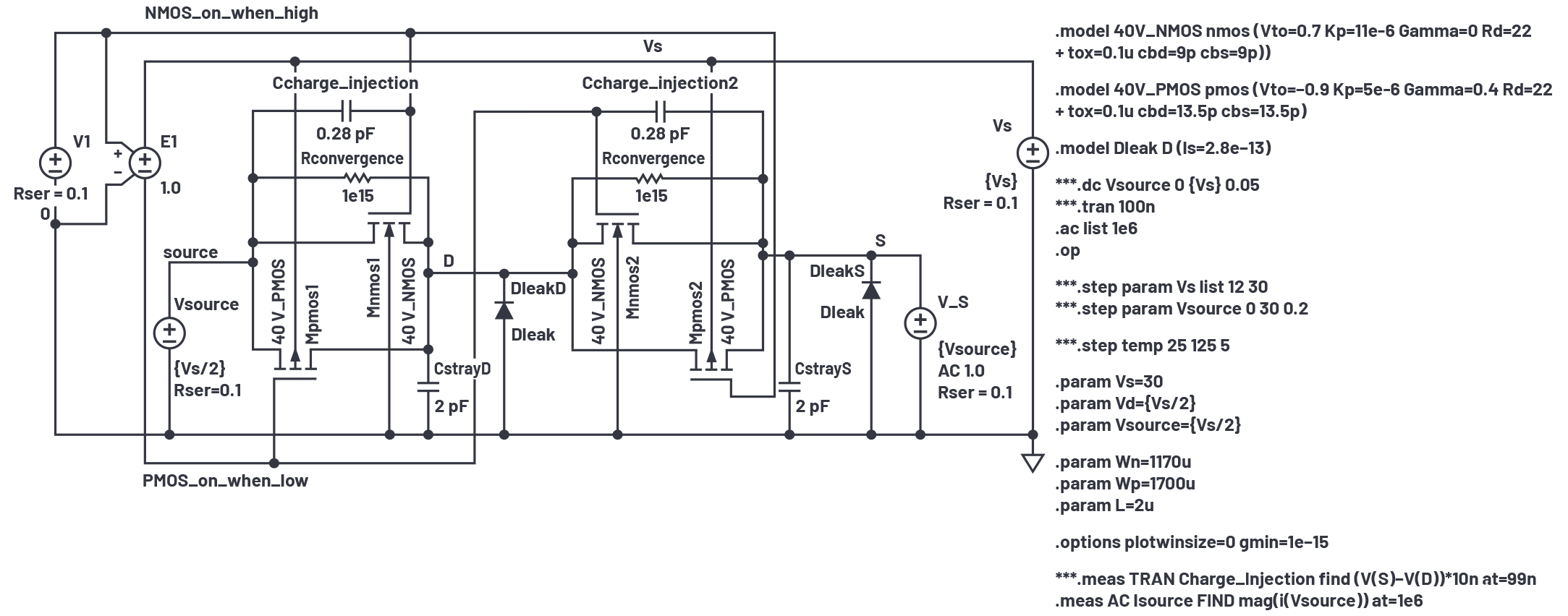

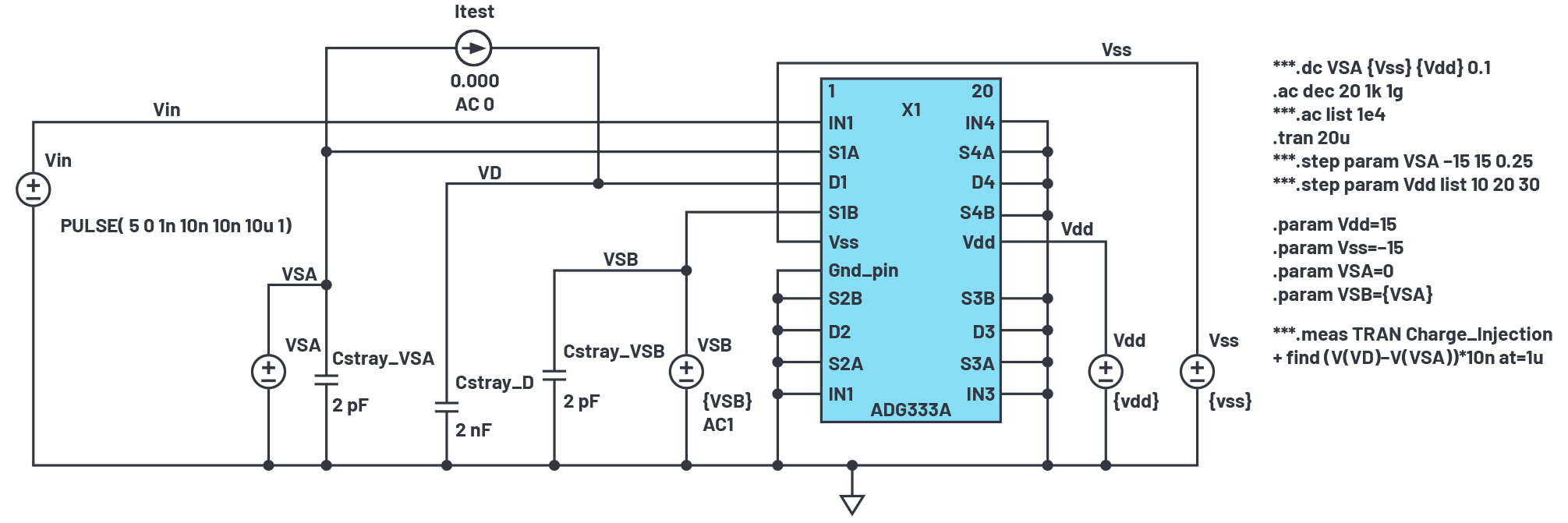

我使用了图2中的LTspice测试电路。请注意,参数 RDN和 RDP,寄生漏极电阻具有适中的价值。我从 1 μ 的值开始,这导致模拟器收敛速度变慢。R型DN值 1 允许适当的模拟速度。添加 R收敛通过为拨动节点提供可收敛的电导来改善模拟器噪声和速度。我测试了一个用于测量电阻的浮动电流源。

图2.导通电阻测试电路。

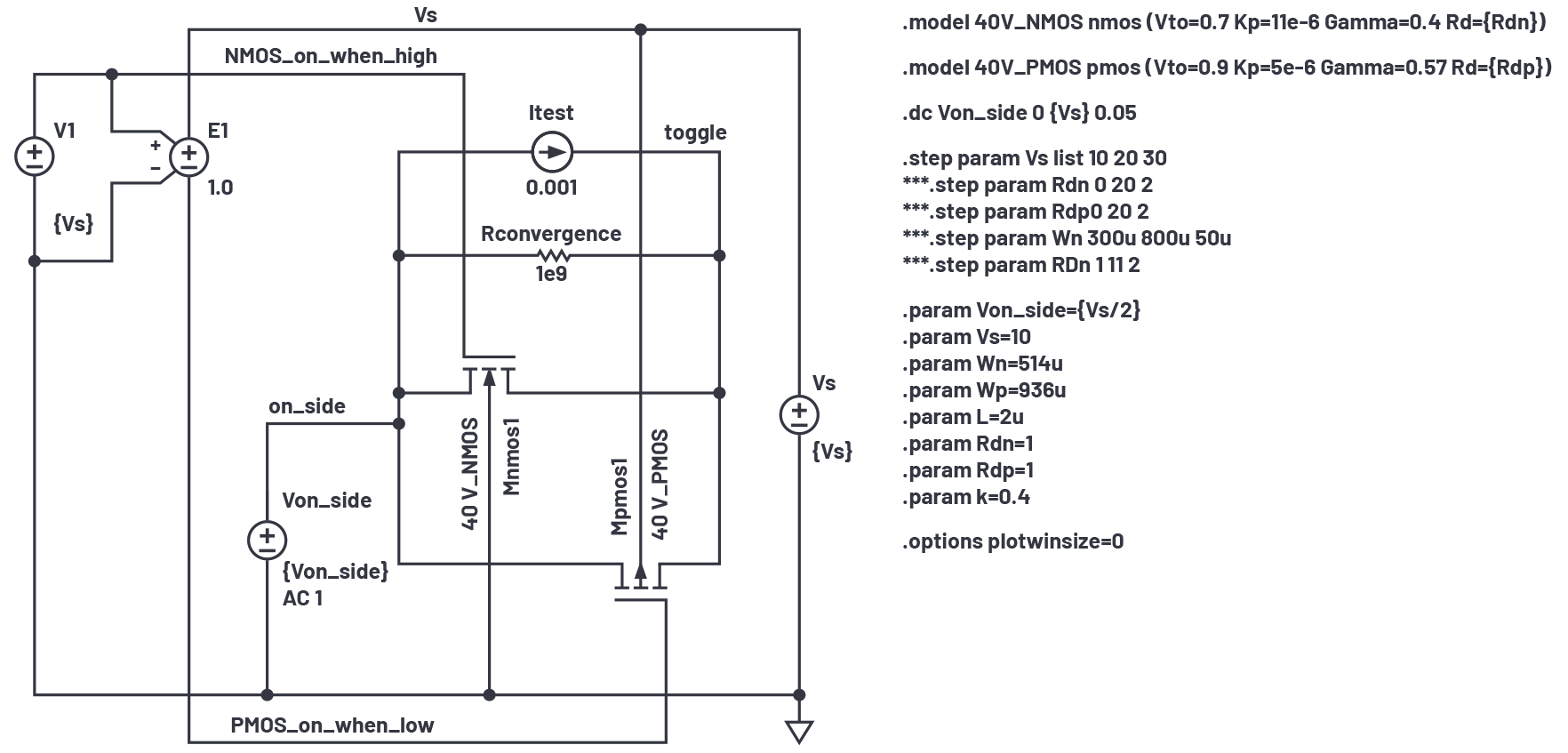

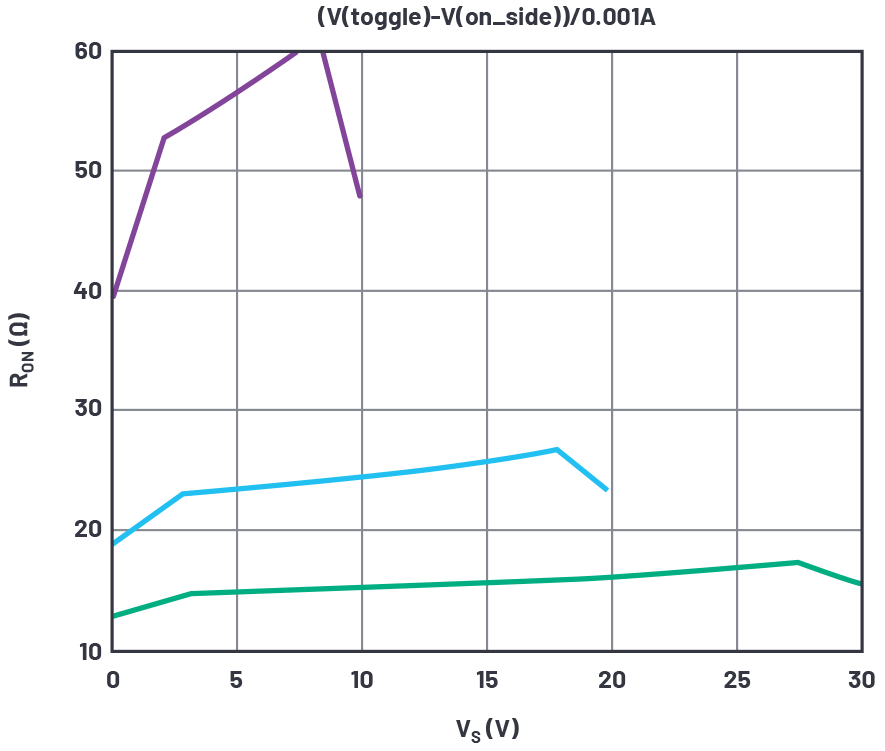

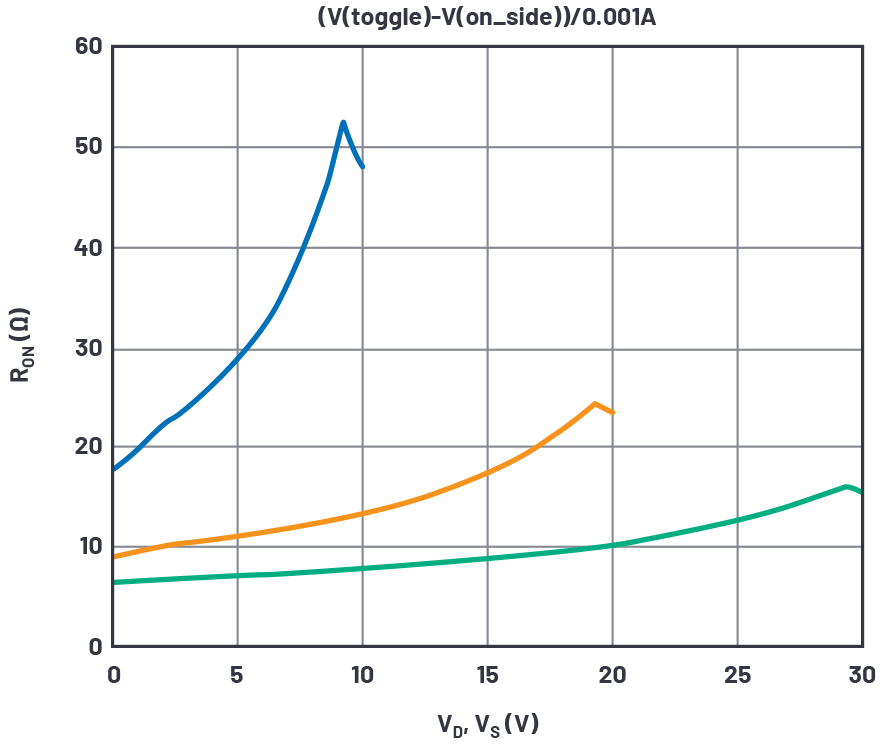

图3显示了各种电源的仿真结果。

图3.具有初始模型值的电阻仿真结果。

这是一个良好的开端。V低压端的扭结S= 30 V在仿真中为3.6 V,在数据手册中为2.7 V。这表明我们降低了PMOS V自,但0.9 V已经是一个现实的最小值。最好调整 PMOS 的伽马,无论如何这只是一个猜测。

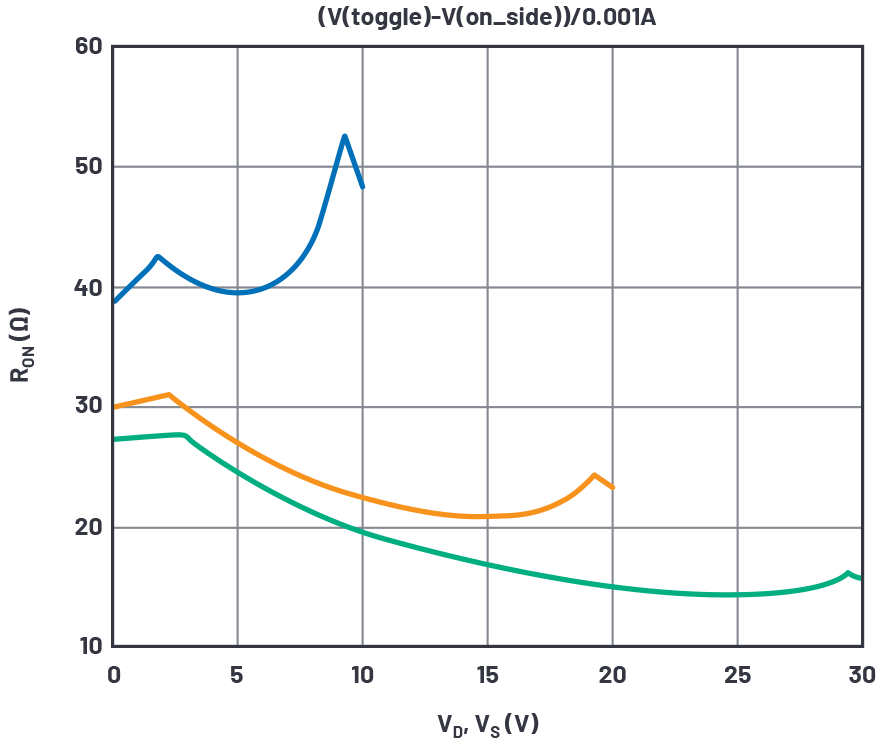

接近最大电源电压的扭结比2 V电源轨低5.30 V,在数据手册中应为~1 V。 各种伽马值夸大了电源轨的扭结电压;我们将只设置 NMOS V自至 1 V,其伽马值为零。零伽马是出乎意料的,但我们只是试图曲线拟合。图4显示了这些值的仿真结果,PMOS的伽马步进适用于多个电源。我们专注于30 V曲线,与较低电源相比,该曲线可最大限度地提高伽马效应。

图4.γ-p的电阻模拟结果各不相同。

从阶梯曲线中,我们将选择 PMOS 伽马 = 0.4。

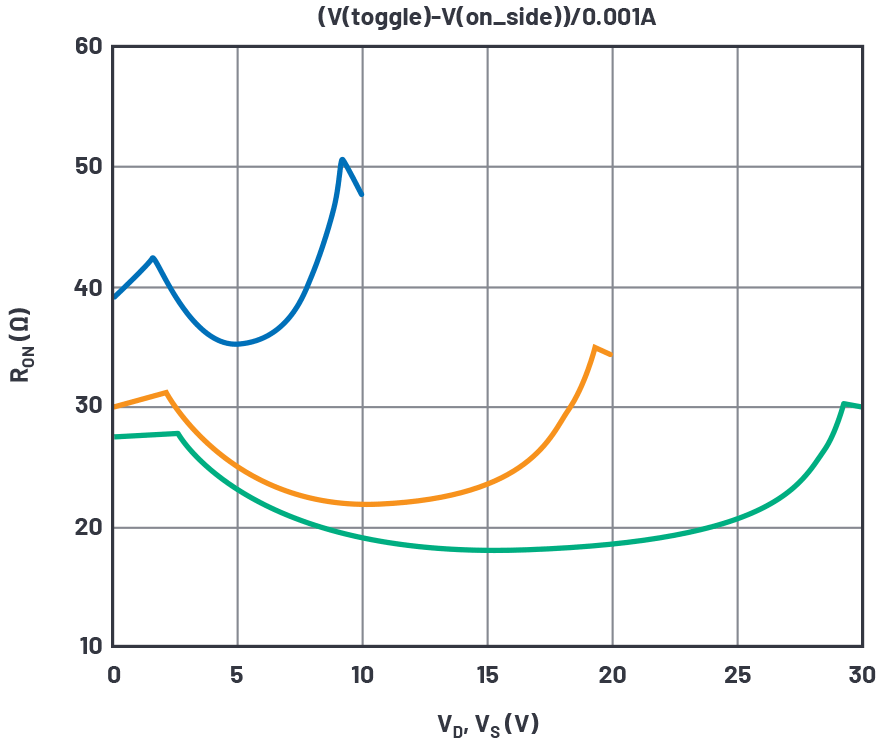

转到 R上.请注意,10 V曲线代表电源极端条件下的数据手册曲线,但仿真产生的R上适用于 20 V 和 30 V 曲线。R型上s 等于 RDS,ON(NMOS)+RD负电源极值和 R 时的 NMOS)DS,ON(PMOS)+RD(PMOS) 处于正极值供应。对于高电源,RD参数将比W/L更重要,对于低电源,W/L将占主导地位。我们在这里有两个变量需要处理;太费力了。我们将假设 R上由于NMOS的增强程度各不相同,因此随供应而变化,但RD值不随电源电压而变化(好吧,在具有漂移区域的漏极的情况下可能会发生变化,但让我们保持简单)。如果我们注意到数据表R的差异上在 10 V 和 30 V 电源(11.4 Ω)之间,我们可以将其与上述曲线进行比较,其中我们仅步进 WN(交换机中 NMOS 的宽度)。经过 W 的几次迭代N在模拟中,很明显我们需要WN= 1170 μm 获得所需的 ΔR上,比最初的猜测要多得多。图 5 显示了我们当前的结果。

图5.导通电阻仿真结果(WN确定。

虽然 R上的NMOS具有正确的电源灵敏度,曲线在零伏时值太低,我们必须增加固定RDN.增加和迭代 R 后DN,我们得到 R 的最佳值DN= 22 Ω,得到的曲线如图 6 所示。

图6.使用 R 的导通电阻仿真结果DN确定。

我们接下来确定WP(交换机中 PMOS 的宽度)来模拟 R上在最大电压下,得到WP= 1700 μm,再次比最初猜测的要多得多。与 RDP也设置为 22 Ω,我们得到最终的 R上图 7 中的曲线。

图7.导通电阻仿真结果(WP和 RDP确定。

这里非常同意;只有几个特性与数据手册不同。一是拐点在数据手册曲线中是平滑的,但在仿真中是真正指向的。这可能是因为使用的简单MOS模型不支持亚阈值传导,并且仿真器件在V时真正关闭。自.真实设备在 V 时未关闭自,但平滑地将电流降低到该电压以下。

另一个误差在30 V曲线中最为明显。R上与数据手册相比,中端电源电压低 15%。这可能是由于漏极漂移区域内的JFET效应,也没有建模。

至于温度,符合性尚可,但柔顺性不强,如图8所示。

图8.导通电阻仿真和数据手册温度范围内的结果。

仿真具有温度依赖性,但不如数据手册曲线那么大。在仿真模型中,RD条款没有 tempco。RDs可以通过具有正确温度系数的外部电阻进行建模,但为简单起见,我们将保持原样。

获取用于电荷注入的LTspice模型参数

当MOS晶体管关闭时,通道中的电荷必须流向某个地方,因此它从漏极和源极端子中喷出。当模拟开关关闭时,电荷也会熄灭,称为电荷注入。一种常见的测量方法是在导通开关的一端放置一个固定电压,在另一端放置一个大电容器。关闭时,电荷被电容器捕获,并产生一个小的电压阶跃。我们现在将添加栅极氧化层厚度T牛= 1 × 10–7到MOS型号(栅极电容是电荷注入的最大来源)。我们的仿真设置如图 9 所示。

图9.电荷注入模拟设置。

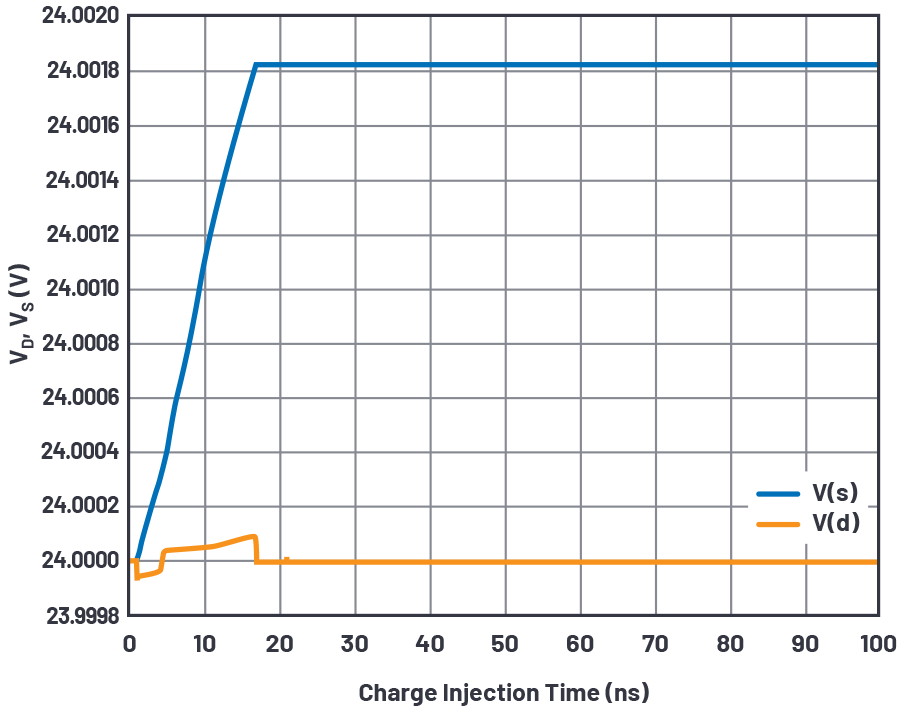

数据手册中的电荷注入测试电路在开关的D端放置一个电压源,在开关的S端放置一个电容Cl。当开关晶体管关闭时,Cl被隔离并集成由开关泵入其中的电荷。这种事件的波形与 VD采用24 V电源时保持至30 V,如图10所示。

图 10.电荷注入模拟波形。

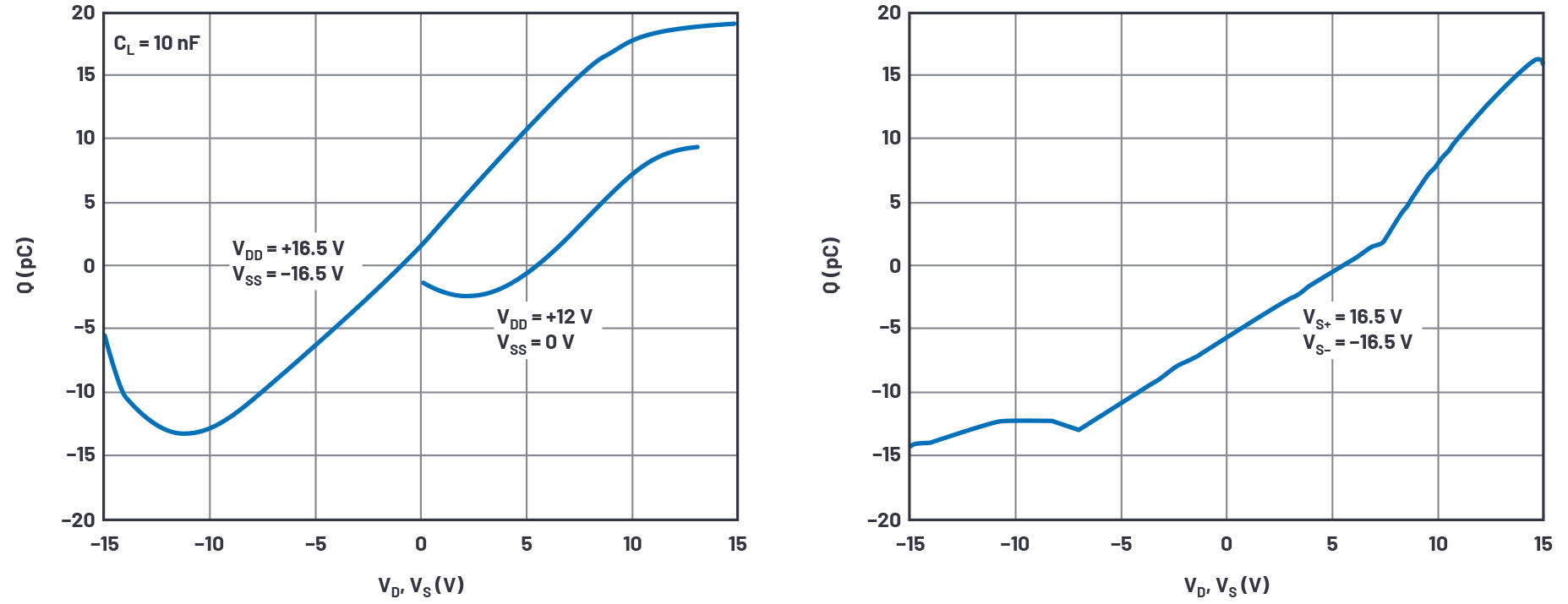

注入的电荷是V(S)和V(D)之间的电压跳跃乘以10 nF保持电容。我们可以步进开关电压VD跨电源电压,并使用 .MEAS 语句捕获每个电压下的电荷注入值。图11显示了数据手册曲线和仿真结果。

图 11.电荷注入数据手册和仿真波形。

我们的简单MOS模型不能很好地模拟数据手册曲线的形状,但数据手册曲线中的峰峰值电荷注入为32 pC,仿真中的峰峰值电荷注入为31 pC。令人惊讶地接近,但如果我们必须这样做,我们可以调整 T牛以完善仿真结果。

曲线之间存在偏移,我们可以使用 C 进行补偿CHARGE_INJECTION.在摆弄了一些值之后,我们选择一个最优的CCHARGE_INJECTION= 0.28 pF。如果需要相反极性的移位CCHARGE_INJECTION将重新连接到PMOS_on_when_low节点。

调整电容器CCHARGE_INJECTION是抵消电荷注入与模拟电压仿真曲线的便捷方法。如果模拟的峰峰值进样太小怎么办?嗯,大多数电荷注入主要是开关的栅极电压摆幅,通过开关晶体管的栅极通道电容发送电荷。如果我们模拟的注入太少,我们可以简单地增加一个或两个浇口区域。为此,我们将开关器件的参数 L 和 W 增加相同的系数,注意不要修改设置导通电阻的 W/L 比。而不是使用 CCHARGE_INJECTION我们本可以增加NMOS W和L。

或者,我们可以调整 T牛在每个器件中获得更好的电荷注入相关性。这在物理上是不可能的,但嘿——这只是一个模拟。对于我们使用的简单模型,T牛不影响其他行为。

获取电容的LTspice模型参数

为良好的 R 设置了参数上和电荷注入仿真结果,我们现在仿真S和D端电容。

重要的一点是,高压MOS开关的漏极和源极区域都必须具有漂移区域。作为开关,您无法分辨源极和漏极之间的功能差异,并且漏极和源极的体电位将需要每个漏极和漏极中的漂移区域。中压软扩散也是如此,但在低压MOS中不存在。我们将漏极和源极中存在的漂移区域电阻归结为R。D,这适用于开关,但不适用于饱和的晶体管。

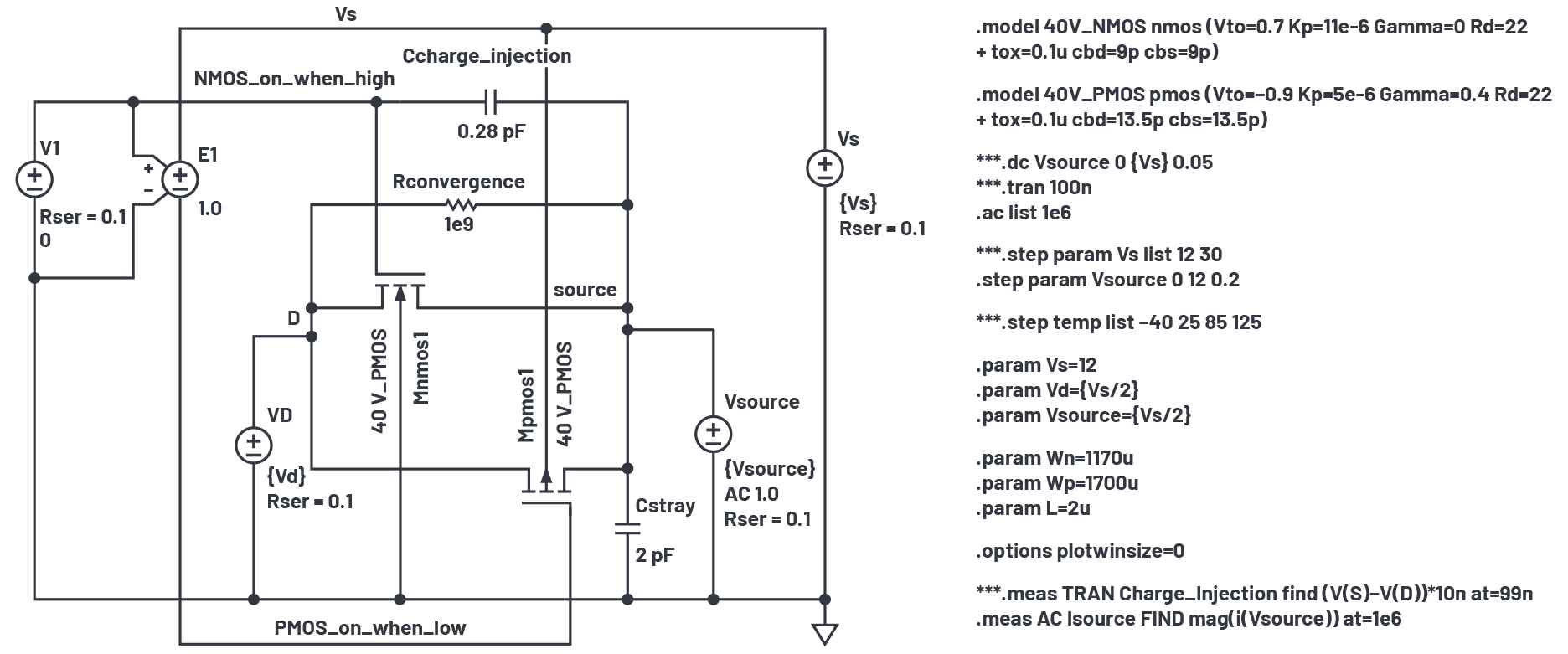

图 12 显示了我们的仿真设置。

图 12.关断电容测试仿真设置。

在LTspice中,您可以使用.ac中的列表选项,只能在一个频率上运行.ac,但仅提供一个频率参数(此处为1 MHz)。然后运行 .步骤 V源电源范围内的直流电压,以获得电容与电压扫描的关系。

关断器件的 D 端保持在中间电源。S 终端,此处重命名源以防止与 V 混淆S,由直流值扫描范围为 0 V 至 V 的电压源驱动S交流驱动为 1 V,电容来自 I(V源)/(2×π×1 兆赫×1 V)。逻辑驱动器V1更改为0 V以关闭晶体管。

漏极和源极电容为C屋宇 署和 C理学士分别在模型语句中。模型中有内置的默认浓度、内置电压和指数,使 C屋宇 署和 C理学士电压可变。由于它们是对称的,因此漏极和源极电容将相等。此外,由于PMOS的宽度与NMOS不同,因此C的比率为CBD,NMOS/CBD,PMOS= CBS,NMOS/CBS,PMOS≡ WN/WP,这是我们在电阻建模中建立的。仿真结果如图 13 所示。

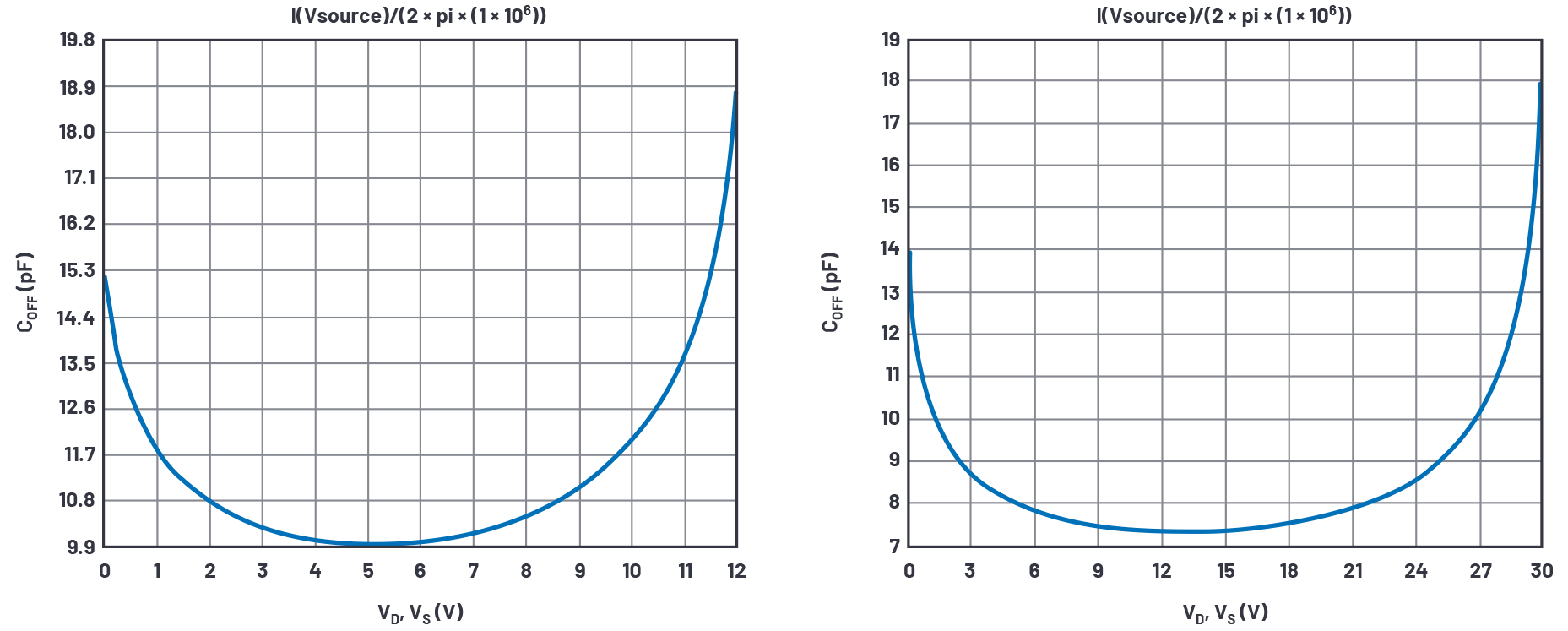

图 13.关断电容与 V 时的直流电压的关系S= 12 V(左)和30 V(右)结果。

显示器为 I(V源)/(2×π×1 MHz),即电容。LTspice不知道这一点,并显示pA而不是pF。

不幸的是,我们没有数据手册曲线可以比较。我们从数据手册的规格表中了解到,电容(可能在中间电源下,但未在数据手册中指定)在7 V电源下典型值为30 pF,在12 V电源下典型值为12 pF。我调整了CBs,在7 V时获得30 pF曲线,但在10 V电源下仅仿真12 pF。在摆弄内置电位和电容公式指数后,所使用的模型无法灵活地提高12 V/30 V的合规性。

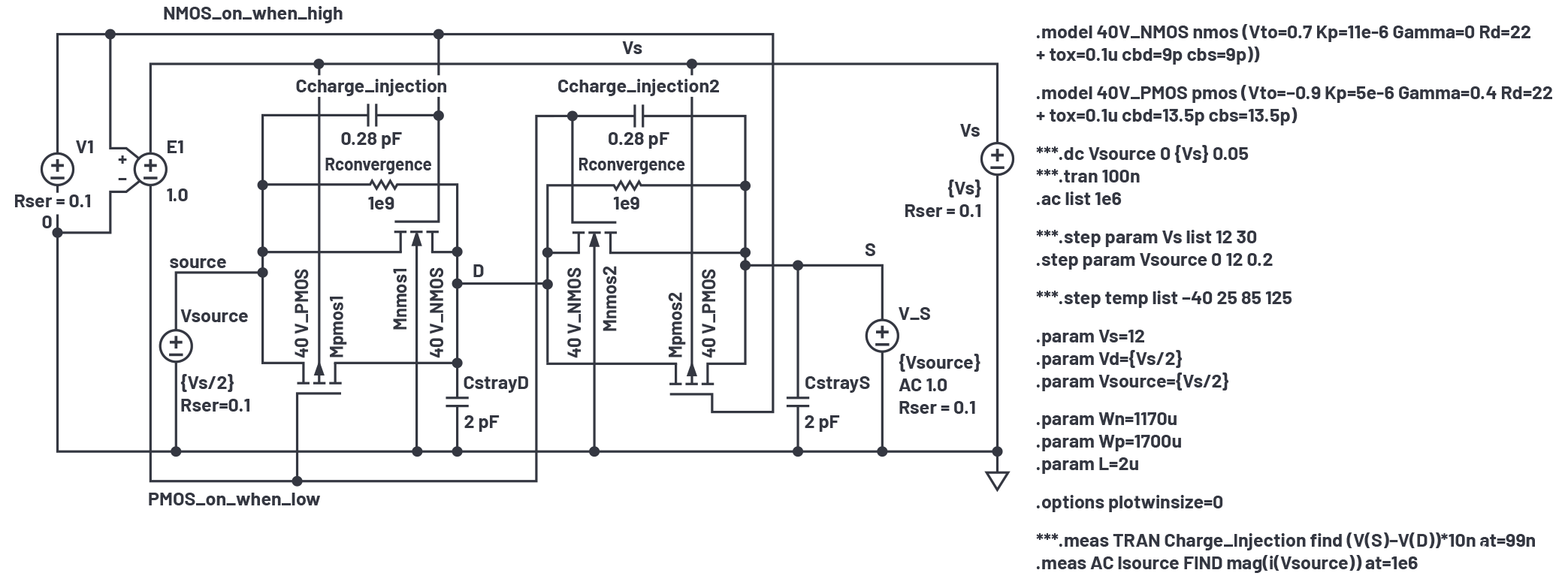

图14显示了导通状态电容仿真设置。

图 14.导通电容测试仿真设置。

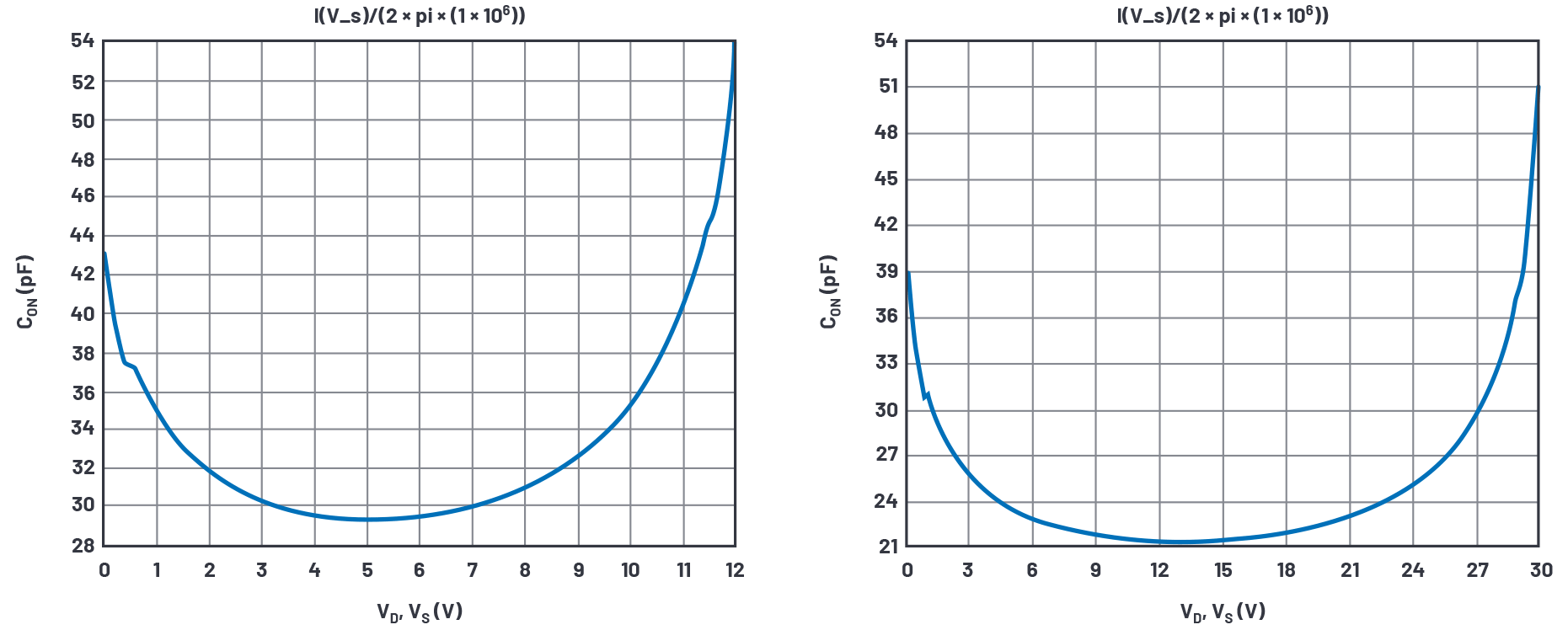

此处,全单刀双掷开关的右侧开关打开,左侧开关关闭并连接到 VS/2来源。左开关右半部分的电容和右开关的全电容,加上D和S端子上不可避免的寄生电容,都由V_s源的1 MHz测试信号并联和驱动,其直流电平跨地步进至VS.图 15 显示了结果。

图 15.导通电容与 V 时的直流电压的关系S= 12 V(左)和30 V(右)结果。

我们模拟29.5 pF和21.4 pF,其中数据手册给出26 pF和25 pF。考虑到电路板布局电容的可变性,我们称之为足够接近。

漏电流

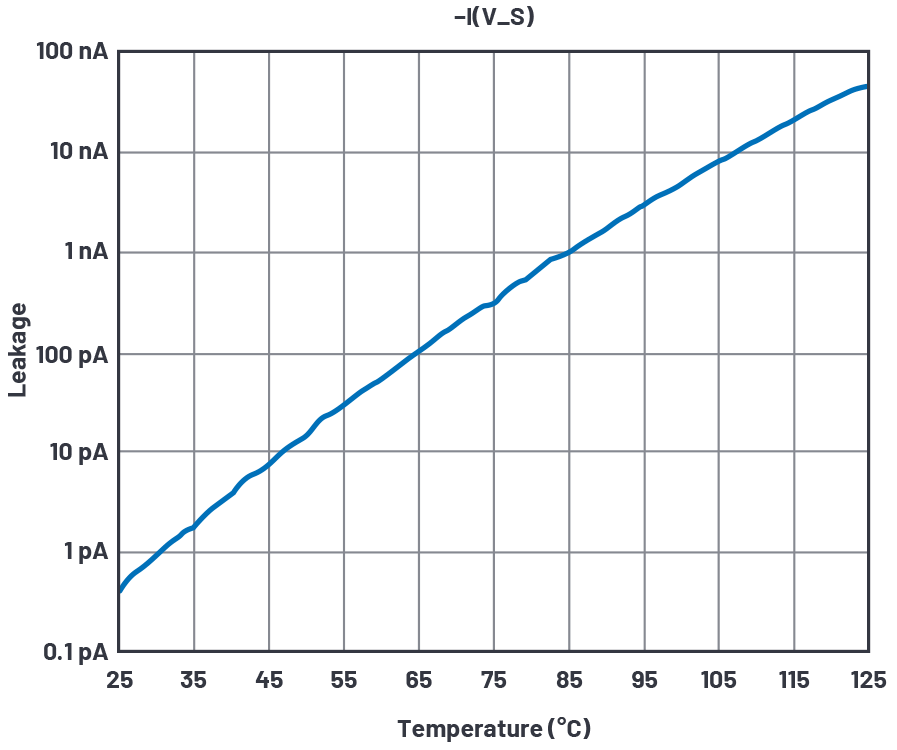

数据手册曲线显示了25°C时与电压相关的pA级漏电流,但数据手册规格仅保证数百pA。我在25°C时对曲线结果的影响更大。 在该器件中,小泄漏电流显然被认为不够重要,无法在测试中保证。公平地说,测量单个pA需要大量的工程开发工作以及较长的测试时间。

在 85°C 时,保证为几 nA(可以有效测量),典型结果在几百 pA 范围内。我会接受这些典型的结果是好的。

漏电流是产品的缺点;它没有严格的统计数据,并且随温度变化很大。它不是我们设计的那种规格 - 相反,它是一个破坏它所连接的电路的数量。对于宏模型使用,任何适当幅度的泄漏都将被模拟为电路缺陷,并对设计人员发出有用的警告。我将为1°C的导通开关选择85 nA的目标。

我们拥有的模型显示没有超出R的泄漏收敛和 G最低电流。G最低是模拟器放置在结点上以帮助收敛的电阻器。通常为 1 × 10–12电导,但在存在 30 V 电源的情况下,我们可以获得 30 pA 电流的倍数,这对于这项工作来说太高了。G最低将减少到 1 × 10–15在模拟和 R 的 .options 行中收敛提高到 1 × 1015.

这些泄漏的物理来源可能主要来自连接到每个引脚的静电放电(ESD)保护二极管。我们将它们插入到图 16 中的仿真设置中。

图 16.泄漏测试模拟设置。

摆弄完我S在二极管模型中,我们得到了图17中温度范围内的泄漏。

图 17.温度模拟结果的泄漏测试。

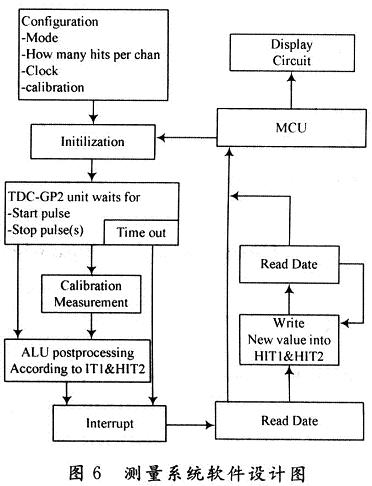

逻辑接口和栅极驱动器

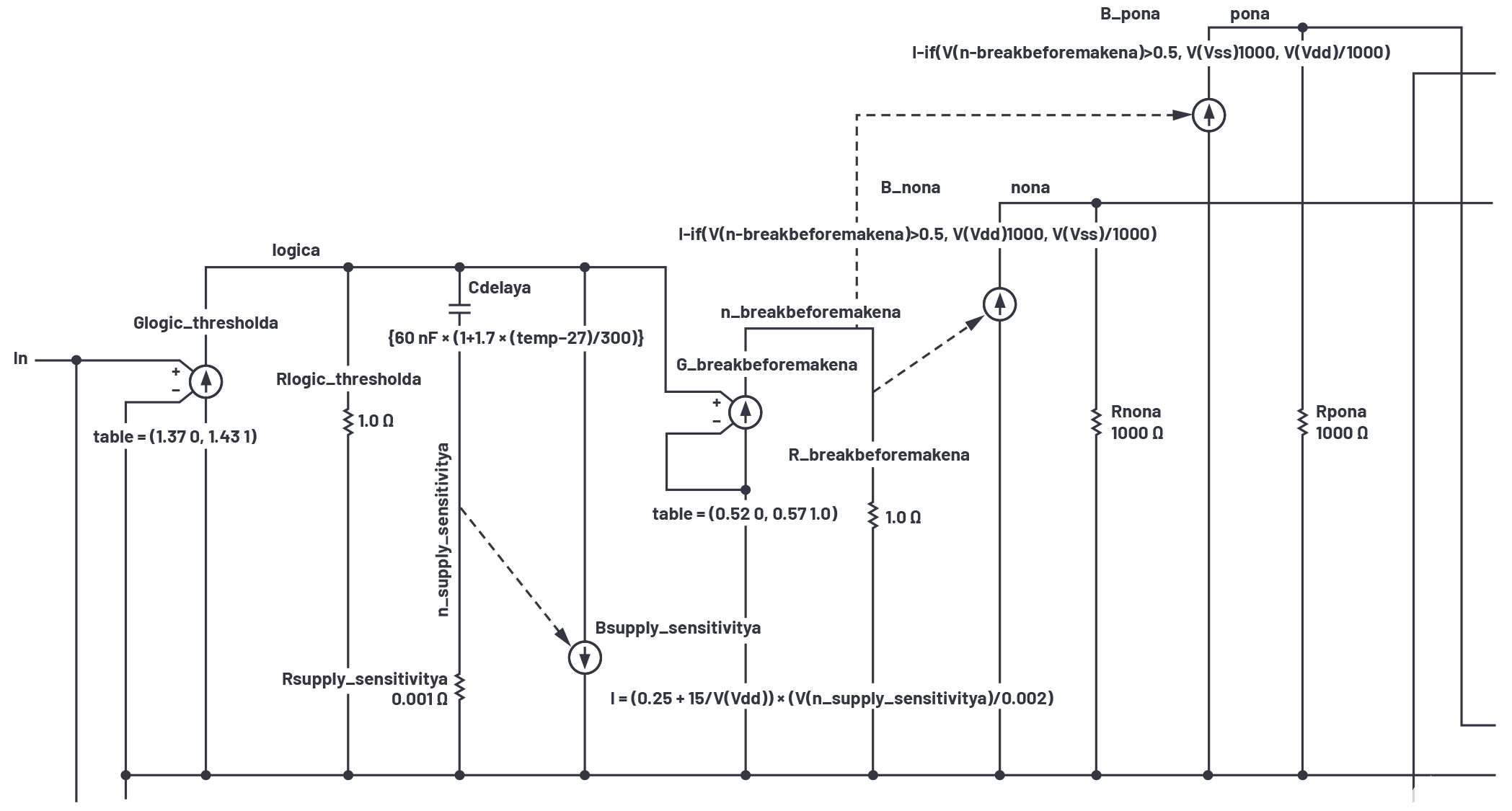

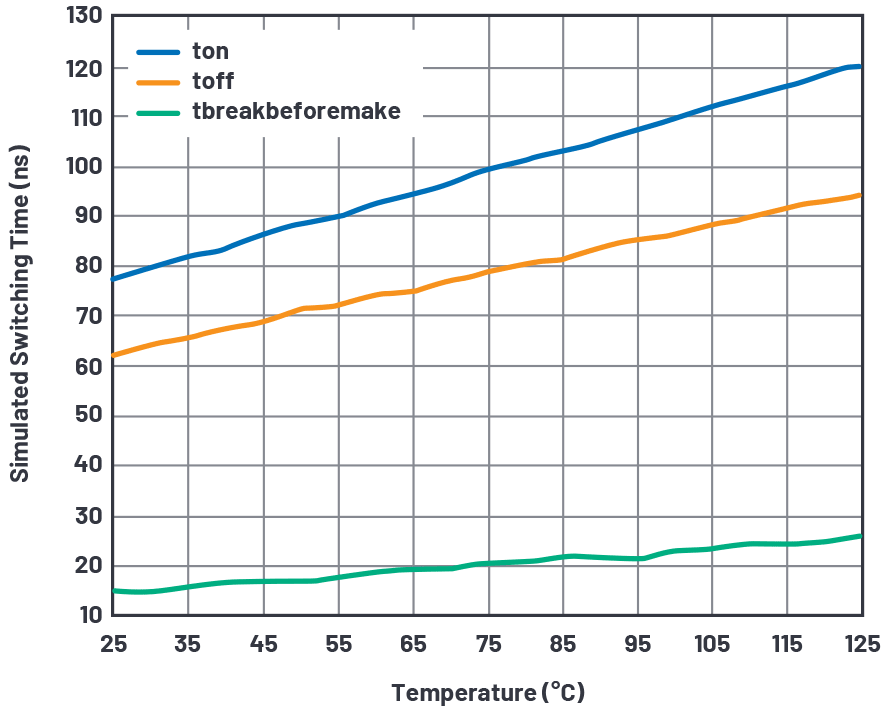

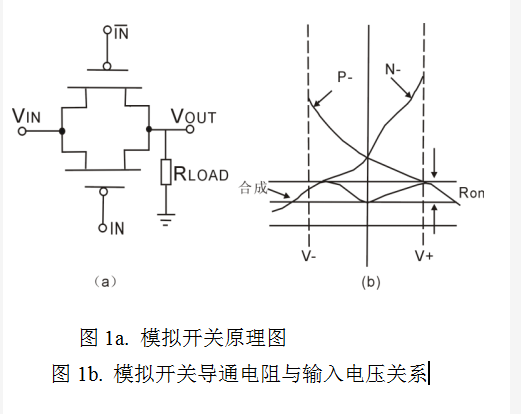

纯行为逻辑到栅极驱动电路如图18所示。

图 18.行为逻辑到门接口。

外部逻辑输入位于图18左侧的In端子。它是理想跨导Glogic_thresholda的输入,具有分段线性传递函数。对于低于1.37 V的逻辑输入,逻辑节点的输出为0 V;对于高于 1.43 V 的输入,逻辑为 1 V;逻辑中的1.37 V和1.43 V之间在0 V至1 V之间线性移动,因此Glogic_thresholda忽略电源变化,提供1.4 V输入阈值。

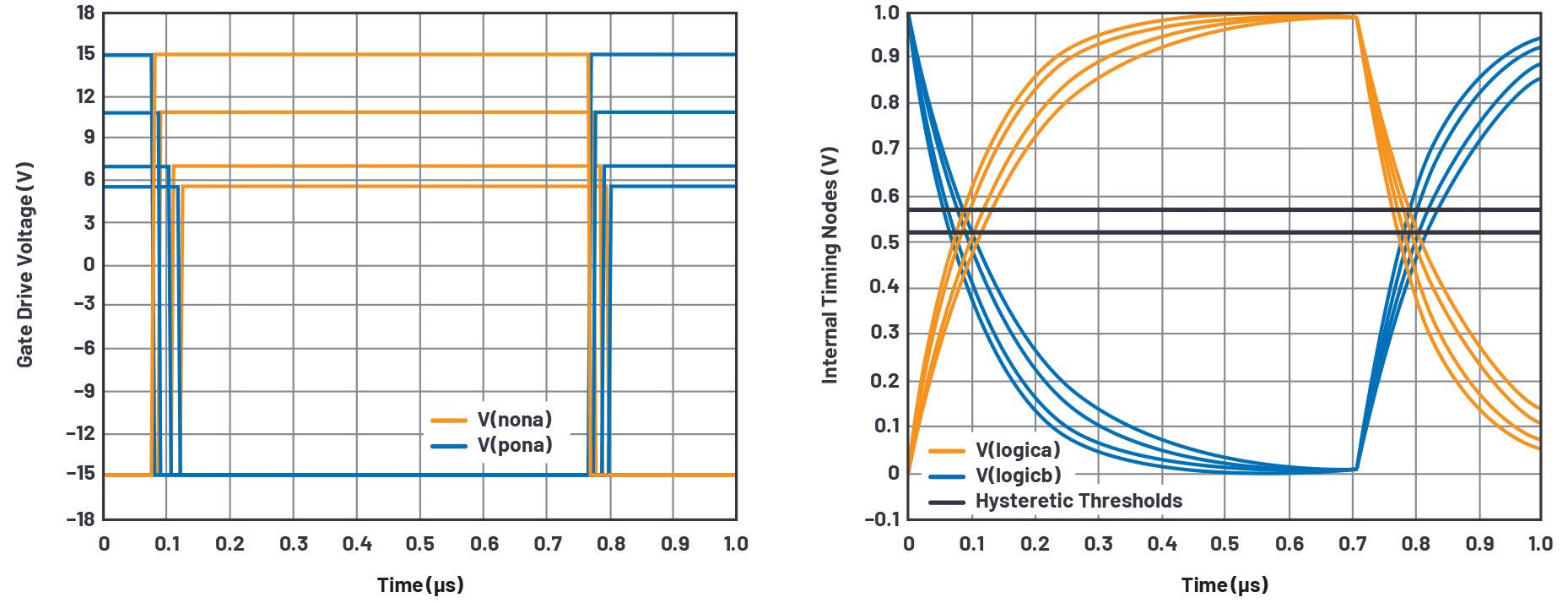

Cdelaya 暂时减慢了 logica 节点的速度,以便我们可以从中挑选一些时间点。为了制作比较器,我们再次使用跨导,此处为Gbreakbeforemakena,其输出再次从0 V变为1 V,但阈值略高于0.5 V。如图 19 所示,

图 19.先开后合时机。

偏斜拾取电压为0.52 V和0.57 V,而不是0.5 V,与从1 V上升的指数相比,从0 V下降的指数的关断速度更快。

全栅极驱动电压由B_non产生,B_pon行为电流源。B_nona源出 V 的电流DD当节点n_breakbeforemakena >1000.0 V时/5,将节点Nona的电压驱动至VDD,由 1000 Ω 电阻加载。当节点n_breakbeforemakena <0.5 V时,节点nona被驱动至V党卫军.因此,我们有一个很好的轨到轨栅极驱动,它符合电源电压,并具有固定的1.4 V输入阈值。

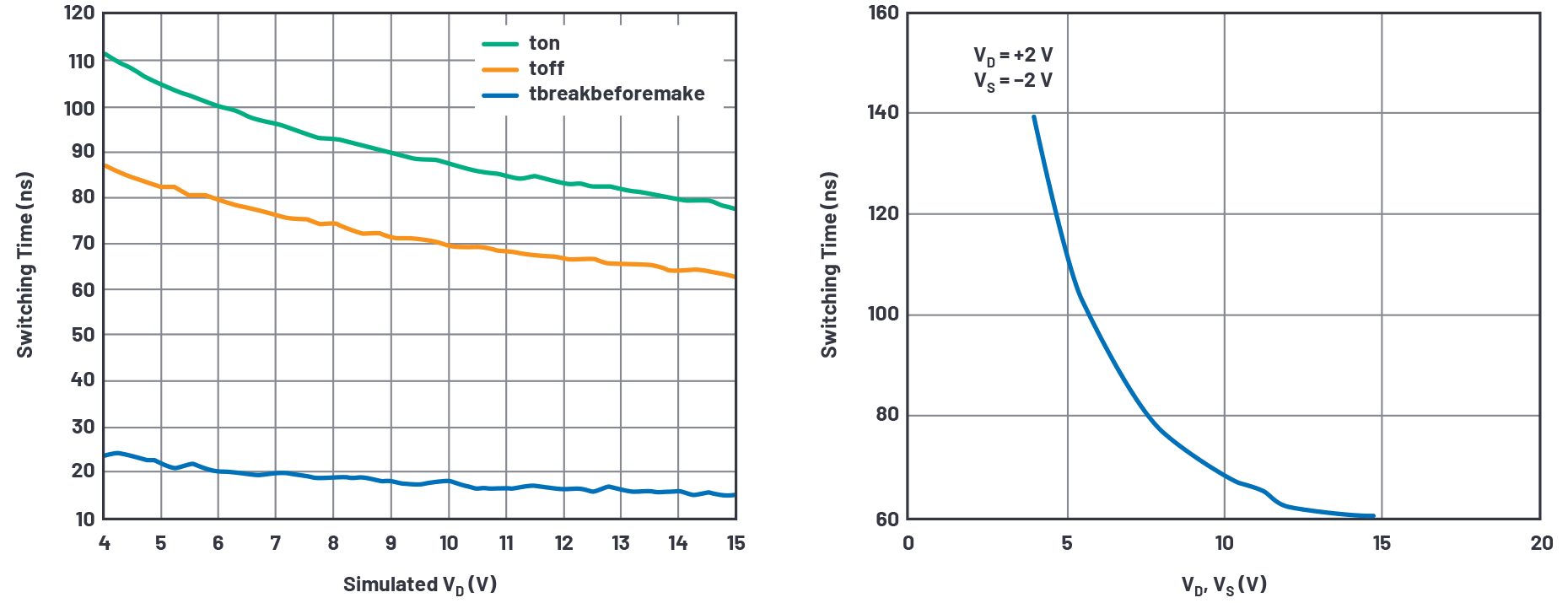

还有一个特征需要解释。请注意,在图20中,较高的电源电压可缩短延迟时间。这是由B_supplysensitivitya实现的,它向Cdelaya反馈了其自身动态电流的一小部分,该动态电流随V而变化DD.由于Cdelaya电流,Rsupply_sensitivitya电压下降非常小,Cdelaya的行为主要是纯电容器。将Cdelaya电流的副本馈回Cdelaya本质上会创建一个可控的可变电容器,而Bsupply_sensitivitya内部的数学运算会产生延迟与V的关系DD图 20 中的曲线。

图 20.仿真和数据手册曲线的先开后合时序结果。

好吧,我们的电路模拟了 T上V 延迟为 111 nsDD= 4 V,而数据手册曲线显示140 ns;和 VDD= 15 V模拟延迟为77 ns,而数据手册中的延迟为60 ns。相关性不大;我将留给读者来完善Bsupply_sensitivity函数以做得更好。至少先开后合在15 ns和24 ns之间变化很大。

虽然我们没有太多关于延迟与温度的数据手册数据,但我在Cdelaya中添加了一个温度项,至少可以模拟热时的减速,如图21所示。

图 21.时序延迟与温度的关系。

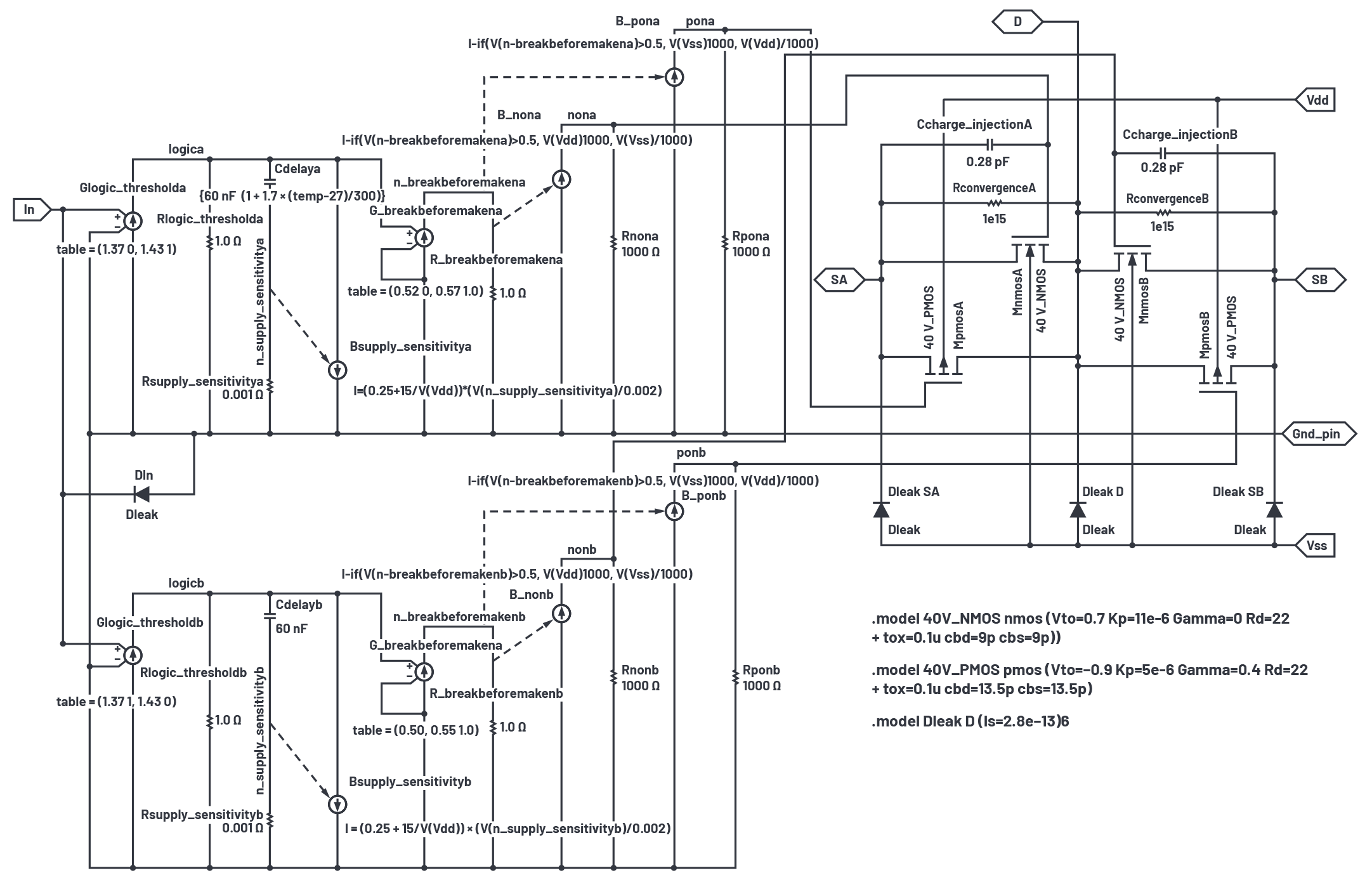

组装宏模型

图22显示了组装好的模拟开关,它将成为子电路。硬L和W数字被放置在晶体管符号而不是参数中,并且所有激励和I / O都被移除,有利于引脚连接SA,D,SB,In,VDD, V党卫军,并Gnd_pin。

图 22.组装单刀双掷子电路单刀双掷40V.asc。

为单刀双掷对的另一个开关提供了第二个逻辑接口。ESD保护二极管安装在模拟端子和V之间党卫军以及逻辑输入和接地之间。请注意,上层逻辑接口设备和节点名称中的“-a”后缀在下层接口中复制为“-b”后缀。Glogic_thresholdb接口具有与表Glogic_thresholda相反的输出,以允许一个或另一个开关对运行,而不是同时打开。

另一种ESD保护方案涉及从受保护引脚到两个V的二极管DD和 V党卫军,以及 V 之间的夹具DD和 V党卫军.数据手册通常提供有关保护方案的信息,漏电流分配给两个电源。

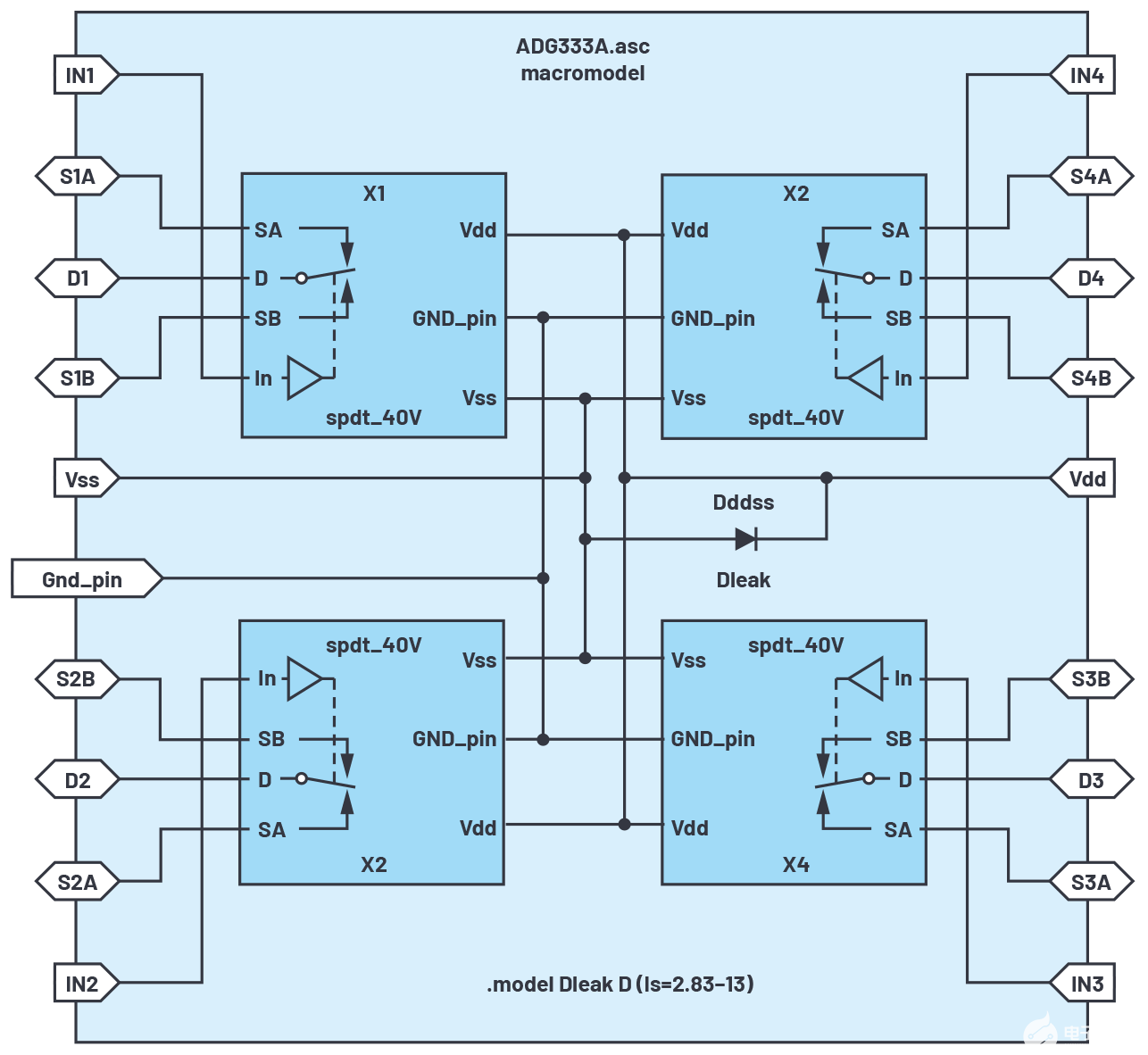

SPDT子电路被赋予一个符号,并在图333的主原理图ADG23A.asc中使用了四次。

图 23.ADG333A宏模型电路原理图

图24是用于验证最终宏模型结果的测试台示意图。

图 24.ADG333A宏模型测试平台。

总结

我们已经了解了如何为特定的模拟开关实现一个体面的宏模型,以及如何获得支持用于实现物理器件的几种不同半导体工艺的参数。由此产生的宏模型显示了诸如导通电阻及其变化、电荷注入与电源和信号电平的函数、寄生电容及其随电压的变化、逻辑接口延迟和泄漏等缺陷。希望宏模型有助于模拟模拟开关的实际性能。

审核编辑:gt

电子发烧友App

电子发烧友App

评论