信号分析仪(也称为频谱分析仪)通常用于测量微弱信号,包括已知信号和未知信号。通过噪声校正、本底噪声扩展 (NFE) 和优化信号分析仪设置,可以实现设备的最佳灵敏度,从而更轻松地检测和测量微弱信号。

2025-08-21 09:30:59 1995

1995

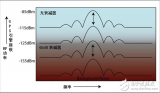

基于GPS/BD兼容高灵敏度导航产品开发和产业化项目,对经典载波跟踪环进行修改,设计实现了高灵敏度跟踪环路。将传统的单点积分数据,转化成一列数据,对该数据进行FFT变换后,可提高载波频率的估计精度,从而提高系统的跟踪灵敏度。并对高灵敏度跟踪环路进行仿真分析,证明高灵敏跟踪环路对弱信号的跟踪能力。

2013-08-12 10:23:01 11617

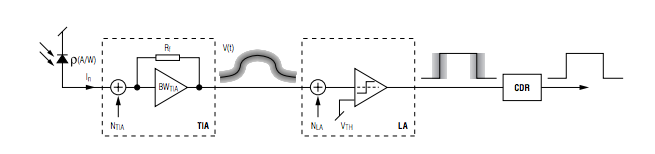

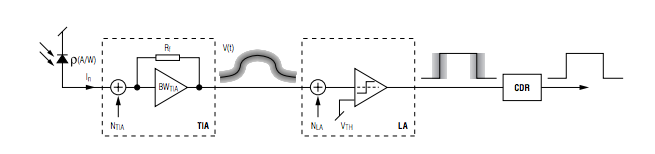

11617 记全部涉及光接收器灵敏度,其中包括由于幅度和时序上的随机噪声和符号间干扰(ISI)的积累而可能对功率输出产生的影响。该分析基于正常的接收器灵敏度,假设理想输入信号的干扰可忽略不计,例如ISI,上升/下降时间,抖动和

2021-05-08 11:35:15 5157

5157

接收灵敏度是指接收机能够处理的最小输入信号强度,通常以信噪比来衡量。

2023-11-05 09:55:05 7856

7856

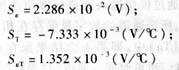

在《全面认知·霍尔元件》中, 我们介绍了三种霍尔元件:超高灵敏度霍尔元件, 高灵敏度霍尔元件和低漂移霍尔元件。

2025-07-10 14:25:36 1911

1911

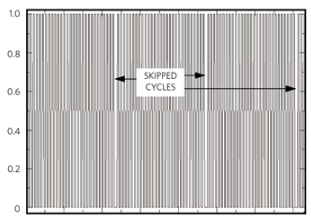

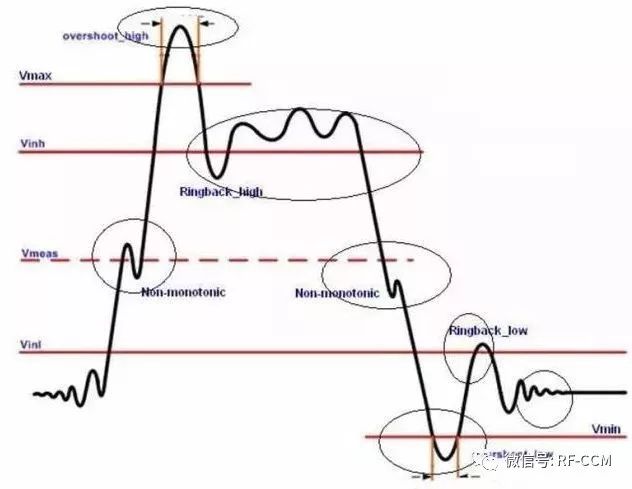

了。如果想稳定触发波形的上升沿,则需要在触发电平的上下范围内使用迟滞比较,以过滤触发电平附近的波形抖动和毛刺。这个迟滞范围就是触发灵敏度。当在测量小信号,或者没有明显噪声干扰的波形时,需要较高的触发灵敏度

2022-09-14 11:41:24

ADC电源分类及灵敏度分析

2021-03-11 06:31:11

CC3200的接收灵敏度可以更改吗?如果可以的话,在哪里更改呢?

2016-04-18 11:03:54

如果我想调整咖啡通道的灵敏度,是否只要调节手指阈值、噪声阈值、负噪声阈值就可以了。

2024-07-05 06:33:26

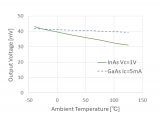

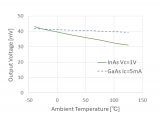

在应用笔记中指出:“磁传感器的灵敏度随着温度的变化而变化,引入温度补偿数字块来补偿温度的影响。”这种针对灵敏度的温度补偿是否需要由用户实施?另外,即使温度传感器被禁用,补偿是否起作用?

2023-02-06 06:56:12

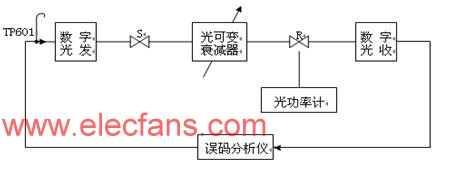

测试方法:测试方法如图,因为PCB本身辐射会大幅影响测试结果,所以设备除了需要放置在屏蔽箱中外,还需要有一定物理间隔(推荐分别放在两个房间里)。测试时,通过固定衰减器将链路衰减固定到接近目标灵敏度

2019-01-14 12:02:08

在multisim中做灵敏度分析的时候,结果中没有电容的灵敏度结果,不知道是为什么,并且结果中每一个器件后面的数字和灵敏度怎么对应呢?

2019-10-24 20:34:59

以帮助设计师自动优化电路性能。PSpice AA提供的高级分析方法包括灵敏度分析、电应力分析、成品率分析、蒙特卡罗分析、以及优化分析,它是在PSpice A/D分析的基础上,最大程度的提高所设计电路

2012-02-15 10:25:49

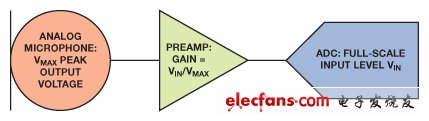

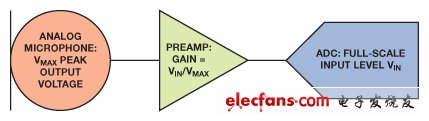

模拟音频信号电平。然而,数字麦克风的灵敏度和输出电平却表示为峰值电平,因为它们是以满量程数字字(即峰值)为参考的。一般来说,在配置可能依赖于精确信号电平的下游信号处理时,必须记住用峰值电平指定数字麦克风

2018-10-22 16:57:17

如果传感器的灵敏度为1mV/V,那么在5VDC激励电源作用下,传感器在额定载荷时的输出信号应该为:Uout=S*Uin=1mV/V*5V=5mV如果传感器的灵敏度为2mV/V,那么在5VDC激励电源

2014-07-26 10:11:24

关于接收机灵敏度[ 问题 ]karen:想做一个关于无线功率控制的算法,要用到接收机灵敏度的概念,我看文献时对这个概念的理解就是无线接收机刚好能正确判决的最小功率值。但是在opnet 的无线接收机

2009-06-14 18:05:26

基站侦听口灵敏度和基站参考灵敏度有何区别?

2016-05-16 09:33:01

用驻极体采集声音,我想知道声压级和驻极体输出电压的对应关系,驻极体灵敏度只有一个范围,怎么能得到准确的灵敏度。。。求大神指教

2013-08-19 12:02:05

您好,我用CC2430组建的星状网络,现在想减小主节点识别范围(子节点发送接收指标不变),想知道如何合理的降低主节点接收灵敏度?谢谢!

2018-06-21 02:57:01

如何理解麦克风的灵敏度规格,如何将其应用到系统的增益级中?

2021-06-02 07:11:07

如何测试LoRa的接收灵敏度呢?LoRa传输数据用加密算法吗?

2022-01-20 06:34:32

如题,如何设置zigbee的接收灵敏度?

2016-03-30 15:04:01

请问各位一个问题,驻极体麦克风的灵敏度可以通过调整外部偏置电阻来调整,百度查看原理是这么解释的:MIC内部设计,可以简单理解为一个电容,电容的一端是固定的,另一端是可动的,两端之间的距离和声音输入

2019-04-10 09:21:38

扬声器的灵敏度(dB/W)通常是指输入功率为1W的噪声电压时,在扬声器轴向正面1m处所测得的声压大小。灵敏度是衡量扬声器对音频信号中的细节能否巨细无遗地重放的指标。灵敏度越高,则扬声器对音频信号中所有细节均能作出的响应。作为Hi-Fi扬声器的灵敏度应大于86dB/W。

2019-05-22 08:47:44

指针式万用表 灵敏度的概念我理解,但数字万用表灵敏度有何含义,实验室买的8.5位数字万用表3458A,直流电压最高灵敏度为10nv,最高分辨率也为10nv,灵敏度,在万用表里分辨率,灵敏度他两是不是一个意思

2014-08-25 17:54:43

0 引言RFID标签芯片的灵敏度是芯片刚刚被激活所需的最小能量。灵敏度是标签芯片最重要的性能指标,它的大小直接影响RFID标签的性能,例如标签读/写距离等。因此标签芯片灵敏度准确测试是芯片测试

2019-07-26 07:42:54

`想要知道无线模块的接收灵敏度是用什么仪器测量的?有的无线模块为什么有的比无线芯片本身的灵敏度还高?、求高手解答?、`

2012-08-13 10:49:13

温度变化如何影响灵敏度?以上来自于谷歌翻译以下为原文 How does temperature changes affect sensitivity?

2018-09-18 16:46:58

请问老师,示波器灵敏度下降,原因自查发现了测过10A12VLeD电源主回路,对数字示波器的量限不明,是看不懂英文,数字示波器连接PC电脑显示,我下载了ni这步了,波形分析,对我帮助很大,谢谢老师!

2022-11-18 03:28:47

怎么解决触摸灵敏度和误触发之间的矛盾?

2012-11-22 14:02:45

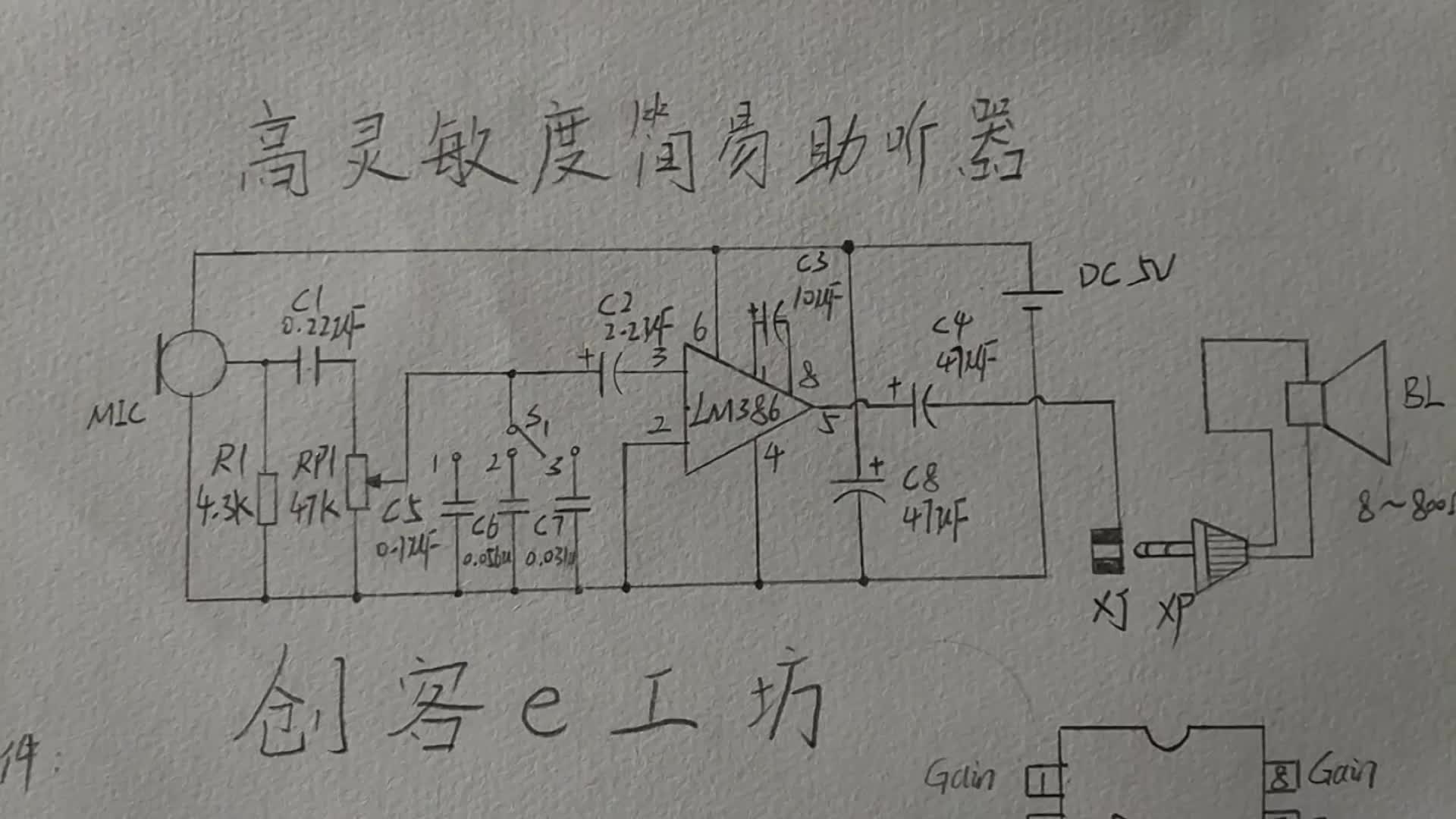

在做个声控延时开关, 灵敏度一直调不理想。如图左边的圆是 压电陶瓷蜂鸣片, 接到反相器上,并联电阻。一开始灵敏度很高,没声音(除了外面的声音,但是已经是晚上了)也会亮。时间到了自动灭掉后,马上

2012-03-03 09:28:21

在12dB SAND下,解调100MHZ的AM音频信号,接收灵敏度可以到-110dBm吗?接LNA可以到这个灵敏度吗?

2018-07-31 09:31:39

大家好!

请教一下CC1101的接收灵敏度能不能用安捷伦的E4432B检测出它的接收灵敏度的,如果行,那具体要怎么做?

2018-05-15 01:48:25

想在ch552触摸按键上,加一块亚克力,发现灵敏度不行,2mm的亚克力都不行,请如何调高触摸灵敏度呢?

2022-06-30 06:21:42

作者: Jerad Lewis灵敏度, 即模拟输出电压或数字输出值与输入压力之比,对任何麦克风来说都是一项关键指标。在输入已知的情况下,从声域单元到电域单元的映射决定麦克风输出信号的幅度。 本文将

2019-07-23 07:51:21

GPS 接收机的灵敏度是影响GPS 应用范围的非常关键的指标,目前业界纷纷推出高灵敏度的GPS 接收系统,使得GPS 的室内定位成为可能,大大拓展了GPS 的应用场景。本文对GPS 接收机

2009-11-12 14:41:41 23

23

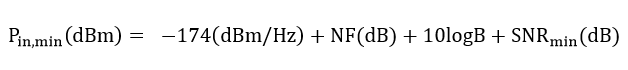

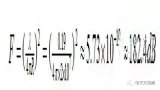

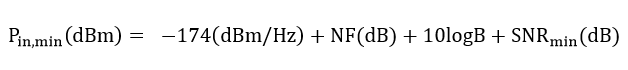

扩频系统的接收机灵敏度方程

本应用笔记论述了扩频系统灵敏度的定义以

2006-05-07 13:43:16 1200

1200 接收机灵敏度的研究

无线电接收机诸多的性能当中,「灵敏度」 (Sensitivity)

2009-03-15 11:04:08 2358

2358 接收灵敏度的定义公式

摘要:本应用笔记论述了扩频系统灵敏度的定义以及计算数字通信接收机灵敏度的方法。本文提供了接收

2009-04-25 09:42:53 15762

15762

什么是接收灵敏度

摘要:本应用笔记论述了扩频系统灵敏度的定义以及计算数字通信接收机灵敏度的方法。本文提供了接收机灵敏度方程的逐步推

2009-05-08 10:46:51 4753

4753

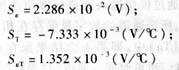

压阻式传感器的应变与温度交叉灵敏度分析

运用二元函数的泰勒展开式给出了应变与温度交叉灵敏度大小的公式,阐明了其物理意义,并结合实际测量数据估计了交叉

2009-10-13 19:13:47 1595

1595

传感器的灵敏度

2009-12-01 13:45:17 1117

1117 耳机灵敏度

2009-12-28 14:13:24 10772

10772 蓝牙的灵敏度

保证达到所要求的误比特率的条件下,接收所需要的最小输入功率。接收灵敏度一般用dBm来表示,它是以lmW光功率为基础的绝对

2009-12-28 14:51:02 7553

7553 蓝牙适配器的灵敏度

在保证达到所要求的误比特率的条件下,接收所需要的最小输入功率。接收灵敏度一般用dBm来表示,它是以lmW光功率为基

2010-01-06 13:50:24 1667

1667 对讲机灵敏度是否越高越好

灵敏度并非越高越好

有人经常常吹嘘灵敏度越高越好,然而

2010-02-08 08:48:44 8442

8442 车载扬声器的灵敏度 灵敏度又称声压级,是衡量车载扬声器是否容易推动时相当重要的指标,是指给

2010-01-04 11:45:37 1503

1503

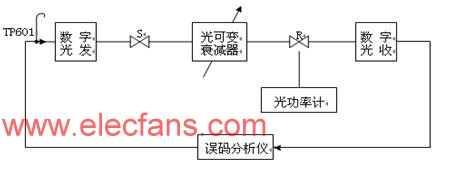

光接收机灵敏度测试实验

一 实验目的 1 理解光接收机灵敏度的概念 2 掌握光接收机灵敏度的测试方法

二

2010-08-22 09:37:23 13298

13298

在收录机、电话机等电器中广泛应用的驻极体话筒,其灵敏度直接影响送话和录放效果。这类话筒灵敏度的高低可用万用表进行简单测试。

2011-02-15 11:26:03 7227

7227 本文将探讨模拟麦克风与数字麦克风在灵敏度规格方面的差异,如何根据具体应用选择灵敏度最佳的麦克风,同时还会讨论为什么增加一位(或更多)数字增益可以增强麦克风信号。

2012-07-09 16:17:00 30071

30071

GPS 测试中的一项重要因素是接收器的灵敏度。主要测试内容是捕获灵敏度和跟踪灵敏度。一般而言,地基天线接收到的 RF(射频)功率水平介于 -125dBm 至 -150dBm 之间,具体取决于环境因素。

2016-01-11 15:35:12 8248

8248

基于可拓云模型的配电网经济运行综合评价及灵敏度分析_马丽叶

2017-01-05 15:34:14 0

0 传输线网络瞬态响应灵敏度分析_赵进全

2017-01-07 16:00:43 0

0 基于灵敏度分析及Volterra级数的非线性模拟电路故障诊断_韩海涛

2017-01-07 16:24:52 8

8 接收灵敏度的定义公式 摘要:本应用笔记论述了扩频系统灵敏度的定义以及计算数字通信接收机灵敏度的方法。本文提供了接收机灵敏度方程的逐步推导过程,还包括具体数字的实例,以便验证其数学定义。 在扩频

2017-12-07 20:31:12 4000

4000

根据GPS 接收机的定位原理和GPS 接收机灵敏度分析接收机性能, 发现灵敏度主要与前端电路和基带有着密切关系。据此对GPS 的天线前端电路设计滤波器和低噪声放大器, 并对电路的其他方面提出要求

2017-12-10 05:59:05 9690

9690 为解决航空液压系统高速高压化发展带来的航空液压管路振动加剧问题,将液压管路与管路支架视为整体振动系统。基于灵敏度分析方法,采用ANSYS软件平台中的灵敏度分析工具,分析航空液压管路支架参数对振动响应

2018-03-06 16:10:47 0

0 目前已有利用变压器绕组电气参数检测绕组变形的方法,但对电气参数变化与绕组变形之间的联系的研究还不够深入。为此,提出一种分析绕组电气参数对不同种类变形的全局灵敏度方法。该方法首先采用响应面法,建立显式

2018-04-10 14:49:19 1

1 接收机灵敏度是指接收机能够输出规定信噪比(S/N)的信号时,该接收机输入端的最小输入信号Smin;一般定义为最小信噪比与平均噪声功率的乘积,如式1所示。若从天线端的输入信号考虑,天线(系统级)灵敏度称为最小工作灵敏度或系统灵敏度,如式2所示。

2018-07-13 17:06:41 40980

40980

随着GPS 应用范围的不断扩展,对GPS 接收机的灵敏度要求也越来越高,高灵敏度的接收性能可以令接收机在室内或其它卫星信号较弱的场景下仍然能够实现定位和跟踪,大大拓展了GPS 的使用范围。

2019-05-05 15:37:51 16082

16082

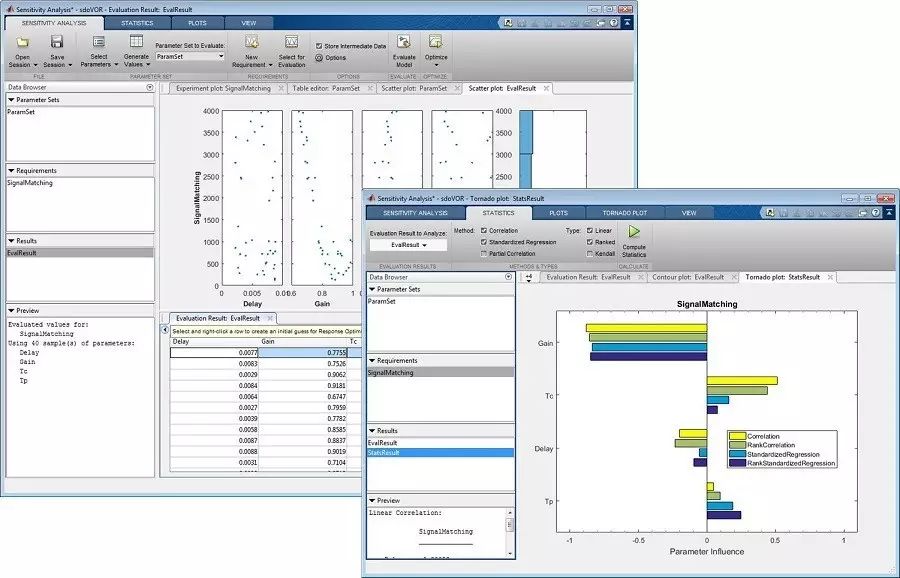

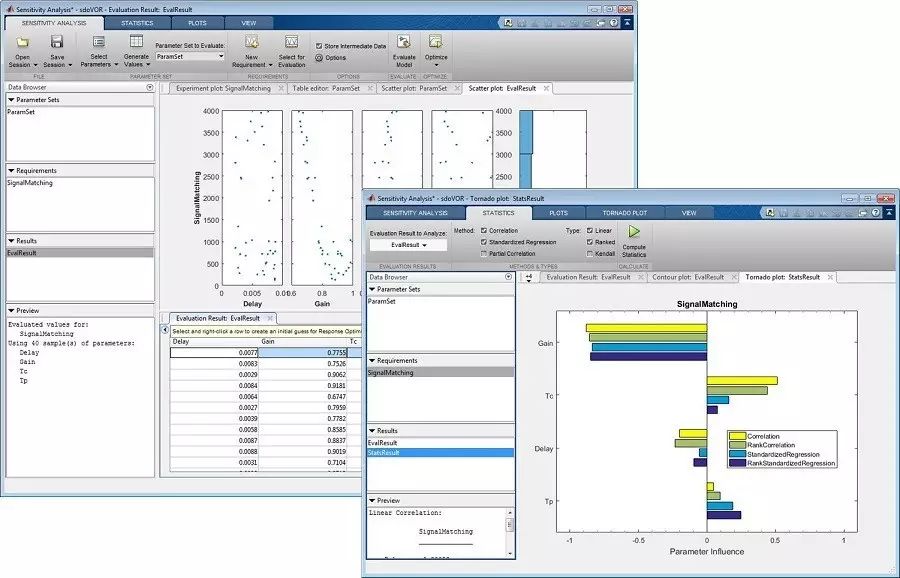

设计工程人员可直接利用灵敏度分析结果改进设计、提高数值优化任务的性能,如依据测试数据进行模型拟合、调试模型来满足设计需求等。Simulink Fast Restart和Parallel Computing Toolbox有助于提升灵敏度分析工具的性能。

2019-09-17 14:33:32 4189

4189

GPS 接收机的灵敏度是影响GPS 应用范围的非常关键的指标,目前业界纷纷推出高灵敏度的GPS 接收系统,使得GPS 的室内定位成为可能,大大拓展了GPS 的应用场景。本文对GPS 接收机的灵敏度性能进行原理性分析,并给出了设计高灵敏度GPS 接收模块的建议。

2020-01-07 16:49:25 17

17 感应灯的灵敏度是可以调的。里边有个调节灵敏度的可调电阻,注意用电安全,一定要断电。

2020-04-07 10:10:47 51243

51243 灵敏度指示器的相对于被测量变化的位移率,灵敏度是衡量物理仪器的一个标志,特别是电学仪器注重仪器灵敏度的提高。通过灵敏度的研究可加深对仪表的构造和原理的理解。

2020-05-28 09:52:22 12993

12993 提高收音机的灵敏度的工作可以分为两个阶段,一是设计者和生产厂家从电路、工艺、结构等多因素入手来生产高灵敏度的收音机。另一方面是对于消费者已经买到手的收音机如何提高灵敏度问题。

2020-12-05 16:34:00 21472

21472 2022-11-17 12:42:30 1

1 以下应用笔记深入探讨了如何定义扩频应用的灵敏度,以及如何计算数字通信接收机所需的灵敏度水平。本技术论文逐步介绍了接收机灵敏度方程的发展,并以数值示例结束,并对其数学定义进行了测试。

2023-02-23 17:31:18 3278

3278

本应用笔记论述了扩频系统灵敏度的定义以及计算数字通信接收机灵敏度的方法。本文提供了接收机灵敏度方程的逐步推导过程,还包括具体数字的实例,以便验证其数学定义。

2023-06-08 16:55:57 2121

2121

无线模块的灵敏度越高越好吗?在回答这个问题前,思为无线小编先简单介绍一下灵敏度到底是什么,接收灵敏度是无线模块中非常重要的一项参数,灵敏度是以负值为单位,负值越小,则代表接收灵敏越高。灵敏度在无线模块接收数据时才会发生效用的一个功能,所以灵敏度一般也叫接收灵敏度。

2021-09-10 11:30:39 3951

3951

灵敏度在无线模块中是一项非常重要的参数,在无线通讯领域中,接收灵敏度就好比人类的听力一样,提高信号的接收灵敏度可使无线产品具有更强地捕获弱信号的能力。当传输距离越远时,信号就会越弱,这时灵敏度高

2021-09-13 11:33:57 4705

4705

**De-sense,** 中文是脱敏,意思是干扰灵敏度的一些谐波,杂讯之类的。通常是在讨论天线灵敏度这块用的比较多。

2023-06-30 14:57:14 1909

1909

柔性传感器的灵敏度多少算高?传感器灵敏度大小与灵敏系数的关系 柔性传感器的应用范围非常广泛,灵敏度大小是衡量其性能优劣的重要指标之一。传感器灵敏度越高,能够检测到的微小变化就越多,精度也就

2023-10-24 11:49:07 4658

4658 怎么来看开关型霍尔元件的灵敏度呢? 开关型霍尔元件是一种常用的传感器元件,用于检测磁场中的变化。它可以在磁场强度达到一定阈值时切换输出状态,从而实现开关的功能。在实际应用中,了解和评估霍尔元件

2023-12-18 15:02:49 4058

4058 频谱分析仪的灵敏度是指在一定的信噪比(SNR)或比特误码率的情况下可测量到的最小信号电平。这一指标关系到仪表对弱信号的检测能力。具体来说,频谱分析仪的灵敏度定义为它所显示的平均噪声电平(DANL

2024-05-08 16:11:49 1884

1884 电子发烧友网站提供《电源设计的灵敏度分析.pdf》资料免费下载

2024-10-10 11:04:14 0

0 dBm与功率灵敏度关系

2025-02-14 16:35:14 0

0 发展。作为无线通信测试中不可或缺的核心工具,信号分析仪的灵敏度对于低电平信号的检测能力和系统性能验证至关重要。因此,提升信号分析仪的性能成为满足当前测试要求的关键

2025-02-28 11:25:15 1294

1294

电子发烧友App

电子发烧友App

评论