Ian Beavers

对于需要一系列同步模数转换器(ADC)的高速信号采样和处理应用,校正和匹配转换器之间的延迟变化的能力至关重要。围绕此功能的系统设计至关重要,因为从模拟采样点到处理模块的任何延迟不匹配都会降低性能。交错处理也需要样本对齐,其中一个转换器样本领先另一个转换器样本几分之一时钟周期。

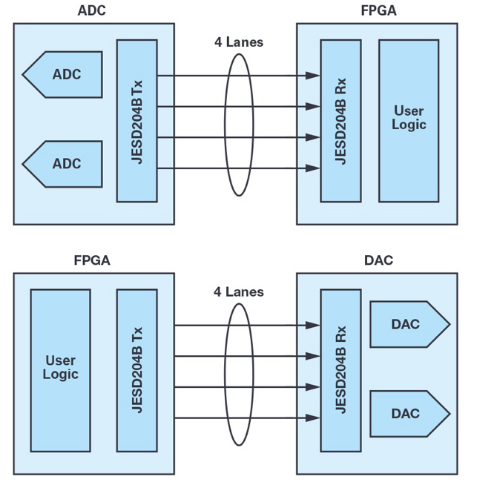

JESD204B第三代高速串行转换器接口的主要特性之一是能够为系统中的每个转换器建立确定性延迟。正确理解和使用此功能后,它可以在单个系统中的多个ADC之间创建同步或交错采样系统。

由于确定性延迟是一种相对较新的转换器接口特性,系统设计人员通常会对如何建立它、感兴趣的信号以及如何实现同步或交错处理有几个问题。以下是设计具有确定性延迟的系统的一些常见问题和答案,该系统与FPGA一起采样的多个JESD204B转换器。

什么是确定性延迟,JESD204B如何定义它?

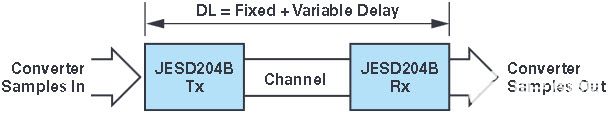

JESD204B链路上的确定性延迟由串行数据从发射器(ADC或源FPGA)的并行成帧数据输入传播到接收器(数模转换器或DAC或接收器FPGA)的并行成帧数据输出所需的时间来定义。这个时间通常是 以分辨率的帧时钟周期或设备时钟测量。

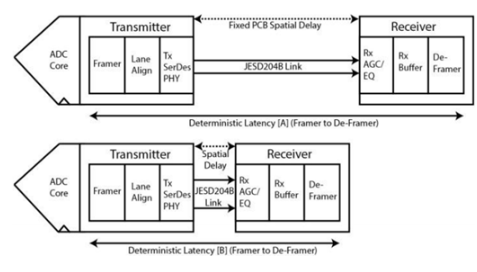

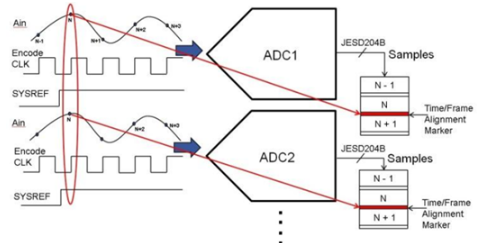

JESD204B的确定性延迟规范未考虑ADC的模拟前端内核或DAC的后端模拟内核。它仅基于进出JESD204B数字成帧的数据。在此延迟计算中,不仅两个有源设备是一个函数,而且连接两者的空间信号路由也是如此。这意味着在多转换器系统中,每个链路的确定性延迟可能更大或更小,具体取决于JESD204B通道路由的空间长度及其各自的延迟。接收器上的缓冲延迟有助于解决路由引起的延迟差异(图 1)。

图1.JESD204B在两个器件之间的确定性延迟将基于三个分量:从发射器成帧器到输出的延迟、空间路由延迟以及从输入到解码器的接收器延迟。来自同一系统中两个不同ADC的数据可能各自具有自己独特的确定性延迟。

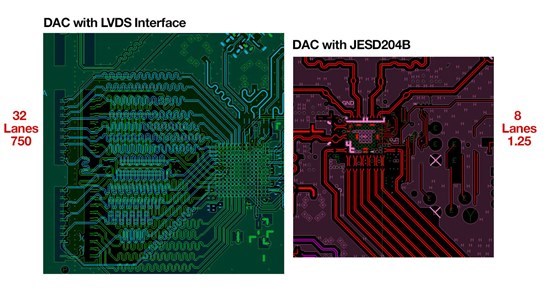

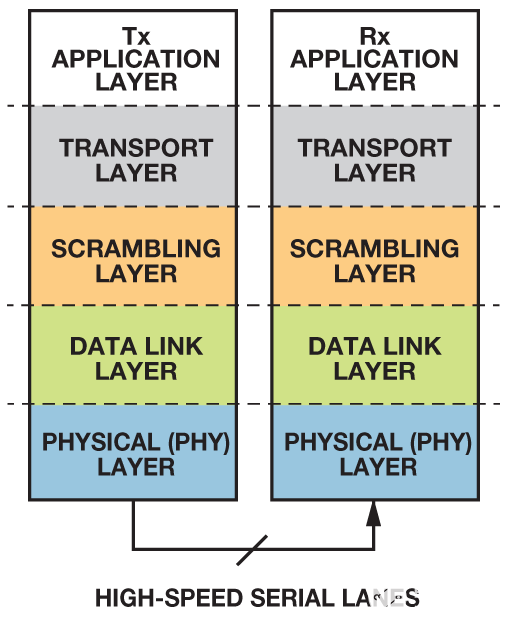

与低压差分信号(LVDS)等简单的串行链路配置不同,JESD204B接口将数据样本打包到定义的帧中。在来自发射器的链路握手或初始通道对齐序列 (ILAS) 期间,一对或几个样本的每个帧边界由一个特殊的控制字符标记。在 ILAS 期间,一个较大的已定义帧组(称为多帧)也用相应的控制字符进行标记。但是,在此序列完成后,不需要控制字符,并且可以获取链路的全部带宽。帧和多帧边界分别与帧时钟和多帧时钟重合。

JESD204子类与确定性延迟的关系是什么意思?

JESD204B协议有三个子类来定义链路的确定性延迟。子类 0 向后兼容 JESD204 和 JESD204A,不支持确定性延迟。子类 1 通过使用称为 SYSREF 的系统参考信号来支持确定性延迟。子类 2 通过双重用途使用 ~SYNC 信号来支持确定性延迟,这也允许接收器启动握手 ILAS 例程。相对于时钟在时间上准确放置 SYSREF 与 ~SYNC 的能力将决定感兴趣的系统需要哪个子类。

如何使用确定性延迟来调整多个转换器之间的采样?

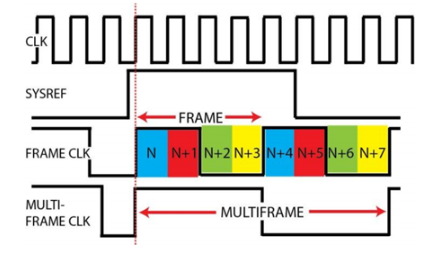

对于子类1转换器实现,帧时钟和多帧时钟在每个器件上通过系统参考边沿SYSREF的出现而内部对齐。当检测到 SYSREF 边沿时,这两个时钟都与该时间点对齐。由于这些时钟保留在每个设备内部,因此它们在发射器内的边界通过使用控制字符通过串行链路进行通信。

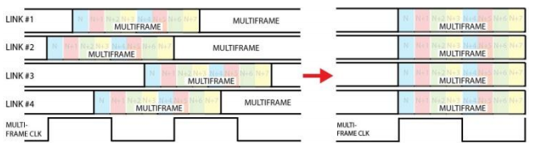

每个接收器都可以隐式解码发射器帧和多帧时钟相对于其自己的同名时钟以及相对于所有发射设备的时间位置。这使得接收器能够使用缓冲延迟在相对较早的数据到达时对样本进行纠偏,以将链路与最新到达的数据相匹配(图 2)。

图2.在JESD204B发送器中,时钟锁存系统参考(SYSREF)边沿后,样本与帧和多帧时钟对齐。出于视觉目的,此处将多帧定义为仅包含八个样本。

对于同步采样,这些数据链路可以在FPGA内及时对齐。对于交错采样,每个链路都可以通过其相应的相对相位延迟来抵消。通过测量从接收器的多帧时钟边沿到每个链路的多帧控制特性的时间延迟,可以识别每个链路的确定性延迟。需要注意的是,每个链路的确定性延迟必须短于多帧时钟周期的持续时间(图 3)。

图3.来自四个JESD204B发送器的多帧样本通过使用缓冲延迟与接收器内的多帧时钟对齐。

确定性延迟是否与转换器总延迟相同?

ADC的总延迟是模拟采样从器件进行计时、处理和数字输出所需的时间。类似地,DAC的总延迟是从数字采样数据时钟输入器件到相应采样从模拟输出时钟出来的时间。通常,它们都是在分辨率的采样时钟周期中测量的,因为它们与频率有关。它部分取决于单个转换器组件中的模拟处理架构。从根本上说,这与JESD204B链路实现所描述的确定性延迟的定义不同,后者是三个组件的函数。

对齐多个转换器的最大纠偏预算是多少?

在ILAS过程中,发射器发送多帧控制字符以标记多帧时钟边界。接收器识别这些字符以创建自己的内部本地多帧时钟,该时钟与上游链路中的每个发射器对齐。对于使用多个接收器的大型阵列系统,多帧时钟也在所有这些器件上对齐。因此,任何转换器链路的确定性延迟都不能超过单个多帧时钟周期的时间。这是跨链接的总纠偏时间预算。

多帧时钟的持续时间通常为数十个采样时钟周期。甚至可以通过在链路握手期间传达的设置参数变量将其调整为更长或更短。

此功能是否与ADC或DAC上的同一模拟采样点正确对齐,还是需要更多?

确定性延迟提供了一种根据提供给JESD204B成帧器的相同时间点对齐样本的方法。除了这段时间之外,ADC在JESD204B成帧器之前处理前端的模拟样本所需的时钟周期更多。转换器供应商必须在时钟持续时间上提前成帧器指定此时间段。相反,DAC在解帧器之后需要额外的时钟周期,以模拟形式将样本处理到输出。

在获得有效的模拟样品数据之前,对准过程需要多长时间?

发送到转换器和FPGA的SYSREF边沿会导致对齐过程开始。在此事件之后,除了ILAS序列外,还需要完成几个多帧时钟周期,然后才能获得有效的样本数据。这相当于许多采样时钟周期的相对时间。具体持续时间可能取决于转换器中JESD204B内核的独特确定性延迟,该值需要由供应商传达。在此期间,链接将被关闭,有效数据将不会传输。在绝对时间内,持续时间将是采样时钟频率的函数。

实现同步采样最具挑战性的系统设计方面是什么?

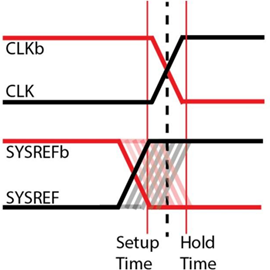

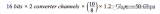

在子类 1 中实现同步或交错处理直至采样电平的最具挑战性的方面之一是能够在多个转换器之间及时对齐 SYSREF 的使能边沿。此外,每个SYSREF边沿都需要满足设置要求,并将时间保持到各自的采样时钟。这将消耗一些可用的时序裕量。主动和独立地偏斜SYSREF和时钟之间的精细相位的能力将有助于实现转换器之间的时序收敛。

SYSREF 是否需要是单个事件,还是可以重复发生?关于每个案例,我需要了解什么?

SYSREF 对准边沿可以是单脉冲、周期性、间隙周期性或重复非周期性。这将取决于系统的需求以及时钟和源头SYSREF之间相位偏差的时序灵活性。对于 SYSREF 的重复情况,帧和多帧 时钟将在每个事件上重新对齐。但是,由于目标是保持一组对齐的时钟,因此周期周期性 SYSREF 的使能沿应落在多帧时钟边界上。由于时钟应该已经在第一个 SYSREF 边沿之后对齐,这将防止不必要的重新对齐。

周期性SYSREF信号的不利影响之一是它有可能耦合到目标模拟信号上。这就是为什么并不总是建议使用周期性信号,并且只应在绝对必要时使用。如果使用周期性SYSREF,则必须注意将其与ADC的模拟前端正确隔离。

有哪些方法可以将 SYSREF 偏斜调整为在单个时钟周期内?

理想情况下,每个转换器和FPGA的SYSREF和时钟可以精确布线,时序裕量可满足所有组件的严格设置和保持时间。但是,随着高性能转换器采样速度的不断提高,仅靠精确的印刷电路板(PCB)布线并不总是能满足时序收敛。器件之间的引脚间差异,加上电源和温度漂移,会在一系列高速转换器上产生相对较大的时序偏差。可能需要高级时序调整功能来提供有源 SYSREF 相位偏斜。

例如,来自ADC的信息性警报可以识别SYSREF边沿是否在设置内锁定,并保持时序窗口。如果发生这种情况,则时钟边沿用于时序参考、时钟[N]或时钟[N+1]将存在歧义。根据检测到 SYSREF 边沿的位置,采样 CLK 边沿相对于 SYSREF 的相位可能会在时钟源处延迟,以保持满足建立和保持时间的有效时序条件。

另一种选择是使用采样时钟的下一个下降沿而不是上升沿来获得半个相位裕量周期。系统中的每个转换器都可以通过这种方式进行调谐,前提是时钟源对各自的 SYSREF 和 CLK 具有独立的相位调整(图 4)。

图4.为了在高速下实现低至样品电平的对齐,满足SYSREF相对于输入时钟的建立和保持时间可能具有挑战性。能够在相位早期偏斜每个SYSREF输入,以防止相对于其CLK的设置时间违规,有助于满足系统中多个转换器之间的时序收敛要求。

是否需要支持子类 1 或子类 2 的转换器才能使用确定性延迟功能?

子类1和子类2是唯一支持确定性延迟的子类,如JESD204B规范中所述。在子类 1 中,SYSREF 信号定义了确定性延迟。在子类 2 中,~SYNC 是定义此延迟的信号。一些转换器供应商创建了一个子类 0 实现,用于支持对齐样本的同步方案。在这种情况下,不使用转换器和FPGA之间多帧时钟的对齐过程

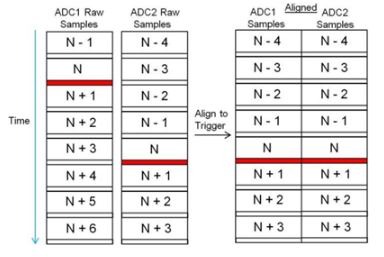

样本级别的时间戳机制可用于使用附加的辅助信息(称为控制位)来标记 SYSREF 的发生。与 SYSREF 边沿重合的每个样本都标有唯一的控制位。在 FPGA 中, 具有此时间戳的每个链路都可以延迟到等于最长路径,然后彼此对齐,与转换器之间的延迟差异无关(图 5 和图 6)。

图5.通过使用SYSREF控制位时间戳,可以在FGPA处理模块内实现子类0中的采样对齐,而不管从模拟输入到JESD204B输出的多个ADC之间是否存在任何实际延迟差异。

图6.通过使用附加的控制位作为与前端模拟输入重合的触发(红色),FPGA可以对齐来自不同延迟的信号链的样本。

总结

虽然确定性延迟是JESD204B的一个有点复杂的选项,但如果使用得当,它可以成为高性能信号处理系统设计的强大功能。来自ADC阵列的样本可以通过缓冲延迟在FPGA内对齐和纠偏,以实现同步或交错采样。JESD204B子类识别对于了解系统的时序对齐功能非常重要。系统ADC两端SYSREF和CLK输入引脚的时序收敛对于实现时间对齐采样至关重要。

审核编辑:郭婷

电子发烧友App

电子发烧友App

评论