几十年来,数据转换器一直是模拟现实世界和数字世界之间的桥梁。从占用多个机架空间并消耗大量功率的分立元件开始(如 11 W 的 DATRAC 50 位 500 kSPS 真空管 ADC),它们已经演变成高度集成的单片硅 IC [1]。自从第一个商用数据转换器问世以来,对更快数据速率的永不满足的需求意味着数据转换器的开发必须跟上步伐。ADC的最新化身是RF采样ADC,采样速度在GHz范围内。

架构开发的进步加上半导体技术的快速发展,使单片硅形式的模数转换器(ADC)得以实现。自1990年代以来,CMOS技术已经能够与构成数据转换器构建模块的分立模拟电路的质量保持同步。将构建模块集成到单片硅片中可实现更节能和节省空间的设计。现在,摩尔定律不仅适用于数字IC设计,也适用于模拟设计[2]。人们只需要观察过去二十年(1990年代中期至今)就能看到技术的快速增长。技术的这种增长刺激了对更快数据转换的需求,从而开发了带宽越来越高的数据转换器。

多年来,硅技术已经足够先进,现在可以经济地设计具有更强大数字处理功能的模数转换器(ADC)。早期ADC设计使用的数字电路很少,主要用于纠错和数字驱动器。新的GSPS(每秒千兆采样)转换器(也称为RF采样ADC)采用先进的65 nm CMOS技术,可以提供更多的数字处理能力,以增强ADC的性能。这使得数据转换器能够从1990年代中期和2000年代的ADC(大A,小D转换器)转变为ADC(小A,大D转换器)。这并不意味着模拟电路及其性能已经缩小,但数字电路的数量急剧增加,以补充模拟性能。这些附加功能允许ADC在ADC芯片中快速进行大量数字处理,并占用FPGA的部分数字处理负载。这为系统设计人员开辟了许多其他可能性。现在,使用这些新型先进GSPS ADC,系统设计人员只需为多个平台设计一个硬件,并有效地使用软件重新配置相同的硬件以适应新应用。

高速增强的数字处理

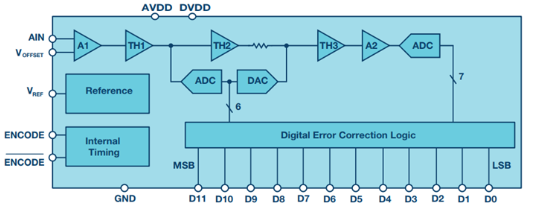

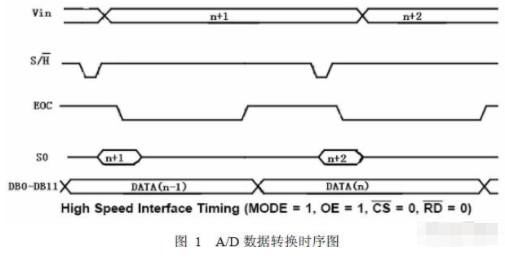

CMOS工艺中不断缩小的几何尺寸与先进的设计架构相结合,意味着ADC首次可以使用数字处理技术来提高其性能。这一突破是在1990年代初实现的,ADC设计人员自[1]以来就没有回头。随着硅工艺的改进(从0.5 μm,0.35 μm,0.18 μm和65 nm),转换速度提高。但是,随着几何形状的缩小,晶体管虽然越来越快(导致更高的带宽),但在模拟设计(如GM(跨导))的性能方面提供了略差的特性。这可以通过添加越来越多的校正逻辑来补偿。然而,硅仍然足够昂贵,以至于ADC内部的数字电路数量仍然相对适中。一个示例的框图如图 1 所示。

图1.具有最少数字纠错逻辑的早期单芯片ADC。

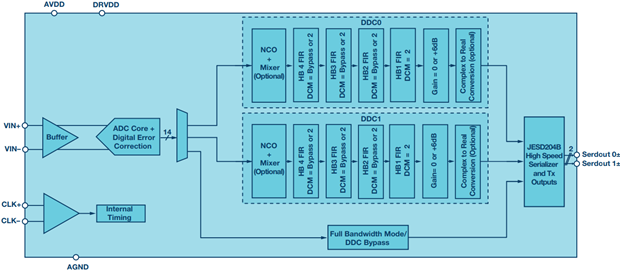

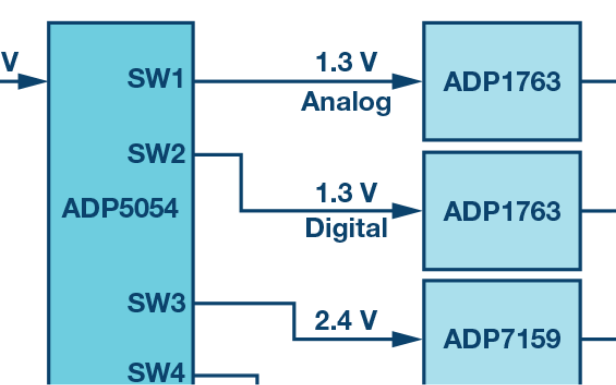

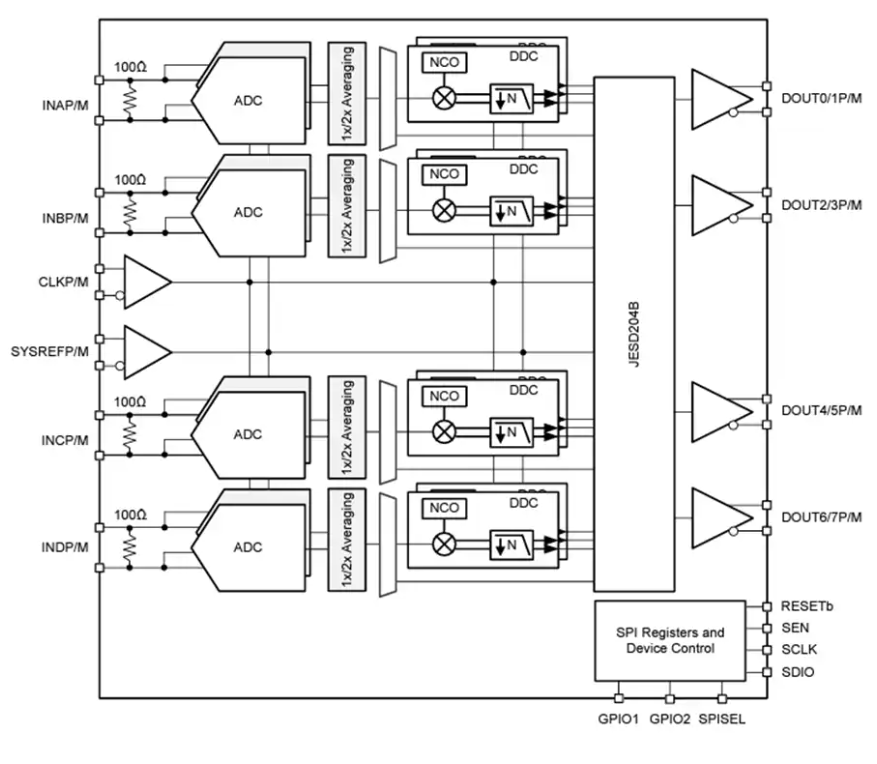

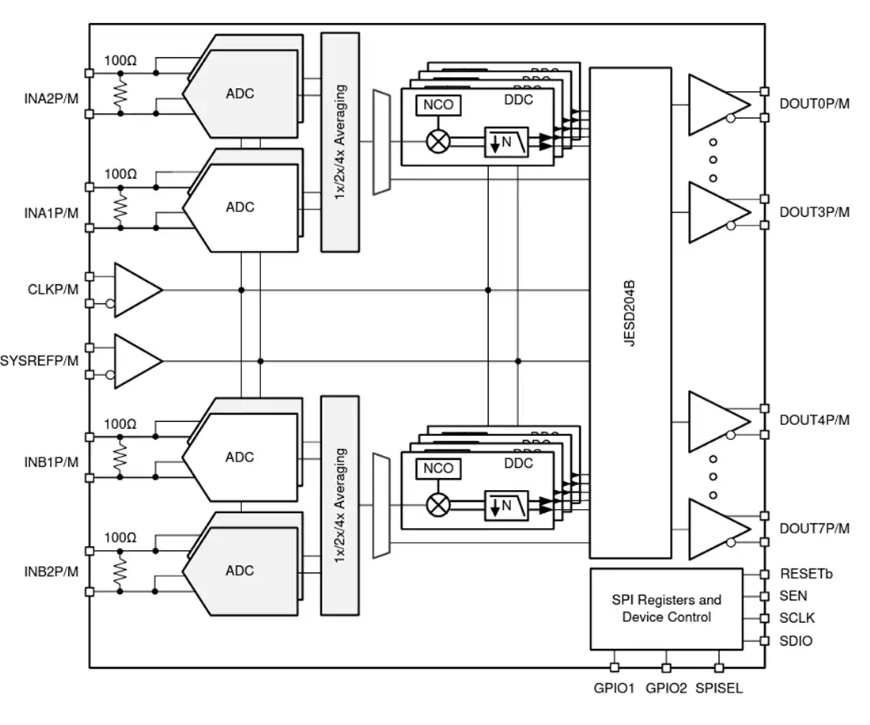

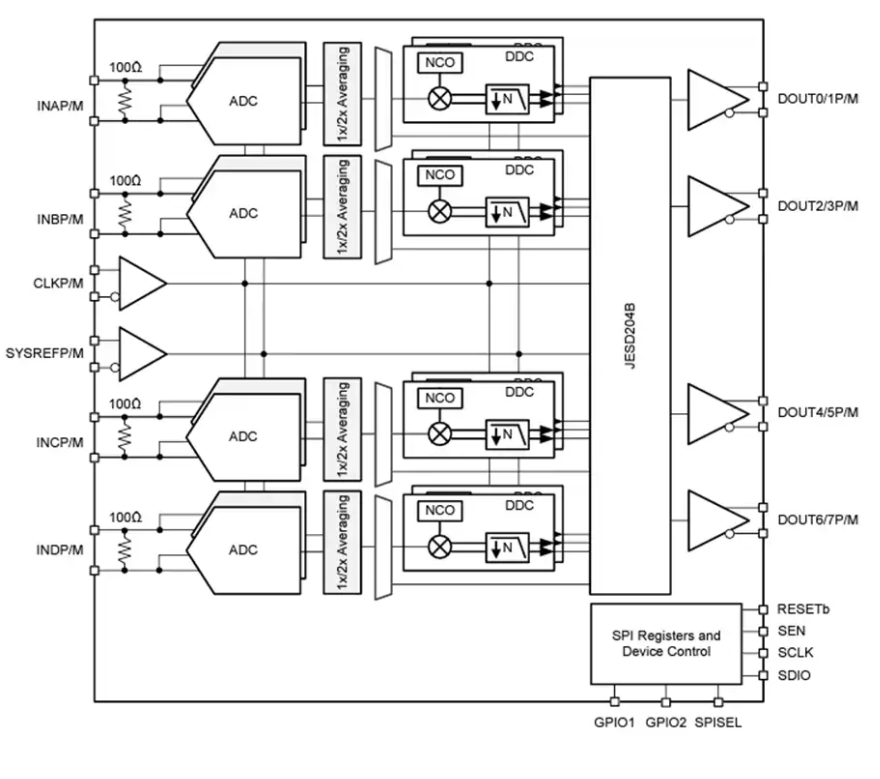

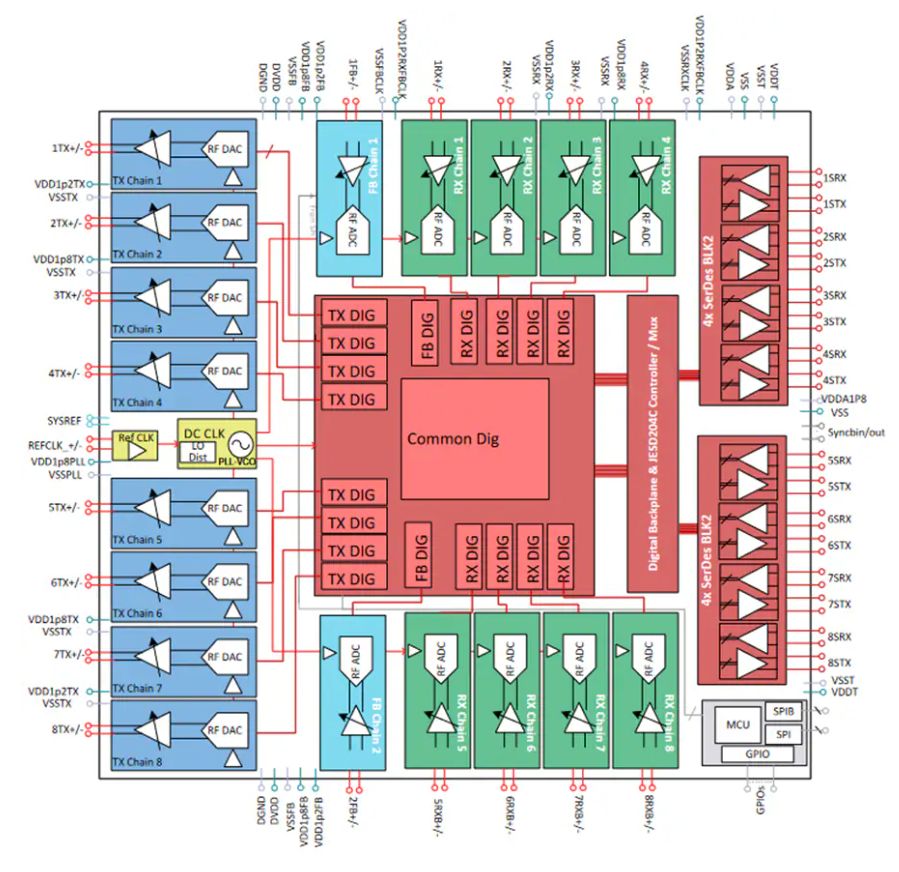

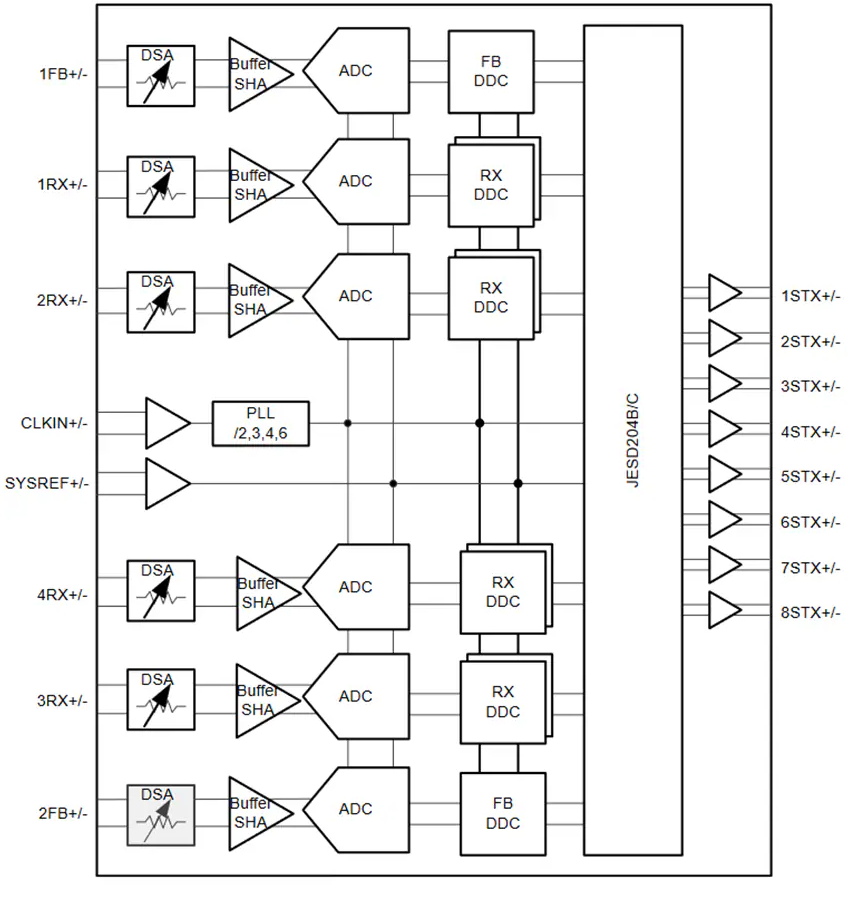

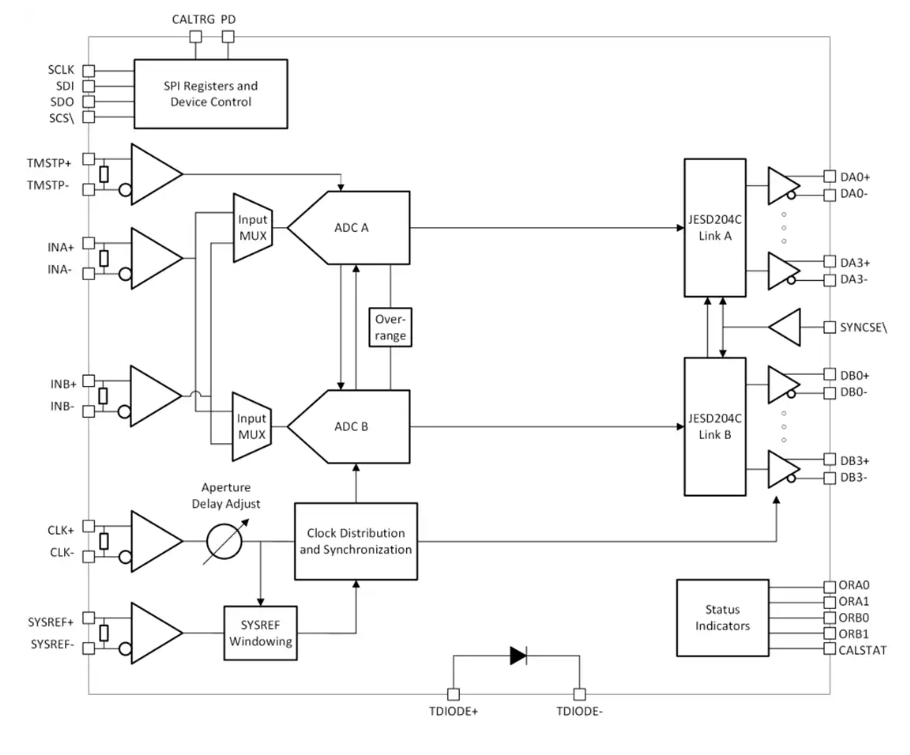

随着硅技术向 65 nm 等深亚微米几何形状的进步,规模经济使得在数据转换器中添加大量数字处理成为可能,此外还可以更快地运行内核(1 GSPS 或更高)[2]。这是二次检查的突破性进展。通常,数字信号处理由ASIC或FPGA处理,具体取决于系统性能和成本要求。ASIC是针对特定应用的,需要大量资金进行开发。因此,设计人员通常会长时间运行ASIC设计,以延长ASIC开发的投资回报。FPGA是ASIC的更便宜的替代品,不需要庞大的开发预算。然而,由于FPGA试图成为每个人的一切,其信号处理能力受到速度和功率效率的阻碍。这是可以理解的,因为它们提供了ASIC无法提供的灵活性和可重构性。图2显示了具有可配置数字处理模块的RF采样ADC(也称为GSPS ADC)的框图。

图2.带数字处理模块的 GSPS ADC。

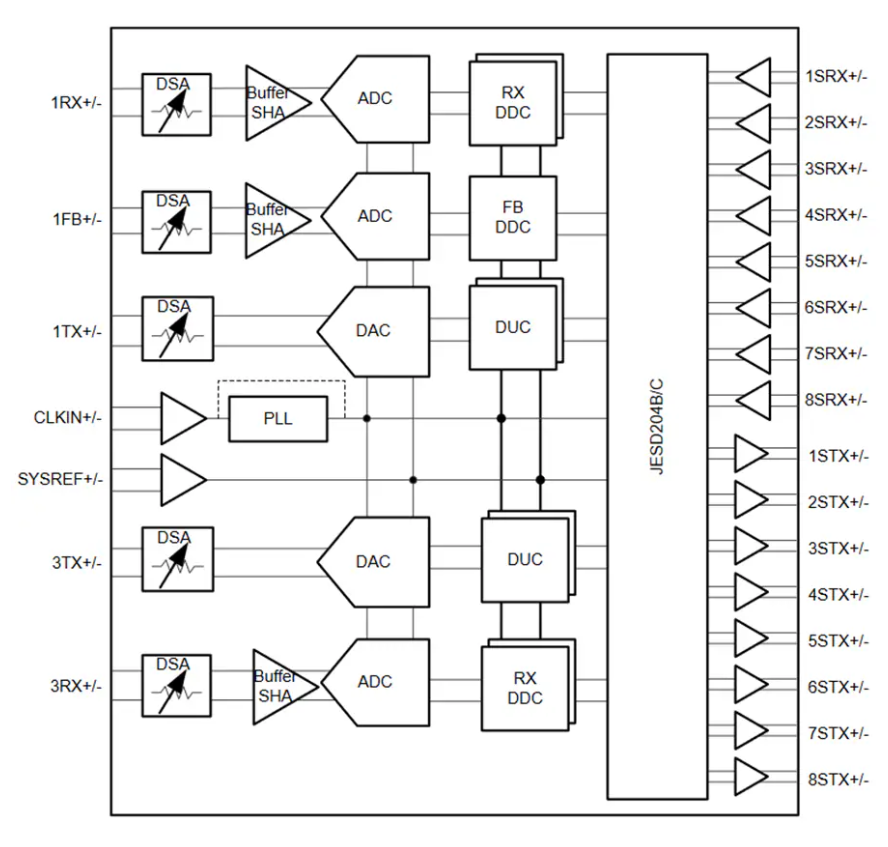

新一代GSPS ADC将彻底改变无线电设计,因为它们为设计表带来了很大的灵活性,其中一些将在下文中讨论:

高速数字处理

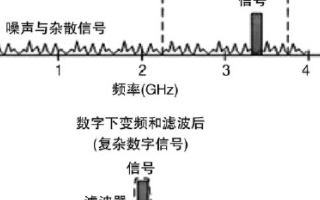

早期的无线电将使用模拟混频器和级联数字下变频器(DDC)的混合,以便将信号降低到基带进行处理。这涉及许多硬件(模拟混音)和电源(在ASIC/FPGA中的模拟和DDC中)。借助新一代RF采样ADC,DDC可以使用完全自定义的数字逻辑在ADC内部以一定速度运行。这意味着处理更加节能。

通过 JESD204B 实现 I/O 灵活性

新一代RF采样ADC不仅具有GSPS采样能力,而且还避开了高速串行接口的过时的LVDS输出。新的JEDEC JESD204B规范允许通过CML(电流模式逻辑)以每通道高达12.5 Gbps的高通道速率传输数字输出数据。这提供了高水平的 I/O 灵活性。例如,ADC可以在全带宽模式下工作,并在多个通道上传输数字数据,或者使用一个可用的DDC并在一个通道上传输抽取和处理的数据,只要输出通道速率保持在每通道12.5 Gbps以下。

可扩展的硬件设计

DDC 的使用在硬件设计方面提供了新的灵活性。系统设计人员现在可以冻结ADC和FPGA的硬件设计,只需进行最少的更改,就可以将系统重新配置为不同的带宽,只要ADC能够支持它。例如,无线电可以设计为全带宽ADC(RF采样ADC),或者使用可用的DDC设计为IF采样ADC(中频带ADC)。系统中唯一的变化是在RF侧,IF ADC可能需要一些最小的额外混频。大部分更改将发生在为新带宽配置ADC所需的软件中。但是,ADC + FPGA硬件设计几乎可以保持不变。这提供了一种参考硬件设计,可以满足许多平台及其要求,软件是唯一的变量。

其他附加功能

深亚微米CMOS工艺允许的高集成度迎来了一个时代,越来越多的功能被内置到ADC中。其中一些特性包括快速检测CMOS输出,可实现高效的AGC(自动增益控制)和信号监控(如峰值检波器)。所有这些特性都有助于减少外部元件和设计时间,从而有助于系统设计。

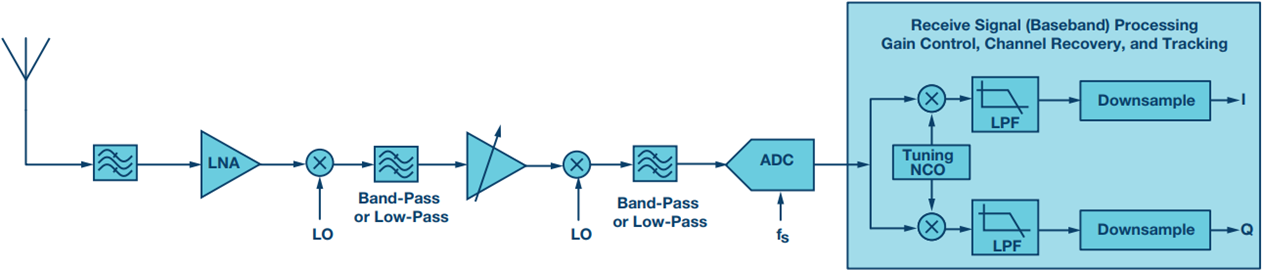

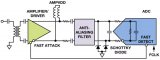

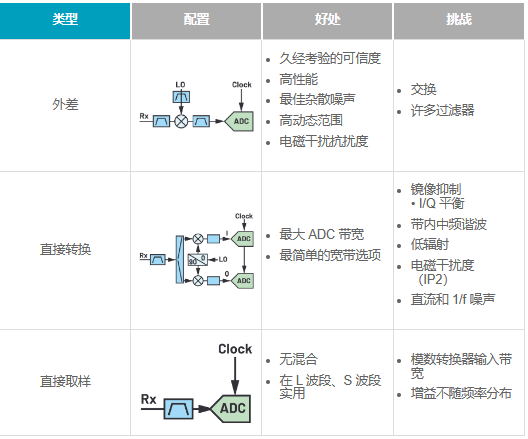

ADC的一个非常常见的用例是通信接收器系统设计。关于软件定义无线电(SDR)和使用ADC的通信接收器已经有许多出版物,这超出了本次讨论的范围。老一代无线电接收器的框图如图3所示[1]。

图3.用于蜂窝无线电的宽带数字接收器。

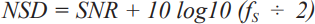

GSM 无线电接收器的正常规格要求 ADC 中的噪声频谱密度 (NSD) 至少为 153 dBFS/Hz 或更高。众所周知,NSD通过以下公式[3]连接到ADC的SNR:

其中:

信噪比以dBFS

f为单位s= ADC 采样速率

传统软件无线电设计

在宽带无线电应用中,一次采样和转换高达50 MHz的频段的情况并不少见。为了正确数字化50 MHz频段,ADC需要对至少五倍的带宽或至少~250 MHz进行采样。 将这些数字代入上述公式,ADC达到–153 dBFS/Hz的NSD规范所需的SNR约为72 dBFS。

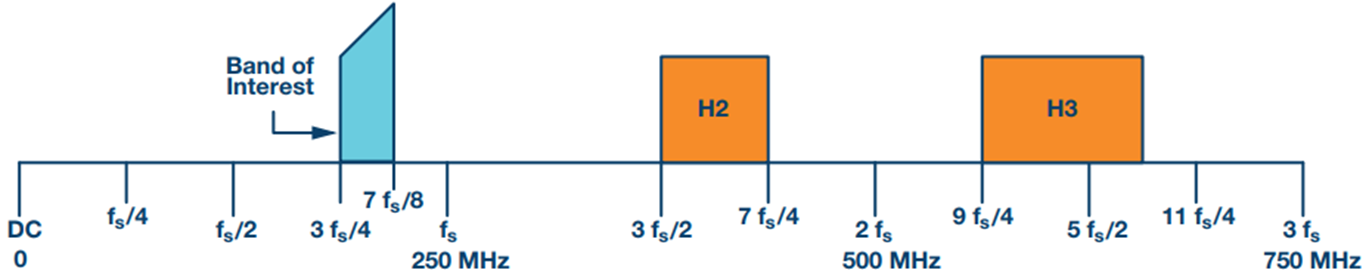

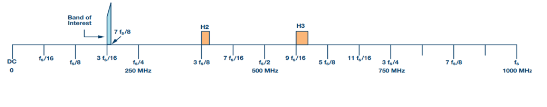

图4显示了使用50 MSPS ADC对250 MHz频段进行有效采样的频率规划。该图还显示了第二和第三谐波带的位置。

图4.使用 50 MSPS ADC 的 250 MHz 宽带无线电的频率规划。

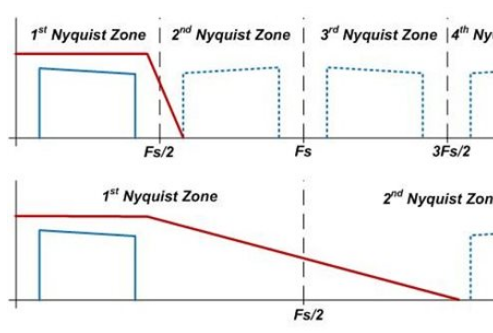

ADC的任何采样频率都将落在ADC的第一奈奎斯特(DC – 125 MHz)频段。这种现象称为混叠,因此包括目标频段在内的频率,其二次和三次谐波有效地折返或混叠到第一奈奎斯特频段。如图 5 所示,如下所示:

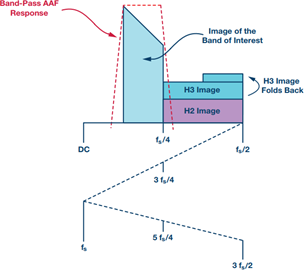

图5.第一奈奎斯特所示的可用频段,具有二次和三次谐波。

除NSD规范外,GSM、LTE和LTE-A等蜂窝通信标准对SFDR(无杂散动态范围)也有其他严格的要求。该规范给前端设计带来了很大的压力,因为前端设计能够在对目标频带中的信号进行采样时衰减不需要的信号。

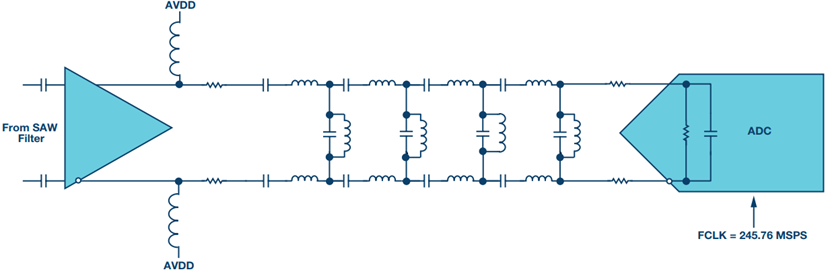

牢记SFDR规范,传统无线电前端设计的抗混叠滤波器要求变得非常难以满足。满足SFDR规范的最佳抗混叠滤波器(AAF)解决方案是实现带通滤波器。通常,这些带通滤波器的数量级为五个或更高。能够满足此类应用的SNR(或NSD)和SFDR要求的合适ADC是AD9467,16位、250 MSPS模数转换器[4]。使用AD9467的蜂窝无线电应用的前端设计如图6所示。

图6.前端设计显示放大器、抗混叠滤波器和250 MSPS时的ADC。

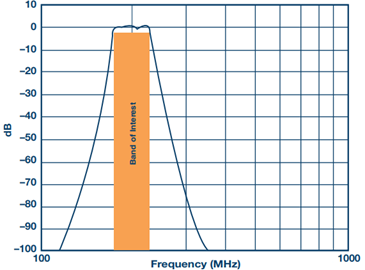

满足SFDR要求的AAF的频率响应如图7所示。该系统的实现并非不可能,但带来了许多设计挑战。带通滤波器是最难实现的滤波器之一,因为它涉及许多组件。在这种情况下,元件选择是关键,因为元件之间的任何不匹配都会导致ADC输出中出现不必要的杂散(SFDR)。除了复杂性之外,任何阻抗不匹配都会影响滤波器的增益平坦度。为了优化该滤波器设计以满足通带平坦度和阻带抑制要求,需要进行大量的设计工作。

图7.前端的带通响应如图6所示。

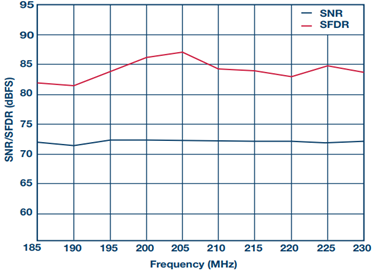

虽然这种无线电设计的前端实现可能很复杂,但确实可以工作,如跨频率图的SNR/SFDR性能所示(如图8所示)。205 MHz时的FFT如图9所示。但是,系统实现因以下原因而变得复杂:

过滤器设计。

FPGA必须专用I/O端口来捕获LVDS数据(16对),这使得PCB设计变得复杂。

在FPGA中留出额外的处理能力用于数字信号处理。

图8.图16所示的250位、6 MSPS ADC设计的SNR/SFDR与频率的关系。

图9.205 MHz 时的 FFT,适用于图 16 所示的 250 位、6 MSPS ADC 设计。

RF采样ADC简化并加快设计

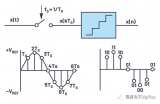

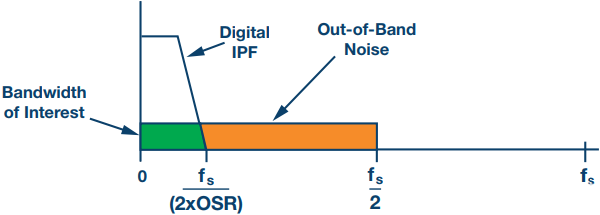

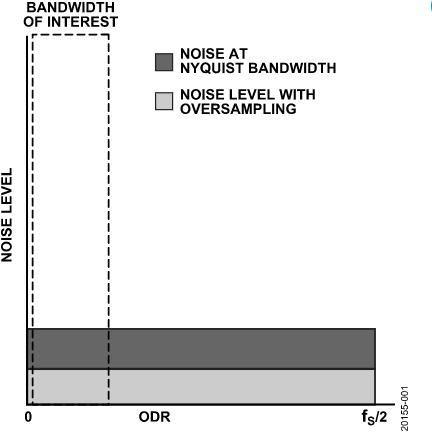

RF采样ADC方法使用过采样然后抽取数据以改善动态范围的技术[5]。深亚微米CMOS技术提供的速度优势与密集的数字集成能力相结合,催生了RF采样ADC的新时代,它可以完成比普通模数转换更多的繁重工作。这些ADC具有更多的数字电路,可以快速处理信号。

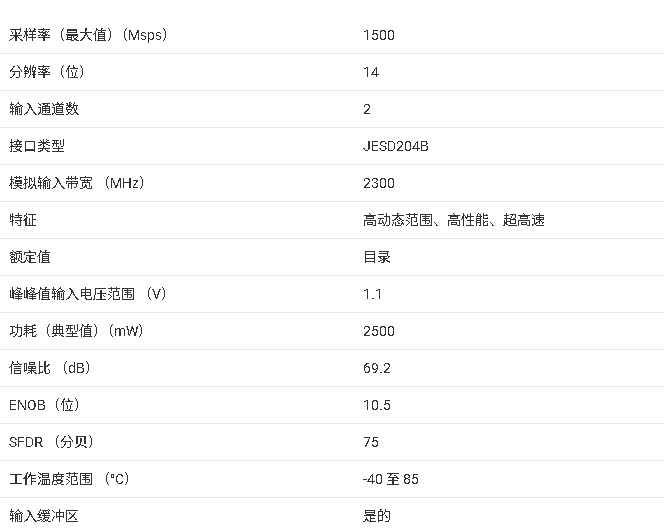

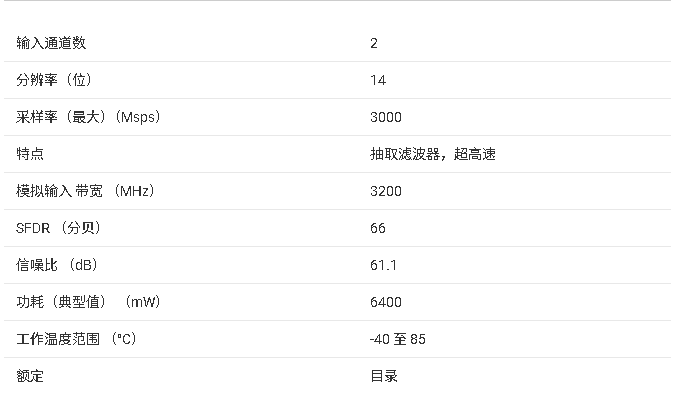

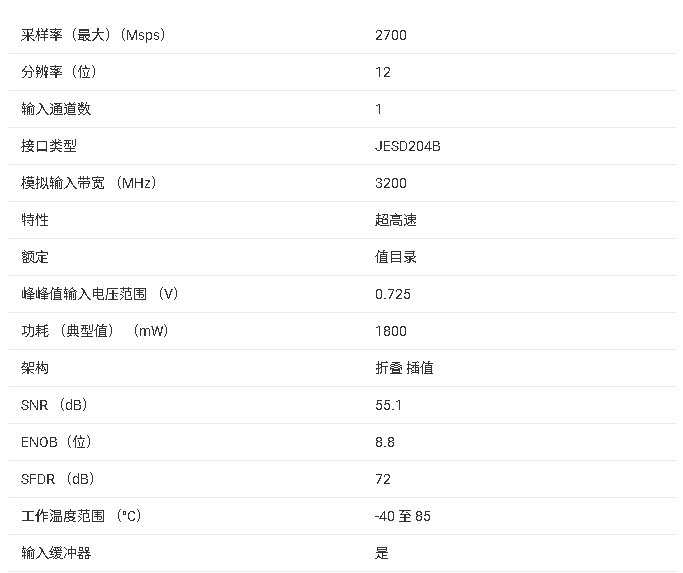

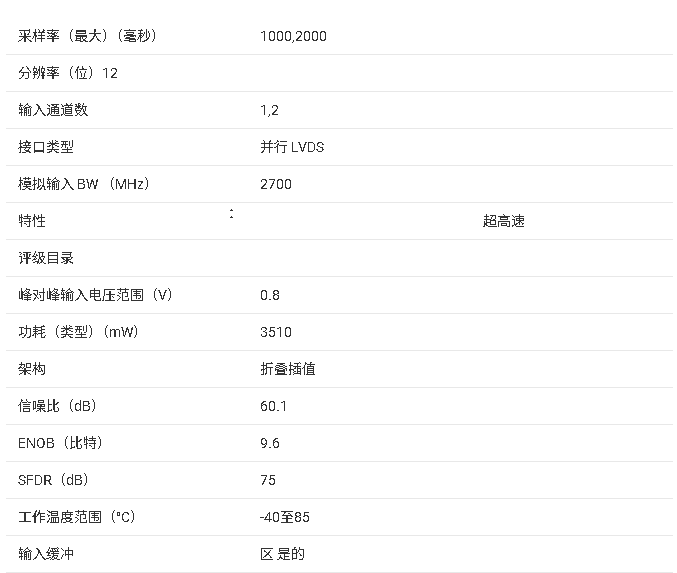

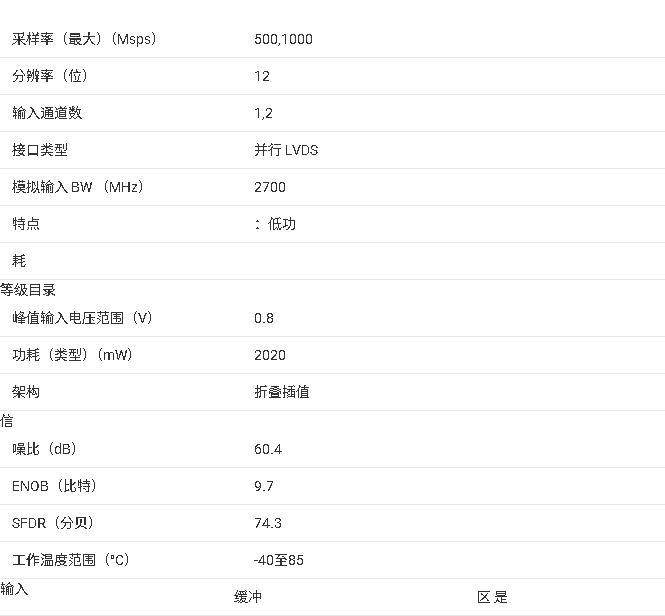

对于系统设计人员来说,这意味着易于实施和其他灵活性,而这些灵活性迄今为止一直是ASIC/FPGA领域的一部分。上述相同的无线电设计示例可以使用RF采样ADC实现。AD9680(14位、1 GSPS JESD204B、双通道ADC)是新一代RF采样ADC之一,还具有额外的数字处理能力[6]。该ADC在全采样速率(1 GSPS)下的NSD为~67 dBFS [3]。这个信噪比还不是一个问题,因为它将在后面变得明显。目标频段与以前相同,但RF采样ADC奈奎斯特区的频率规划要简单得多,如图10所示。这是因为与前面描述的示例(1 MHz)相比,该ADC的采样频率为250倍(<> GHz)。

图 10.使用 50 GSPS ADC 的 1 MHz 宽带无线电的频率规划。

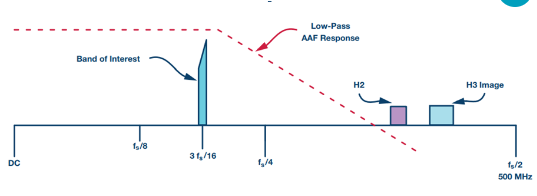

从频率规划中可以明显看出,这是一个比图4所示方案更简单的计划。AAF 要求也放宽了,如图 11 所示。在这种方法中,其思路是使用简单的模拟前端设计,并将数字处理模块留在RF采样ADC内,以进行繁重的信号处理。

图 11.用于 1 GSPS ADC 的 AAF 植入。

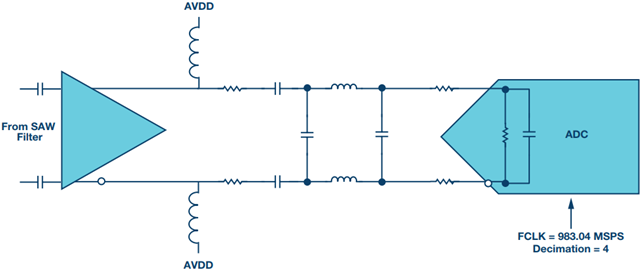

过采样的好处基本上是将频率规划分散到奈奎斯特区,比250 MSPS奈奎斯特区大四倍。这极大地放宽了滤波要求,与250 MSPS ADC实现中使用的带通滤波器相反,一个简单的三阶低通滤波器就足够了。使用RF采样ADC的简化AAF实现如图12所示。

图 12.前端设计显示放大器、抗混叠滤波器和ADC,速率为1 GSPS。

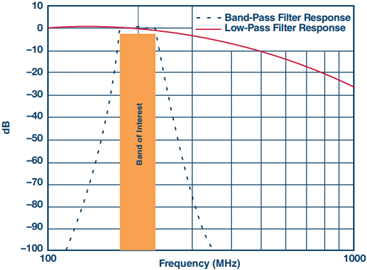

图13显示了低通滤波器响应。带通响应也显示为比较。低通滤波器实现了更好的通带平坦度,并且在元件失配方面更易于管理。在匹配阻抗方面也更容易实现。此外,由于组件数量较少,系统的成本也降低了。前端设计的这种简单性可以缩短设计时间。

图 13.250 MSPS ADC 和 1 GSPS ADC 的 AAF 比较。

现代RF采样ADC具有更多的数字处理能力,这意味着数字处理可以在ADC内部快速完成。如本文前所述,这可实现高能效和I/O效率设计。现在,系统设计人员可以使用他/她的FPGA中未使用的JESD204B收发器来处理来自其他RF采样ADC的数据,这些ADC已经处理了数据(模数转换、滤波和抽取)。这样就可以有效地使用FPGA资源,同时增加无线电设计中的通道数量。

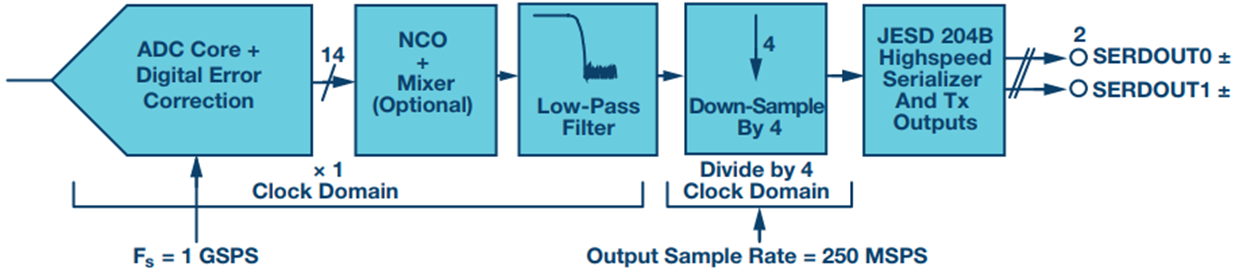

利用DDC,ADC可用作数字混频器,以调谐至设计可能需要的任何IF。在此示例中,使用与上面讨论的相同的频率计划。因此,使用具有实际混频的抽取4选项来演示ADC的性能。如图 14 所示。

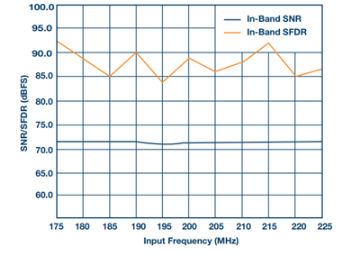

图 14.RF采样速率为1 GSPS,DDC设置为抽取4。

在正常或全带宽模式下,AD9680的SNR约为66 dBFS至67 dBFS。但是,当DDC运行时,抽取比设置为4时,可以额外获得6 dB的处理增益[3]。这可确保保持动态范围性能。由于RF采样ADC的采样速率为原始采样速率的4×,因此谐波分散开来(如图10所示)。RF采样ADC中的DDC确保抽取滤波器以数字方式衰减不需要的信号。但是,落在目标频带中的谐波(高阶或其他)仍将显示,因为DDC允许它们通过。这可能是由放大器伪像或低通滤波器没有足够的衰减引起的。低通滤波器可以根据系统要求重新设计,以满足其他杂散性能。图15显示了1 GSPS ADC的SNR/SFDR与输入频率的关系。从数据中可以清楚地看出,使用DDC可将SNR提高6 dB(由于处理增益)和SFDR。在全带宽模式下运行时,SFDR通常受到二次或三次谐波的限制,而在DDC模式下(抽取4),它是最差的其他谐波。

图 15.图14所示的1位、12 GSPS ADC设计的SNR/SFDR与频率的关系。

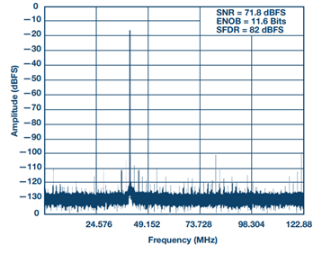

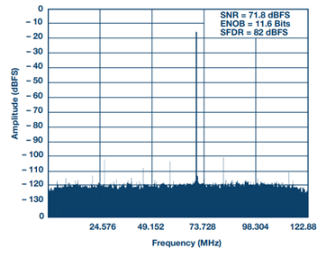

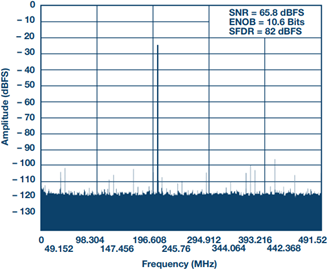

抽取输出的FFT如图16所示。使用 DDC 时,必须注意确保正确处理目标频带。在这种情况下,NCO被调谐到200 MHz,以便感兴趣的频段落在抽取的奈奎斯特的中心。这降低了 FPGA 的处理开销。为了进行比较,AD9680在正常(全带宽)工作下的FFT如图17所示。

图 16.205 GSPS ADC 上的 1 MHz FFT,抽取 4;NCO 调谐到 200 MHz。

图 17.全带宽模式下 205 GSPS ADC 上的 1 MHz FFT。

数据显示,DDC除了改善带内噪声性能外,还提供无次谐波的干净频谱。由于DDC对数据进行滤波和抽取(至250 MSPS),因此它们还会降低输出通道速率,从而为JESD204B串行接口提供灵活的选择。这使系统设计人员可以在高通道速率(更昂贵)、低 I/O 数 FPGA 或低通道速率(更便宜)、高 I/O 数 FPGA 之间进行选择。

结论

RF采样ADC在系统设计中具有独特的优势,这在几年前是不可能的。业界正在寻求加速基础设施的设计和实施,以应对对更高带宽的需求。设计时间和预算正在缩减,对更多软件驱动的可扩展、可重新配置架构的需求有助于成为新常态。对带宽需求的增加也伴随着对更高容量的需求。这给FPGA I/O带来了额外的压力,RF采样ADC可以通过使用其内部DDC来抵消压力。

审核编辑:郭婷

电子发烧友App

电子发烧友App

评论