为了在USB 3.0中实现数据的8 b/10 b编解码,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,然后在FPGA上实现了具体的硬件电路。

2011-11-30 11:38:18 2803

2803

语音编解码器技术的发展一定程度上处于静止状态,但音频编解码器技术一直在向前演进。音频编解码器朝更多的环绕声通道发展就是一个趋势。

2012-02-03 16:17:11 4774

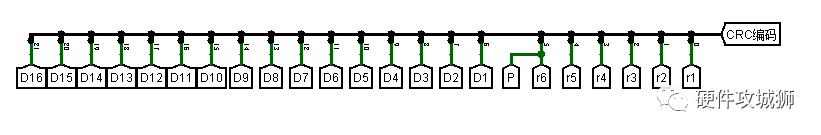

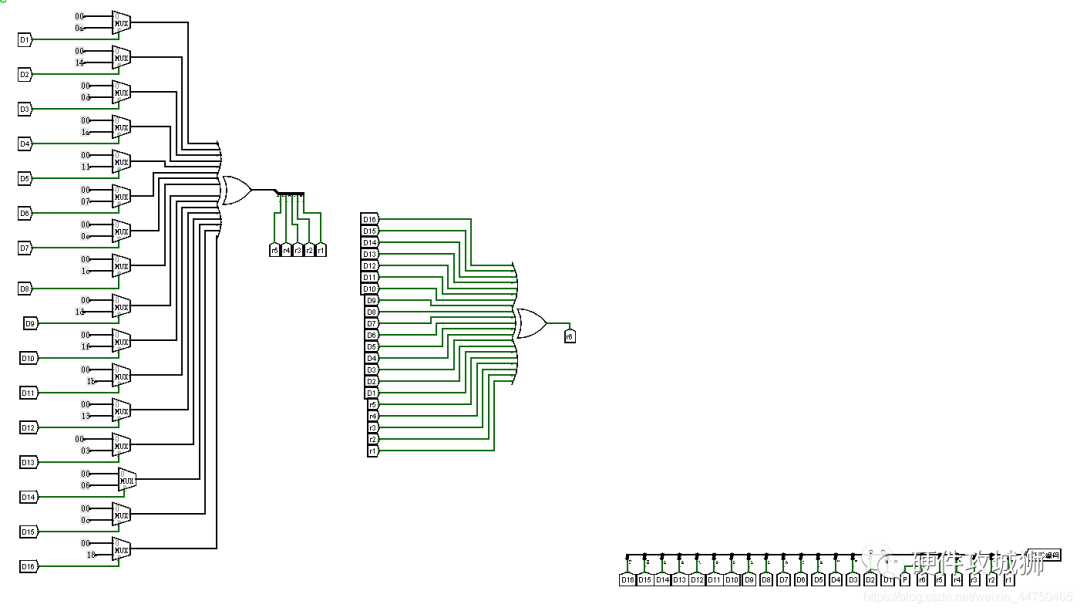

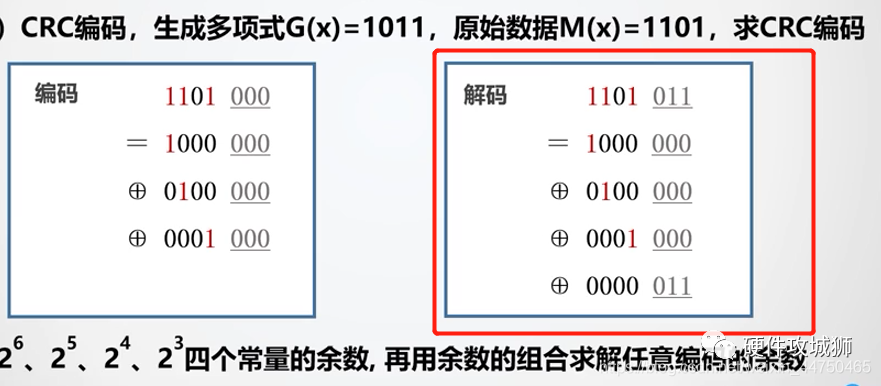

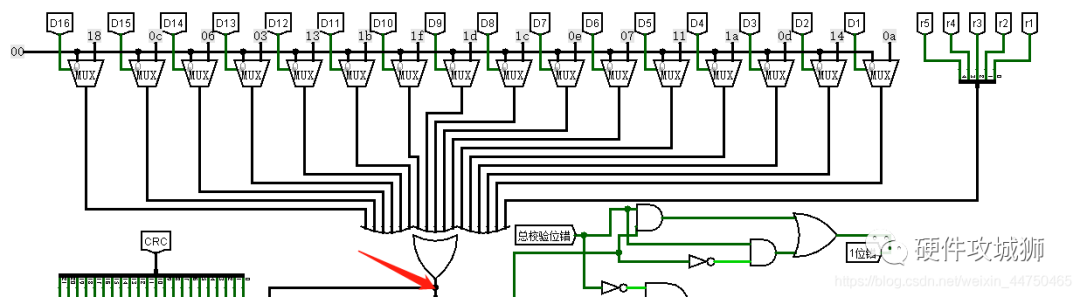

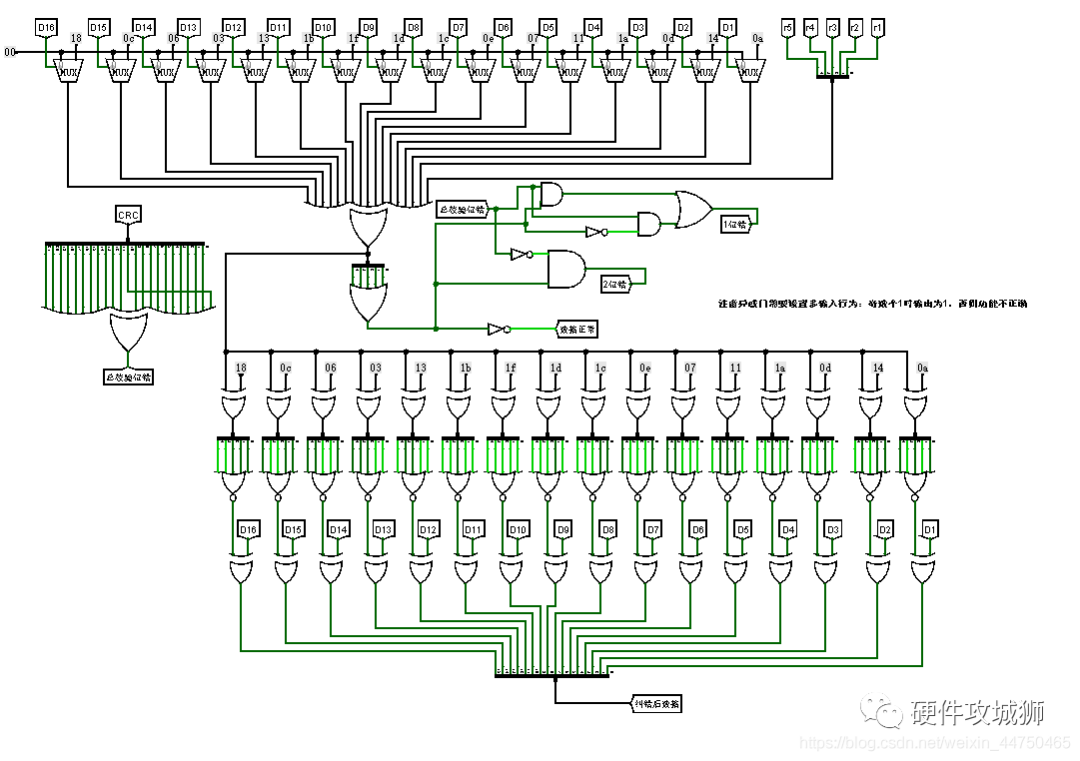

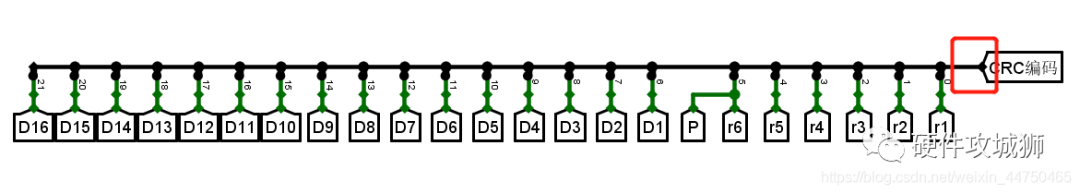

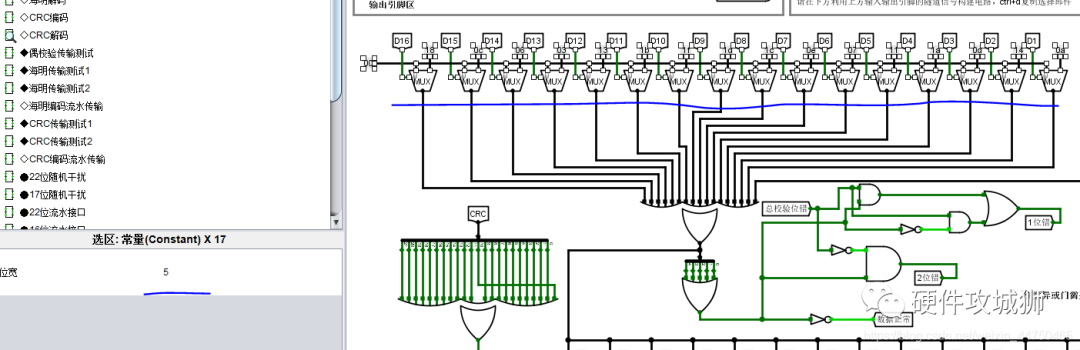

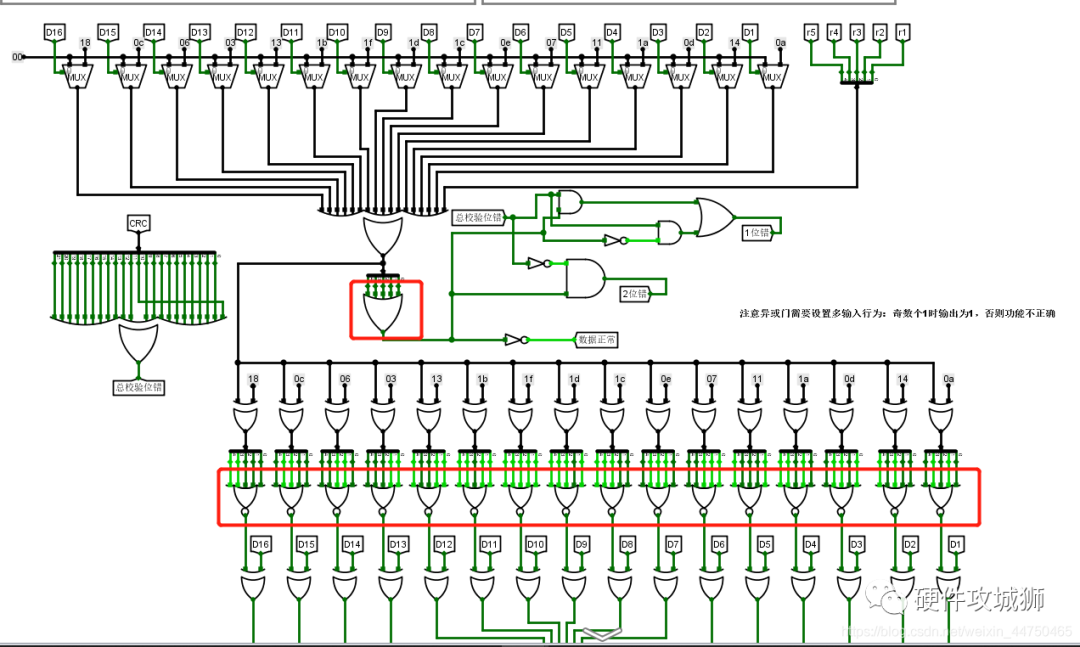

4774 10G以太网系统中的并行CRC编解码器的设计

2012-08-10 17:59:00

53小波的EZW压缩编解码FPGA实现,有了解的麻烦指点下,谢谢!

2014-06-22 11:25:36

16位音频编解码芯片[ES689]开发手册

2012-08-20 13:22:31

16B 20B编解码 Xilinx提供1

2012-08-10 18:01:22

锁定,12位数据一起输入到电脑的并行口(打印口)。经电脑翻译用中文显示发生报警的地址和报警的类型,并同时发出“嘟嘟”的报警声,以引起注意,如图4和图5所示。图4 接收解调和解码模块原理方框图图5 解码

2008-09-02 10:55:21

编解码器是用于对数字媒体文件(如歌曲或视频)进行压缩或解压缩的软件。Windows Media Player 和其他程序使用编解码器来播放并创建数字媒体文件。

2020-04-06 09:00:42

AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-13 09:57:27

AD7655并行模式工作,为何我采集的数据无论何时候16bit中都是第3~0位一直为F,变化的是第4~11位,在原理图设计中我将byteswap引脚接地了,在sigtap中采集的波形图如下,急求指点呀

2023-12-22 07:22:36

AKD4641EN-A,AK4641评估板,16位立体声编解码器,内置麦克风放大器和16位单声道CODEC,用于蓝牙接口。除环回模式(A / D至D / A)外,AKD4641还可单独评估A / D

2020-06-18 08:44:41

Android硬编解码主要用MediaCodec实现。以下是Android官方的使用说明:我就用MediaCodec做一个demo,实现硬编解码摄像的的preview数据。demo界面如图:程序界面

2022-04-11 14:39:36

我正在使用 I91260 语音芯片,我在SDS 看到有不同的编解码格式(AudioPlayback MD4 NuOneEx ...) 我想知道这些格式有什么区别,我如何更好的选择使用那个格式?

我的另一个问题是,在那个文档 展示了关于 音频编解码的 介绍,比如 采样率,通道选择 等描述

2023-06-13 06:16:22

Verilog并行CRC校验

2012-08-20 21:52:15

)====================================================================版权归作者所有,未经允许,请勿转载。====================================================================一、opus编解码简介Opus是一个完全开放,免版税,高度通用的音频编解码器。在互联网上Opus是交互式语音和音乐传输,也

2021-12-24 06:56:37

小弟最近在做2013年国赛题目红外通信装置,其实核心就是对音频信号进行PCM编解码,其中我们用到了MC14LC5480这款PCM编解码芯片,其中有几个疑问1.看全英文的文档介绍说有四种工作模式,但我

2016-03-15 11:30:37

下面的代码是为8位CRC编写的。有人建议如何转换下面的代码为16位CRCCode修改 以上来自于百度翻译 以下为原文 The below code written for 8 bit CRC

2018-10-16 11:00:35

初识红外编解码

2021-08-16 06:35:47

数字通信过程中,基带信道对传输信号的码型有严格的限制。针对数字光纤通信传输信号码型的要求,介绍了CMI码的编解码原理,提出了一种基于可编程逻辑器件EPM240T100C5实现CMI编解码的方法,给出

2010-05-06 09:06:05

语音通信、联网音频甚至高性能音频处理应用。较之 ARM 等通用处理器,此设计还通过在 DSP 上实现 Opus 编解码器来提升性能。根据通用处理器上所运行代码的优化级别,通过在 C66x TI DSP

2018-08-20 06:02:22

ADPCM算法及其编解码器原理是什么?如何去设计ADPCM语音编解码电路?

2021-05-06 06:37:15

WM873l是什么?WM8731芯片接口时序有哪几种?如何对音频编解码芯片WM8731进行接口电路的设计?

2021-06-07 06:20:50

怎样运用CPLD去控制曼彻斯特编解码器?

2021-05-07 07:09:08

)PARALLEL-TO-SERIAL位模式与帖子头部的图片相同,我必须发送到编解码器,串行,首先是MSB,16位数据,其余32-16将是16.所以我必须发送一个LRframe总共32位,因为32是同步串行输入的时钟脉冲。并行到

2019-06-11 09:48:00

CODE WORD, 支持CD(载波侦测),FEC前项纠错,16位CRC校验,data whitening ,曼彻斯特编解码,3/4线SPI接口, 独立的64字节RX 和TX FIFO.专业无线总汇

2011-04-11 10:20:37

没有遇到过。我所知道的每个编解码器都使用一个 256 位帧和 8 个 32 位槽,尽管它们通常每个样本使用少于 32 位。有谁知道可以使用 16 位插槽的 8 通道输出音频编解码器或 DAC?

2023-04-12 06:12:20

目前在做视频编解码,功能只是实现对640*480 25fps做H.264编码和解码,请教专家:1、基于这种应用DM368是否就可以了?2、DM368能否支持编码和解码的并行执行?即两路同时输入,一路

2019-02-20 09:16:35

音视频编解码标准简介

2021-01-21 06:53:21

本人完全未接触过音频编解码,最近因为需要了解了一下音频编解码的芯片,其中均集成了ADC和DAC,想请教一下,音频编解码与ADC和DAC是什么关系?(我理解是:ADC是编码的基础,DAC是解码的基础,解码其实就是将数字量经DAC后生成了模拟量在经运放等恢复音频,不知对否?)

2014-08-07 15:22:30

;amp;amp;D),威声(VLSI)针对新技术的集成电路开发了近20年,其产品涵盖了许多低功率产品应用程序。公司的研究重点是低功耗应用的数模混合信号与射频信号。威声(VLSI)专注开发的音频编解码

2012-11-06 09:44:06

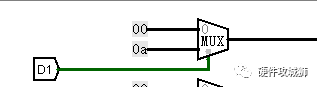

顶层为原理图的能显示16进制减法计数器设计1.用VHDL设计一个二选一电路,并用ModelSim Simulator 仿真验证。 要求该二选一电路能实现16进制数的两位数据串行输出(或称动态输出

2009-10-11 08:51:38

RS编解码原理是什么如何实现RS编解码器?

2021-04-29 06:11:40

TLC320AD535编解码器电路图,原理图

2007-06-05 17:49:23 40

40 Jupiter 1.0是一款符合中国国情的原理图设计软件,聚焦核心功能,覆盖原理图设计全流程,功能设计更智能化,界面操作更人性化,让硬件工程师使用得更愉悦、顺畅。为昕科技旨在通过新技术提高硬件工程师

2022-04-11 13:47:20

AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-13 09:54:41 25

25 AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-15 15:13:14 27

27 HDB3码是基带传输系统中经常采用的传输码型。本文阐述了HDB3码编解码电路的基本原理,在MAX+PLUSⅡ软件平台上,给出了利用复杂可编程逻辑器件设计的HDB3码编解码电路,并进行了编译和

2010-02-24 15:59:48 51

51 基于AMI/HDB3编解码原理,设计了一种用CD22103集成芯片实~AMI/HDB3编解码的硬件电路.详细分析了编解码的实现过程、单双极性变换及位同步,最后给出实验结果并分析了编解码时延

2010-04-13 08:56:28 145

145 主题内容与适用范围

本标准规定了PCM编解码系统信号的格式和其他有关条件。

本标准适用于录像系统录放音频信号用的PCM编解码器。

系统说明

PCM编解码

2010-08-31 18:26:25 35

35 采用多路复用流水线的思想,设计基于FPGA仿真测试的RS编解码的改进IBM算法,使用Verilog硬件编程语言实现,进一步提高RS编解码器的运行速度及纠错能力,扩大应用范围。系统设计

2010-12-22 17:02:40 25

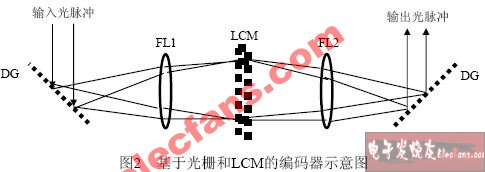

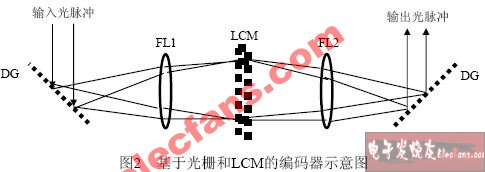

25 频域相位编解码OCDMA系统

基于频域相位编解码OCDMA通信系统如图1所示[3]。频域相位编解码OCDMA通信系统,无论是在实验还是理论方面,相对

2009-02-28 11:32:43 1009

1009

什么是音频编解码器?

编解码器(编码器/解码器)转换成模拟信号的数字码流,另一个相同的编解码器转换为数字流回到成模拟信

2009-05-03 23:48:59 3870

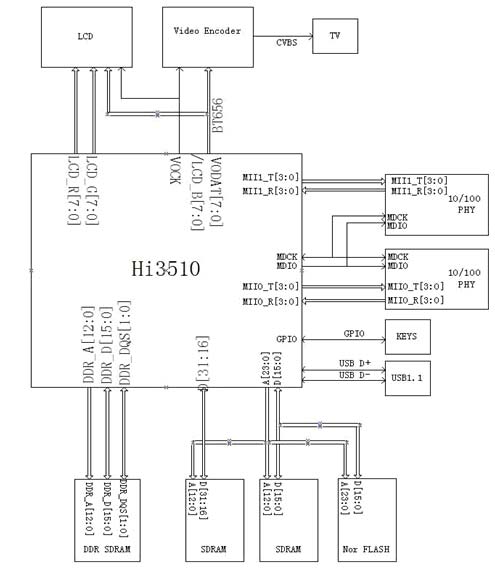

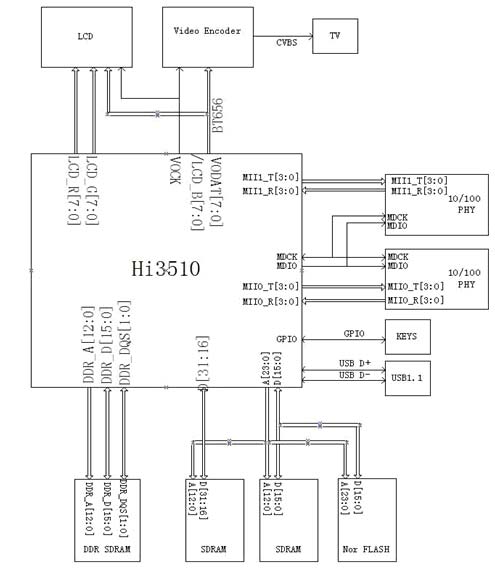

3870 i3510编解码的应用 Hi3510自带的Linux操作系统(同时支持Vxworks、WinCE等开放式操作系统)和ARM处理器,使得芯片除了编解码功能外,还可以实现许多丰富的应用功能开发。如图2

2009-05-13 11:13:28 1360

1360

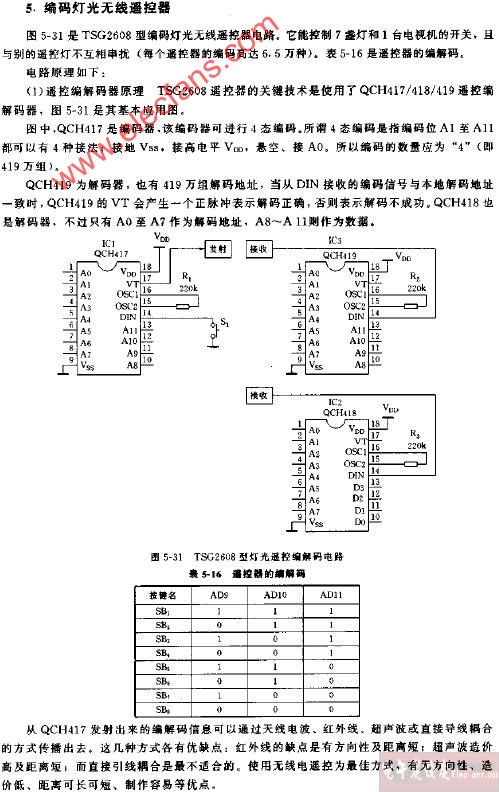

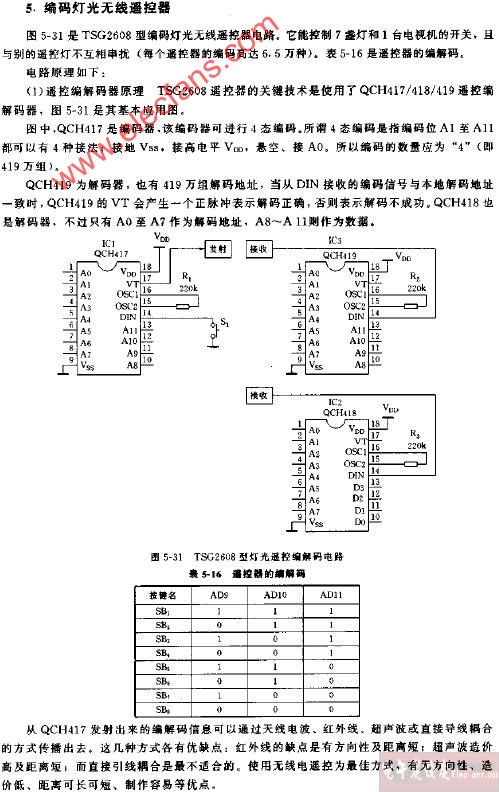

TSG2608型灯光遥控编解码电路图

2009-06-13 16:58:01 838

838

讨论如何使用CPLD实现单片机与曼彻斯特编解码器的接口。设计时采用自顶向下的流程,具体电路可灵活地添加到各种曼彻斯特码接口系统中。

关键词 曼彻斯特编解码器 T2模

2009-06-16 07:40:18 1251

1251

摘要:介绍了HDB3编解码的原理和方法,给出了用CPLD(Complex Programmable Logic Device)实现E1信号HDB3编解码的方法,同时给出了它的实现原理图,最后给出了XI

2009-06-20 13:44:03 1049

1049

摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 3364

3364

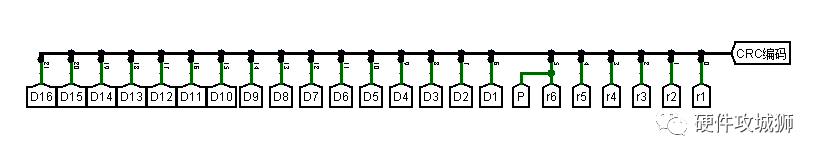

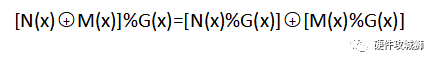

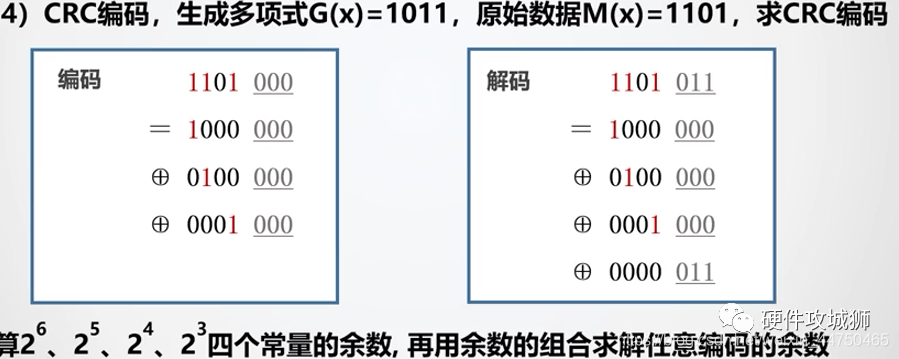

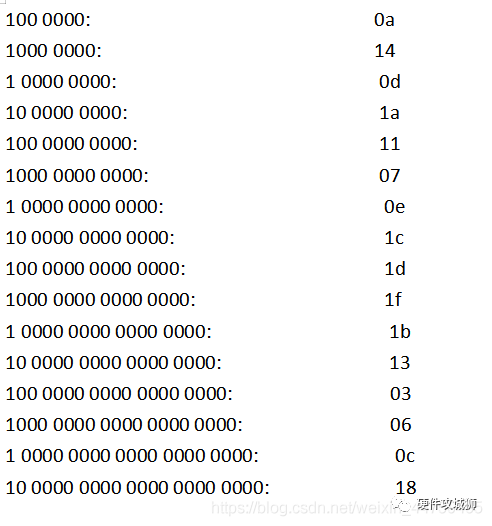

循环冗余码校验 CRC (Cyclic Redundancy Check) 广泛用于通讯领域和数据存储的数据检错。基于FPGA在通讯领域和数据存储的应用越来越广泛,CRC的编码解码模块已经是FPGA上的常用模块了。采

2011-08-15 11:19:57 40

40 结合RS码的基本特性,讲述了RS码的编解码过程,给出了经过实际验证的RS编解码在超短波跳频电台开发中的软件应用实例。

2012-02-13 10:07:26 26

26 在介绍CRC校验原理和传统CRC32串行比特算法的基础上,由串行比特型算法推导出一种CRC32并行算法。并结合SATAⅡ协议的要求,完成了SATAⅡ主控制器设计中CRC生成与校验模块的设计。最后

2012-11-07 16:19:37 54

54 E文JPEG编解码介绍,很好的资料,快来学习吧

2016-02-18 14:14:31 0

0 RS编解码的FPGA实现-说明RS编解码的FPGA实现-说明。

2016-05-04 15:59:44 21

21 六路编解码电路原理图都是值得参考的设计。

2016-05-11 17:00:47 33

33 四路编解码电路原理图都是值得参考的设计。

2016-05-11 17:33:19 27

27 循环码编解码电路的EDA设计。

2016-05-20 11:47:38 11

11 基于FPGA的JPEG实时图像编解码系统

2016-08-29 16:05:01 15

15 通信接口——编解码

2017-09-04 09:39:45 9

9 基于Cortex_A8多媒体编解码优化

2017-09-25 13:20:56 7

7 串行编码原理得到8 位并行数据的CRC 校验矩阵,之后对矩阵进行迭代简化,得到32 位并行数据的参数矩阵,此参数矩阵作为该CRC 算法的核心实现了对数据进行预处理。最后对该算法进行了硬件实现,仿真及综合结果表明,该算法可在单周期内完成对128 位并行数据的CRC 编码和解码校验,

2017-10-30 16:39:25 3

3 。CRC的实现方式分为串行方式和并行方式,由于并行方式一个时钟周期内可以处理8个bit,与千兆以太网的C;MIl接口协议相符合,故千兆以太网的CRC校验码的生成和校验中常使用并行算法实现。本文研究了CRC校验码的串行实现算法和并行实现算法,并且

2017-11-13 14:20:47 12

12 基于串行异步收发器(UART)的通信中经常用到循环冗余校验(CRC),常见的CRC校验电路多为串行校验,校验所需时钟周期较多,基于查找表或输入矩阵转换的并行算法,需要存储余数表,占用大量的硬件资源

2017-11-18 11:24:54 1789

1789

对L9320编解码器的工作原理和使用方法 进行了分析,给出了L9320在便携式语音系统中的典型应用电路.

2019-12-20 17:27:09 24

24 本文档的主要内容详细介绍的是PCM语音编解码的PCB原理图免费下载。

2020-10-14 14:52:00 20

20 的LFSR 电路为基础,推导出产生32位并行数据的CRC - 16编码表达式,用EDA 工具设计出CRC - 16编码模块,并对其进行综合仿真,验证其可行性。

2021-03-10 15:50:00 14

14 CRC校验的实现基于串行位移寄存器,如果要处理并行数据,需要对电路进行改进。本文介绍了一种并行CRC电路HDL代码的快速生成钟算法,只需要带入不同的参数,可自动生成不同长度以及并行度的并行CRC电路的HDL代码。

2021-03-28 09:29:50 15

15 文章介绍了用于 USB 总线数据传输的CRC 校验的原理和算法,并且采用并行电路实现 USB2.0 中的 CRC产生和CRC校验,与传统的串行电路实现相比,并行电路实现方法虽然在芯片面积上大于串行电路实现, 但由于降低了时钟频率,电路更容易综合实现,并且大大降低了功耗,有利于低功耗电路设计。

2021-03-28 09:32:27 11

11 用软件实现 CRC 校验码计算很难满足高速数据通信的要求 ,基于硬件的实现方法中 ,有串行经典算法 LFSR 电路 以及由软件算法推导出来的其它各种并行计算方法。以经典的LFSR 电路为基础 ,研究

2021-03-28 09:34:24 30

30 、并行总线共用和丌AG菊花链技术。通过国内外技术对比和网络性能测试,DSP实现语音编解码技术最终在多个项目中得以广泛应用,为今后语音编解码技术的发展提供了借鉴经验。

2021-04-11 11:39:38 17

17 AD1846:低成本并行端口16位SoundPort立体声编解码器过时数据表

2021-05-14 15:12:53 6

6 PCM语音编解码及原理图下载

2021-07-14 09:56:33 12

12 NANDFLASH快速BCH编解码算法及便件实现(嵌入式开发自学网)-NANDFLASH快速BCH编解码算法及便件实现

2021-07-30 14:14:40 5

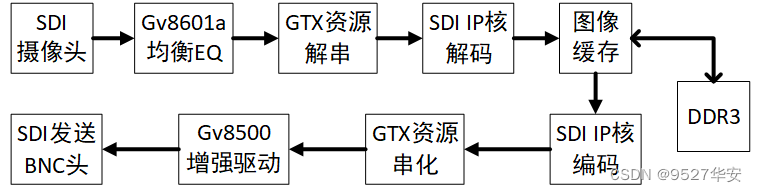

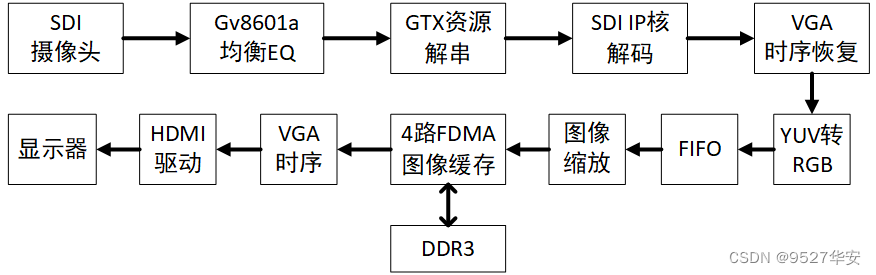

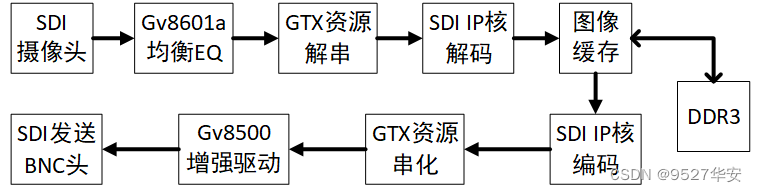

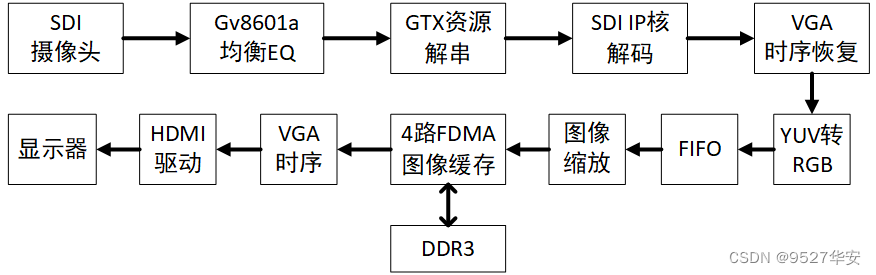

5 一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCRCB,

2023-06-14 14:48:28 679

679

大家好,今天我分享的是走向实用的AI图像编解码。本次将着重从 “走向”两个字出发,阐述AI编解码研发的关键内容和进展。

2023-06-15 09:19:10 465

465

一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCRCB,GS2972发送器直接将并行的YCRCB编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格

2023-06-19 16:55:52 809

809

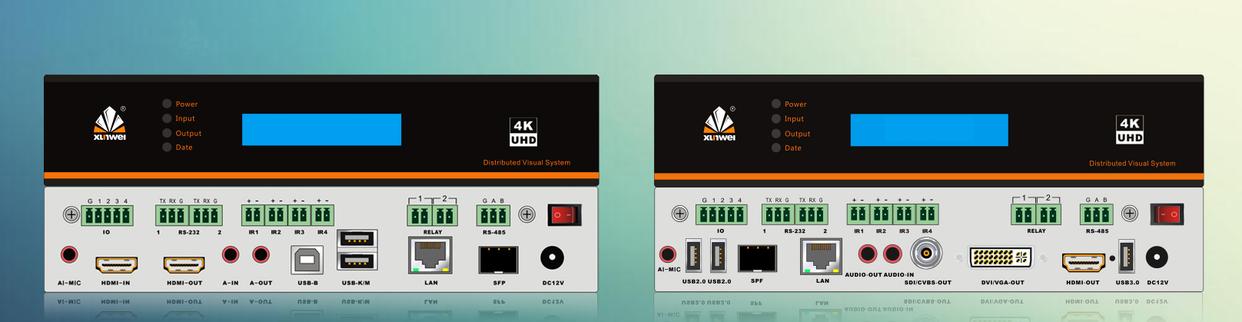

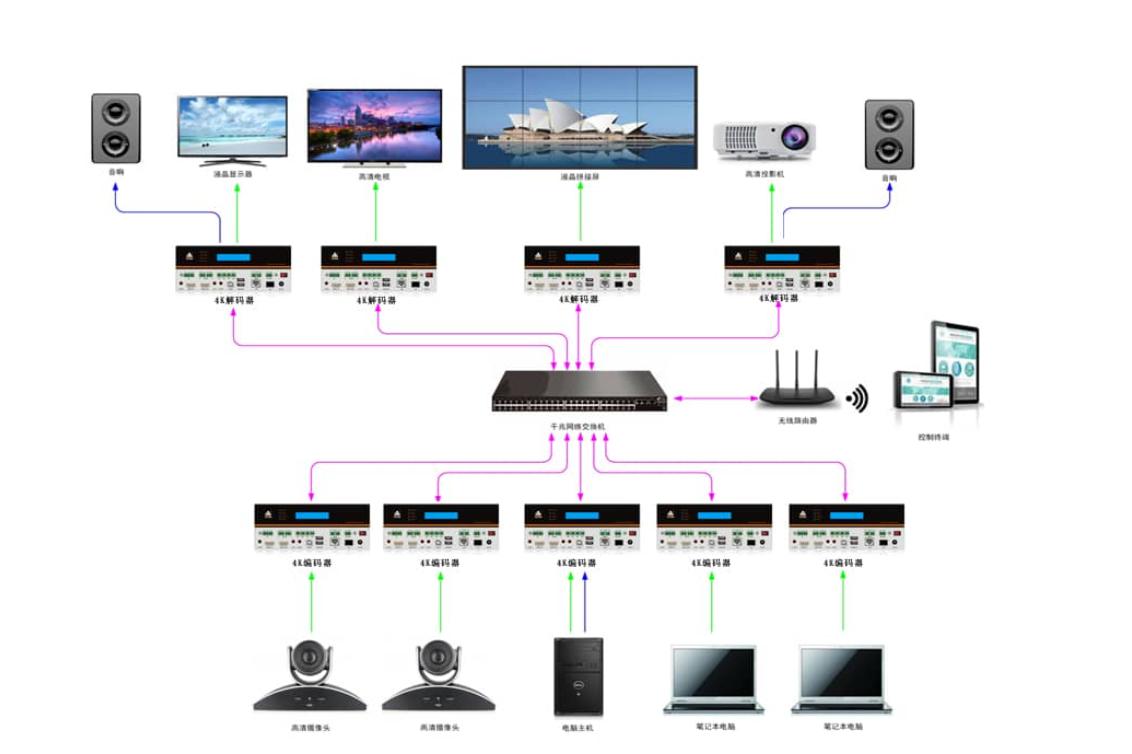

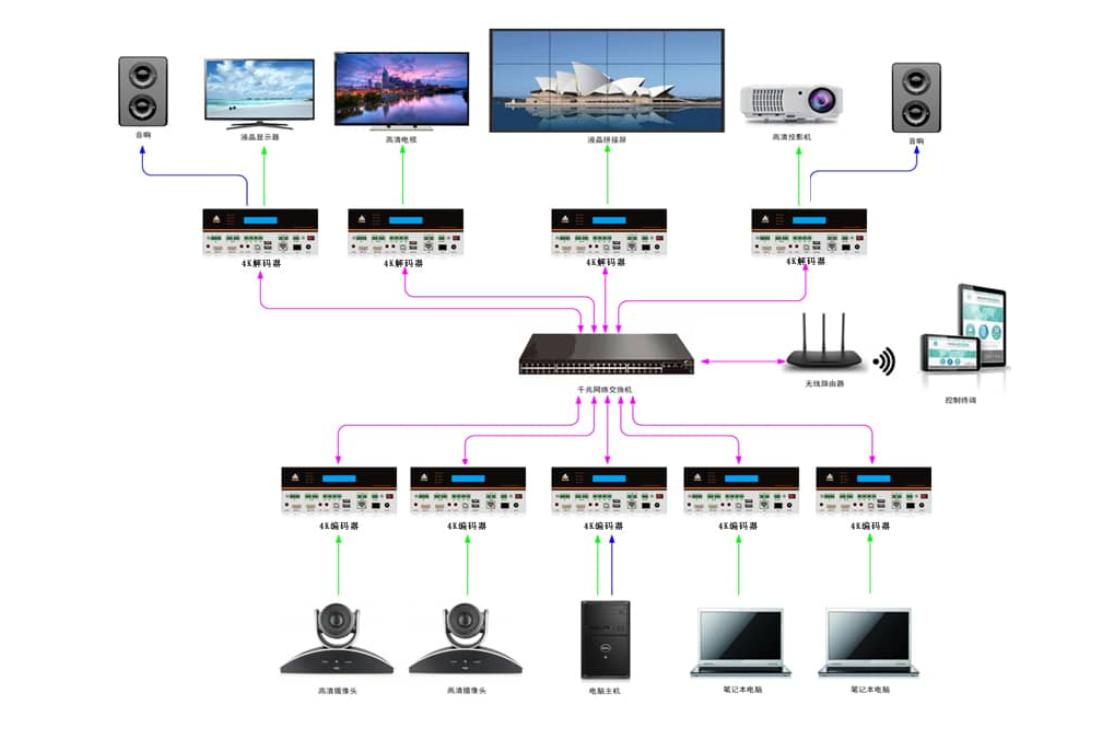

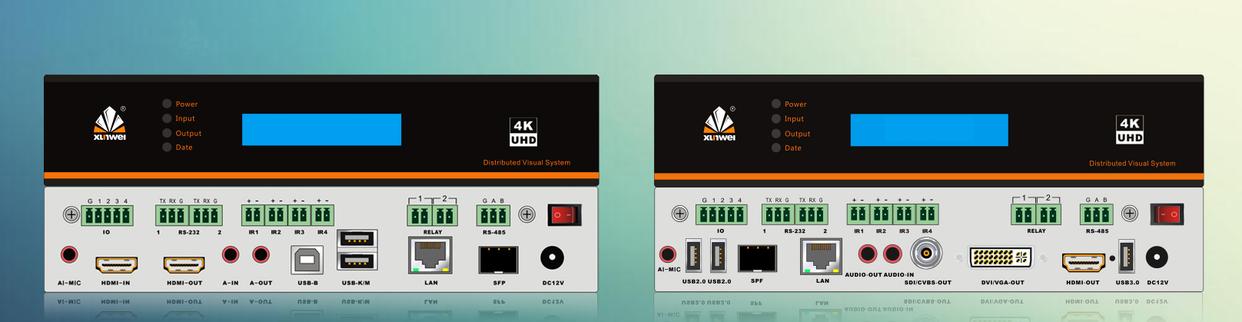

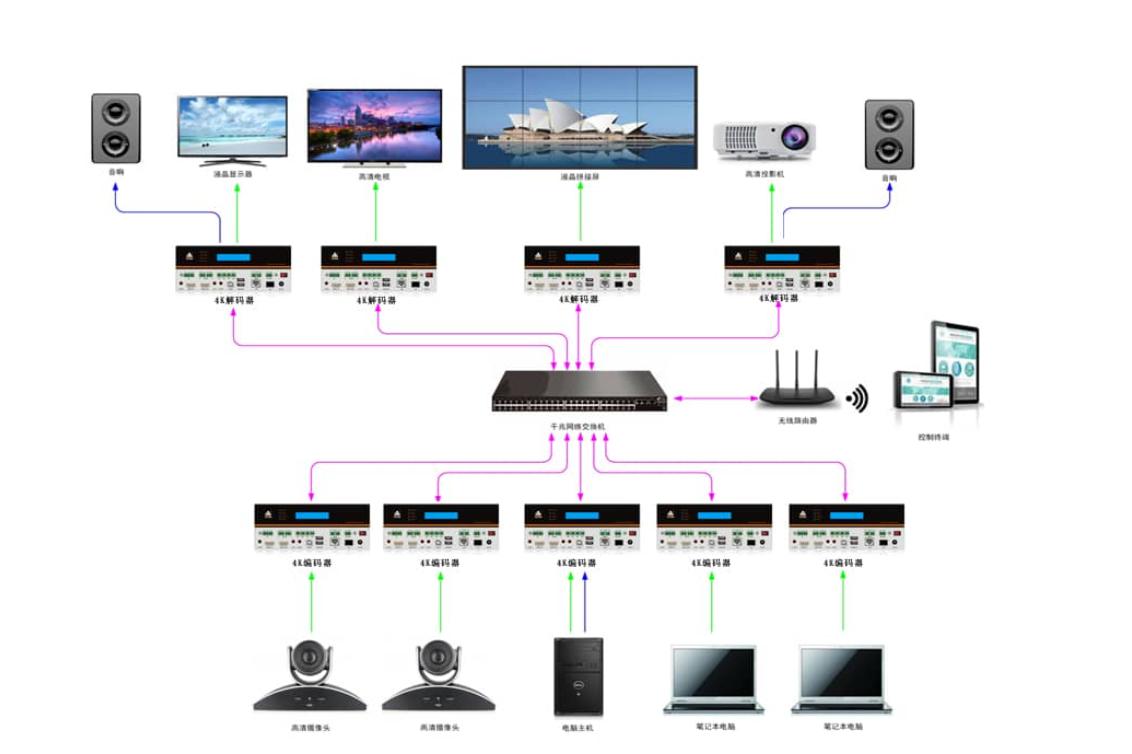

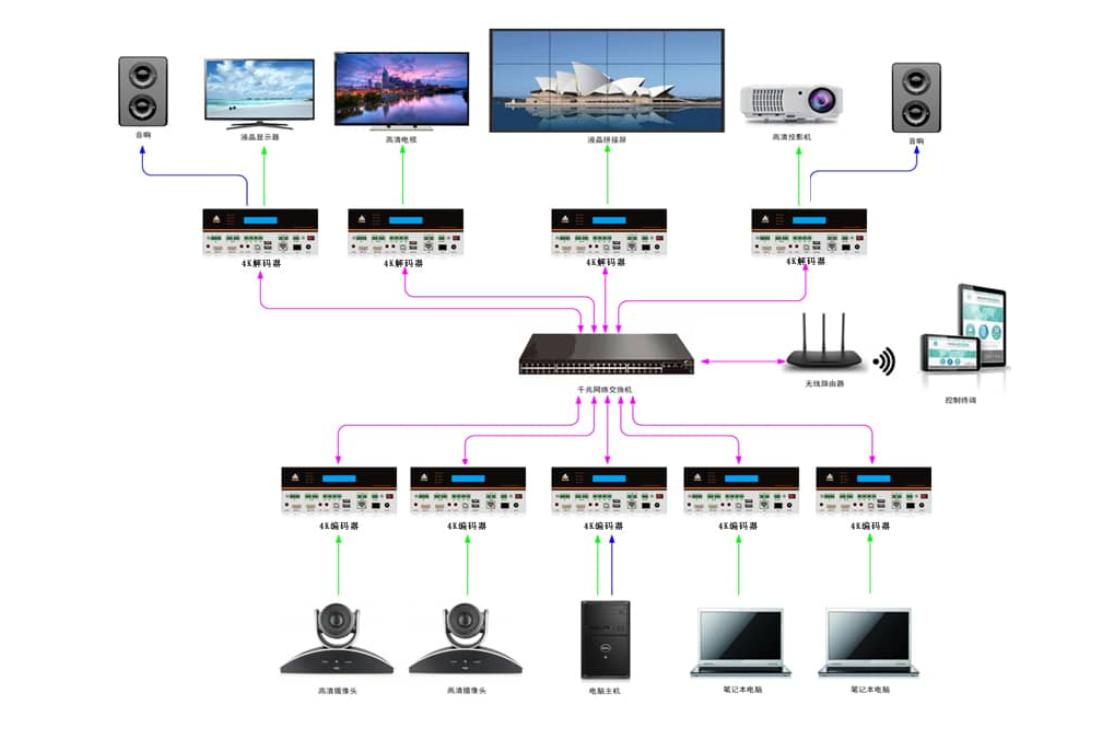

编解码一体机是一种集视频编解码、音频编码以及数据传输功能于一体的多媒体设备。这种设备通常基于云计算技术和先进的编解码算法,能够高效地处理视频流,提供低延迟、高稳定性的音视频传输服务。此外,编解码

2024-01-31 14:19:36 168

168

编解码一体机作为音频处理的新选择,以其高效、灵活的解决方案,引领着音频处理技术的新篇章。这种设备集成了音频编解码和数据传输功能,将复杂的音频处理流程简化在一台设备中,提高了音频处理的效率和灵活性

2024-01-31 14:46:16 134

134

编解码一体机是一种集视频编解码、音频编码以及数据传输功能于一体的多媒体设备。它基于云计算技术,具有高效、实时的视频处理能力,广泛应用于安防监控、视频会议、教育录播等领域。 首先,编解码一体机采用

2024-01-31 14:48:04 148

148

编解码一体机相对于传统的编解码设备具有多个优势。以下是编解码一体机的几个主要优势: 高效实时的视频处理能力:编解码一体机采用先进的编解码算法和云计算技术,能够实现高效、实时的视频处理,满足各种应用场

2024-01-31 14:56:04 291

291

编解码一体机是一种集视频编解码、音频编码以及数据传输功能于一体的多媒体设备,广泛应用于各个领域。以下是编解码一体机的几个主要应用场景: 来百度APP畅享高清图片 视频会议:编解码一体机可以为视频会议

2024-01-31 14:57:21 146

146

电子发烧友App

电子发烧友App

评论