摘 要

超宽禁带氧化镓(Ga2O3)半导体具有临界击穿场强高和可实现大尺寸单晶衬底等优势, 在功率电子和微波射 频器件方面具有重要的研究价值和广阔的应用前景。 尽管Ga2O3材料与器件研究已取得很大进展, 但其极低的热导 系数和缺少有效的p 型掺杂方法成为限制其复杂器件结构制备和器件性能提升的主要瓶颈。

针对上述两大关键瓶 颈, 本文综述了利用异质材料集成的方法实现高导热衬底Ga2O3 异质集成晶体管与基于p 型氧化镍/n型氧化镓(p- NiO/n-Ga2O3)异质结的Ga2O3功率二极管和超结晶体管的研究进展。

采用离子刀智能剥离-键合技术实现的高导热 衬底Ga2O3异质集成方案可有效解决其导热问题, 碳化硅(SiC)和硅(Si)基Ga2O3异质集成晶体管展现出远优于Ga2O3体材料器件的热相关特性。

采用异质外延技术制备的p-NiO/n-Ga2O3功率二极管和超结晶体管均展现出良好的电 学特性, p-NiO/n-Ga2O3异质结为Ga2O3双极器件的发展提供了一种可行途径。

异质集成和异质结技术可有效地克 服Ga2O3本身的关键难点问题, 助力高效能、高功率和商业可扩展的Ga2O3微电子系统的实现, 推动其实用化进程。

研究背景

超宽禁带氧化镓(Ga2O3)半导体禁带宽度为4.5~ 5.16 eV, 理论预测其击穿电场强度达到8 MV/cm, 远高 于硅(Si) 、碳化硅(SiC)和氮化镓(GaN)等半导体材料, 在功率和射频器件方面有着重要的研究价值和巨大的 应用前景[1] 。经过多年的发展, Ga2O3单晶研究取得了长 足的进步。目前, 可以利用区熔法、导模法和提拉法等 方法实现大尺寸β相Ga2O3单晶衬底的制备[1,2] 。 早期的β-Ga2O3晶体管由于Ga2O3外延沟道材料质 量较差, 因此电学特性不理想[3~5] 。2016年, 日本国家信 息与情报中心(The National Institute of Information and Communications Technology, NICT)的Wong等人[6]在铁(Fe)掺杂β-Ga2O3(010)半绝缘衬底上制备了场板结构金 属-氧化物-半导体场效应晶体管(metal-oxide-semicon- ductor field effect transistor, MOSFET), 其击穿电压Vbr 超过750 V, 且开关电流比ION/IOFF高于109, 自此拉开了 高性能Ga2O3 晶体管研究序幕。目前,Ga2O3晶体管方面 的研究已经引起了广泛的关注, 各国政府和科研机构 都针对Ga2O3材料 、器件的研发投入大量人力和 物力[2] 。

为提升Ga2O3晶体管器件性能, 研究人员开发了 凹槽栅结构 [7] 、复合场板结构 [8] 、垂直鳍(fin)型沟 道结构 [9] 和超高介电常数BaTiO 3 栅介质层结合β -

(Al0.18Ga0.82)2O3/Ga2O3双异质结导电沟道[10]等器件技 术。目前, 水平和垂直结构Ga2O3晶体管器件分别实现 了最高击穿电压8[11]和4 kV[2], 最高功率品质因子408[10] 和280 MW/cm2[9] 。虽然Ga2O3晶体管在器件性能上已经 取得良好进展, 但Ga2O3材料极低的热导率和缺少有效 p型掺杂技术仍然是限制其进一步发展的主要瓶颈。

Ga2O3材料中更为剧烈的声子-声子散射导致其热 导率相比其他材料更低[12], 解决其极低热导率问题是Ga2O3器件实用化的必由之路。中国科学技术大学的Yu 等人 [13] 通过衬底减薄技术进行Ga2O3肖特基二极管 (Schottky barrier diode, SBD)的热管理, 衬底厚度从 650 μm减到250 μm后, 器件散热效果得到一定的提升, 但衬底机械减薄较难控制 。

利用异质集成的方法将 Ga2O3单晶薄膜转移到高导热衬底上形成Ga2O3异质集 成晶圆是解决Ga2O3低导热瓶颈的有效方法之一。西安 电子科技大学和中国科学院上海微系统与信息研究所 合作团队, 从2017年开始, 经过两年攻关, 成功开发出 应用于Ga2O3晶圆的离子注入-键合剥离技术。2019年, 该合作团队[14]在国际电子器件会议(International Elec- tron Device Meeting, IEDM)上报道了利用该技术制备 的晶圆级高导热衬底Ga2O3异质集成晶圆和晶体管。该 工作引起了广泛关注, 并被Compoundsemiconductor发 表题为“Helping gallium oxide keep its cool”的文章进 行报道。 p型掺杂技术是Ga2O3材料与器件研究的关键技术 难点。

非故意掺杂Ga2O3价带顶的E-k色散关系比较平 坦, 导致其内部空穴有效质量较大, 空穴强烈局域化于 电负性较强的O 2p能级上, 同时传统单一掺杂引入的 深能级受主在室温下激活效率极低, 难以向价带贡献 有效的自由空穴, 因而Ga2O3难以实现p型掺杂[15] 。目前 广泛使用的Fe掺杂半绝缘Ga2O3衬底随着温度升高展 现出明显的n型导电特性, 直接导致Ga2O3 MOSFETs的 关态电流随着测试温度升高而急剧增加[16] 。而且, 缺少 p型Ga2O3, 就不能实现pn结以及与之相关的双极型功 率电子器件。虽然已经有文献报道了不同的Ga2O3p型 掺杂技术和理论研究, 譬如使用氢(H)元素对Ga2O3实 现p型和n型双极型掺杂[17] 、固态反应掺杂[18]等, 但是 这些技术都存在受主离化率低与空穴浓度偏低的问 题[19] 。

研究人员也提出利用其他p型氧化物, 比如p型 NiO与n型Ga2O3组合形成pn结, 并开发了相关异质结 器件[20~23], 包括结型场效应晶体管(junction field-effect transistor, JFET)[20] 、超结(superjunction, SJ)晶体管[21] 和pn结二极管[22]等。JFET使用与沟道构成pn结的半导 体作为栅极, 类似金属-半导体场效应晶体管(metal semiconductor field-effect transistor, MESFET), 而超结 晶体管基于超结结构, 利用pn结之间的电荷平衡原理 实现漂移区电场调控。2021年, 西安电子科技大学与南 京大学合作团队报道了基于p-NiO/n-Ga2O3异质结的Ga2O3超结MOSFET[24] 。 本文将综合介绍高导热衬底Ga2O3异质集成晶体 管和基于p-NiO/n-Ga2O3异质结的功率二极管与超结晶 体管研究进展。

1 高导热衬底Ga2O3异质集成晶圆

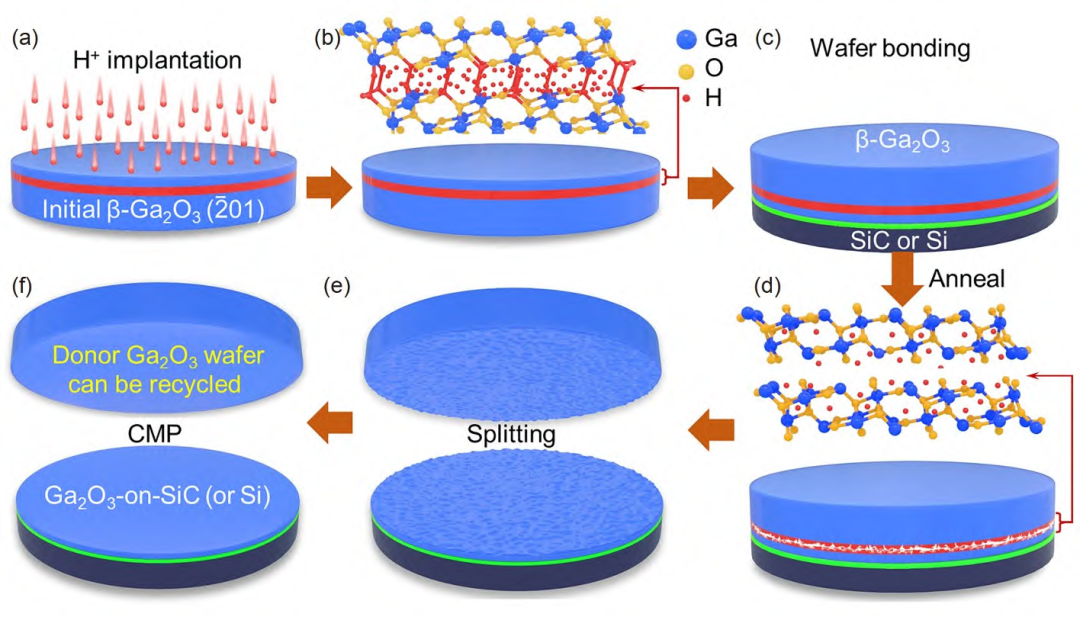

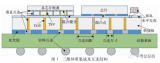

离子注入-键合剥离技术也称为“ 万能离子刀 ”技 术, 可以突破不同材料之间晶格失配 、晶型失配等多 物理场失配限制, 实现高质量的Ga2O3单晶薄膜与高导 热衬底的异质集成。目前基于该技术的绝缘体上硅(si- licon on insulator, SOI), 即SOI晶圆制备[25] 已经产业化, 其商业名称是Smart CutTM。 高导热衬底Ga2O3异质集成晶圆制备流程如图1所 示。首先将氢离子(H+)注入Ga2O3晶圆内部产生H+缺陷 层, 之后将注入H+ 的Ga2O3晶圆与高导热的SiC或Si晶 圆进行键合。

在退火过程中,Ga2O3薄膜将沿着H+缺陷 层位置从Ga2O3晶圆上剥离下来, 并转移到SiC(Si)衬底 上, 从而实现Ga2O3薄膜与高导热衬底的异质集成[14] 。通过控制注入离子能量和剂量 ,Ga2O3 薄膜厚度在 100 nm~10 μm范围内实现可控变化。 Liao等人[26]将氦(He)离子注入Ga2O3体材料中, 通 过加热观察到了Ga2O3表面的起泡行为, 但由于He离子 半径大, 注入He离子后的Ga2O3晶体质量会大幅度恶 化。在晶圆键合方面, Xu等人[27]和Lin等人[28]通过表面 激活键合工艺实现了Ga2O3与n型单晶SiC和多晶SiC的 键合。然而这些工作都是独立的, 并没有实现可用于器 件制备的Ga2O3薄膜与SiC衬底的异质集成。

2019年, Xu等人[14]通过在Ga2O3晶圆中注入H+, 结 合表面激活键合工艺成功地将2英寸(1 in=2。54 cm)的Ga2O3单晶薄膜异质集成到SiC衬底上(图1)。该技术的 难点在于, 剥离退火过程中异质晶圆之间的热失配会 导致其解键合, 从而剥离失败, 因此需要对离子注入剂 量 、键合方法以及剥离温度工艺协同优化[29,30] 。目前 通过该技术已经实现了Ga2O3-SiC(GaOSiC) 、Ga2O3- Al2O3-SiC(GaOISiC)和Ga2O3-Al2O3-Si(GaOISi)三种不同结构的高导热衬底Ga2O3异质集成晶圆。

对于制备的2英寸Ga2O3异质集成晶圆, Ga2O3薄膜 的转移面积达到95%, 剥离之后, 剩余Ga2O3 晶圆完整, 后续通过化学机械抛光(chemical mechanical polishing, CMP)工艺处理, 其可以循环使用, 以减少Ga2O3异质晶 圆的制备成本。

转移后的Ga2O3薄膜有极佳的厚度均匀 性, 其厚度不均匀性小于±2%, 通过CMP可将异质集成Ga2O3薄膜的表面粗糙度均方根(root mean square, RMS)减小到0。2 nm[14,30] 。通过高温退火处理,Ga2O3薄 膜摇摆曲线的半高宽从刚转移的230 arcsec提升到80 arcsec, 其质量接近于同质外延薄膜的质量(22 arc- sec)[31] , 远优于蓝宝石衬底上异质外延的Ga2O3 薄膜 (4248 arcsec)[32] 。

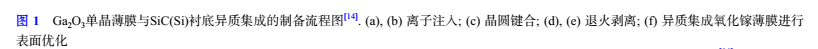

根据制备的Ga2O3/SiC异质集成界面 的透射电子显微镜表征结果, 键合界面处存在着几个 纳米的非晶键合层[14,33], 键合层厚度可以通过键合工 艺和器件制备工艺温度来适当调整。 通过瞬态热反射方法对Ga2O3异质集成晶圆的热 输运能力进行研究。

通过有限元模型拟合瞬态热反射 曲线[34], 得到Ga2O3异质集成晶圆热导率和界面热阻等 关键数据, 相关结果如图2所示[29,30]。高温退火后, Ga2O3异质集成晶圆的热输运能力得到大幅度提升, Ga2O3异 质集成薄膜的热导率达到9。0 W/mK, 相比退火前提升 一倍, 界面热阻为7.5 m2 K/GW, 下降为原来的1/3, 这是 源于介质层的结晶化。高温退火后, SiC基Ga2O3异质集 成晶圆的热扩散速率接近于SiC体材料, 远优于Ga2O3体材料。

同时, 退火处理的Ga2O3异质集成薄膜的热传 导机制由原来声子-缺陷散射机制转变为以声子-声子 散射机制为主[30] 。 Ga2O3异质集成器件展现出优异的散 热能力, 如图2(d)所示, 在相同的功率偏置下, Ga2O3体 材料SBD的表面最高温度是SiC基Ga2O3 SBD的4倍, 同 时SiC基Ga2O3 SBD表面温度分布非常均匀, 证明了高 导热衬底优异的散热能力。

综上所述, 通过万能离子刀异质集成技术实现的 高导热衬底Ga2O3异质集成晶圆, 具有优异的表面均匀 性、粗糙度和结晶质量。 通过高温退火处理, Ga2O3异 质集成晶圆的材料热输运能力和器件散热能力得到大 幅度提升 。 高导热衬底Ga2 O 3 异质集成技术是解决 Ga2O3散热瓶颈的关键技术。

2 高导热Ga2O3异质集成功率晶体管

2.1 Ga2O3异质集成晶体管

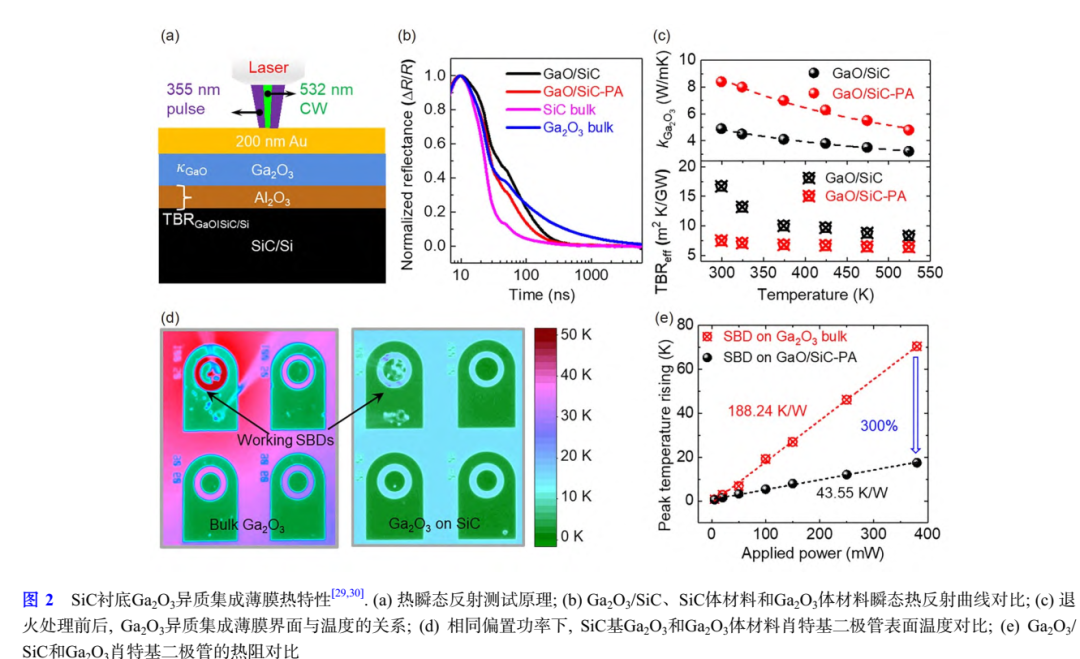

基于材料特性良好的高导热衬底Ga2O3异质集成 晶圆, 西安电子科技大学和中国科学院上海微系统与 信息研究所合作团队开发和制备了高导热衬底Ga2O3异质集成MOSFETs。 相比于报道的Ga2O3衬底上器件, Si和SiC基Ga2O3异质集成晶体管均呈现出更优异的 开、关态热稳定性。 在工作温度由室温上升至250°C时, Si基Ga2O3异质集成晶体管的开态工作电流基本保持 不变, 关态泄漏电流上升小于两个数量级, 如图3(a)所示[33] 。

在工作温度上升过程中, SiC基Ga2O3异质集成晶 体管的开、关态电流呈现更优的相关性, 图3(b)中对比 了SiC基Ga2O3异质集成晶体管与报道的Ga2O3衬底上 器件的导通电阻随温度的变化关系, 150°C时SiC基 Ga2O3异质集成晶体管导通电阻相比于室温时略有下 降, 而Ga2O3衬底上器件导通电阻均增加12%以上[35] 。

如图3(c), (d)所示, 采用凹槽栅和场板结构相结合 制备的SiC基Ga2O3 MOSFETs, 在漏端电压VDS为5 V的 条件下, 实现了19。15 mS/mm的峰值跨导, 开态电流超 过300 mA/mm, 导通电阻RON仅为24 Ω mm, 对应的特 征导通电阻率RON,SP为0。72 mΩ cm2。对比已报道数据, 制备的凹槽栅场板结构GaOSiC MOSFETs实现了目前 最低特征导通电阻值, 如图3(e)所示[36]。 通过增加器件 栅漏尺寸, 器件击穿电压超过1000 V, 在工作环境温度 由25°C增加至200°C时, 其击穿和输出特性没有发生明 显的衰退, 如图3(e)所示[36] 。器件良好的温度稳定性源 于衬底良好的导热性和绝缘层上薄膜结构有效抑制器件静态泄漏电流随工作环境温度的迅速增加。

综上所述, 高导热衬底Ga2O3异质集成晶体管展现 出远优于Ga2O3体衬底器件的热稳定性和温度相关性, 根据实验结果, 在室温至250°C的工作温度范围内, 其 呈现出稳定的器件电学特性。

2.2 Ga2O3异质集成晶体管迁移率

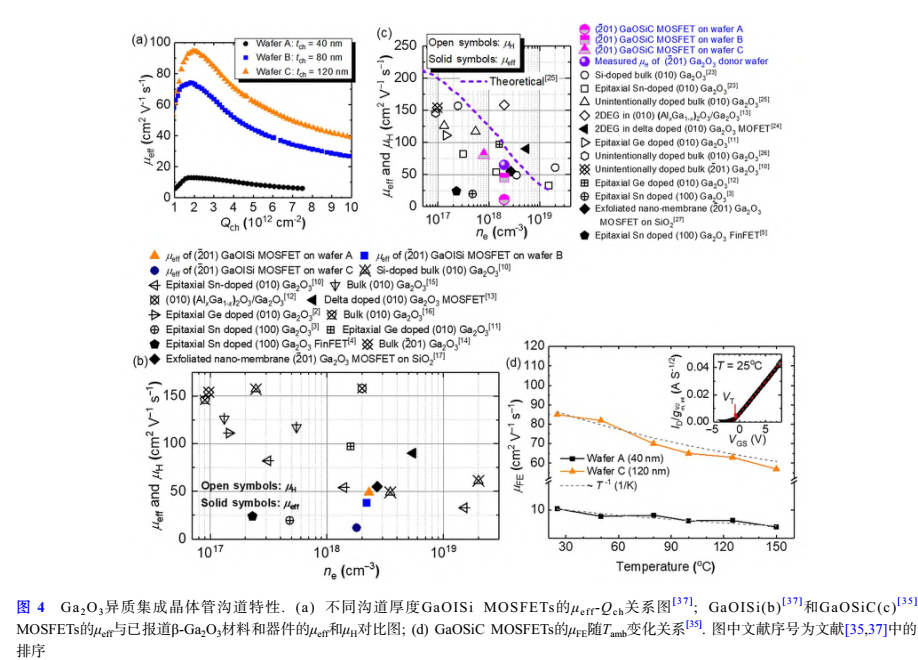

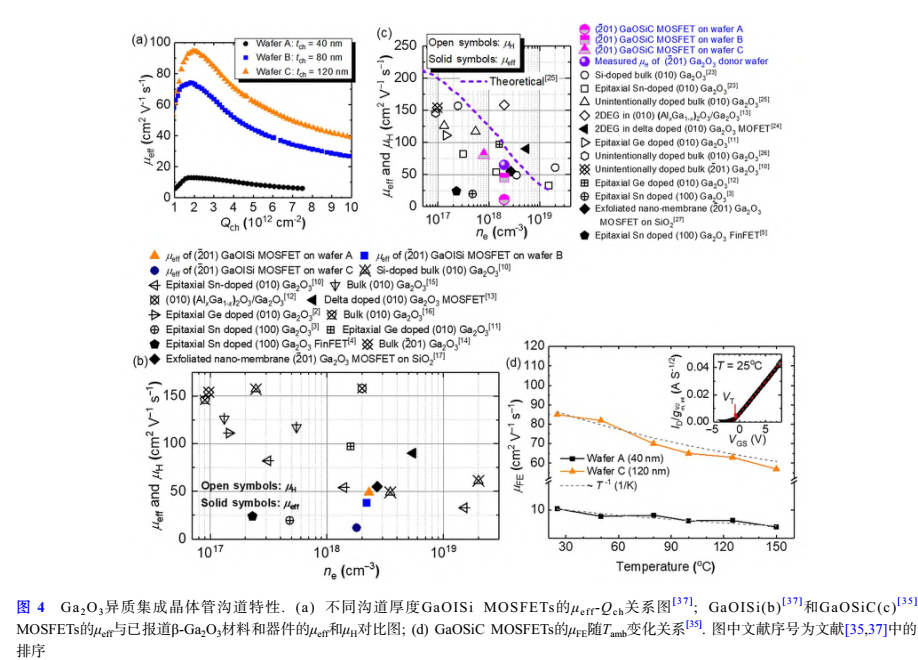

晶体管迁移率反映载流子导电能力的大小, 是晶 体管电学特性中最为关键的参数之一。我们对高导热 衬底Ga2O3异质集成晶体管的沟道特性进行了深入分 析, 探究了不同沟道厚度和不同激活温度条件下, Ga2O3异质集成沟道有效迁移率μeff的变化规律以及晶体管场 迁移率的温度相关性和作用机制。

基于Si基Ga2O3 MOSFETs(GaOISi MOSFETs)测试 的栅电容和转移特性曲线, 计算得到不同沟道厚度(tch) 晶体管的μeff随沟道内电荷密度的变化关系如图4(a)所 示。随着沟道厚度减小, 器件的μeff降低, 沟道厚度为 120 nm时(Wafer C), μeff峰值高达约95 cm2 V- 1 s- 1, 而沟道厚度减少至40 nm时(Wafer A), 其μeff峰值不足 20 cm2 V- 1 s- 1[37] 。

如图4(b)所示, 对比了Si基Ga2O3MOSFETs的μeff与 报道的同质外延β-Ga2O3 、delta掺杂Ga2O3和β-Ga2O3体 材料中的霍尔迁移率μH和(AlGa)2O3/Ga2O3 中二维电子 气(two dimensional electron gas, 2DEG)迁移率以及同 质外延材料制备的β-Ga2O3 MOSFETs中的μeff[37] 。

在相 近的掺杂浓度条件下, 沟道厚度为120 nm的硅基Ga2O3 MOSFETs(Wafer C)的μeff与同质外延β-Ga2O3薄膜和体 材料中的μH水平相当, 证明采用离子注入-键合剥离技 术制备的高导热衬底Ga2O3异质集成晶圆具有与Ga2O3 体材料相当的迁移率特性。基于SiC基Ga2O3 MOSFETs (GaOSiC MOSFETs)探究器件μeff与注入激活温度的关 系。将提取的器件μeff与报道的迁移率结果进行对比, 如图4(c)所示, 虚线为考虑各种散射机制作用的迁移率 随掺杂浓度变化的理论计算结果。

1200°C退火的GaO-SiC MOSFET(Wafer A)实现μeff约为80。5 cm2 V- 1 s- 1, 而1100°C退火(Wafer B)器件的μeff与剥离前β-Ga2O3 晶 圆的μH值相近, 表明在1100°C退火后, 剥离和注入产生 的缺陷得到有效恢复, 更高激活温度将进一步提升迁 移率[35] 。

基于SiC基Ga2O3 MOSFETs的变温转移特性结合 Y-function, 研究其场迁移率μFE 随测试温度Tamb 的变化 关系, 如图4(d)所示[35] 。 在Tamb 由25~150°C变化过程中, SiC基Ga2O3 MOSFETs的μFE与测试Tamb满足T 1amb变化 关系, 随着Tamb 的升高, μFE逐渐降低。

在声子散射效应 起主要影响作用时, 迁移率与温度遵从T-3/2amb 的规律 变化, 而当杂质散射占主导作用时, 变化规律为T3/2amb, 所以制备的SiC基Ga2O3 晶体管的μFE 随Tamb 的变化规律 主要由声子散射机制决定, 杂质散射对声子散射起到 一定的补偿作用, 在两者共同作用下, 呈现T- 1amb 的变 化关系。 结合相关特性分析, 上述结果表明载流子被严格限制在顶层Ga2O3薄膜内运动, 呈现电学上的pn结限 制效应, 有利于减小器件泄漏电流。

3 p-NiO/n-Ga2O3异质结超结晶体管

3.1 异质外延集成功率二极管

Ga2O3是一种离子性很强的超宽禁带半导体材料, 存在p型掺杂困难的关键瓶颈问题[38] 。相比于单极型器 件, 采用p-n结构设计的双极型器件具有电导调制能 力 、雪崩能力和更优异的浪涌电流能力, 同时可以通 过降低表面电场(reduced surface electric field, RES- URF)设计更多的终端结构[2] 。

在p型掺杂难以实现的情况下, 将Ga2O3与其他p型 材料进行异质集成, 可以为Ga2O3基功率器件设计提供 新的自由度。目前研究较多的p型材料主要包括SnO 、 CuAlO2家族及NiO等, 其中p-NiO/n-Ga2O3异质结展现出极佳的性能[2] 。

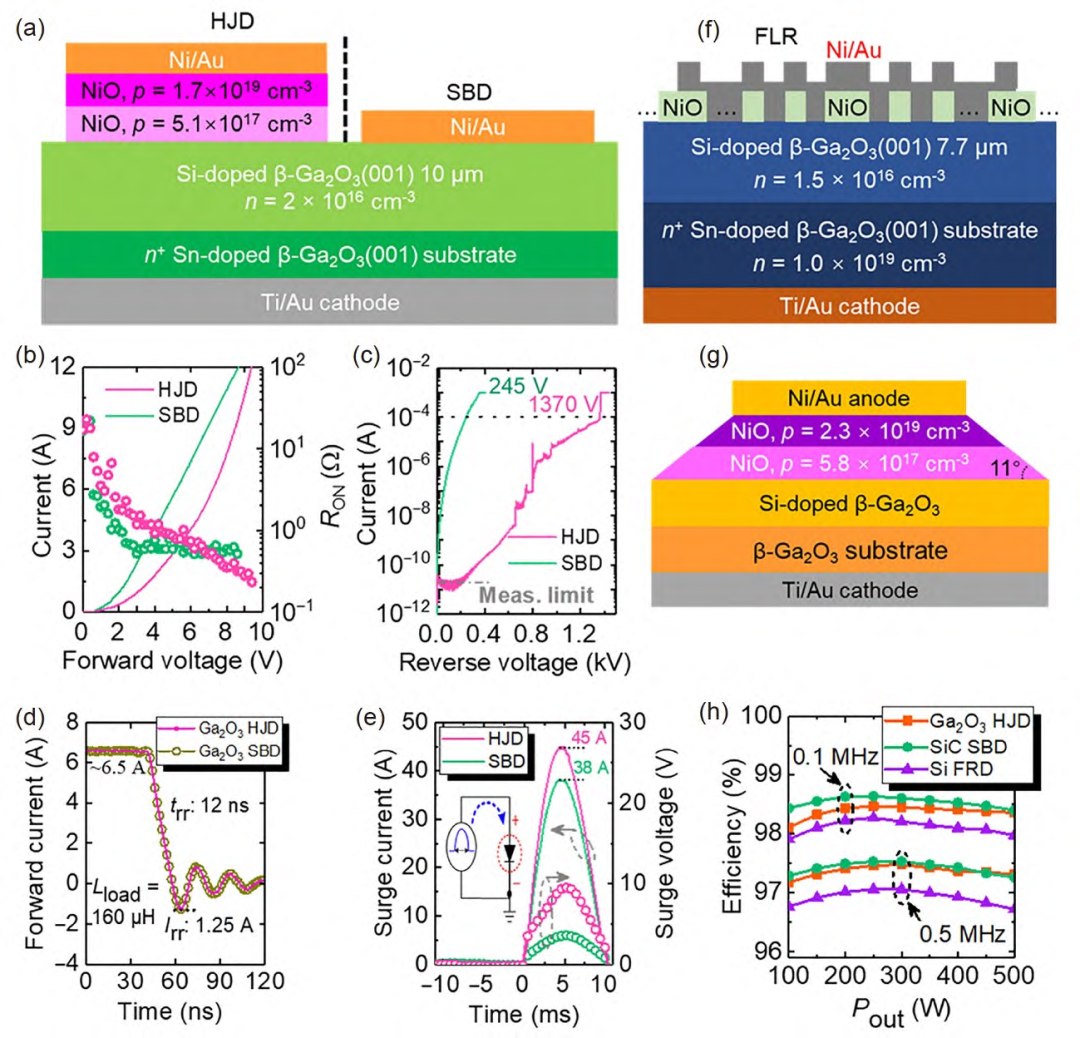

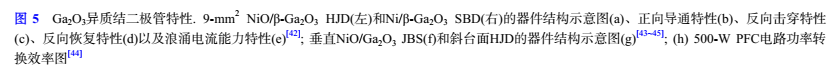

理想化学配比的NiO薄膜是一种室温 绝缘体, 通过增加Ni空位和/或填隙氧原子, 可有效降低 NiO的电阻率, 使之呈现良好的p型导电, 掺Li的NiO薄 膜电导率可降低到~1。4 Ω- 1 cm- 1[39] 。 近年来, 多家研究 单位基于p-NiO/n-Ga2O3异质结, 制备出低漏电、高耐 压的pn异质结二极管(heterojunction diode, HJD)整流 器件, 其击穿电压远超过未使用终端和场板结构保护 的SBDs[40~42] 。

2020年, 南京大学团队[41]采用双层NiO结构与Ga2O3 异质集成, 实现了器件极低的泄漏电流, 器件在400 K 工作温度下仍具有高于1010 的开关比, 同时其击穿电压 达到了1。86 kV。 2021年, 南京大学团队[42]进一步改善 NiO溅射工艺, 实现了具有1。37 kV/12 A开关能力的大 面积HJD, 首次在实验中发现HJD具有一定的电导调制 能力, 其导通电阻随着正向偏压的增加逐渐减小, 且具 有明显降低的反向泄漏电流, 1 mm×1 mm器件击穿电

压达到1.37 kV, 远超Ga2O3 SBD的245 V。 在动态特性方 面, HJD具有与SBD几乎相同的反向恢复时间, 仅为 12 ns; 同时, HJD具有更优异的浪涌电流能力, 在10 ms 的浪涌应力持续时间下, HJD可以承受的峰值浪涌电流 达到45 A, 超过SBD的38 A, 如图5(a)~(e)所示。

为了减少HJD的开启电压, 南京大学团队[44]实现 了场限环结构的异质结势垒肖特基二极管(junction barrierSchottky, JBS), 结构如图5(f)所示, 器件同时具有 低开启和高阻断能力。 通过引入斜台面NiO技术, 南京 大学团队[45]进一步实现了击穿电压达到2 kV的大电流 功率HJD, 器件结构如图5(g)所示。

功率转换能力是评 估功率器件的一种简单有效的方法, 南京大学团队[44] 构建了一个500 W的功率因数校正(power factor correc- tion, PFC)电路, 在国际上首次采用NiO/Ga2O3 HJD实现 了98.5%的功率转换效率, 如图5(h)所示。

以上研究结果表明, p-NiO/n-Ga2O3异质结的优异 性能为Ga2O3功率器件结构设计和实际应用空间提供了更多可能性。

3.2 Ga2O3超结晶体管

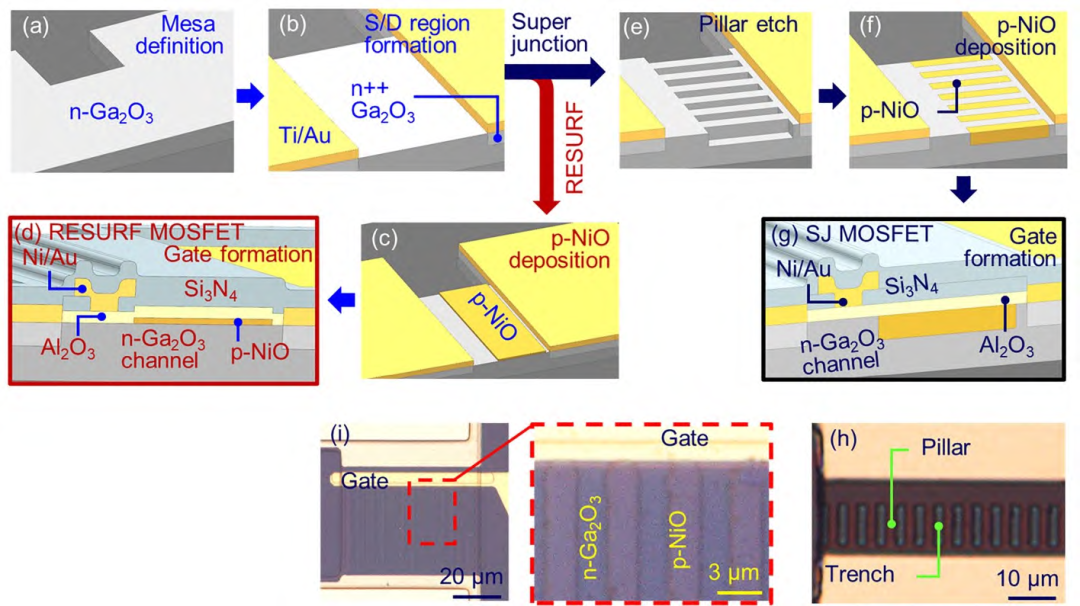

p-NiO/n-Ga2O3异质结展现出良好的电学特性, 西 安电子科技大学和南京大学合作团队基于其设计 、制 备了表面电场降低和超结结构β-Ga2O3 MOSFETs, 制 备流程如图6所示[24] 。

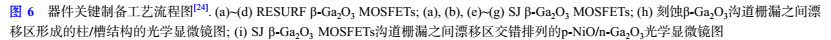

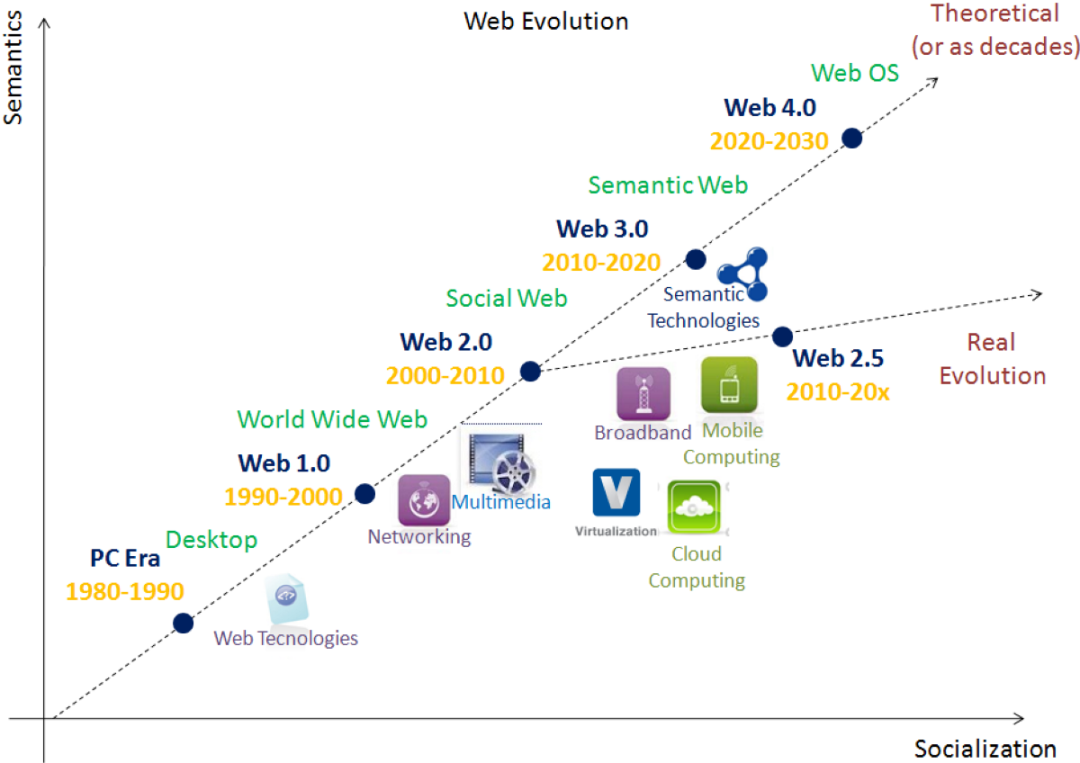

SJ β-Ga2O3 MOSFETs展现出与相同结构尺寸常规 器件相似的转移特性曲线, 如图7(a)所示。 随着p-NiO条 宽度增加, SJ β-Ga2O3 MOSFETs相比于对照器件, 开态 电流略有下降, 导通电阻略有上升[24] 。随着p-NiO条宽 度的增加, SJ β-Ga2O3 MOSFETs的击穿电压呈现先增 加后减小的变化趋势, 在p-NiO条宽度为2 μm时, 实现 了1326 V的高击穿电压,而在p-NiO条宽度增加至3 μm 时, 其击穿电压发生退化, 如图7(b)所示[24] 。

在p-NiO条 宽度为2 μm时, SJ β-Ga2O3 MOSFET的击穿电压相比于 相同结构参数的常规器件获得了2.42倍提升, 对应于功率品质因子(power figure of merit, PFOM)实现4。86倍的 提升, 如图7(c)所示[24] 。 随着尺寸的增加, 由于SJ结构对 器件的抑制影响, 其击穿电压和功率品质因子均发生 退化, 表明p-NiO条宽度在0~3 μm之间存在最优尺寸, 使得击穿电压达到最大值。

同时, 随着击穿电压和导通 电阻的权衡, 存在一个最优尺寸使得SJ β-Ga2O3 MOS- FETs的综合性能最优。 根据理论分析, 该值可能更靠近 于0 μm区域, 即交错的p-NiO/n-Ga2O3条以纳米尺度交 错排列 、相互实现全耗尽, 可实现更优的击穿电压和 功率品质因子; 而在相互全耗尽尺寸下, 结合其内载流 子浓度值变化实现理想的电荷平衡状态, 则可以实现 最优的击穿电压和功率品质因子, 但平衡状态对器件设计、制备等均具有一定的挑战性。

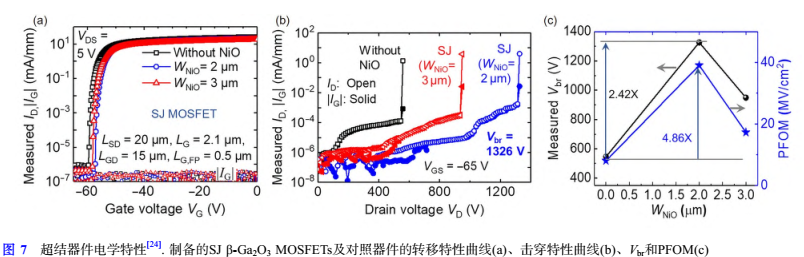

击穿电压的显著提升源于超结结构对晶体管漂移 区电场的重构作用。SJ结构器件将常规MOSFET器件 三角形电场分布向漏端平滑, 转变为矩形电场分布,有 效抑制了漂移区边缘峰值电压的上升速度, 进而增加 了器件的击穿能力, 对应器件电场仿真结果如图8所 示[21] 。

综上所述, 基于p-NiO/n-Ga2O3异质结设计的双极 型二极管和超结结构Ga2O3 MOSFETs均展现了良好 的电学特性, 其为Ga2O3缺少p型材料的难题提供了一 个有效的解决方案, 进一步拓宽了Ga2O3器件的应用 广度。

4 总 结

本文介绍的高导热衬底异质集成晶体管和超结晶 体管两类Ga2O3功率晶体管均为我国创新实现。 利用离 子注入-键合剥离工艺实现的高导热衬底Ga2O3异质集 成晶圆和器件是解决Ga2O3低导热瓶颈的有效方法。 实 验证明, SiC基Ga2O3 晶圆热导率达到9。0 W/mK, 界面热 阻为7。5 m2 K/GW, 其热扩散速率接近于SiC晶圆, 远优 于Ga2 O3 晶圆; 同时制备的Ga2 O3 异质集成晶体管在 250°C仍保持着极佳的热稳定性, 开关态特性退化小于 两个数量级, 器件综合性能达到Ga2O3器件主流水准。

超结晶体管是唯一已被证明可以突破功率半导体击穿 极限的器件结构, 由于p-Ga2O3 的缺少而不易实现。

相 关研究创新性地利用p-NiO/n-Ga2O3异质结实现了超结 结构Ga2O3 MOSFETs, 器件的击穿电压相比于同步制 备的相同结构参数常规器件获得了2。42倍提升, 对应于功率品质因子实现4。86倍的提升。

随着p-NiO外延技术的不断成熟以及p-NiO/n - Ga2O3异质结研究的深入, 在p型Ga2O3掺杂难以实现的 现状下, p-NiO/n-Ga2O3异质结必将是高性能Ga2O3器件 的有效解决方案。

目前高导热衬底Ga2O3异质集成晶体 管性能已经逐步接近Ga2O3体衬底器件的主流水平, 随 着对其注入激活工艺 、欧姆接触工艺 、沟道界面处理 工艺等的开发以及复合场板结构 、浮空栅结构等设计 的深入研究, 将进一步提升高导热衬底Ga2O3异质集成 晶体管器件性能, 特别是与p-NiO/n-Ga2O3异质结的结 合, 开发实现高导热衬底Ga2O3异质集成超结晶体管, 将有望实现器件性能突破材料极限且热导性能极佳的 Ga2O3功率器件。 高导热衬底Ga2O3异质集成和p-NiO/n- Ga2O3异质外延技术将有效推动Ga2O3功率晶体管的发 展, 助力其在功率、射频等领域的实用化进程。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论