1、市场

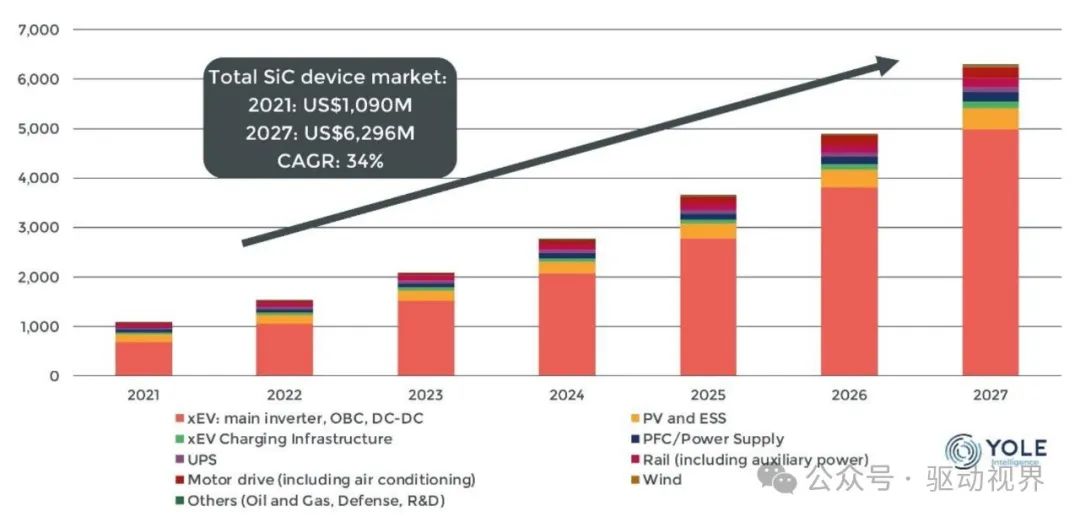

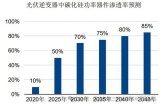

随着新能源汽车、光伏、充电桩等应用对系统效率的不断追求,功率半导体市场将迎来前所未有的增速。

SiC功率器件市场规模:

▲Source:Power SiC report,Yole intelligence,2022

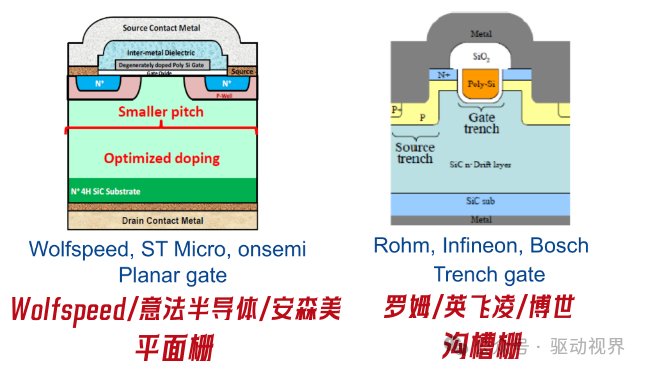

SiC市场格局仍由海外巨头主导,市占率排名依次是:意法半导体、英飞凌、wolfspeed、罗姆、安森美、三菱电机等。

特斯拉是业界首个在电动汽车逆变器中采用SiC的车企,2018年,特斯拉在model 3中首次将IGBT换成SiC。

2、分类和应用

导电型SiC目前主要应用于逆变器中,用于制造功率器件。逆变器将电池的直流电转化为电机所用的交流电,在传统Si基IGBT逆变器中,利用方波电源控制IGBT的开关,使得原来的直流电输出方波高压电,经过整形后形成正弦电压,即交流电。

由于输出电压和输出频率可以任意控制,所以逆变器广泛用于控制交流电机和无刷电机。

半绝缘型衬底主要用于制造氮化镓射频器件等,通过在半绝缘型SiC衬底上生长氮化镓外延层,制得碳化硅基氮化镓外延片。

3、原理和优势

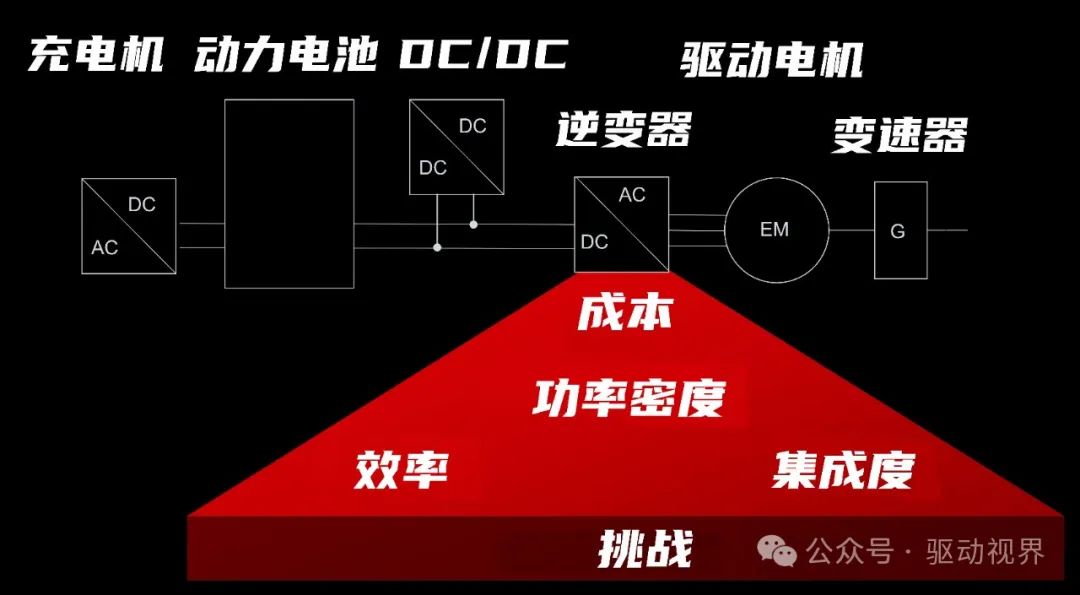

▲电驱动主要部件和挑战 电动汽车驱动用模块(Power Module for EV)的特点:

(1)布置空间受限(Limited);

(2)温度变化大(-40℃~105℃);

(3)振动剧烈(Tough);

(4)可靠性要求高(Higher);

(5)通常为水冷(体积小)(Water);

(6)需要精确的力矩控制,要求动态性能较好(High requirement);

(7)要求性价比高(High requirement)。

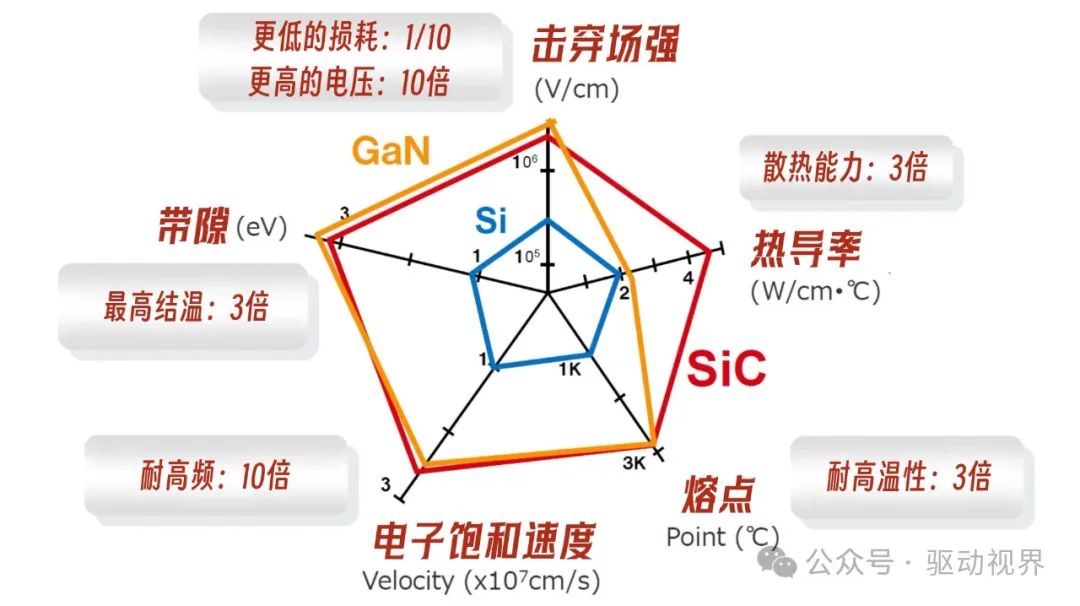

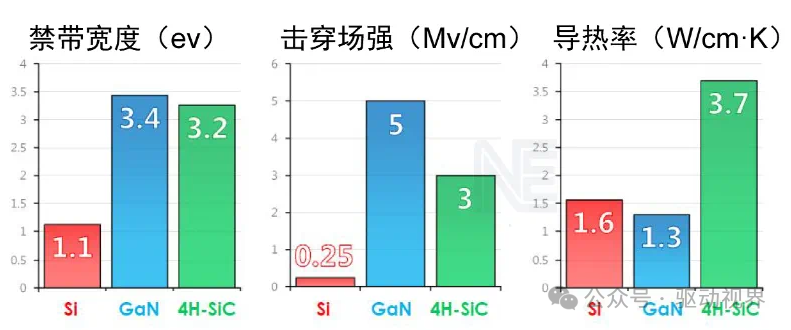

SiC碳化硅是由碳元素和硅元素组成的一种化合物半导体材料,是制作高温、高频、大功率、高压器件的理想材料之一。

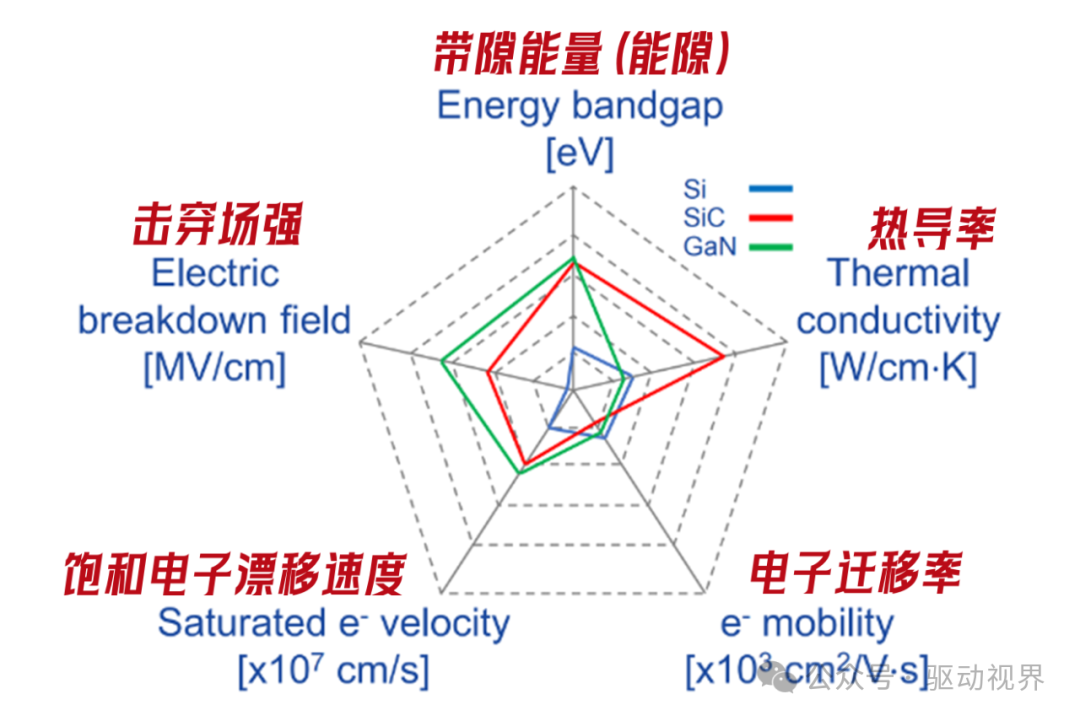

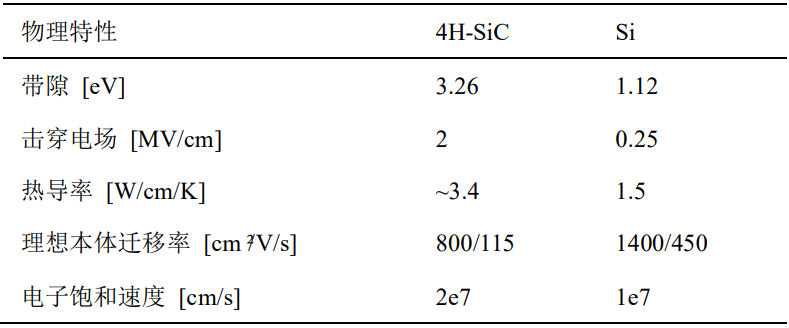

相比传统的硅材料,碳化硅的禁带宽度是硅的3倍,导热率是硅的4-5倍,击穿电压是硅的8-10倍,饱和电子漂移速率是硅的2-3倍。

碳化硅器件的核心优势在于:

1)耐高压:阻抗更低、禁带宽度更宽,能承受更大的电流和电压,带来更小尺寸的产品设计和更高的效率;

2)耐高频特性:SiC器件在关断过程中不存在电流拖尾现象,能有效提高开关速度(大约是SiC的3-10倍),能达到更高频率和更高开关速度;

3)耐高温特性:SiC相对Si拥有更高的热导率,能在更高温度下工作。

碳化硅与硅基半导体相比(SiC VS. Si):

(1)击穿场强×10

(2)禁带宽度×3,极低的本征载流子浓度,耐高压、高温能力

(3)热导率×3,散热能力提升,有助于提升功率密度

以SiC和GaN为代表的宽禁带半导体是实现高效率能量转换、小型化、低系统成本的更佳选择。

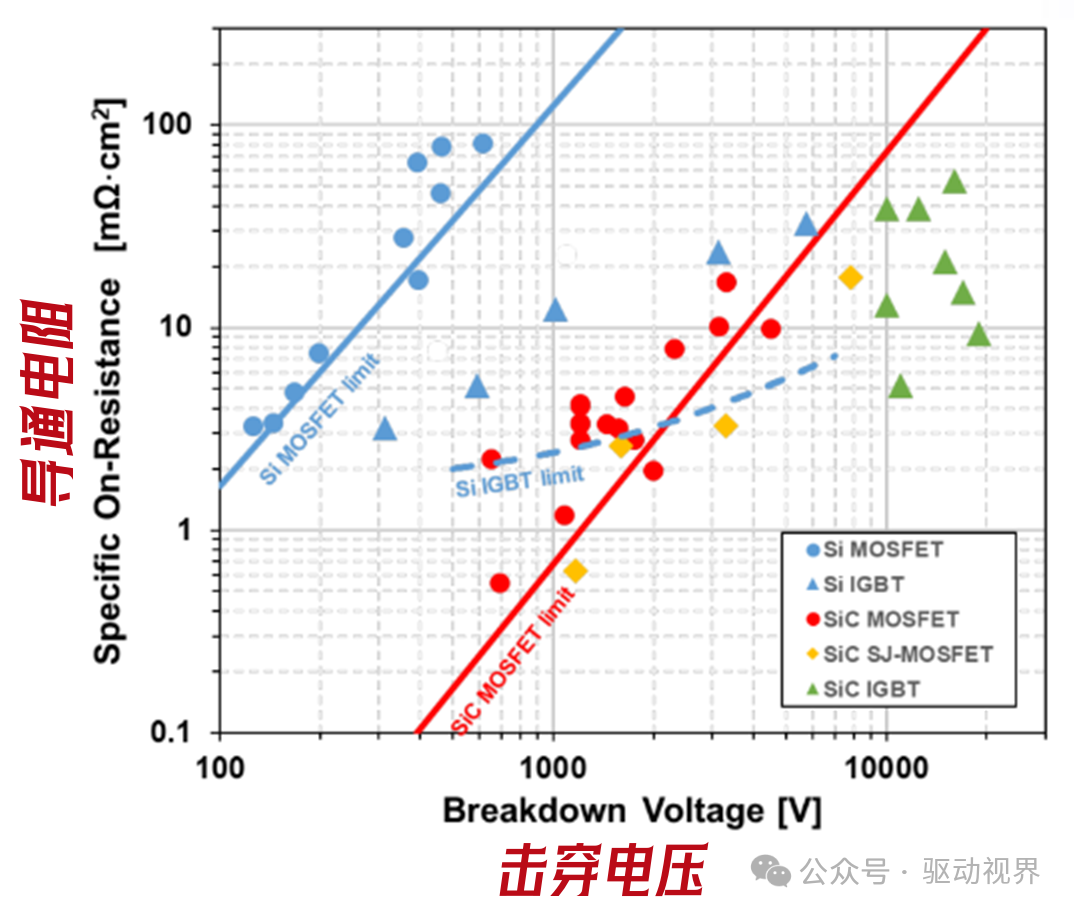

SiC MOSFET在多方面均表现出远超传统Si基器件的性能,有望在多个领域逐渐实现替代,可靠性与成本是商业化的核心

新型器件结构、高沟道迁移率、超级结、SiC-IGBT、SiC-IC是未来努力的方向

SiC卓越的材料性能:具有Si和C共价键的化合物半导体

极硬材料,新莫氏硬度:13(钻石15)

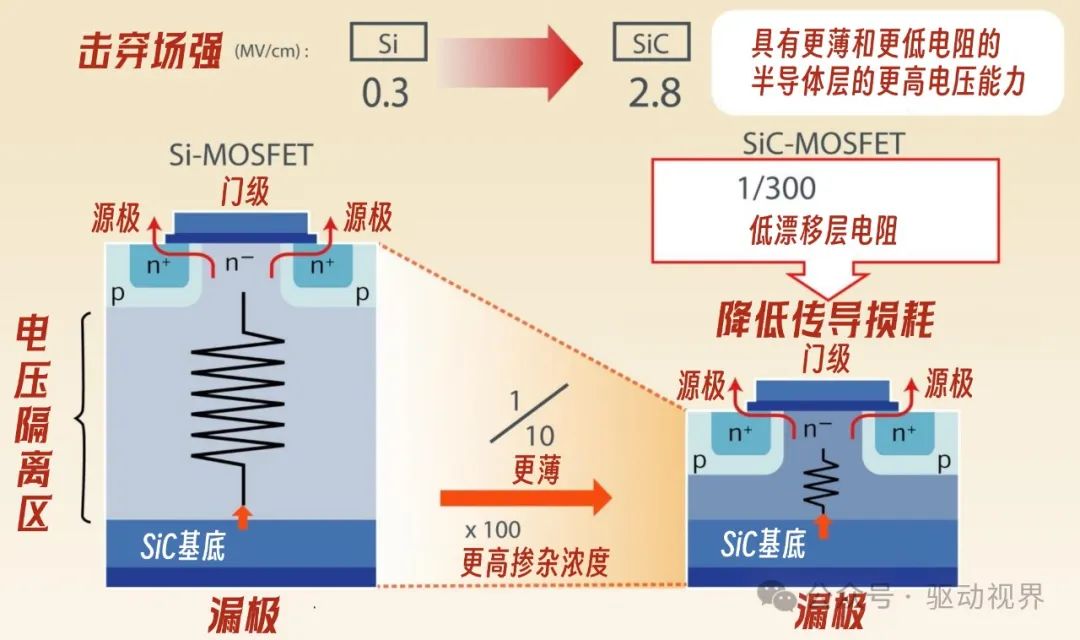

Si-MOSFET 和SiC-MOSFET结构单元比较:

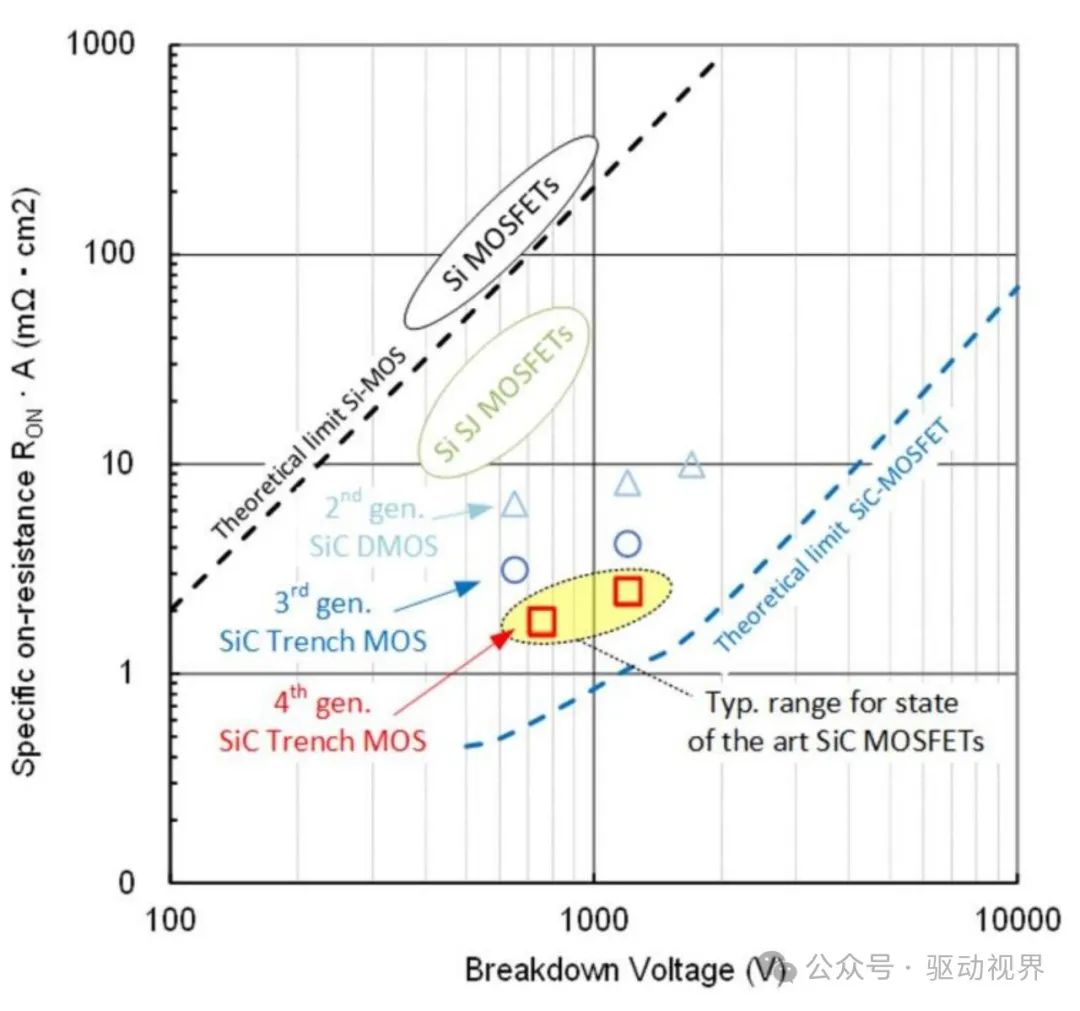

▲Si和SiC材料性能比较 SiC-mos 与Si-IGBT和Si-SJMOS的比较:

(1)与Si器件相比,SiC器件大大提高了工作性能

(2)每一代SiC器件都接近理论极限

(3)来自不同供应商的最先进的SiC MOSFET达到了同类产品的性能

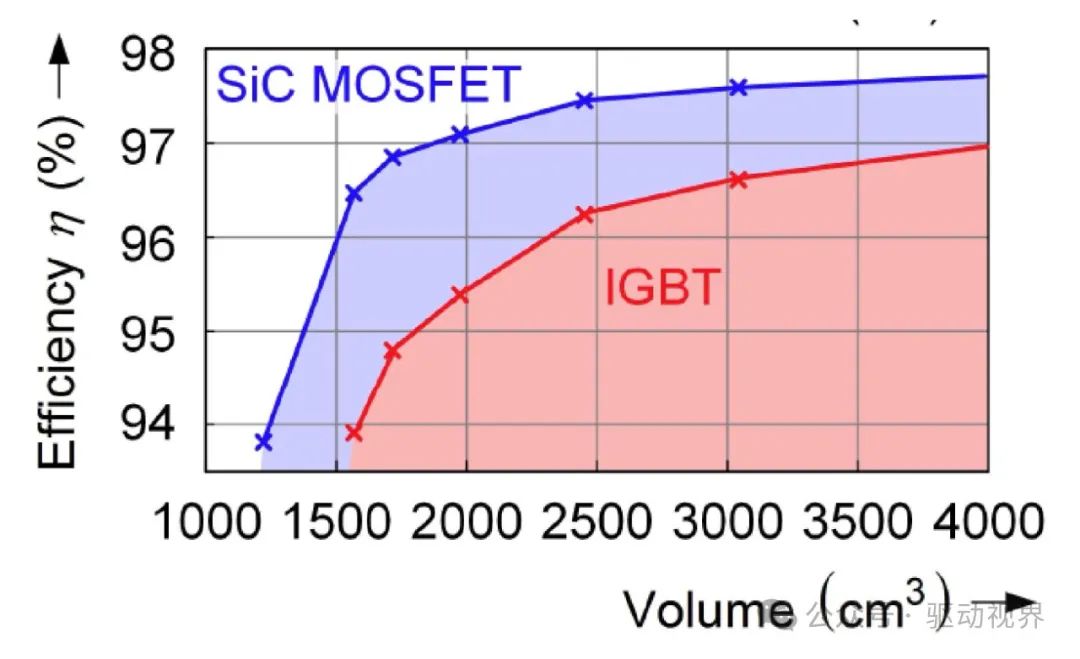

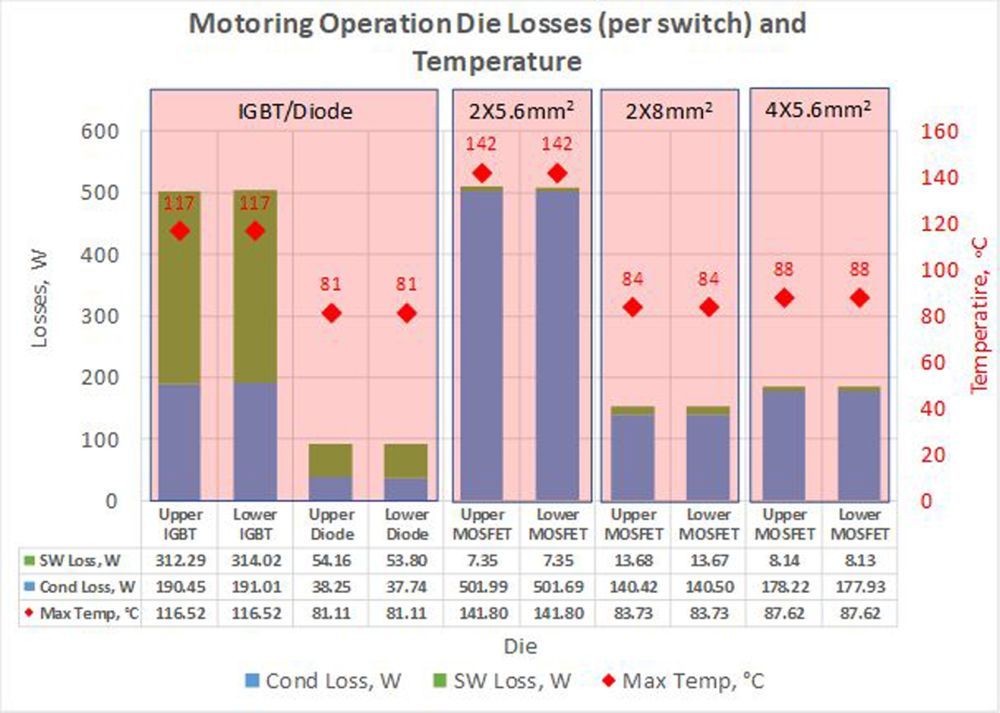

在电动汽车逆变器中采用SiC MOSFET的系统级效益:

SiC MOSFET技术的器件级优势:

(1)低导通损耗

(2)低开关损耗

SiC逆变器的系统级效益:

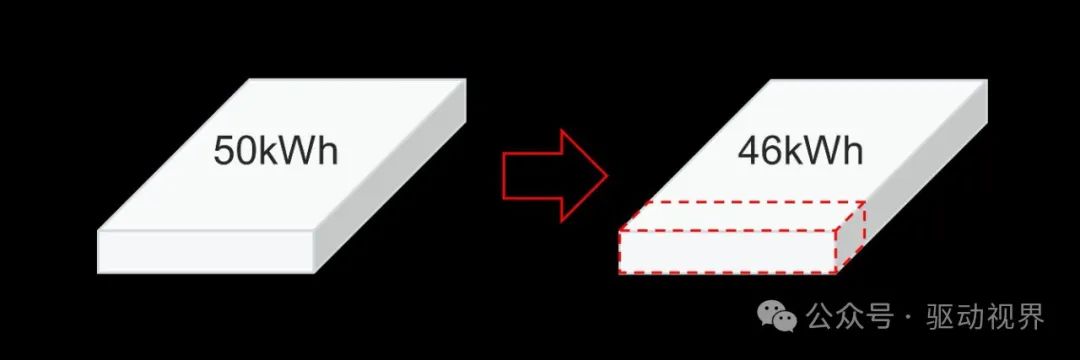

(1)高效率:在不牺牲车辆续航里程的情况下降低电池容量

(2)简化且更紧凑的冷却系统

▲基于SiC MOSFET的逆变器实现更高的效率

▲Nitzsche et al.,“Comprehensive Comparison of a SiC MOSFET and Si IGBT Based Inverter”,PCIM2019

锂离子电池尺寸和容量减少+保持续航里程不变

半导体成本的增加被电池费用的节省所弥补

相比传统硅基材料,SiC各项性能指标优势明显:

SiC MOSFET在电动汽车主驱逆变器中相比Si-IGBT优势明显,虽然当前SiC器件单车价格高于Si-IGBT,但SiC器件的优势可降低整车系统成本:

(1)由于SiC MOSFET相比Si-IGBT功率转换效率更高,根据Wolfspeed数据,采用SiC MOSFET的电动汽车续航距离相比Si-IGBT可延长5%~10%,即在同样续航里程的情况下可削减电池容量,降低电池成本;

(2)SiC MOSFET的高频特性可使得逆变器线圈、电容小型化,电驱尺寸得以大幅减小;

(3)SiC MOSFET可承受更高电压,在电机功率相同的情况下可以通过提升电压来降低电流强度,从而降低线束成本。

SiC器件相比Si基器件的优势:

(1)导通电阻小(Low resistance):是Si基器件的1/3~1/5;

(2)可高温工作(High temp.):是Si基器件的1.5~2倍;

(3)可高速开关(High frequency):是Si基器件的3~5倍

4、产品和技术

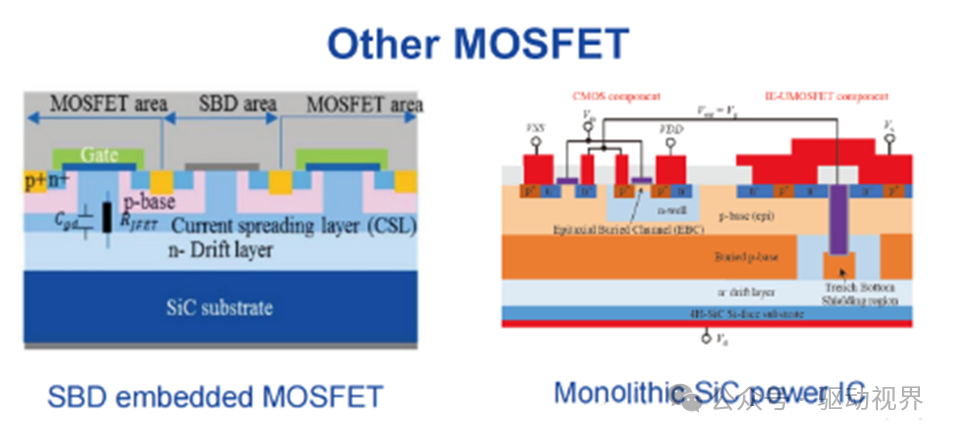

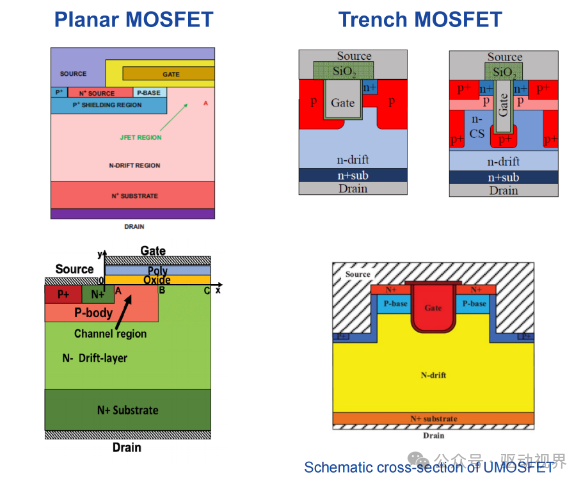

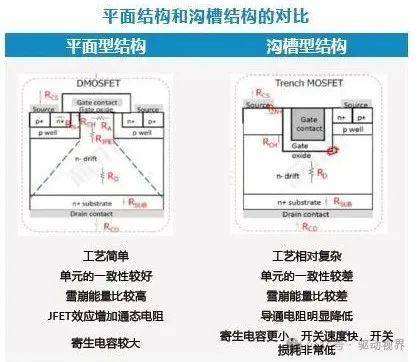

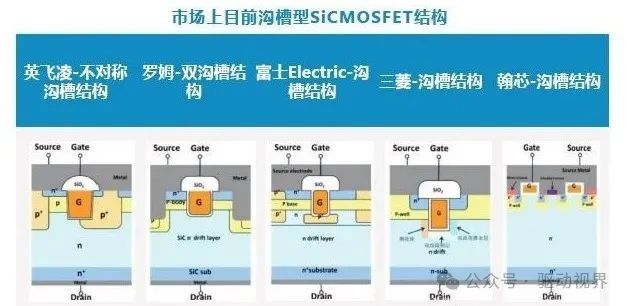

主流SiC功率器件结构:

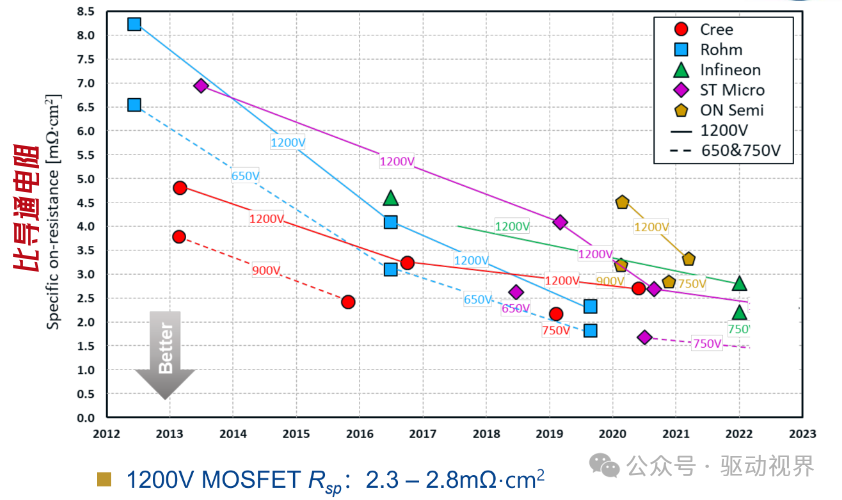

主流SiC MOSFET比导通电阻发展趋势

受工艺成熟度与稳定性影响,沟槽栅器件暂时并没有实现对平面栅结构的全面超越。

目前平面型结构式主流,未来沟槽型在高压领域会广泛应用。平面结构相比沟槽,不容易产生局部击穿问题,不影响工作稳定性,在1200V以下市场应用广泛。并且平面结构制造相对简单,成本可控。

沟槽型器件寄生电感极低,开关速度快,损耗低,器件性能相对高效。

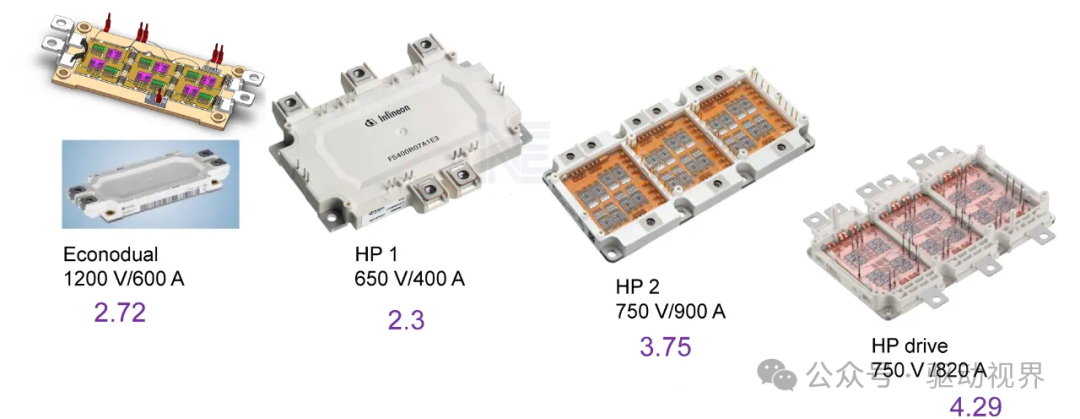

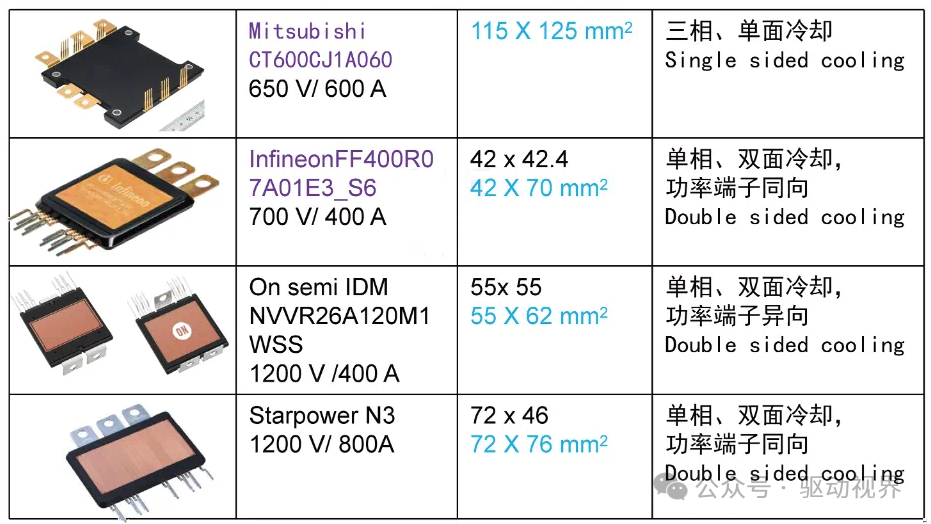

▲车用功率模块功率密度演化

等效单相功率密度=电压×电流÷体积×相数

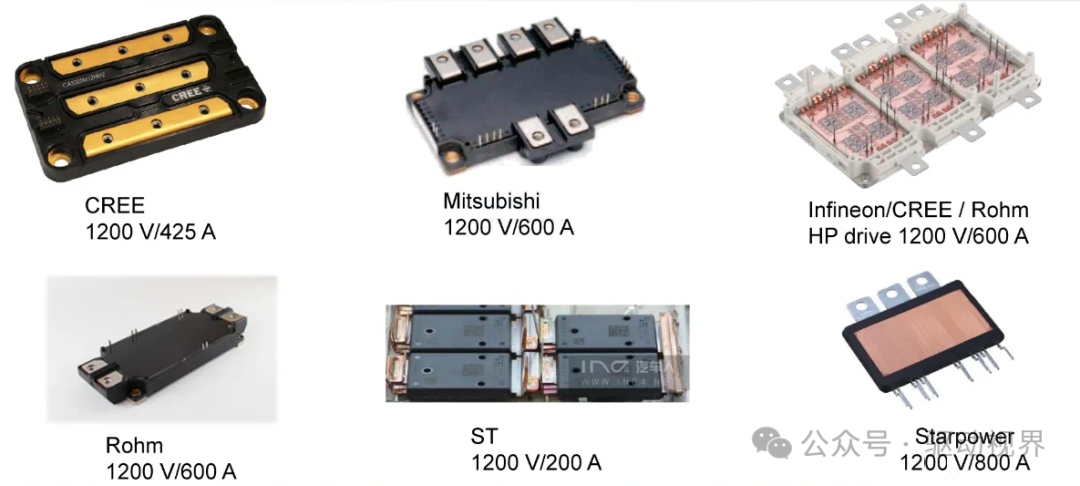

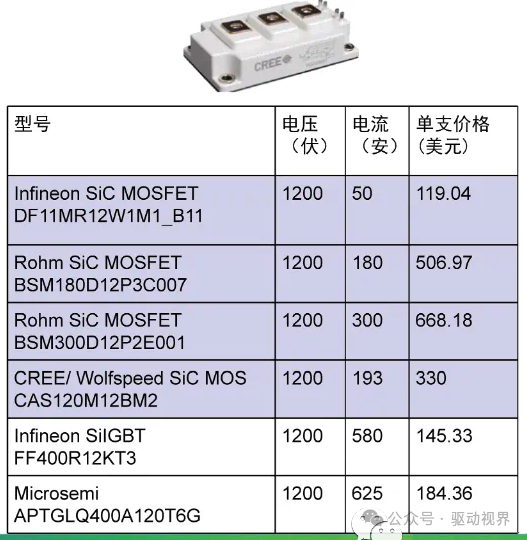

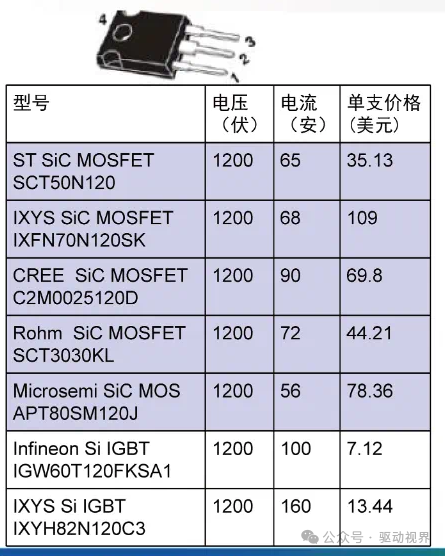

▲大功率SiC车用模块

▲器件价格对比

SiC行业存在的问题:

(1)SiC衬底制备成本高

(2)高端技术和人才缺乏

(3)国外技术封锁

(4)外延设备国产化率低

(5)产品良率低

SiC技术降本路径:

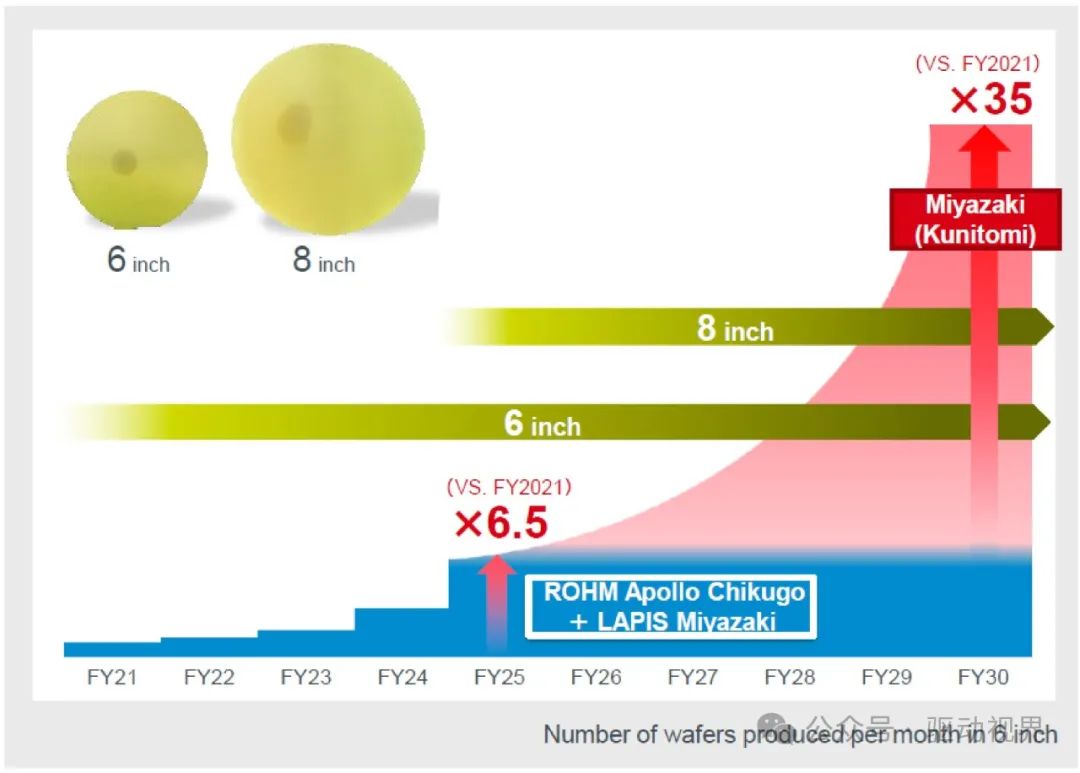

(1)扩大晶圆尺寸。从6寸晶圆转向8寸晶圆,SiC芯片(32mm²)数量有望从448颗增加到845颗;能够使整体碳化硅器件成本降低20%~35%。

(2)改进SiC长晶技术,提升长晶速度。

(3)应用ColdSplit技术分割碳化硅晶圆,从而使单个晶圆芯片数量翻倍。

5、设计和开发

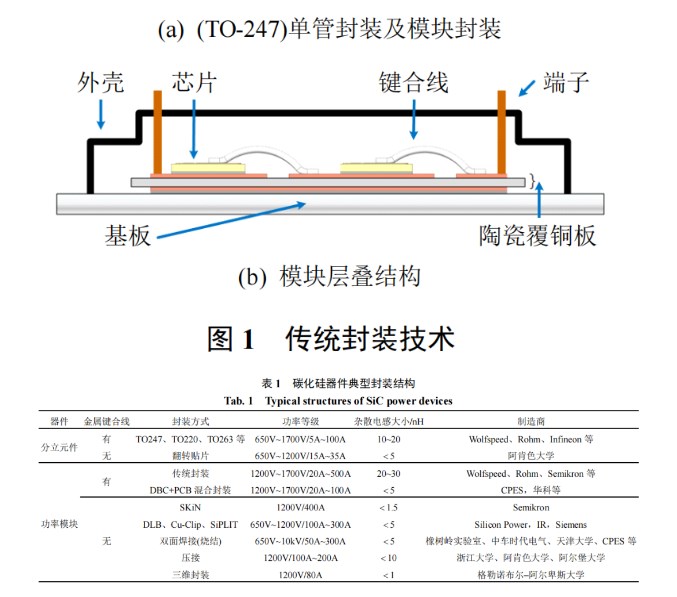

SiC器件应用需要突破的限制:

(1)突破现有模块150℃限制(Package limit for high temp.),实现功率模块200℃稳定运行;

(2)解决高速开关易受干扰问题(Gate drive limit for high freq.),实现高速门级驱动;

(3)解决散热过于集中问题(Thermal limit for high density),采用高效散热方法

碳化硅功率模块相关设计要点(SiC High Density Converter Design):

(1)模块布局(Module layout)

(2)高温封装(High temp. packaging)

(3)驱动设计(Gate drive design)

(4)保护设计(Sensor & protection)

(5)高温主回路(Busbar design)

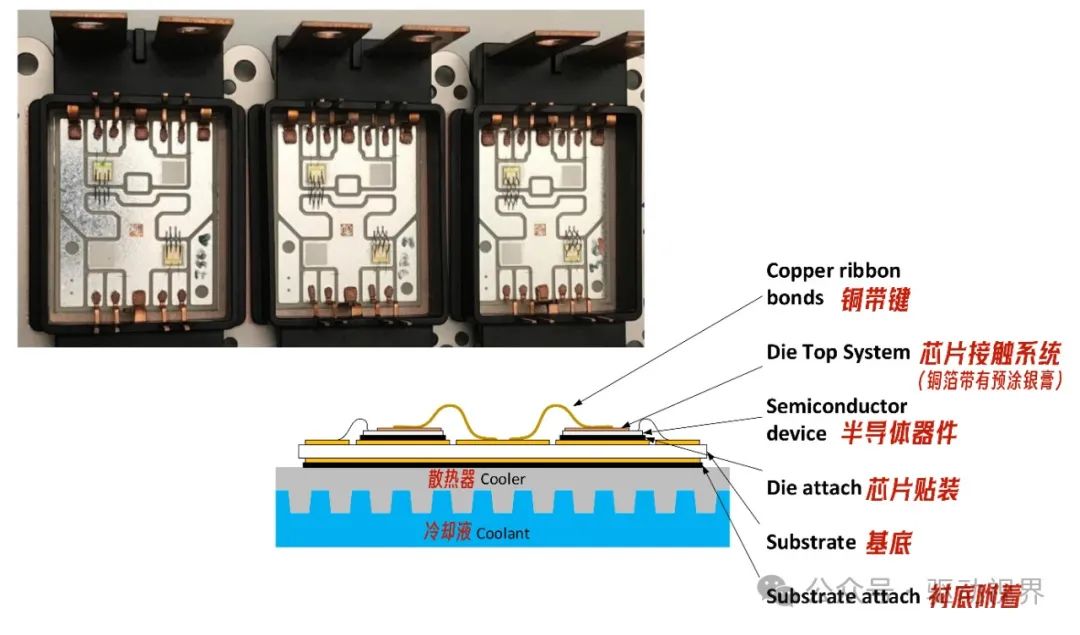

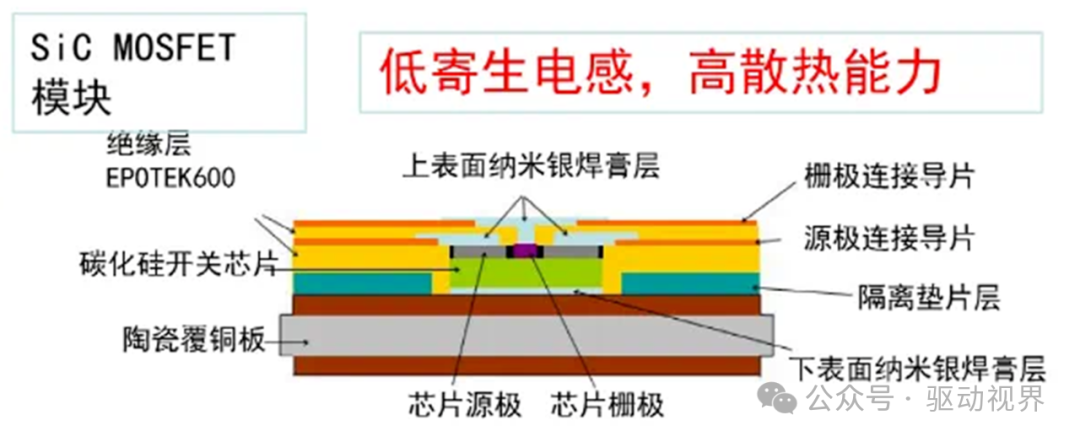

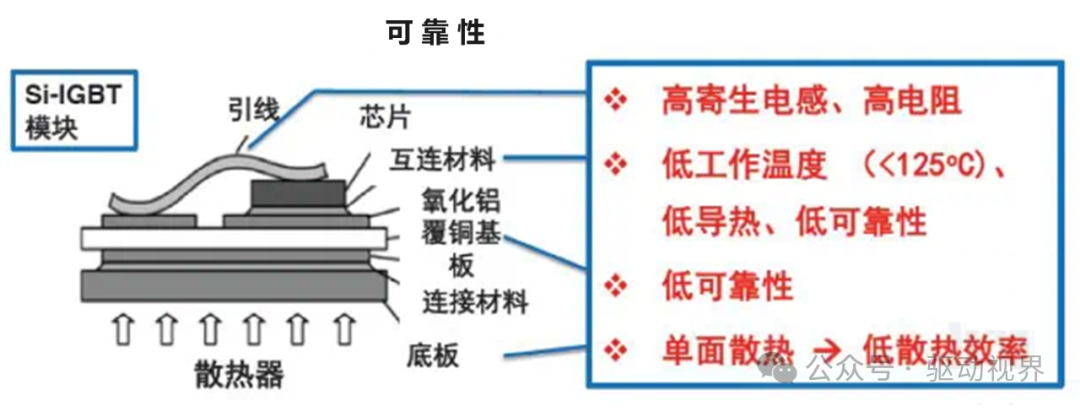

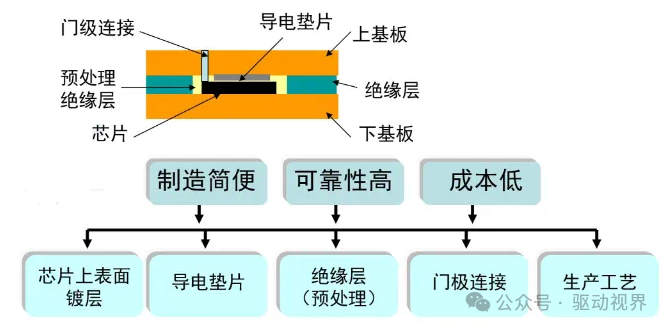

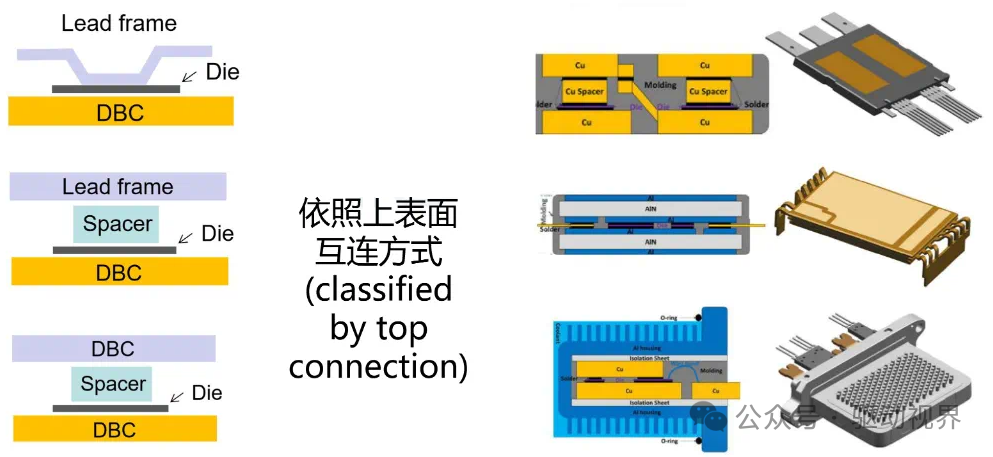

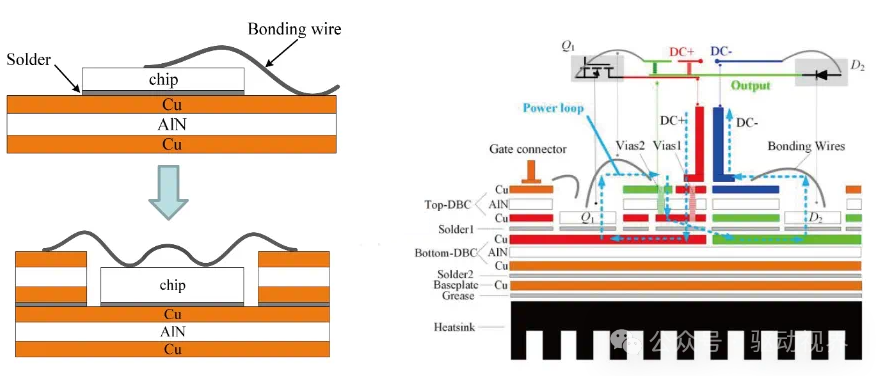

平面封装和双面冷却技术(Double)

(1)低寄生电感:电压过冲减小

(2)高散热能力:降低局部热点温度

(3)柔性互联/缓冲层:抗热应力能力提高

(4)无键合线:功率循环可靠性提高

▲平面型封装硅模块

▲平面型封装硅模块典型产品(Plannar Packaged Products)

▲平面型模块分类(Planar Package Classification)

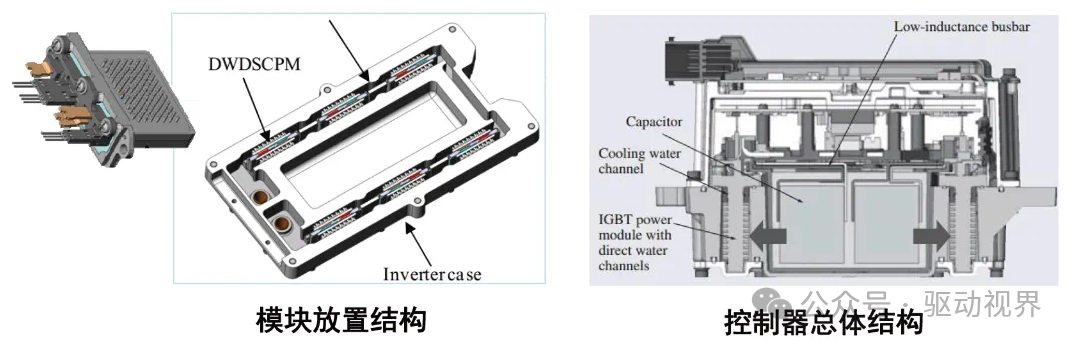

▲双面散热

双面散热(Double-sided Cooling)技术要点:

(1)互连与散热约束

(2)高性能母排

(3)散热平衡设计

(4)驱动板排布位置

▲无源器件水冷散热

2014年日本Hitachi硅基变频器,应用Pinfin双面冷却模块,电容水冷,峰值功率122.5kW,体积3.5L,功率密度35kW/L。

6、工艺、制造和产业链

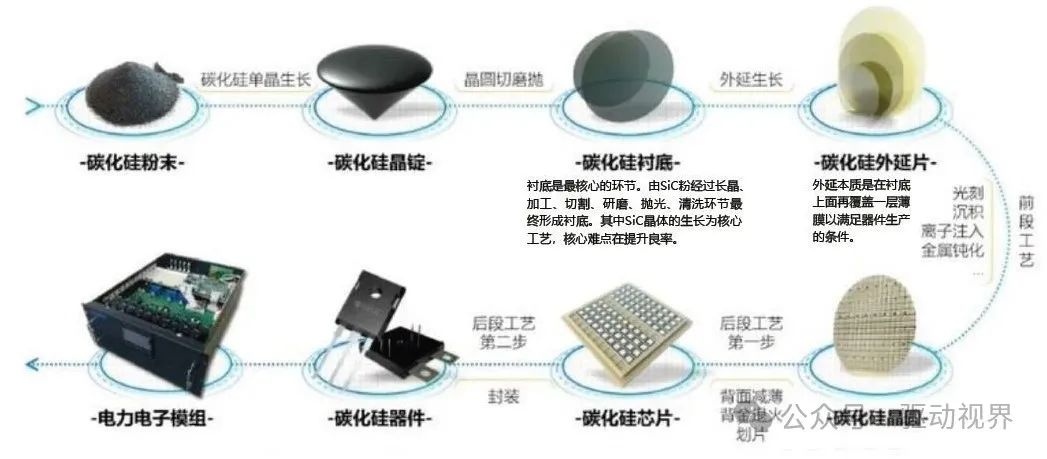

产业链上游是衬底和外延,中游是器件和模块制造,下游是终端应用。

产业链价值量倒挂,其中衬底制造技术壁垒最高、价值量最大,是SiC大规模产业化推进的核心。

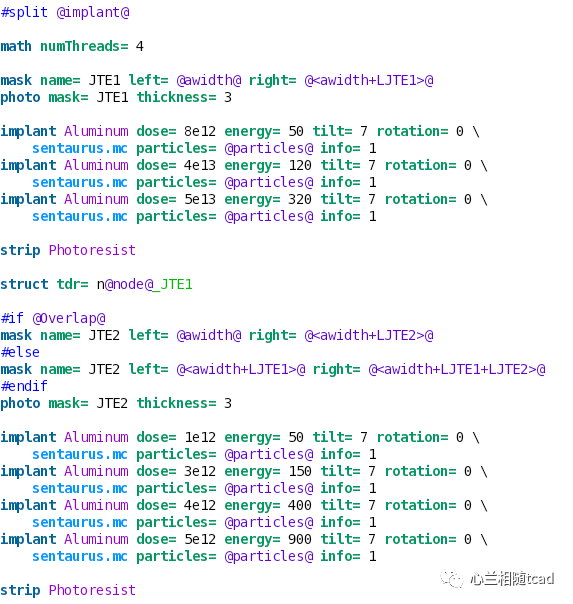

从工艺流程上看,碳化硅一般是先被制作成晶锭,然后经过切片、打磨、抛光得到碳化硅衬底;衬底经过外延生长得到外延片;外延片经过光刻、刻蚀、离子注入、沉积等步骤制造成器件。将晶圆切割成die,经过封装得到器件,器件组合在一起放入特殊外壳中组装成模组。

碳化硅单晶生长热场存在温度梯度,导致晶体生长过程中存在原生内应力及由此诱生的位错、层错等缺陷,降低可靠性。

SiC粉经过长晶、加工、切割、研磨、抛光、清洗环节,最终形成衬底。

▲SiC晶圆生产很复杂

与传统硅功率器件制作工艺不同,碳化硅器件不能直接制作在碳化硅衬底上,需在导电型衬底上生长碳化硅外延层得到碳化硅外延片,并在外延层上制造肖特二极管、MOSFET、IGBT等功率器件。

碳化硅衬底无法直接加工,需要生长一层薄膜后再进行加工。导电型衬底生长出同质外延层,半绝缘型衬底生长出异质外延层。

SiC晶体生长过程中会不可避免地产生缺陷、引入杂质,导致衬底材料的质量和性能都不够好。而外延层的生长可以消除衬底中的某些缺陷,使晶格排列整齐。

现在所有的器件基本上都是在外延上实现,所以外延的质量对器件的性能影响非常大。

在半绝缘型SiC衬底上生长氮化镓外延层,成为异质外延层;在导电型SiC衬底表面上生长一层碳化硅外延层,称为同质外延。

外延是一种常用的单晶薄膜制备技术,和Si器件工艺不同,几乎所有的SiC电力电子器件工艺都是在4H-SiC同质外延层上实现,衬底只是起到支撑和导电的作用。

电压越高,对外延厚度和掺杂浓度均匀性要求越高,生产难度越大。

外延片市场Wolfspeed一家独大,占据50%市场份额。

现在SiC薄膜外延的方法主要有:化学气相沉积(CVD)、分子束外延(MBE)、液相外延法(LPE)等,其中化学气相沉积(CVD)是最为普遍的4H-SiC外延方法。

SiC单晶方面主要三个难点:

(1)生长温度在2300℃以上,对温度和压力的控制要求高;

(2)长晶速度慢,7天时间大约可生长2cm碳化硅晶棒;

(3)晶型要求高、良率低,只有少数几种晶体结构的单晶型碳化硅可作为半导体材料。

7、概念和定义

(1)能隙(Bandgap energy gap)或译作能带隙,在固态物理学中泛指半导体或是绝缘体的价带(valence band)顶端至导带(conduction band)底端的能量差距。

(2)电子迁移率(electron mobility)是固体物理学中用于描述金属或半导体内部电子在电场作用下移动快慢程度的物理量。

(3)DTS(Die Top System):是一种芯片顶部系统技术。

模块内部采用的连接技术最常见的是焊接和铝线互连,通常使用的铝线线径在100um~500um,在150℃以上时可靠性就有了局限性。

随着运行温度和可靠性要求的提升,在车规模块中采用铜线代替铝线是趋势,但铜线直接键合到传统的芯片金属化会导致一些损伤和缺陷。

贺利氏推出的DTS技术有效地解决了硬铜线绑定的一些问题,包含了在铜片上的预涂银层来保护芯片免受相对于铝绑定线而言更高的键合力,同时将芯片电流产生的热量均匀地分布到整个芯片表面,降低芯片局部温度。

传统焊料的熔点在220℃~240℃,在较高的运行温度下会出现过早的失效,特别是碳化硅此类的宽禁带半导体。而银的熔点在962℃左右,非常薄的银层(如20um或30um)作为粘合层,能够满足高温要求。同时银具有较低的热阻。

DTS是铜箔带有预涂银膏的组合,主要适用于单面水冷设计,其中芯片的热量也可以有效的从芯片顶部耗散。

DTS系统与银烧结结合应用对其可靠性有巨大的影响。仅用银烧结剂代替焊料,用DTS烧结和铜线代替顶部铝线,在极端条件下,结温度至少降低了10K,寿命至少增加了10倍。

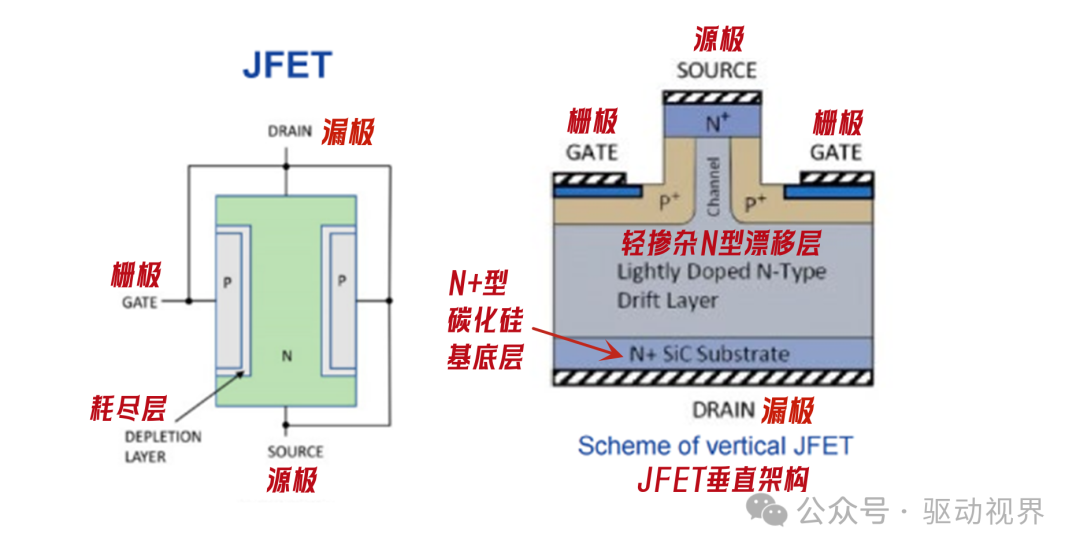

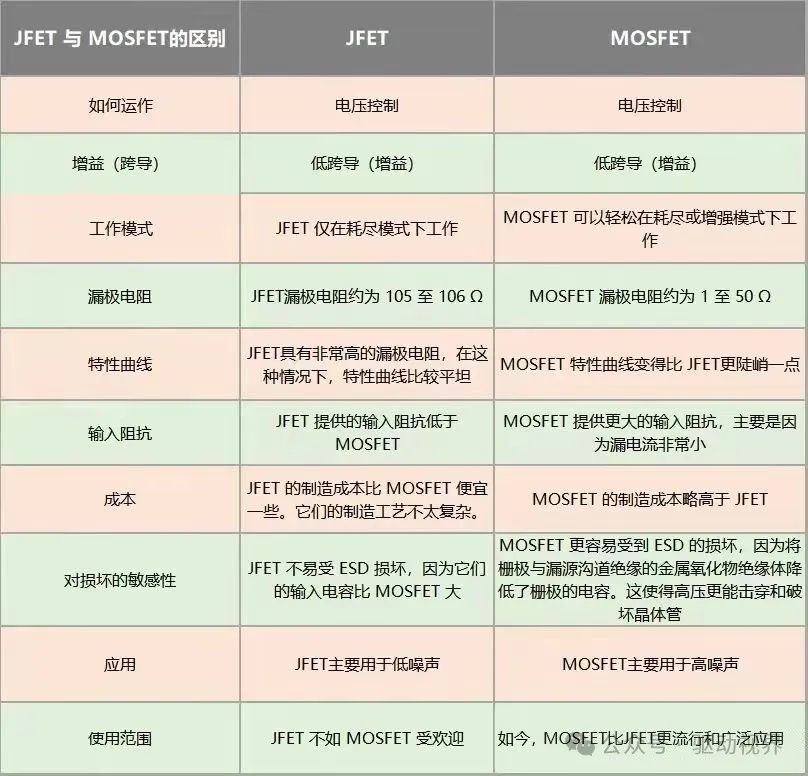

(4)MOSFET和JFET的区别

JFET是结型场效应晶体管的首字母缩写,由栅极、源极和漏极 3 个端子组成。在 JFET 中,电场施加在控制电流流动的栅极端子上。从漏极流向源极端子的电流与施加的栅极电压成正比。JFET基本上有两种类型,基本上是N沟道和P沟道。

MOSFET是金属氧化物半导体场效应晶体管的首字母缩写。在这里,器件的电导率也根据施加的电压而变化。MOSFET有两种类型:耗尽型MOSFET和增强型 MOSFET。

(5)衬底和外延

衬底定义:沿特定结晶方向切割、研磨、抛光,得到具有特定晶面和适当电学、光学和机械特性,用于生长外延层的洁净单晶圆薄片。

衬底分类:从电化学性质差异来看,碳化硅衬底材料可以分为导电型衬底和半绝缘型衬底。

外延工艺是指在SiC衬底的表面上生长一层质量更高的单晶材料。

8、中科院电工所

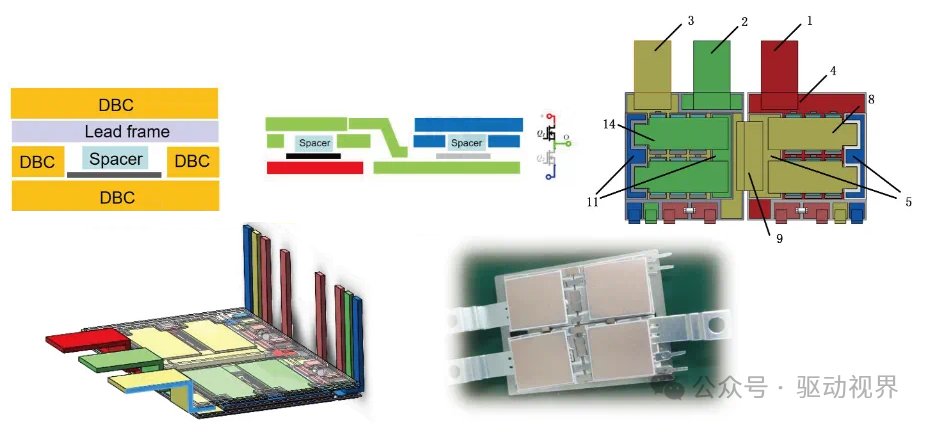

▲叠层DBC方案

中科院电工所叠层DBC方案(Stacked DBC Method):

(1)破除通流瓶颈,芯片并联数量提高80%(Break the limit of current path,parallelling more dies)。

(2)依靠互感降低自感,总体寄生阻抗降低50%(Reduce parastic parameters)。

▲叠层平面模块设计

中科院电工所叠层平面模块设计(Stacked Planar Module)

(1)导电层从2层增加到4层,芯片并联数量提高50%,寄生阻抗降低15%(Conduction layer increased)

(2)多层DBC直接支撑,可使用双面pinfin直焊,进一步降低热阻(DBC support top layer)

中科院电工所18芯片并联SiC模块样品通过800V/670A双脉冲测试@150℃(Double pulse test)

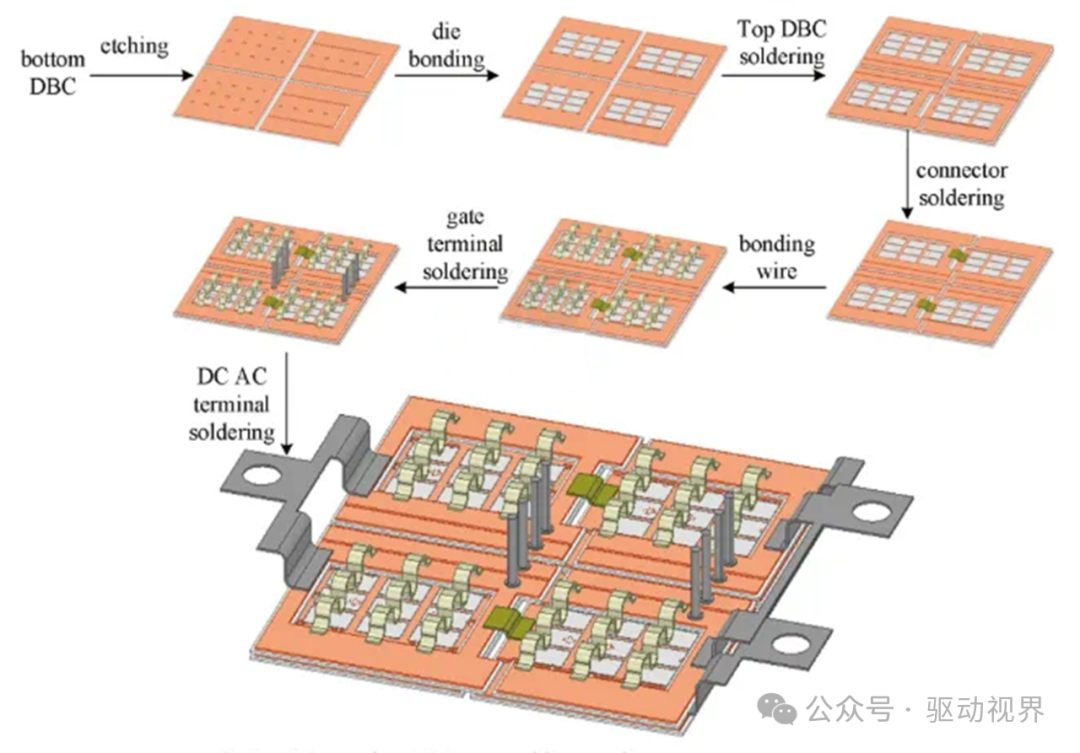

▲叠层模块制造流程

叠层模块制造流程(Stacked Module Fabrication):

(1)2~3次焊接,与普通工艺一致(2~3 soldering steps)

(2)功率端子可选择使用超声波焊接(Ultra-sonic bonding for terminal)

小结:

(1)平面封装适用于电动汽车应用中的sic器件

(2)堆叠DBC方法可以提高功率模块的功率密度

(3)格子法有助于热设计

9、罗姆(ROHM)

罗姆SiC产能扩展计划:

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论