前言

大多数设计者都熟悉基于Pierce(皮尔斯)栅拓扑结构的振荡器,但很少有人真正了解它是如何工 作的,更遑论如何正确的设计。我们经常看到,在振荡器工作不正常之前,多数人是不愿付出 太多精力来关注振荡器的设计的,而此时产品通常已经量产;许多系统或项目因为它们的晶振 无法正常工作而被推迟部署或运行。情况不应该是如此。在设计阶段,以及产品量产前的阶 段,振荡器应该得到适当的关注。

石英晶振的特性及模型

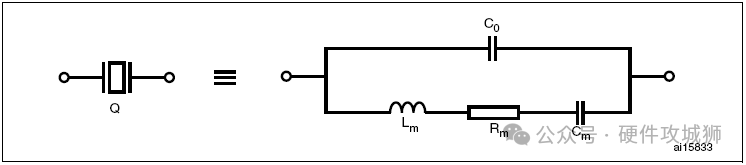

石英晶体是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。它可 用如下模型表示:

石英晶体模型

C0:等效电路中与串联臂并接的电容(译注:也叫并电容,静电电容,其值一般仅与晶振的尺寸 有关)。

Lm:(动态等效电感)代表晶振机械振动的惯性。

Cm:(动态等效电容)代表晶振的弹性。

Rm:(动态等效电阻)代表电路的损耗。

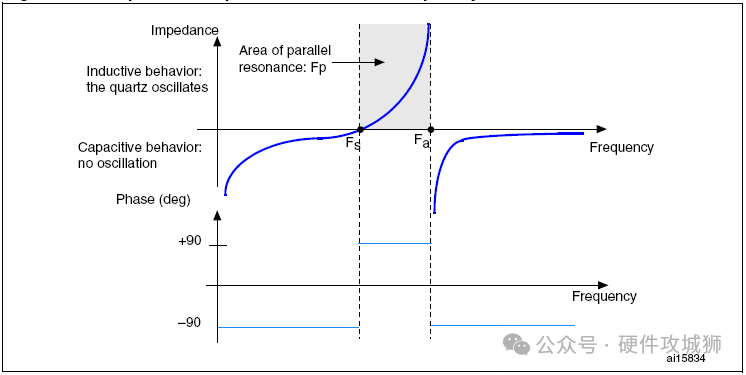

晶振的阻抗可表示为以下方程(假设Rm可以忽略不计):

石英晶振的频域电抗特性

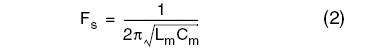

其中Fs的是当电抗Z=0时的串联谐频率(译注:它是Lm、 Cm和Rm支路的谐振频率),其表达式如 下:

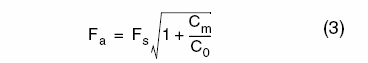

Fa是当电抗Z趋于无穷大时的并联谐振频率(译注:它是整个等效电路的谐振频率),使用等式 (1),其表达式如下:

在Fs到Fa的区域即通常所谓的:“并联谐振区” (图2中的阴影部分),在这一区域晶振工作在并 联谐振状态(译注:该区域就是晶振的正常工作区域, Fa- Fs就是晶振的带宽。

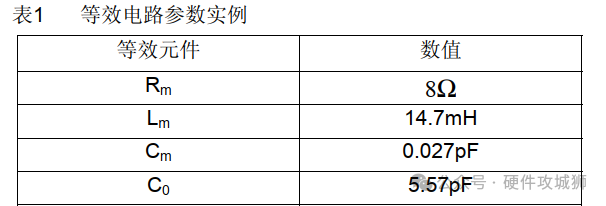

带宽越窄,晶振 品质因素越高,振荡频率越稳定)。在此区域晶振呈电感特性,从而带来了相当于180 °的相移。其频率FP(或者叫FL:负载频率)表达式如下:

从表达式(4),我们知道可以通过调节负载电容CL来微调振荡器的频率,这就是为什么晶振制造 商在其产品说明书中会指定外部负载电容CL值的原因。通过指定外部负载电容CL值,可以使晶 振晶体振荡时达到其标称频率。

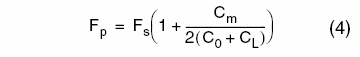

下表给出了一个例子来说明如何调整外部参数来达到晶振电路的8MHz标称频率:

使用表达式(2)、 (3)和(4),我们可以计算出该晶振的Fs、 Fa 及FP:Fs = 7988768Hz, Fa = 8008102Hz 如果该晶振的CL为10pF,则其振荡频率为:FP = 7995695Hz。要使其达到准确的标称振荡频率8MHz, CL应该为4.02pF。

振荡器原理

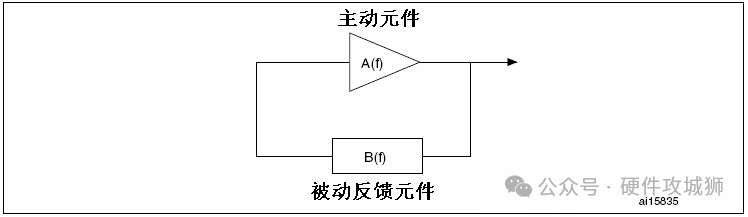

振荡器由一个放大器和反馈网络组成,反馈网络起到频率选择的作用。图3通过一个框图来说明 振荡器的基本原理。

振荡器的基本原理

其中:

A(f)是放大器部分,给这个闭环系统提供能量以保持其振荡。

B(f)是反馈通道,它决定了振荡器的频率。

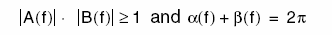

为了起振, Barkhausen条件必须得到满足。即闭环增益应大于1,并且总相移为360°。

为了让振荡器工作,要保证|A(f)|.|B(f)| >> 1。这意味着开环增益应远大于1,到达稳定振荡所需 的时间取决于这个开环增益。

然而,仅满足以上条件是不够解释为什么晶体振荡器可以开始振 荡。为了起振,还需要向其提供启动所需的电能。

一般来说,上电的能量瞬变以及噪声可以提 供所需的能量。应当注意到,这个启动能量应该足够多,从而能够保证通过触发使振荡器在所 需的频率工作。

实际上,在这种条件下的放大器是非常不稳定的,任何干扰进入这种正反馈闭环系统都会使其 不稳定并引发振荡启动。干扰可能源于上电,器件禁用/使能的操作以及晶振热噪声等...

同时必须注意到,只有在晶振工作频率范围内的噪声才能被放大,这部分相对于噪声的全部能量来 说只是一小部分,这也就是为什么晶体振荡器需要相当长的时间才能启动的原因。

Pierce振荡器

皮尔斯振荡器有低功耗、低成本及良好的稳定性等特点,因此常见于通常的应用中。

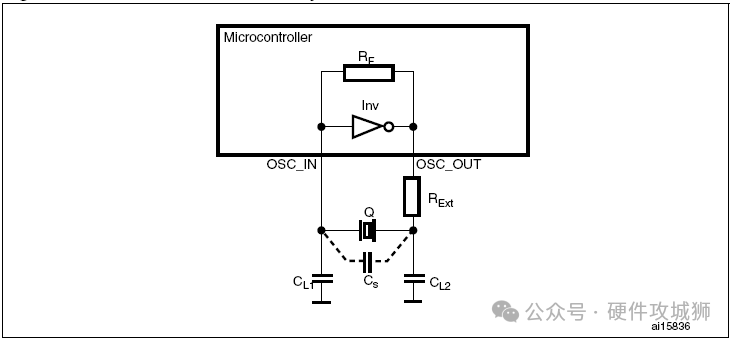

皮尔斯振荡器电路

Inv:内部反向器,作用等同于放大器。

Q:石英或陶瓷晶振。

RF:内部反馈电阻(译注:它的存在使反相器工作在线性区, 从而使其获得增益,作用等同于放 大器)。

RExt:外部限流电阻。

CL1和CL2:两个外部负载电容。

Cs:由于PCB布线及连接等寄生效应引起的等效杂散电容(OSC_IN和OSC_OUT管脚上)。

Pierce振荡器设计

反馈电阻RF

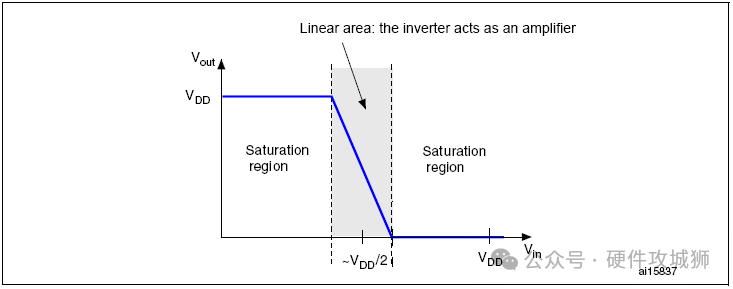

在大多数情况下,反馈电阻RF是内嵌在振荡器电路内的(至少在ST的MCU中是如此)。它的作用 是通过引入反馈使反向器的功能等同于放大器。

Vin和Vout之间增加的反馈电阻使放大器在Vout= Vin时产生偏置,迫使反向器工作在线性区域(图5中阴影区)。该放大器放大了晶振的正常工作区域内的在并联谐振区内的噪声(例如晶振的热噪声)(译注:工作在线性区的反向器等同于一个反向放大器),从而引发晶振起振。在某些情况下,如果在起振后去掉反馈电阻RF,振荡器仍可以继续正常运转。

反向器工作示意图

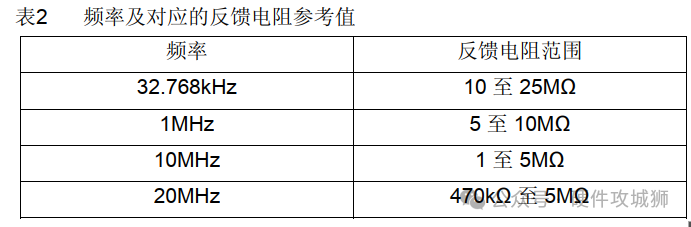

RF的典型值于下表中给出。

负载电容CL

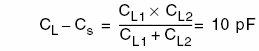

负载电容CL是指连接到晶振上的终端电容。CL值取决于外部电容器CL1和CL2,刷电路板上的杂 散电容(Cs)。CL值由由晶振制造商给出。保证振荡频率精度,主要取决于振荡电路的负载电容与 给定的电容值相同,保证振荡频率稳定度主要取决于负载电容保持不变。外部电容器CL1和CL2 可用来调整CL,使之达到晶振制造商的标定值。CL的表达式如下:

CL1和CL2计算实例:例如,如果CL =15pF,并假定Cs = 5pF,则有:

即:CL1 = CL2 = 20pF

振荡器的增益裕量

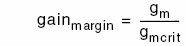

增益裕量是最重要的参数,它决定振荡器是否能够正常起振,其表达式如下:

其中:

gm是反向器的跨导,其单位是mA/V(对于高频的情况)或者是µA/V(对于低频的情况,例如 32kHz)。

gmcrit (gm critical)的值 取决于晶振本身的参数。假定CL1 = CL2 ,并假定晶振的CL将与制造商给定的值相同,则gmcrit表达式如下:

其中ESR是指晶振的等效串联电阻。根据Eric Vittoz的理论(译注:具体可参考Eric A. Vittoz et al., "High-Performance CrystalOscillator Circuits: Theory and Application", IEEE Journal of Solid-State Circuits, vol. 23, No. 3,pp. 774-782, Jun. 1988),放大器和两个外部电容的阻抗对晶振的RLC动态等效电路的电抗有补偿作用。

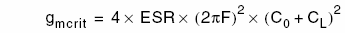

基于这一理论,反向器跨导(gm)必须满足:gm > gmcrit 。在这种情况下才满足起振的振荡条 件。为保证可靠的起振,增益裕量的最小值一般设为5。例如,如果设计一个微控制器的振荡器部分,其gm等于25mA/V。如果所选择的石英晶振(来自 FOX公司)的参数如下:

频率 = 8MHz, C0 = 7pF, CL = 10pF, ESR = 80 Ω 那么该晶体能否与微控制器配合可靠起振?让我们来计算gmcrit:

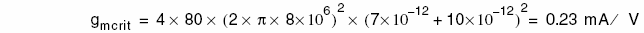

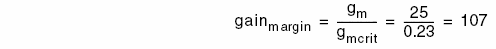

如果据此来计算增益裕量,可得:

此增益裕量远大于起振条件即Gainmargin>5,晶振将正常起振。如果不能满足增益裕量起振条件(即增益裕量Gainmargin小于5,晶振无法正常起振),应尝试选择 一种ESR较低或/和CL较低的晶振。

4.4 驱动级别DL外部电阻RExt计算

驱动级别DL计算

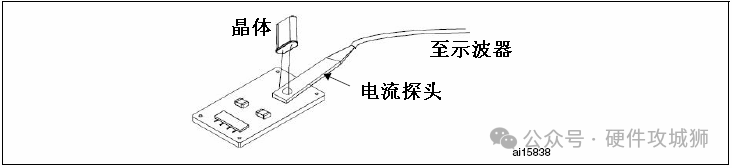

驱动级别描述了晶振的功耗。晶振的功耗必须限制在某一范围内,否则石英晶体可能会由于过 度的机械振动而导致不能正常工作。通常由晶振制造商给出驱动级别的最大值,单位是毫瓦。超过这个值时,晶振就会受到损害。驱动级别由下述表达式给出:

其中:

ESR是指晶振的等效串联电阻(其值由晶振制造商给出):

IQ是流过晶振电流的均方根有效值,使用示波器可观测到其波形为正弦波。电流值可使用 峰-峰值(IPP)。当使用电流探头时(如图6),示波器的量程比例可能需要设置为1mA/1mV。

使用电流探头检测晶振驱动电流

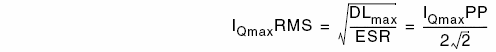

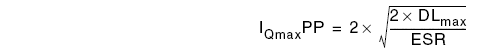

如先前所描述,当使用限流电位器调整电流值,可使流过晶振的电流不超过IQMAX均方根有效值 (假设流过晶振的电流波形为正弦波)。IQMAX均方根有效值表达式如下:

因此,流过晶振的电流IPP不应超过IQMAXPP(使用峰-峰值表示), IQMAXPP表达式如下:

这也就是为什么需要外部电阻RExt的原因(请参考4.4.3节)。当IQ超过IQmaxPP时, RExt是必需的, 并且RExt要加入到ESR中去参与计算IQmax。

外部电阻RExt计算

这个电阻的作用是限制晶振的驱动级别,并且它与CL2组成一个低通滤波器,以确保振荡器的起 振点在基频上,而不是在其他高次谐波频率点上(避免3次, 5次, 7次谐波频率)。如果晶振的功 耗超过晶振制造商的给定值,外部电阻RExt是必需的,用以避免晶振被过分驱动。如果晶振的功 耗小于晶振制造商的给定值,就不推荐使用RExt了,它的值可以是0Ω。

对RExt值的预估可以通过考虑由RExt和CL2的电压分压RExt/CL2实现(注意到RExt和CL2构成了一个分 压/滤波器,考虑通带宽度应不小于振荡器频率),则有RExt的值等于CL2的电抗:

输入:

振荡器频率F = 8MHz

CL2 = 15pF

得到:RExt = 1326Ω

优化RExt值的方法推荐如下:首先根据前面的介绍确定好CL1和CL2的值,其次使用电位器来代替 RExt, RExt值可预设为CL2的电抗值。然后调整电位器的值直到它满足晶振驱动级别的需要,此时 电位器的值即是CL2值。

注意:

在计算完RExt值后要重新计算Gain margin的值(请参考4.3节)以确保RExt值对起振条件没有影响。例如, RExt值的值需要加入到ESR中参与gmcrit的计算,同时要保证gm >>gmcrit

注意:

如果RExt值太小,晶振上可能会承担太多的功耗。如果RExt值太大,振荡器起振条件将得不到 满足从而无法正常工作。

启动时间

启动时间是指振荡器启动并达到稳定所需的时间。这个时间受外部CL1和CL2电容影响,同时它 随着晶振频率的增加而减少。不同种类的晶振对启动时间影响也很大,石英晶振的启动时间比 陶瓷晶振的启动时间长得多。起振失败通常和Gainmargin有关,过大或过小的CL1和CL2,以及过 大的ESR值均可引起Gainmargin不能满足起振条件。

频率为MHz级的晶振的启动时间是毫秒级的。

而32kHz的晶振的启动时间一般要1~5秒

挑选晶振及外部器件的简易指南

第一步:增益裕量(Gainmargin)计算

(请参考4.3节:振荡器的增益裕量)

选择一个晶振(参考MCU的数据手册确定晶振的频率)

计算晶振的增益裕量(Gainmargin)并检查其是否大于5:

如果Gainmargin < 5,说明这不是一个合适的晶振,应当再挑选一个低ESR值和/或低CL值的 晶振,重新第一步。如果Gainmargin > 5,进行第二步。

第二步:外部负载电容的计算

(请参考4.2节:负载电容CL)

计算CL1和CL2的值,并检查标定为该计算值的电容是否能在市场上获得。

如果能找到容值为计算值的电容,则晶振可以在期望的频率正常起振。然后转到第三步。

如果找不到容值为计算值的电容:

该应用对频率要求很高,你可使用一个可变电容并将其调整到计算值,然后转到第三步。

如果对频率的要求不是特别苛刻,选择市场上能获得的电容中容值距计算值最近的电容, 然后转到第三步。

第三步:驱动级别及外部电阻的计算

(请参考4.4节:驱动级别DL外部电阻RExt计算)

计算驱动级别DL并检查其是否大于DLcrystal:

如果 DL < DLcrystal,没必要使用外部电阻,祝贺你,你找到了合适的晶振。

如果 DL > DLcrystal,你应该计算 RExt 使其确保 DL< DLcrystal 并据此重新计算 Gainmargin。

如果 Gainmargin> 5,祝贺你,你找到了合适的晶振。

如果 Gainmargin< 5,你别无选择,再重新挑选另外一个晶振吧。然后重新回到第一步

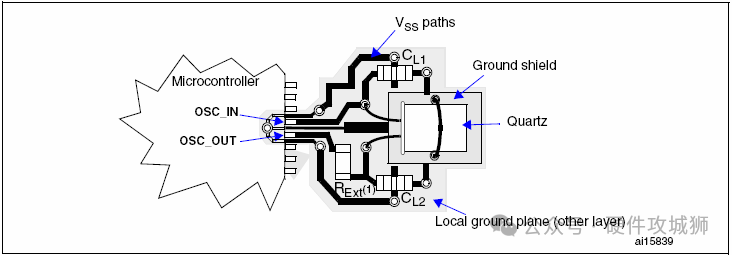

关于PCB的提示

外部杂散电容和电感要控制在一个尽可能小的范围内,从而避免晶振进入非正常工作模式或 引起起振不正常等问题。另外,振荡器电路旁边要避免有高频信号经过。

走线长度越短越好。

接地平面用于信号隔离和减少噪声。例如:在晶振的保护环(译注:(Guard ring),指器件或 走线外围成一圈用于屏蔽干扰的导线环,一般要求理论上没有电流从该导线环上经过)下直 接敷地有助于将晶振和来自其他PCB层的噪声隔离开来。要注意接地平面要紧临晶振但只限 于晶振下面,而不要将此接地平面敷满整个PCB板(见图7)。

像图7所示来布地线是一个好的作法。这种布线方法将振荡器的输入与输出隔离开来,同时 也将振荡器和临近的电路隔离开来。所有的VSS过孔不是直接连到地平面上(除晶振焊盘之 外),就是连接到终端在CL1和CL2下方的地线上。

在每一对VDD与VSS端口上连接去藕电容来平滑噪声。

推荐的晶振布线电路

注意:

仅当晶振上的功耗超过晶振制造商给定的值, REXT才是必需的。否则, REXT的值应当是0

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论