外部监测

DS314xx输入时钟监测逻辑不能监测1Hz输入时钟。此外,DS314xx DPLL不能因为缺少有效的1Hz输入时钟(即没有时钟沿)或频偏而失效。如果需要监测1Hz输入时钟的有效信号和/或频率,则必须在DS314xx器件外部增加监测功能。

对于来自系统或子系统(GPS接收机或IEEE 1588等从设备)的1Hz信号,系统可能已经对1Hz信号源进行了必要监测。这种情况下,系统软件可从信号源接收时钟的状态信息,并且利用相应的VALCR位控制1Hz时钟的有效工作或禁止。

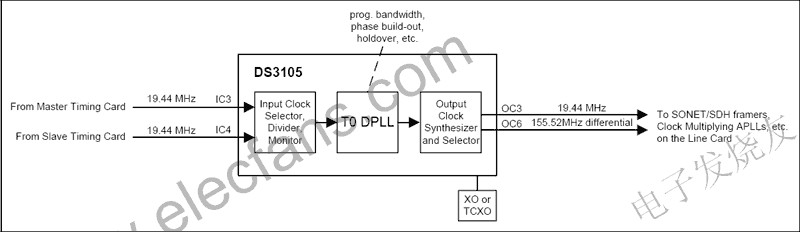

如果系统没有对1Hz信号源进行必要监测,则可在FPGA逻辑电路中构建监测电路。将来自DS314xx的高速时钟信号(例如50MHz或100MHz)连接至FPGA。FPGA内部逻辑电路可在每个1Hz时钟周期内对高速时钟信号进行计数。如果使用100MHz时钟信号时,以这种方式测量频率时,分辨率可以达到0.01ppm。如果发现测得的频率过高或过低,FPGA的监测逻辑电路可以指示频率超出技术指标。随后,系统软件即可利用DS314xx器件中的VALCR位禁止1Hz时钟操作。

工作在1Hz时钟时,如果将VALCR位清零,DPLL将自动锁定到下一优先级的有效输入时钟;如果没有其它时钟,则可切换到保持状态。其它输入可以是1Hz或更高频率的任意时钟。

1Hz输入时钟无效时,DS314xx DPLL的工作状况

DPLL锁定到一个停止翻转(例如电缆断开)的1Hz输入时钟时,DPLL不能快速识别时钟没有翻转。这是因为信号出现时,DPLL每秒只能接收到一个相位更新。DPLL在数秒内才能退出锁存状态,并且可能在Prelocked/Prelocked2、锁存、失锁状态之间切换状态,不会进入保持状态。

当DPLL退出锁存状态(如果使能,会在DS314xx INTREQ引脚产生中断请求),系统软件应该有所反应,判断1Hz信号故障,然后清除VALCR位。此时,允许DPLL切换到下一个有效输入,或在没有其它输入时钟的情况下进入保持状态。

如果系统软件没有禁止失效的1Hz时钟,DPLL在1Hz信号恢复时仍然尝试锁存到1Hz信号,DPLL锁存将非常缓慢。特别是,DPLL频率可能在最终锁定到1Hz输入时钟之前,一直移动在HRDLIM字段设定的正、负门限。该锁定过程可能花费数十或数百秒。如果系统软件检测到DPLL频率偏离标称值过多,可通过清零然后再置位输入时钟的VALCR位进行干预。从而允许DPLL使用其相位扩充程序在数秒内锁定。

进入、退出保持状态所需要的额外步骤

配置工作在1Hz时,DS314xx DPLL只有从DS314xx输入时钟模块接收到“新选定的参考时钟”信号时,才能退出保持状态。为确保从1Hz时钟产生该信号,系统软件必须能够执行以下操作:

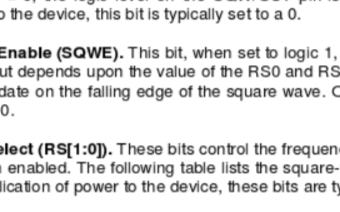

无效的1Hz输入时钟必须标记为无效。通过清除相应的VALCR位或将输入时钟的优先级设置为0实现。

有效的1Hz输入时钟必须标记为有效。通过置位相应的VALCR位或将输入时钟的优先级设置为非零值实现。

如果将DPLL强制为保持状态,系统软件必须利用DPLLCR2.STATE字段执行额外的几个步骤。当STATE字段返回到自动状态转换时,如果输入时钟保持有效,则不产生“新选定的参考时钟”信号,DPLL不会退出保持状态。为了避免这种现象,系统软件应将DPLL STATE字段切回到自动状态,然后执行以下步骤:

如果DPLLCR1.REVERT=0,则将其置1。

清除然后再置位最高优先级、有效输入时钟对应的VALCR位。

将REVERT位恢复到其原始值。

以上步骤使输入时钟模块产生“新选定的参考时钟”信号,它允许DPLL退出保持状态并锁定至最高优先级的有效输入时钟。

增大ppm调整以满足Stratum 3标准所需的软件支持

对于频率≤ 0.06Hz,每秒钟只有一次相位更新时,锁定在1Hz输入时钟的DS314xx DPLL的频率变化非常缓慢。例如,在锁存状态下,改变9.2ppm的频率可能需要10分钟以上的时间。为了满足stratum 3标准,系统需要在100s内锁定至新的输入时钟。如果输入时钟的频率与DPLL的当前频率相差高达9.2ppm,如果DPLL采用常规的锁存机制,显然不能满足100s的要求。

幸运的是,系统软件可利用以下步骤大大加速这一过程:

从DS31400外部的时钟监测器获得新的1Hz输入时钟的频率。

(如果信号发生频率跃变,这也可能是当前1Hz时钟信号的新频率。)

计算新频率与FREQ寄存器字段读取的当前DPLL频率之差。

将DPLL当前频率写入手动保持频率字段HOFREQ。

将DPLLCR2.HOMODE和MINHO设置为01,将DPLL配置为手动保持。

通过设置DPLLCR2.STATE=010,强制DPLL进入保持状态。

调整HOFREQ字段的手动保持频率,将其更改到新的频率。为达到GR-1244 stratum 3标准要求,变化率应小于2.9ppm/s。

通过设置DPLLCR2.STATE=000,允许DPLL进行自动状态转换。

清除然后置位相应的VALCR位,允许DPLL退出保持状态。

将DPLLCR2.HOMODE和MINHO设置为10。

DPLL将快速锁定至1Hz输入时钟。

输出、输入之间的相位差不为零

DS314xx DPLL开始跟踪1Hz输入时钟时,它将输入时钟的当前相位设置为其相位目标,该目标相位通常为0°。DPLL锁定时,DPLL的PHASE寄存器字段中的零值或接近于零的数值表示DPLL已经锁定到选定的目标相位。该DPLL的输出时钟信号与DPLL的目标相位对齐,因此与1Hz输入时钟之间存在一个固定的相位关系,通常是一个不为零的数值。

对于要求输出必须与1Hz输入同相的应用,或者输出与输入相位必须存在受系统控制的相位关系时,Maxim提供的DS31408和DS31415两款器件能够满足这一需求,这些器件包含另外一个称为时间引擎的模块。该时间引擎使得器件能够锁定至1Hz输入时钟,并产生相位精确的输出时钟。

总结

Maxim的DS314xx时钟同步IC可以进行现场升级,使其锁定至1Hz (1PPS)输入时钟信号。利用外部1Hz信号监测电路,并借助本文介绍的系统软件提供少量支持,即可将DS314xx器件构建成符合标准的时钟同步系统,能够工作在1Hz和更高频率的任意输入时钟。

电子发烧友App

电子发烧友App

评论