关键词: TI , DS90UB913 , 象素 , 照相机 , PD-Link

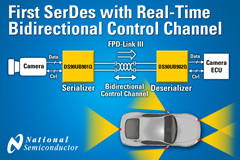

TI公司的DS90UB913Q/DS90UB914Q芯片组是10-100MHz 10/12位FPD-Link III SER/DES,提供高速FPD-Link III接口和高速正向通路以及用于差分对上数据发送的双向控制通路,主要用在图像和汽车ECU的视频处理器间的连接,主要用在汽车视频系统,防碰撞系统的前端照相机,后视镜照相机和停车系统辅助管理.本文介绍了DS90UB913Q/DS90UB914Q主要特性,框图和应用框图以及DS90UB913Q/914Q评估板主要特性,电路图和PCB布局图.

2012-8-22 12:20:23 上传

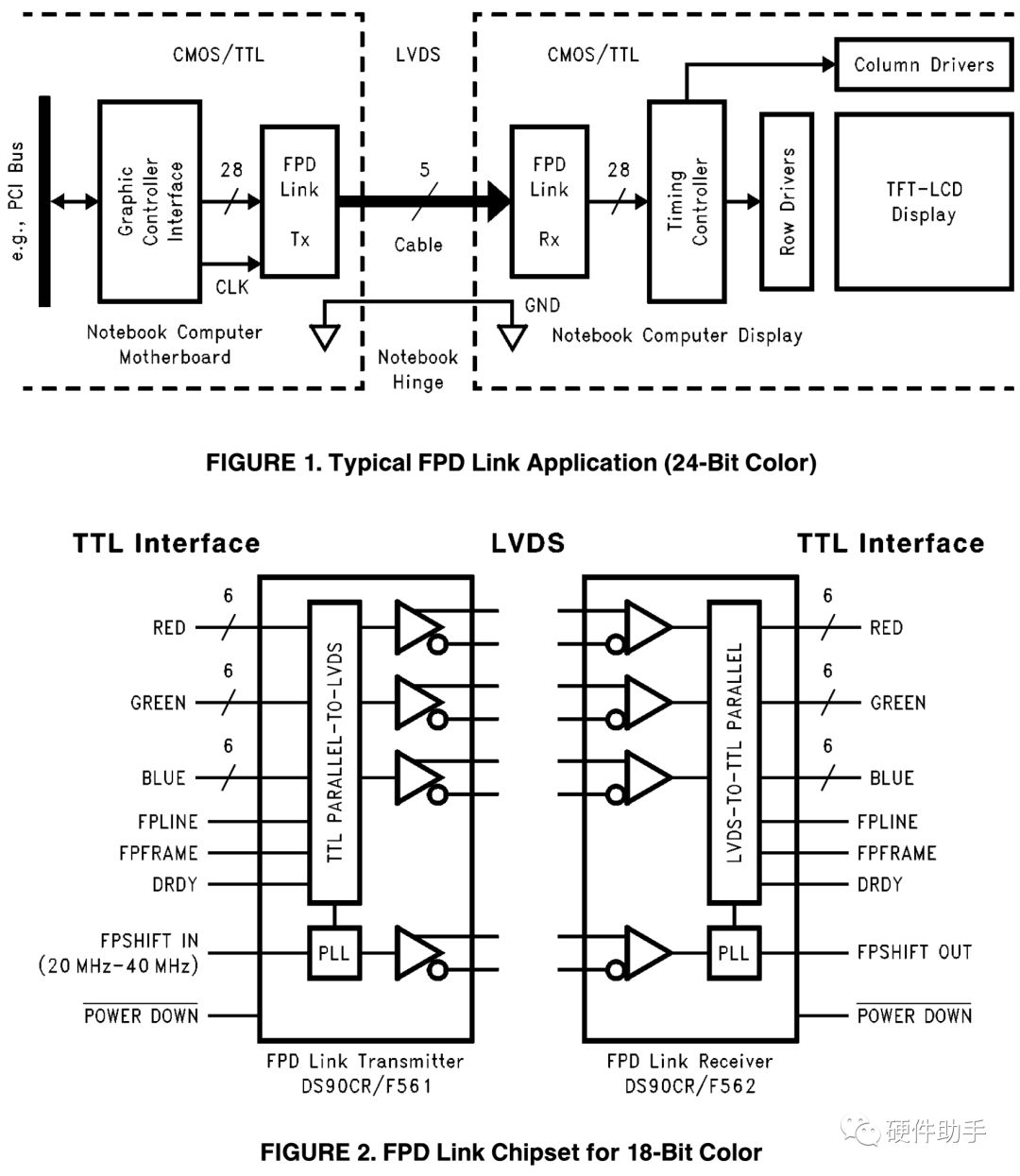

The DS90UB913Q/DS90UB914Q chipset offers a FPD-Link III interface with a high-speed forward channel and a bidirectional control channel for data transmission over a single differential pair. The DS90UB913Q/914Q chipsets incorporate differential signaling on both the high-speed forward channel and bidirectional control channel data paths. The Serializer/ Deserializer pair is targeted for connections between imagers and video processors in an ECU (Electronic Control Unit). This chipset is ideally suited for driving video data requiring up to 12 bit pixel depth plus two synchronization signals along with bidirectional control channel bus.

There is a multiplexer at the Deserializer to choose between two input imagers. The Deserializer can have only one active input imager. The primary video transport converts 10/12 bit data over a single high-speed serial stream, along with a separate low latency bidirectional control channel transport that accepts control information from an I2C port and is independent of video blanking period.

Using TI’s embedded clock technology allows transparent fullduplex communication over a single differential pair, carrying asymmetrical bidirectional control channel information in both directions. This single serial stream simplifies transferring a wide data bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. This significantly saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins. In addition, the Deserializer inputs provide adaptive equalization to compensate for loss from the media over longer distances. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects. The Serializer is offered in a 32-pin LLP package and the Deserializer is offered in a 48-pin LLP package.

DS90UB913Q/DS90UB914Q主要特性:

● 10 MHz to 100 MHz input pixel clock support

● Single differential pair interconnect

● Programmable data payload:

— 10 bit payload up to 100Mhz

— 12 bit payload up to 75MHz

● Continuous Low Latency Bidirectional control interface channel with I2C support@400kHz

● 2:1 Multiplexer to choose between two input imagers

● Embedded clock with DC Balanced coding to support ACcoupled interconnects

● Capable of driving up to 25 meters shielded twisted-pair

● 4 dedicated General Purpose Input (GPI)/ Output (GPO)

● LOCK output reporting pin and AT-SPEED BIST diagnosis feature to validate link integrity

● Integrated termination resistors

● 1.8V, 2.8V or 3.3V compatible parallel inputs on Serializer

● Single power supply at 1.8V

● ISO 10605 and IEC 61000-4-2 ESD Compliant

● Temperature range −40℃ to +105℃

● Small serializer footprint (5mm x 5mm)

● No reference clock required on Deserializer

● Adaptive Receive Equalization

● EMI/EMC Mitigation

— DES Programmable Spread Spectrum (SSCG) outputs.

— DES Receiver staggered outputs

DS90UB913Q/DS90UB914Q应用:

● Automotive Vision Systems

● Front camera for collision mitigation

● Rear view camera for backup protection

● Parking Assistance

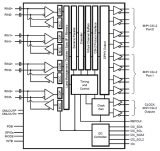

图1.DS90UB913Q/DS90UB914Q框图

2012-8-22 12:22:18 上传

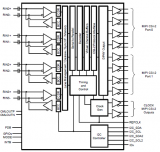

下载附件 (25.14 KB)图2.DS90UB913Q/DS90UB914Q应用框图

2012-8-22 12:20:21 上传

下载附件 (19.29 KB)图3.DS90UB913Q/DS90UB914Q典型应用框图

The DS90UB913Q/914Q evaluation boards consist of two sections. The first part of the board provides the point-to-point interface for transmitting parallel video data. The second part of the board allows bi-directional control communication of an I2C bus control of using a MCU/FPGA to programming a remote peripheral device via the Serializer.

2012-8-22 12:20:20 上传

下载附件 (47.46 KB)图4.DS90UB913Q/914Q评估板外形图

The DS90UB913Q/914Q chipset supports a variety of automotive mega-pixel camera systems over a two (2) wire serial stream. The single differential pair (FPD-Link III) is well-suited for direct connections between an imager and Host Controller/Electronic Control Unit (ECU)/FPGA. The bidirectional control channel of the DS90UB913Q/914Q provides seamless communication between the ECU/FPGA and the imager module. Transmission of a full-duplex high-speed video data (10/12 bits of parallel data, two SYNC bits and PCLK), with transparent bi-directional control channel (I2C) over the same serial video link. Additionally, there are four unidirectional general purpose (GPI and GPO) signal lines from the Deserializer to the Serializer. This interface allows transparent (no dependency of video blanking interval) ,full-duplex communication over a single high-speed differential pair. The Serializer and Deserializer communicate data at PCLK clocks speeds ranging from 10 to 100 MHz and I2C bus rates up to 400 kbps at up to 25 meters cable length over -40 to +105 Deg C.

DS90UB913Q/914Q评估板主要特性:

On-board Rosenberger connectors for use with Leoni-Dacar cables (not included)

Optional single ended coaxial connectors to work with coaxial cables

Supports a variety of automotive mega-pixel camera systems over a two (2) wire serial stream

Requires only a single 5V supply

Power transfer over coax or power transfer over differential pair capability

Enables high-speed video data transmission, with integrated low latency bi-directional control, over a single twisted pair cable

Delivers 10/12 bits of parallel data, two SYNC bits and PCLK, with a bidirectional I2C bus control channel

Four additional unidirectional general purpose (GPI and GPO) signal lines from the Deserializer to the Serializer

Full-duplex communication and asymmetrical bi-directional control over a single high-speed differential pair, without video blanking intervals

Transmit data at PCLK clocks speeds, ranging from 10 to 100 MHz

I2C bus rates up to 400 kbps

2012-8-22 12:20:18 上传

下载附件 (50.67 KB)图5.DS90UB913Q EVK电路图(1)

2012-8-22 12:20:17 上传

下载附件 (37.01 KB)图6.DS90UB913Q EVK电路图(2)

2012-8-22 12:20:16 上传

下载附件 (18.83 KB)图7.DS90UB913Q EVK电路图(3)

2012-8-22 12:20:14 上传

下载附件 (51.81 KB)图8.DS90UB914Q EVK电路图(1)

2012-8-22 12:20:13 上传

下载附件 (36.47 KB)图9.DS90UB914Q EVK电路图(2)

2012-8-22 12:20:12 上传

下载附件 (13.57 KB)图10.DS90UB914Q EVK电路图(3)

2012-8-22 12:20:12 上传

下载附件 (33.84 KB)图11.DS90UB913Q评估板PCB布局图

2012-8-22 12:20:11 上传

下载附件 (32.82 KB)图12.DS90UB914Q评估板PCB布局图

2012-8-22 12:20:10 上传

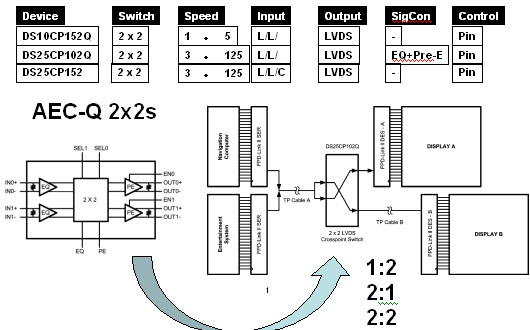

下载附件 (23.1 KB)图13.汽车视频控制框图

详情请见:

snls420.pdf (177.06 KB, 下载次数: 3)

2012-8-22 12:15:44 上传

下载次数: 3下载积分: 积分 -1 和

snlu110.pdf (1.23 MB, 下载次数: 3)

2012-8-22 12:16:18 上传

下载次数: 3下载积分: 积分 -1

电子发烧友App

电子发烧友App

评论