关键词: LED的秘密 , LED芯片 , LED照明

2011-11-11 10:18:01 上传

效率下降是阻碍GaN基LED在高电流密度这一重要的新兴应用领域大施拳脚的主要原因。但RPI的研究人员表示,通过采用极性匹配的外延结构可以克服这一缺点。

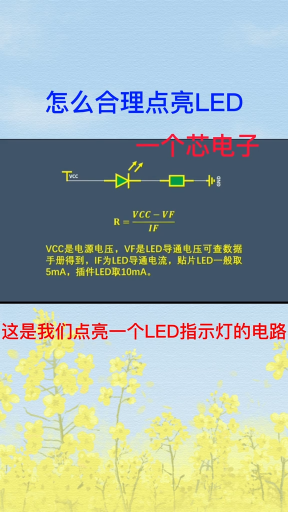

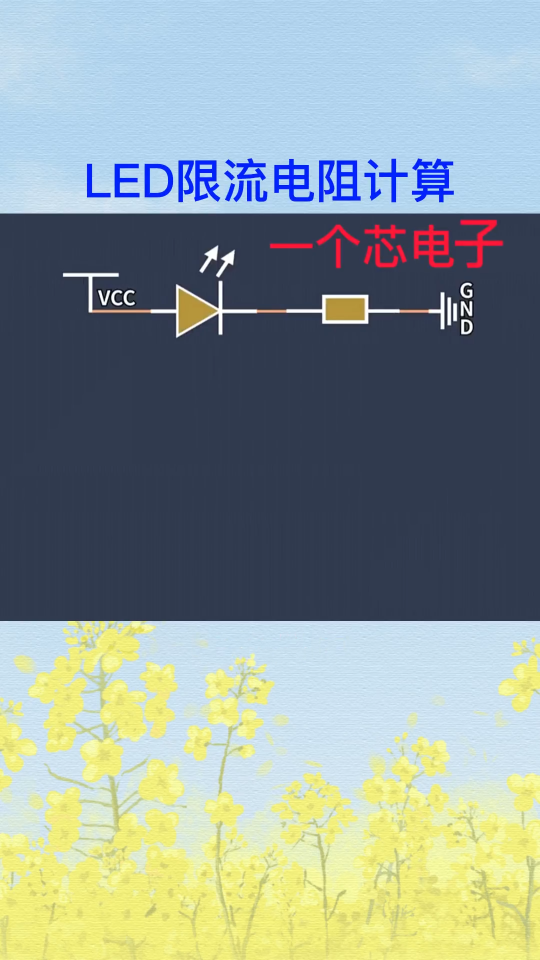

LED制造商们目前非常关注一些新的市场,例如汽车前灯、大屏幕显示和普通照明。从某种程度上说,降低价格能帮助LED打入这些领域,但仅仅如此还不够。LED的芯片还需要在大驱动电流下也能实现高功效。这也意味着需要解决功率下降这一广受关注的问题。

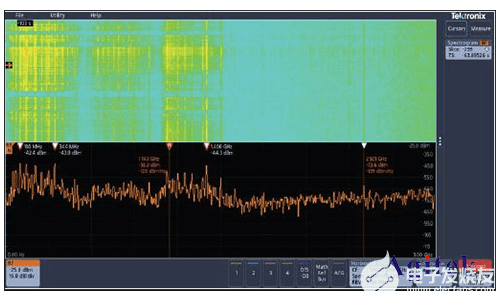

通过比较电和光激发LED的输出情况,可以帮助RPI的相关研究人员研究GaN基器件功率下降的原因。

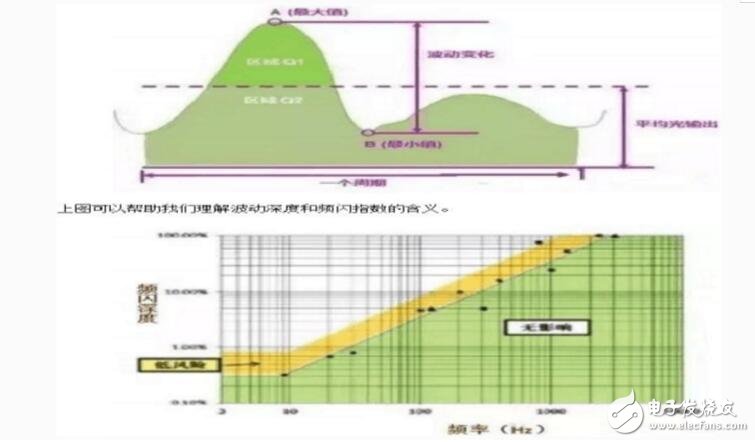

功率下降具体来说是指蓝光、绿光和白光LED在电流增大时效率反而下降的现象。GaN基LED通常仅在电流密度10A cm-2时效率达到峰值,电流密度为100A cm-2时效率降为峰值的一半。这引起了大家的关注,当今的高亮度芯片都需要在比10A cm-2大得多的电流密度下高效地工作。

攻克这一难题显然非常重要,而且它已经吸引了全球工业界和学术界大批研究人员的兴趣,其中也包括我们位于纽约州特洛伊市伦斯勒理工学院的研究团队,我们在过去的几年里一直在探索效率下降这一问题的根源。我们相信我们能找到症结所在,并通过完全不同的LED设计克服这一问题。

我们与位于新墨西哥州Sandia国家实验室的Mary Crawford研究小组合作,一起研究功率下降问题的成因。我们关注位错密度对于LED效率的影响,发现位错会降低低电流密度时的效率,但并不影响高电流密度下的效率降低问题。

在低电流密度时,载流子通常在一个陷阱辅助的过程(即SRH复合)中损失掉了,而且会随着位错密度的增加变得更加严重。通过增强自发辐射,加大电流密度起初会提高效率,但随着电流的进一步增加,另一个与之抗衡的载流子损耗机制会引发效率的下降。

漏电的LED

我们还与韩国三星电机公司合作。这一努力终于让我们找到了效率下降的原因——由于量子势阱层、量子势垒层和电子阻挡层之间的极性失配导致的有源层电子泄漏。

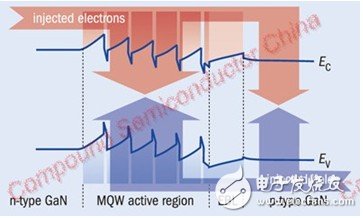

我们的解释能说明为什么高电流密度时效率下降的主要原因——当提高驱动电压时,会导致更多注入的电子逃出有源层,抵达LED的p型区,从而与p电极处的空穴进行非辐射复合(图2)。

通过比较LED器件在电偏压和光激发时的光输出(详见“探索LED的结构”),该理论已通过实验得到了验证。我们在使用数值模拟工具将载流子泄漏与极性失配联系起来之前,就曾表明在量子阱外也有复合机制发生。

界面问题

我们的精力主要集中于在GaN传统的晶面—c面上生长LED。这些器件通常有很强的内建电场,在界面处会产生相当强的表面电荷(详见“感受内部的力”)。

2011-11-11 10:18:01 上传

下载附件 (23.94 KB)图1a. 对面积为1mm×1mm的传统GaInN LED芯片进行测量,揭示了在驱动电流大于10mA时输出效率会降低。如果能完全避免引起效率下降的机制,LED芯片的效率则会随着电流的增加而不断增加。

2011-11-11 10:18:01 上传

下载附件 (24.42 KB)图1b.非辐射机制在低驱动电流时占主导地位,随着电流增加让位于辐射复合,之后效率反而下降。

界面表面电荷会从两个方面阻碍LED的性能。它们会提高电子注入多量子阱区的势垒,同时降低来自量子阱和电流阻挡层上电子泄漏的势垒。

我们的模拟支持了这一假设,表面电荷通过电子的泄漏降低LED的性能,这也说明减少表面电荷可以缓解载流子的损失。计算同时表明缺乏对p型结构的重掺杂会加剧效率的下降,尤其是在电子阻挡层。

众所周知,与双极结型晶体管的基极相比,发射极的重掺杂能阻止少数载流子注入发射极。而在LED中,GaN和AlGaN层p型掺杂浓度低,阻碍了空穴(p型区中空穴为多数载流子)注入有源区——这反过来加剧了电子的泄漏。

我们对电子泄漏造成LED效率下降的解释还并未得到广泛接受;事实上,还有研究者提出了几种不同的机制。其中以Philips Lumileds研究人员提出的俄歇复合理论(Shen et al. 2007)为主流。

在c面GaInN/GaN双异质结上进行了若干光致发光的试验,观察到高光激发密度时效率亦出现了下降。使用速率模型分析使得他们将俄歇复合当作是多量子阱LED效率降低的原因。

为此他们引入了有效复合厚度的概念,在设计双异质结时选定的物理厚度更小,因为量子阱中电子和空穴较小的重叠。

将该复合厚度代入速率方程,得出量子阱在有电场时的自发辐射速率比无电场时的更高。但这与GaN量子阱中电场减弱自发辐射的事实相反。因此,我们感觉Lumileds高估了多量子阱LED中俄歇复合在大电流密度时的重要性。

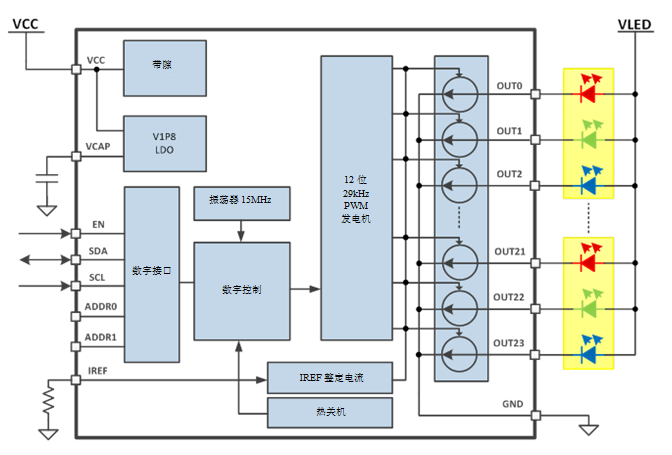

布丁好不好吃,当然尝过了才知道。最后将我们的模拟结果付诸实施,生长带有AlGaInN势垒层的LED。用AlGaInN层替代传统的GaN势垒层和AlGaN电子阻挡层,使得我们能自由的调节带隙宽度和极性,并最终减少极性失配和有源区界面间的表层电荷。

2011-11-11 10:18:01 上传

下载附件 (20.31 KB)图2. RPI的研究人员认为,电子逃逸是造成LED效率下降的主要原因。这些逃出的载流子与p型GaN区或p电极处的空穴进行非辐射复合。

2011-11-11 10:18:01 上传

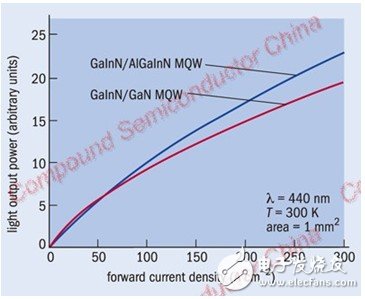

下载附件 (25.52 KB)图3.具有量子势阱和势垒极性匹配的LED通过减少电子泄漏,在大驱动电流下仍能表现出优异的性能。

对于量子势垒,我们将生长一种与GaN同样带隙宽度的四元化合物,并且能与典型量子阱的极性相匹配。这是一项十分艰巨的任务,因为生长高铟组分和高铝组分的AlGaInN层是非常困难的。但通过减少极性的不平衡,能显着地提高器件的性能。这也同样适用于电子阻挡层。

我们的模拟显示,对极性匹配做一下调整就能获得几乎所有的好处,而使用势垒和势阱只能减少一半的极性失配。关键点是将势垒的带隙宽度略微减小,就能在有源区内形成附加的载流子约束。

提高能效

这些调整已经带来一些令人鼓舞的结果。由于减缓了效率的下降,在大电流时光输出提高了20%(图3)。由于降低了载流子注入量子阱区的势垒的高度,正向电压也相应的降低了。减少量子阱区表面电荷的另一个好处是将总能效提高25%。调整还带来其它好处,由于量子阱内的电场强度更低,减少了波长随电流变化而产生的漂移。

很明显,人们对效率下降问题的兴趣在不断增加,这本身对LED的发展有益。我们加深了对它的了解,现有的设计看上去能解决这个问题。具有上述特性的商业器件就应该积极筹备开拓新的市场,直指终极目标——替代通用照明灯泡。

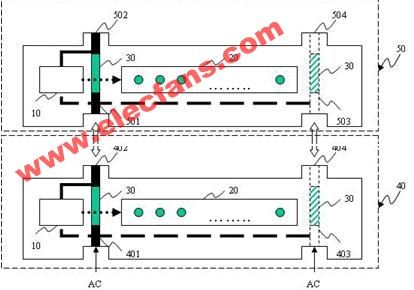

探索LED的结构

通过比较光激发和电偏压时光的输出,伦斯勒理工学院的研究人员研究GaInN蓝光LED中效率下降的问题。上述比较是以电子和空穴的产生速率是相同的为前提,结果显示效率下降是由于载流子输运引起的。

在稳态光激发的条件下,不应该存在例外的逃逸电子或空穴。如果发生了,就会损失一种载流子——这意味着在量子阱内形成了电场分布,产生额外的载流子泄漏。电子或空穴自发的逃逸也不太可能,因为空穴被严格的约束在势阱内。

无论如何,部分载流子确实从势阱中逃逸出来了。使用405nm激光轰击这一结构,会产生非零的开路电压。这是因为器件的正向偏置电压需要反向电流来补偿。净电流仍为零,这是任何一个没有接入外部电路的器件都必须遵守的。

正向偏置改变了LED的载流子输运。空穴和电子对量子阱的注入和逃逸速率会发生变化,往往会导致电子从势阱中泄漏出去。这需要LED在光激发和电偏置两种情况下不同的光输出效率来证明。RPI进行的测量证实了这一点。在电泵浦的器件中观察到了效率的下降,但在光激发的情况下却没有。这意味着某种形式的载流子复合机制在量子阱外的区域发生,造成了效率的下降。

感受内部的力

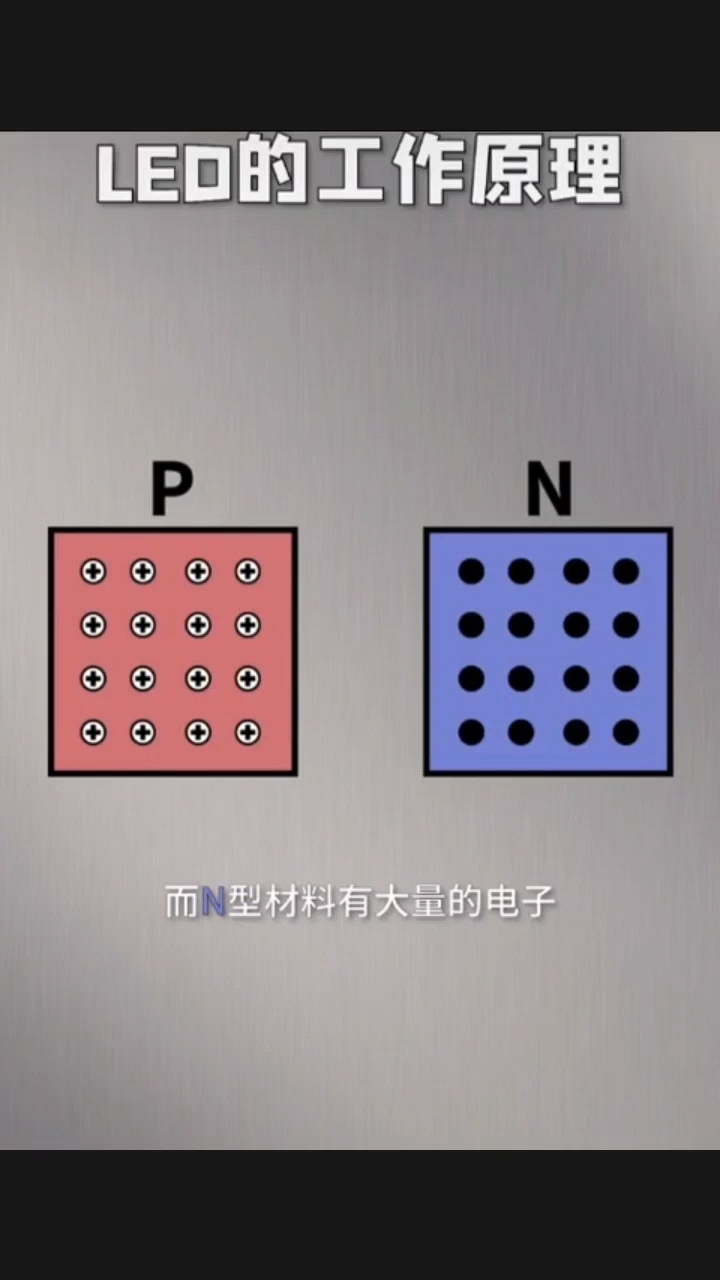

GaN具有纤锌矿晶体结构,并在c晶向上存在极化电场。当LED生长在这个晶向上时,由于各相邻层间在自发极化和应变诱发的压电极化两方面存在差异,会在界面间产生较大的表面电荷。通过减少有源区的电子束缚以及增加有源区的电子泄漏,这些电荷会降低LED的效率。

在传统的蓝光LED中,GaN势垒围绕在GaInN量子阱的两侧,势阱的n型区一侧表面电荷为负。这些电荷会排斥电子,并阻碍电子注入。势阱的p型区一侧表面电荷为正,会吸收电子,增加电子逃逸的可能性(图a)。

2011-11-11 10:18:01 上传

下载附件 (19.5 KB)

2011-11-11 10:18:01 上传

下载附件 (20.78 KB)AlGaN电子阻挡层具有相反的效果。它们会在n型区一侧产生正电荷,使得电子更容易跨越势垒(图b)。通过提高Al组分来增加电子阻挡层的带隙宽度并不是一个很好的解决办法,原因是表面电荷也会同时增加。

发光效果取决于接触面

一个美国团队将光致发光强度(PLI)作为电容-电压(CV)光谱分析法的辅助技术,用以决定III-V族材料与电介质之间的界面质量。

这些界面严重影响着III-V族MOSFET的性能,作为一种可能拓展摩尔定律的器件,了解它的性能极其重要。CV光谱分析法因其复杂性一般广泛用于测量界面态密度。

Matthias Passlack曾是前任飞思卡尔在德研究人员,现在正与英国格拉斯哥大学展开合作。他表示,“很不幸,CV或许被普遍误解为非硅半导体的相关技术。相反,PLI数字通译更加直截了当一些”,这是因为激光激发是测量过程中唯一的可变量。

利用PLI测量法得到了大量有关界面态密度的实验数据。很显然,这种分析界面质量的方法并不新鲜。早在上个世纪90年代日本北海道大学的Hasegawa小组就用该项技术做过实验;而Passlack也于1994-1995年间在贝尔实验室建立了一些初步的PLI,并于1996-1997年间在摩托罗拉构建了当前的器件结构。

Passlack最近发表的论文对一门更为复杂的学科略有陈述,里面对基于GaAs的22种材料展开了研究,包括GdGaO、In2O3和Ga2O3电介质;其中Ga2O3是唯一适合用作器件级界面的电介质。Passlack想用PLI来分析InGaAs MOSFET,并为格拉斯哥大学的Iain Thayne小组提供帮助,为他们建立一个能实现此项测量的实验装置。

来源:电子工程网

电子发烧友App

电子发烧友App

评论