当前在汽车、轨道交通的安全系统开发中,很多使用了双核锁步(dual core lockstep)安全芯片,本篇来谈谈双核锁步安全芯片的技术特点。

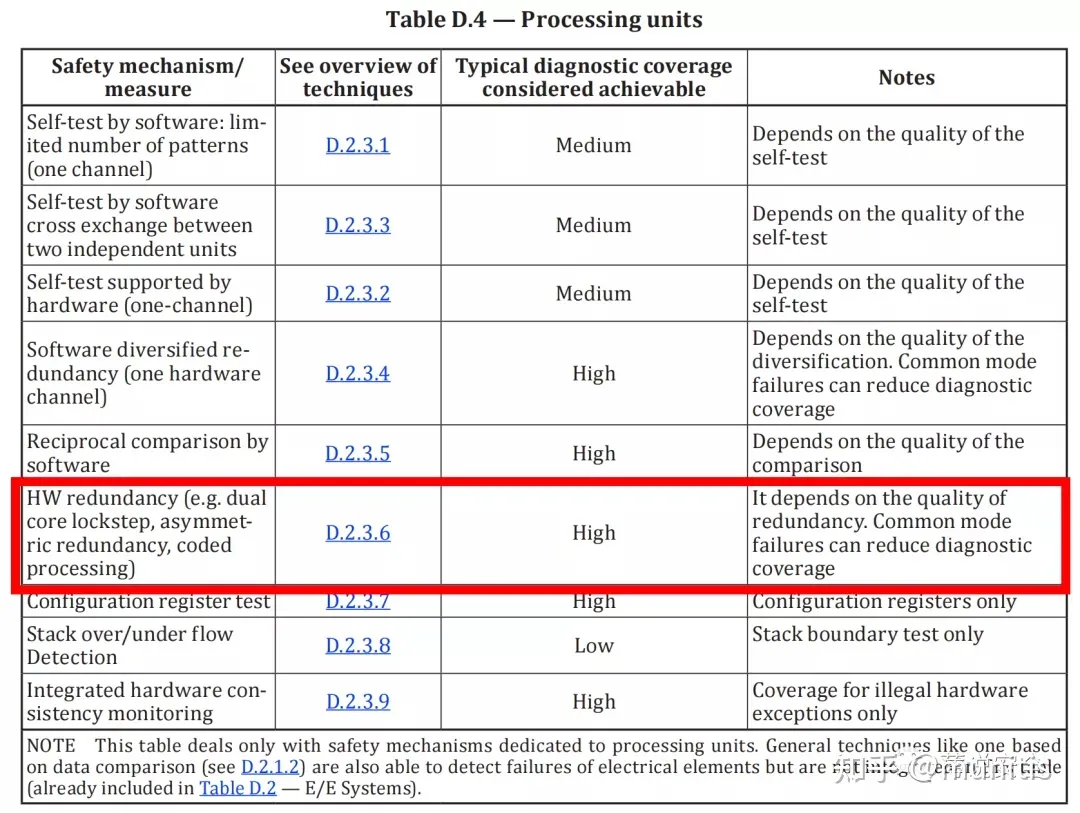

ISO26262对双核锁步芯片的规定条款

在汽车功能安全标准ISO26262-5 2018 产品开发:硬件层面附录D对处理单元的诊断覆盖率推荐的安全技术措施中,作为可实现高诊断覆盖率的几种技术措施之一,硬件冗余技术中,双核锁步、非对称冗余、编码计算是三种典型的技术措施。

技术特性

处理器CPU作为控制器的核心,内部包括寄存器、内存、译码器、ALU、高速缓存、总线、电源、时钟、堆栈、复位电路,所有组成部分需要以正确的时序要求运行,但CPU也会出现故障,如EMC、辐射、时钟漂移、低电压都可能导致CPU出现错误导致控制行为不可控。

双核锁步CPU是一种CPU冗余技术,在一个芯片中包含两个相同的处理器,一个作为master,一个作为slave,它们执行相同的代码并严格同步,master可以访问系统内存并输出指令,而slave不断执行在总线上的指令(即由主处理器获取的指令)。slave产生的输出,包括地址位和数据位,发送到比较逻辑模块,由master和slave总线接口的比较器电路组成,检查它们之间的数据、地址和控制线的一致性。检测到任何总线的值不一致时,就会发现其中一个CPU 上存在故障,但不会确定是哪个CPU故障。

这种CPU架构使得CPU自检独立于应用软件,不需要执行专门的指令集自检,实际运行的软件指令在每个时钟都进行比较,只需要测试软件用到的CPU资源,但这种架构不会对内存和总线进行检测,需要增加单独的检测方法以避免两个CPU的共模故障。

在Delphi Secured Microcontroller Architecture这篇关于锁步MCU的论文中,这种架构的优势有四方面:

由于减少了硬件元器件数量和连接,相比于使用两个独立的MCU,提高了硬件的可靠性;

电路板布局的小型化和复杂度降低,使得板级EMI性能提升和辐射发射降低;

故障诊断能力的提升,故障从源头并且在第一次出现时就被检测到,不会漏掉潜伏故障;

提高了软件的可靠性,不需要双CPU的通信和数据同步,减少数据比较和决策逻辑,降低了软件验证的复杂度。

典型的双核锁步芯片

各大芯片厂商都在积极开发双核锁步架构的芯片,以期望在功能安全芯片领域占有更多的市场,典型的芯片系列有:

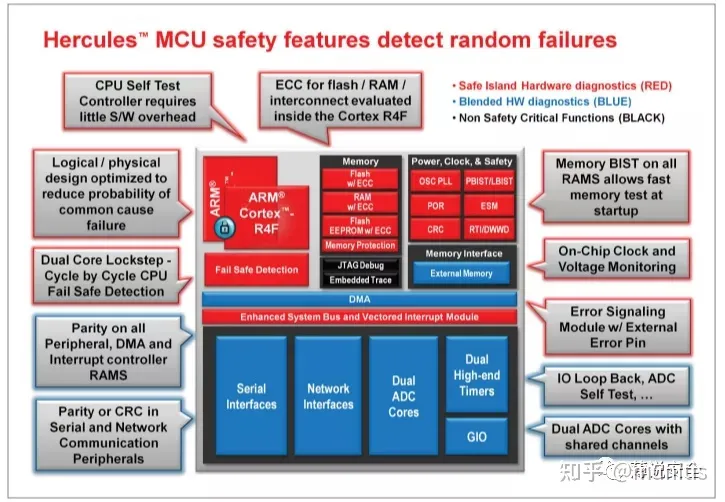

TI Hercules系列

Hercules是TI公司以ARM Cortex核心构建的安全关键CPU,包括三个系列:RM4,TMS570和TMS470M,内部由锁步双核CPU组成,最高可满足ISO26262 ASIL-D和IEC61508 SIL3功能安全标准的要求,并符合AEC-Q100车规级要求,双核锁步CPU架构、硬件BIST、MPU、ECC、片上时钟和电压监控可以满足汽车、铁路和航天航空关键功能安全应用。

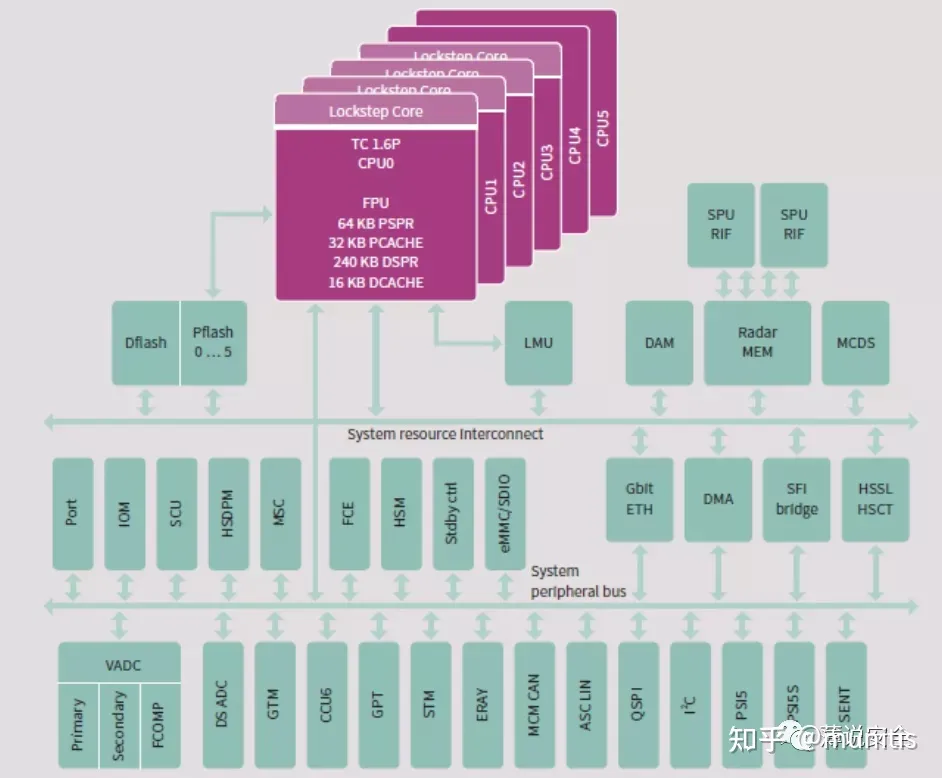

英飞凌AURIX系列

AURIX多核微控制器具有高实时性和嵌入式安全和安保特性。可用于控制内燃机、电动汽车和混动汽车的ECU单元、底盘域、刹车系统,EPS,安全气囊和ADAS系统,还可应用于铁路、工业自动化等领域。最新一代的AURIX TC3xx系列搭载了多达6个TriCore嵌入式内核,每个内核的时钟频率最高可达300MHz。配备千兆以太网、信号处理单元等最新通信接口。

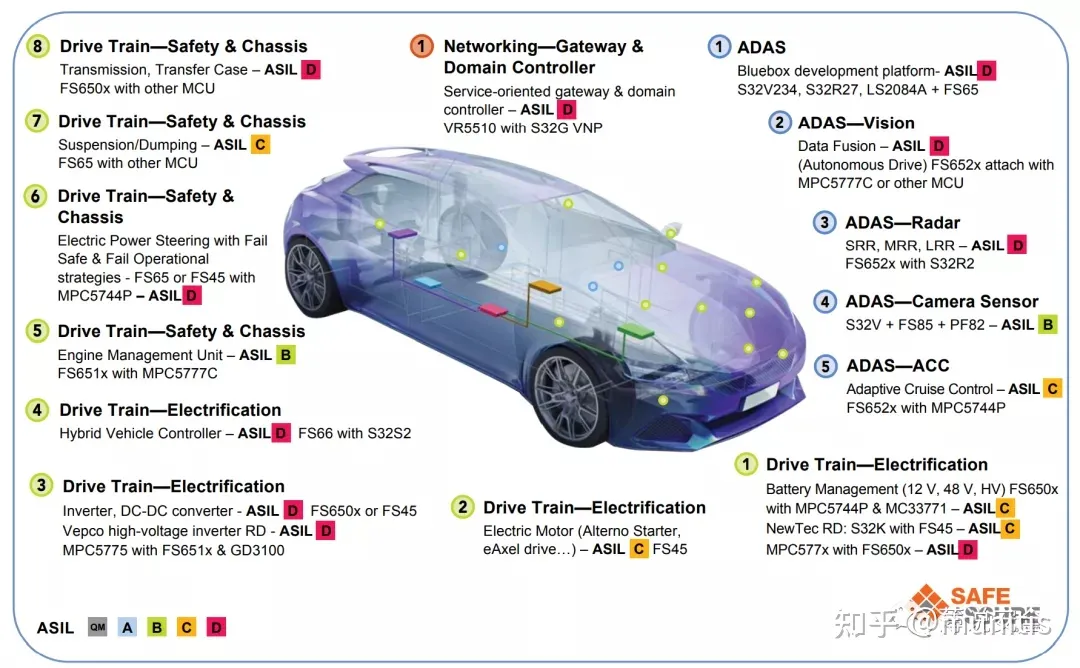

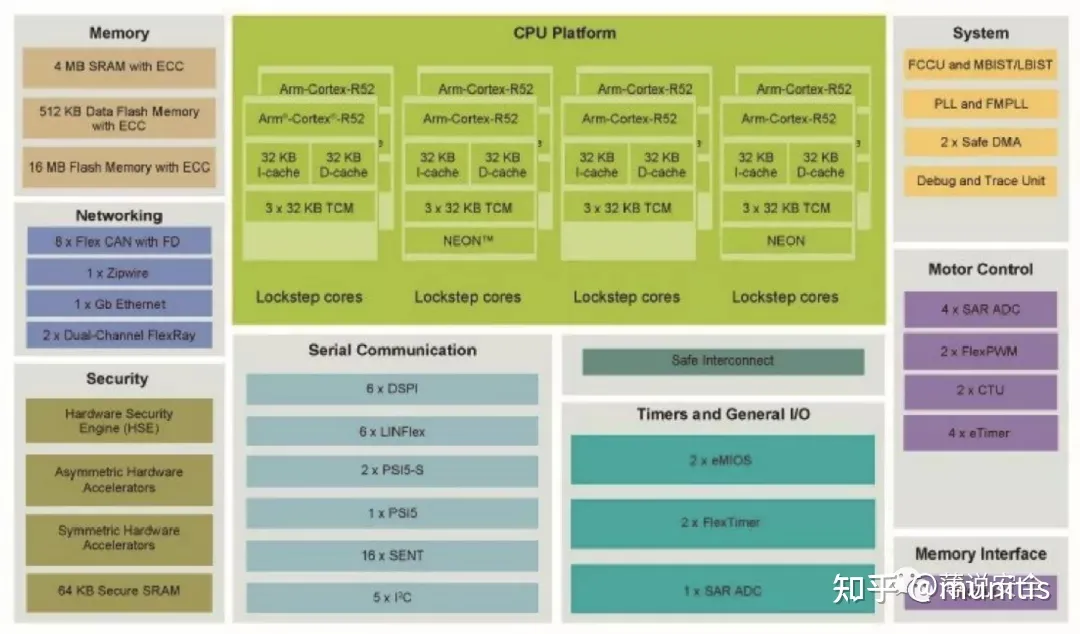

NXP S32、MPC57xx系列

NXP的S32系列基于ARM Cortex架构,包括:

S32K MCU用于一般的汽车和工业应用,达到ASIL B/D 的high safety和security;

S32G 车用网络处理器,用于处理与面向服务的网关、域控制器和安全协处理器相关的高性能应用;

S32S 车辆安全动力学MCU,用于管理为未来的自动驾驶和电动汽车安全加速、制动和转向;

S32R45 雷达处理器,用于远距离雷达成像的高性能、安全和可靠的处理。

MPC57xx系列基于Power Architecture®,包括MPC5777C,MPC577xK,MPC5777M,MPC5744P等,应用于汽车动力学、ADAS、高级自动驾驶应用。

发展趋势

从车用芯片的发展趋势来看,呈现以下几个趋势:

锁步芯片能支持的计算能力越来越强,目前最高的主频已由原来200-300MHz上升到1GHz;

由双核锁步向多核锁步发展,芯片内部可以实现多核,每2个核实现锁步运算;

支持千兆以太网,CAN、FlexRay,满足车内高速互联需求;

在功能安全达到ASIL-B/D要求下,同时支持Security特性,硬件加密,可编程的硬件安全引擎支持公钥和私钥加密,防范 IP 失窃和恶意黑客入侵;

支持OTA空中在线升级特性。

NXP S32K MCU架构

这类芯片在应用中比起常规的CPU芯片,需要注意并不是使用了具有锁步特性的芯片就达到了对应的安全等级要求,芯片会配套一系列完整的芯片安全使用要求需要遵循,一般会写在芯片的safety manual中,包括:

操作和使用环境的约束限制;

防范系统性失效;

系统级安全功能与芯片安全功能的匹配性,安全状态,安全时序要求,芯片不会实现特定的安全功能;

芯片安全诊断措施的正确配置和实施;

CPU芯片与外部芯片的匹配性,一般会搭配电源IC、看门狗IC、驱动IC共同实现安全要求;

common cause(共因)失效的防范。

这些要求都需要应用者逐项检查后将要求加入到系统性的安全设计中。

双核锁步芯片作为芯片级功能安全技术的代表,当前的应用已非常广泛,功能安全已不再局限于使用既有硬件元器件实现,已扩展到半导体领域,用于实现集成度更高、性能更优的安全产品,在ISO26262-11 2018中对半导体技术在汽车领域的应用进行了说明,IEC61508、EN50129也有相应条款说明了半导体技术在各自范围内的功能安全要求。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论