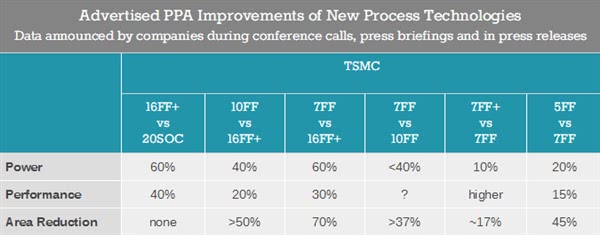

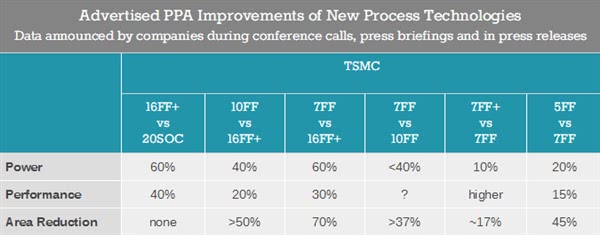

的性能和功耗优化。 采用5纳米的新工艺,与公司的7纳米工艺相比,相同的Cortex-A72内核可实现1.8倍的逻辑密度和15%的速度提升。 5nm工艺采用EUV光刻(极紫外曝光)制造,与公司以前的节点相比,通过简化制造工艺和在同一发展阶段实现出色的技术成熟度,可

2019-04-10 09:18:16 1114

1114 已经完成,现在可以为客户提供样品。通过在其基于极紫外(EUV)的工艺产品中添加另一个尖端节点,三星再次证明了其在先进晶圆代工市场的领导地位。 与7nm相比,三星的5nm FinFET工艺技术将逻辑区域效率提高了25%,功耗降低了20%,性能提高了10%,从而使其能够拥有更多创

2019-04-18 15:48:47 6010

6010 共享一些设计规则。新的N5工艺将提供7nm变体以上的完整节点增加,并在10层以上的层中广泛使用EUV技术,从而减少了7nm以上的生产总步骤。新的5nm工艺还采用了台积电的下一代FinFET技术。 芯片命名 公开资料显示,台积电5nm EUV工艺可提供整体逻辑密度增加约1.84倍,功率

2019-12-13 11:18:57 4940

4940 TSMC在FinFET工艺量产上落后于Intel、三星,不过他们在10nm及之后的工艺上很自信,2020年就会量产5nm工艺,还会用上EUV光刻工艺。

2016-07-18 10:47:09 989

989 · 新思科技Custom Design Platform为三星7LPP工艺技术提供经认证的工具、PDK、仿真模型、运行集(runsets)以及定制参考流程。

· 新思科技Custom

2018-07-18 11:46:35 7228

7228 在7nm及以下节点上,台积电的进展是最快的,今年量产7nm不说,最快明年4月份就要试产5nm EUV工艺了,不过这个节点的投资花费也是惊人的,台积电投资250亿美元建厂,5nm芯片设计费用也要比7nm工艺提升50%。

2018-10-08 09:52:33 3674

3674 10月10日晚间消息,著名半导体制造公司台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破,一是首次使用7nm EUV工艺完成了客户芯片的流片工作,二是5nm工艺将在六个月后开始试产!

2018-10-11 11:45:23 3704

3704 其5nm工艺。不过,最近有消息传出,三星遇到麻烦了,其5nm工艺的良率竟然低于50%。 韩国媒体报道,三星电子华城园区V1厂,最近面临晶圆代工良率改善难题,5nm等部分工艺良率低于50%。 三星华城园区共有V1、S3及S4等晶圆厂,其中V1为EUV专用厂,于201

2021-07-05 18:35:59 3553

3553 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是

2023-05-19 16:25:12 784

784

翁寿松(无锡市罗特电子有限公司,江苏无锡214001)1 32 nm/22 nm工艺进展2006年1月英特尔推出全球首款45 nm全功能153 Mb SRAM芯片。英特尔将投资90亿美元在以下4座

2019-07-01 07:22:23

基于10nm++开发7nm工艺、基于7nm设计开发5nm工艺,基于5nm工艺来开发3nm工艺,毫无疑问,每一个“+”或者“++”所拥有的技术更新都将有可能进入下一代节点的设计之中。 在7nm节点之后

2020-07-07 11:38:14

研究机构IMEC已经发表了一篇论文,该研究表明,在5nm节点上,STT-MRAM与SRAM相比可以为缓存提供节能效果。这种优势比非易失性和较小的空间占用更重要。

2019-10-18 06:01:42

是通过提升技术成本来平衡工序成本和周期成本。例如,按照格罗方德的测算,启用EUV技术,在7nm和5nm节点,都仅需要1个光罩即可生产。这样理论上来说,就可以起到简化工艺流程,减少生产周期的作用。对此,芯谋

2017-11-14 16:24:44

想问一下,TSMC350nm的工艺库是不是不太适合做LC-VCO啊,库里就一个电容能选的,也没有电感可以选。(因为课程提供的工艺库就只有这个350nm的,想做LC-VCO感觉又不太适合,好像只能做ring-VCO了)请问350nm有RF工艺嘛,或者您有什么其他的工艺推荐?

2021-06-24 08:06:46

EMC设计、工艺技术基本要点和问题处理流程推荐给大家参考。。

2015-08-25 12:05:04

感到非常鼓舞人心。我们已与用户设计团队密切合作,设计能够在高级工艺节点上应对日益升级的技术挑战的平台。通过使用7nm Fusion Design Platform,设计团队能够显著提高生产力,增加

2020-10-22 09:40:08

Sic mesfet工艺技术研究与器件研究针对SiC 衬底缺陷密度相对较高的问题,研究了消除或减弱其影响的工艺技术并进行了器件研制。通过优化刻蚀条件获得了粗糙度为2?07 nm的刻蚀表面;牺牲氧化

2009-10-06 09:48:48

从7nm到5nm,半导体制程芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。所谓的XXnm指的是集成电路的MOSFET晶体管栅极

2021-07-29 07:19:33

)光刻技术,而GlobalFoundries当年也曾经研究过7nm EUV工艺,只不过现在已经放弃了。 而使用极紫外光(EUV)作为光源的光刻机就是EUV光刻机,当然这绝对不是单纯只换个光源这么简单

2020-07-07 14:22:55

Research、东京电子和中微半导体,而通过台积电5nm工艺认证的则更少。在这个领域,中国大陆的中微半导体取得了可喜的进步,其5nm蚀刻机已经打入台积电供应链。中微半导体主要生产蚀刻机、MOCVD等设备

2020-03-09 10:13:54

业界对哪种半导体工艺最适合某一给定应用存在着广泛的争论。虽然某种特殊工艺技术能更好地服务一些应用,但其它工艺技术也有很大的应用空间。像CMOS、BiCMOS、砷化镓(GaAs)、磷化铟(InP

2019-07-05 08:13:58

业界对哪种半导体工艺最适合某一给定应用存在着广泛的争论。虽然某种特殊工艺技术能更好地服务一些应用,但其它工艺技术也有很大的应用空间。像CMOS、BiCMOS、砷化镓(GaAs)、磷化铟(InP

2019-08-20 08:01:20

7nm以下的工艺也将导入EUV技术。据***媒体报道,台积电5nm制程将于今年第二季度量产。据台积电介绍, 5nm是台积公司第二代使用极紫外光(EUV)技术的制程,其已展现优异的光学能力与符合预期的良好

2020-02-27 10:42:16

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

如何提高多层板层压品质在工艺技术

2021-04-25 09:08:11

求TSMC90nm的工艺库,请问可以分享一下吗?

2021-06-22 06:21:52

求一份tsmc 7nm standard cell library求一份28nm或者40nm 的数字库

2021-06-25 06:39:25

新思科技与中芯国际合作推出用于中芯65纳米低漏电工艺技术的、获得USB标志认证的DesignWareUSB 2.0 nanoPHY

通过芯片验证的DesignWare PHY IP

2010-05-20 17:39:09 589

589 随着芯片微缩,开发先进工艺技术的成本也越来越高。TSMC对外发言人孙又文表示,台积电会继续先进工艺技术节点的投入和开发,今年年底台积电将推出20nm工艺

2012-08-30 14:34:30 1782

1782 Mentor Graphics公司日前宣布Calibre LFD(光刻友好设计)光刻检查工具已获得TSMC的20nm IC制造工艺认证。 Calibre LFD可对热点进行识别,还可对设计工艺空间是否充足进行检查。光学临近校正法

2012-09-29 10:30:46 1761

1761 电子发烧友网核心提示 :Mentor Graphics公司日前宣布Calibre LFD(光刻友好设计)光刻检查工具已获得TSMC的20nm IC制造工艺认证。 Calibre LFD可对热点进行识别,还可对设计工艺空间是否充足进

2012-10-08 16:00:14 915

915 FinFET制程的设计规则手册(DRM)第0.5版的认证,同时从即刻起可以提供一套TSMC 16-nm可互通制程设计套件(iPDK)。凭借其对iPDK标准强大的支持,Synopsys的Laker定制解决方案为用户提供了从180-nm到16-nm的多种TSMC工艺技术的全面对接。

2013-09-23 14:45:30 1050

1050 ® Analog FastSPICE™ 电路验证平台已完成了电路级和器件级认证,Olympus-SoC™ 数字设计平台正在进行提升,以帮助设计工程师利用 TSMC 10nm FinFET 技术更有效地验证和优化其设计。10nm V1.0 工艺的认证预计在 2015 年第 4 季度完成。

2015-09-21 15:37:10 1300

1300 Technology (12FFC) 和最新版本 7nm FinFET Plus 工艺的认证。Nitro-SoCTM 布局和布线系统也通过了认证,可以支持 TSMC 的 12FFC 工艺技术。

2017-10-11 11:13:42 2372

2372 本周在火奴鲁鲁举行的VLSI(超大规模集成电路)研讨会上,三星首次分享了基于EUV技术的7nm工艺细节。

2018-06-22 15:16:00 970

970 EUV被认为是推动半导体产业制造更小芯片的重要里程碑,但是根据目前的EUV微影技术发展进程来看,10奈米(nm)和7nm制程节点已经准备就绪,就是5nm仍存在很大的挑战。

2018-01-24 10:52:39 2279

2279

TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证。Mentor 同时宣布,已更新了 Calibre nmPlatform 工具,可支持TSMC的晶圆堆叠封装 (WoW)技术

2018-05-17 15:19:00 3391

3391 Synopsys设计平台用于高性能、高密度芯片设计 重点: Synopsys设计平台获得TSMC工艺认证,支持高性能7-nm FinFET Plus工艺技术,已成功用于客户的多个设计项目。 针对

2018-05-17 06:59:00 4461

4461 Intel 10nm工艺还在苦苦挣扎,台积电和三星已经开始量产7nm,下一步自然就是5nm,台积电近日也首次公开了5nm的部分关键指标,看起来不是很乐观。 明年,台积电的第二代7nm工艺会在部分

2018-05-15 14:35:13 3793

3793

5nm、4nm、3nm工艺,直逼 这两年,三星电子、台积电在半导体工艺上一路狂奔,虽然有技术之争但把曾经的领导者Intel远远甩在身后已经是不争的事实。

2018-06-08 07:12:00 3709

3709 Synopsys Synopsys近日宣布, Synopsys 设计平台获得TSMC最新版且最先进的5nm工艺技术认证,可用于客户先期设计。通过与TSMC的早期密切协作,IC CompilerII

2018-06-01 09:35:00 3784

3784 10月10日晚间消息,著名半导体制造公司台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破,一是首次使用7nm EUV工艺完成了客户芯片的流片工作,二是5nm工艺将在六个月后开始试产!

2018-10-11 08:44:33 4918

4918 基于7nm工艺技术的控制器和PHY IP具有丰富的产品组合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解决方案支持TSMC 7nm工艺技术所需的先进汽车设计规则,满足可靠性和15年汽车运行要求。

2018-10-18 14:57:21 6541

6541 IC Compiler II和Design Compiler Graphical提供了统一流程,实现最低功耗、最佳性能和最优面积。

StarRC、PrimeTime和PrimeTime PX支持全流程设计实现并提供时序和功耗分析的signoff支持。

2018-10-23 14:29:14 5460

5460 新思科技(Synopsys)推出支持TSMC 7nm FinFET工艺技术的汽车级DesignWare Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2

2018-11-13 16:20:23 1518

1518 国内的中微电子已经研发成功5nm等离子刻蚀机,并通过了台积电的认证,将用于全球首条5nm工艺。

2018-12-20 08:55:26 24111

24111 工智能(AI)市场。 台积电表示,相较7nm制程,5nm的微缩功能在Arm的Cortex-A72核心上能够提供1.8倍的逻辑密度,性能可提升15%。此外,5nm制程将会完全采用极紫外光(EUV)微影技术,因此可带来EUV技术提供的制程简化效益。 台积电指出,5nm制程能提供芯片设计业者

2019-04-04 11:16:02 2899

2899 台积电指出,5nm制程将会完全采用极紫外光(EUV)微影技术,因此可带来EUV技术提供的制程简化效益。5nm制程能够提供全新等级的效能及功耗解决方案,支援下一代的高端移动及高效能运算需求的产品。目前,其他晶元厂的7nm工艺尚举步维艰,在5nm时代台积电再次领先。

2019-04-04 16:05:57 1660

1660 包括7nm批量生产和6nm产品的流片, 三星电子在基于EUV技术的先进制程工艺开发上取得重大进展 4月16日,三星电子宣布,其5nm FinFET( 鳍式场效应晶体管)工艺技术已经开发完成,该技术

2019-04-18 20:48:54 272

272 通过使用三星7nm EUV工艺代替台积电的7nm工艺,Nvidia可能能够获得更多供应。

2019-06-10 09:06:12 6225

6225 新思科技近日宣布,三星(Samsung Electronics)认证了新思科技Fusion Design Platform™,用于三星采用EUV光刻技术的5纳米Low-Power Early(早期

2019-06-12 13:48:35 3553

3553 近日,全球知名的EDA工具厂商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先进工艺的良率学习平台设计取得了重大突破,这将为三星后续5nm、4nm、3nm工艺的量产和良品率的提升奠定坚实基础。

2019-07-09 17:13:48 4225

4225 全球知名的EDA工具厂商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先进工艺的良率学习平台设计取得了重大突破

2019-07-11 14:49:47 3326

3326 采用极紫外(EUV)光刻技术的Cadence 数字全流程解决方案已通过Samsung Foundry 5nm早期低功耗版(5LPE)工艺认证。

2019-07-11 16:36:47 3437

3437 近两年先进半导体制造主要是也终于迎来了EUV光刻机,这也使7nm之后的工艺发展得以持续进行下去。台积电和三星都对自家工艺发展进行了规划,现在两家已经逐步开始进行7nm EUV工艺的量产,随后还有5nm工艺及3nm工艺。

2019-07-24 11:45:42 2702

2702 7nm+ EUV节点之后,台积电5nm工艺将更深入地应用EUV极紫外光刻技术,综合表现全面提升,官方宣称相比第一代7nm EDV工艺可以带来最多80%的晶体管密度提升,15%左右的性能提升或者30%左右的功耗降低。

2019-09-26 14:49:11 4798

4798 日前,高通发布了新一代旗舰平台骁龙865、主流平台骁龙765/765G,分别采用台积电7nm、三星8nm工艺制造。那么,高通为何在两个平台上使用两种工艺?骁龙865为何没用最新的7nm EUV?5nm方面高通有何规划?

2019-12-09 17:23:23 6488

6488 在全球晶圆代工市场上,已经没有公司能超过台积电了,他们的16/12nm订单居高不下,7nm及改良版7nm EUV工艺如火如荼,下一代的5nm工艺进展也非常顺利,据悉现在的良率就比7nm工艺初期要好了。

2019-12-01 09:57:11 776

776 高通发布了新一代旗舰平台骁龙865、主流平台骁龙765/765G,分别采用台积电7nm、三星8nm工艺制造。那么,高通为何在两个平台上使用两种工艺?骁龙865为何没用最新的7nm EUV?5nm方面高通有何规划?

2019-12-09 17:56:29 3685

3685 台积电将会在今年年中开始进行5nm EUV工艺的量产,届时台积电的主要5nm工艺客户有苹果和华为两家。根据MyDrivers报道,华为的下一代旗舰处理器可能命名为麒麟1020,有5nm EUV工艺加持后性能会比麒麟990 5G SoC提升50%!

2020-03-07 15:52:09 2486

2486 台积电5nm制造工艺基于ULV,也就是紫外线光刻技术实现,之前的7nm EUV工艺同样也是基于这项技术。那么制程的缩小又意味着什么?相比于7nm工艺,5nm工艺可以进一步提升芯片的晶体管密度,提升性能并降低功耗,可广泛用于PC、智能手机等设备的元器件中。

2020-03-12 14:10:44 2570

2570 在开发5nm制程技术仅一年之后,三星就开始了 5nm EUV(极紫外)生产线的建设。三星公司希望在2030年之前击败台积电,并成为半导体业务的领导者。

2020-03-12 14:30:36 2065

2065 2020年,全球最先进的半导体工艺要从7nm升级到5nm了,台积电最近上半年就开始量产5nm EUV工艺,而三星也加码投资,预计6月底完成5nm EUV生产线。

2020-03-13 08:35:01 2624

2624 台积电上周发布了3月及Q1季度财报,营收同比大涨了42%,淡季不淡。不过接下来的日子半导体行业可能不太好过了,ASML的EUV光刻机已经断货,要延期交付,好在台积电今年已经在5nm工艺上抢先三星了。

2020-04-15 08:55:17 3193

3193 4月20日消息,据国外媒体报道,按计划,在7nm工艺量产近两年之后,芯片代工商台积电今年将大规模量产5nm芯片,台积电方面日前也透露,他们的5nm工艺已经量产,良品率也非常可观。

2020-04-20 17:00:03 2742

2742 ,虽然整体多少还是受到疫情影响,但台积电强调5nm工艺技术影响程度不大,仅接下来的3nm工艺试产可能会有延后情况。

2020-04-21 15:56:23 2478

2478 基于5nm EUV工艺。 到底哪家的5nm工艺更稳,要等双双有终端上市后才能掰一掰腕子。 另外,AMD的Zen3和RDNA2都没有上马5nm,而是7nm增强版。除了

2020-09-17 13:58:01 790

790 (功耗、性能和面积)优势,同时加快产品上市时间 ● 新思科技进一步强化关键产品,以支持TSMC N3制造的进阶要求 新思科技(Synopsys)近日宣布,其数字和定制设计平台已获得TSMC 3nm制造技术验证。此次验证基于TSMC的最新设计参考手册(DRM)和工艺设计工具包(

2020-10-14 10:47:57 1764

1764 重点 ● TSMC认证基于新思科技3DIC Compiler统一平台的CoWoS和InFO设计流程 ● 3DIC Compiler可提高先进封装设计生产率 ● 集成Ansys芯片封装协同分析解决方案

2020-10-14 11:11:21 2099

2099 5nm工艺是7nm之后台积电又一项行业领先、可带来持久营收的重要工艺,随着投产时间的延长,其产能也会有明显提升,会有更多的客户获得产能,5nm工艺为台积电带来的营收也会大幅增加。

2020-10-16 16:40:02 1732

1732 在先进半导体工艺上,台积电已经一骑绝尘了,其他人望不到尾灯了,今年量产了5nm,明年就轮到3nm了。

2020-10-17 09:12:38 1777

1777 1080处理器是三星首款基于最新的5nm EUV FinFET工艺制造的处理器,进一步提高设备的电源效率和性能。 三星Exynos在11月12日在上海举行首场国内线下发布会;据介绍,vivo将首发搭载

2020-11-12 18:13:20 3186

3186 Shin称,通过采用和集成现有的最先进技术,例如5nm EUV和最新的处理内核,Exynos 1080可以在移动设备中提供5G,设备内置AI技术

2020-11-12 16:48:02 1631

1631 制造工艺EUV(极紫外光刻)。Exynos 1080 所采用的 5nm EUV 工艺与 8nm LPP(成熟低功耗)相比,性能提升 14%,功耗降低 30%;与 7nm DUV(深紫外光刻)相比,

2020-11-12 16:48:29 1671

1671 在先进工艺上,台积电可以说是天字一号晶圆代工厂了,7nm工艺领先别家两年量产,5nm工艺今年也抢到了苹果、华为两个大客户,尽管华为9月份之后就被迫退出了。

2020-12-22 12:45:55 1235

1235 ,AMD、NVIDIA等公司也会跟进5nm,不过至少要到2021年底了,在此之前台积电的5nm工艺会有一段空缺,有报告称明年Q2季度5nm利用率会降至80%以下。 谁能来填补这个空缺?矿机厂商现在已经找到机会了,一方面是最近比特币价格大涨,数字货币市场全面复兴

2020-12-22 14:12:28 1618

1618 日 /美通社/ -- Arasan Chip Systems为台积公司(TSMC)行业领先的22nm工艺技术扩展其IP产品,用于台积公司22nm工艺SoC设计的eMMC PHY IP立即可用。台积公司22nm工艺

2021-01-21 10:18:23 2386

2386 SoC 设计与应用技术领导厂商Socionext Inc.(以下“Socionext”)宣布,公司将采用台积电最新5nm制程工艺(N5P)用于下一代汽车定制芯片业务。Socionext汽车定制芯片

2021-02-05 11:50:27 1835

1835 )宣布,其数字和定制/模拟流程已获得 TSMC N3 和 N4 工艺技术认证,支持最新的设计规则手册(DRM)。通过持续合作,Cadence 和 TSMC 发布了 TSMC N3 和 N

2021-10-26 15:10:58 1928

1928 ”)已在5nm、4nm和3nm工艺技术中认证了新思科技的PrimeLib统一库表征和验证解决方案,可满足高性能计算、5G、汽车、超连接、以及人工智能芯片等下一代设计的高级计算需求。此次认证还包括

2021-11-09 16:59:26 1459

1459 技(Synopsys)近日宣布其数字定制设计平台已获台积公司N3制程技术认证,双方将共同优化下一代芯片的功耗、性能和面积(PPA)。基于多年的密切合作,本次经严格验证的认证是基于台积公司最新版本的设计规则手册(DRM)和制程设计套件(PDK)。此外,新思科技

2021-11-16 11:06:32 1558

1558 Siemens Digital Industries Software 宣布,其用于模拟、数字和混合信号 IC 设计的电源完整性分析的全新 mPower™ 解决方案现已通过 TSMC 的 N7 和 N5 工艺技术认证。

2022-03-16 14:36:14 1489

1489 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 4800

4800 新思科技数字和定制设计流程获得台积公司的N3E和N4P工艺认证,并已推出面向该工艺的广泛IP核组合。

2022-07-12 11:10:51 877

877 ,纳斯达克股票代码:SNPS )近日宣布,得益于与台积公司的长期合作,新思科技针对台积公司N3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的

2022-11-08 13:37:19 1360

1360 Ansys凭借实现灵活的功耗/性能权衡,通过台积电N3E工艺技术创新型FINFLEX架构认证 主要亮点 Ansys Redhawk-SC与Ansys Totem电源完整性平台荣获台积电N3E

2022-11-17 15:31:57 697

697 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 708

708 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381 流程现已通过 Intel 16 FinFET 工艺技术认证,其 Design IP 现可支持 Intel Foundry Services(IFS)的此工艺节点。 与此同时,Cadence 和 Intel 共同发布

2023-07-14 12:50:02 382

382

Cadence近日宣布,其数字和定制/模拟流程在Intel的18A工艺技术上成功通过认证。这一里程碑式的成就意味着Cadence的设计IP将全面支持Intel的代工厂在这一关键节点上的工作,并提

2024-02-27 14:02:18 160

160

正在加载...

电子发烧友App

电子发烧友App

评论