在高速实时或者非实时信号处理系统当中,使用大容量存储器实现数据缓存是一个必不可少的环节,也是系统实现中的重点和难点之一。SDRAM(同步动态随机访问存储器)具有价格低廉、密度高、数据读写速度快的优点

2018-01-18 07:21:00 7964

7964

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR3

2019-04-22 07:00:08

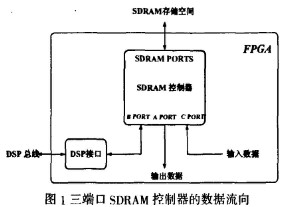

现场电路设计中。本文用 FPGA 作为接口芯片,提供控制信号和定时信号,来实现 DSP 到 SDRAM 的数据存取。1 、SDRAM 介绍本文采用的 SDRAM 为 TMS626812A,图 1 为其

2020-04-23 08:00:00

FPGA怎么实现控制CF从SDRAM中读取数据以及实现CF卡向SDRAM中上传数据????本人初学者,希望大家帮帮忙!!!!谢谢!!

2013-02-25 21:58:59

处理方法。本系统的主要工作是通过基于FPGA的嵌入式系统,实现数据采集、数据存储、LCD显示、USB数据传输和数据处理,完成光 纤微扰动传感的扰动识别和定位功能。1 系统结构和硬件设计1.1 系统结构

2020-09-04 09:56:23

存储器)也是FPGA设计中经常采用的内存器件,掉电后不能保存数据,功耗也比较大。因此Flash用于保存FPGA系统启动所需的配置文件,SDRAM则用于系统的数据的缓存,所有程序的运行都在内存中进

2018-08-02 09:37:08

实战应用,这种快乐试试你就会懂的。话不多说,上货。SDR SDRAM驱动设计实用进阶 本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板,以下为配套的教程,如有入手开发板,可以登录官方

2023-03-27 17:09:14

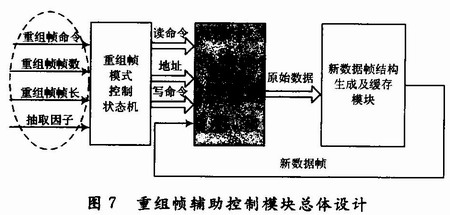

SDRAM文件结构存储控制的FPGA实现面对不同的应用场景,原始采样数据可能包含多种不同样式的信号,这给传统基于连续存储方式的数据缓存系统带来了挑战。除此之外,由于对不同信号的处理往往需要不同的数据

2012-08-13 10:40:40

和后仿真。以上介绍了一种应用于通用微处理器系统中的SDRAM与双口RAM之间的数据转移接口控制电路,由VHDL语言设计,用Xilinx公司4000系列FPGA实现,目前该电路硬件实现和微处理器系统已经通过验证,证明可将SDRAM作为高速、大容量存储器应用在简单电子系统中。

2019-06-10 05:00:08

对SDRAM的控制,并通过利用FPGA控制数据存取的顺序来实现对数字视频图像的旋转,截取、平移等实时处理。SDRAM的控制原理,如图1所示。 [/hide]

2009-11-13 11:37:08

请问各位大虾 SDRAM是如何进行读写的,如何将文件数据存储到SDRAM中 网上没找到这方面的资料 求各位大虾帮忙

2013-04-14 10:09:13

用DAQmax采集助手做的一个数据采集系统,用TDMS文件格式存储数据,怎样实现系统把一天的数据存储到以当日日期命名的数据文件中?

2014-10-25 09:01:55

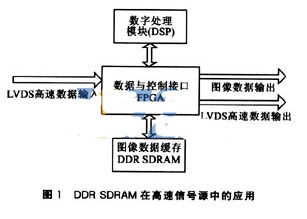

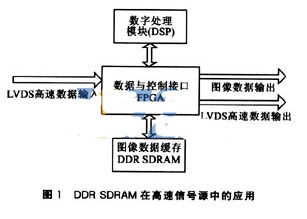

。 在该系统中,由FPGA的完成各模块之间的接口控制。FPGA接收从前端传送过来的高速数字信号,并将其存储在DDR SDRAM中;DSP通过FPGA读取DDR中的数据,处理后再送回到DDRSDRAM,最后

2018-12-18 10:17:15

的文件系统,实现了文件系统基本的数据缓存、掉电恢复、磨损均衡等功能,在资源相对富裕的环境中,开发者们可以对其运行机制甚至存储结构进行“使用空间换时间”的优化策略,提升读写的IO性能。学会有效地利用文件系统往往能起到事半功倍的作用,希望开发者能够将所学知识有效应用到未来的开发工作中,从而提高开发工作的效率。

2022-07-18 12:18:40

缓存控制器( Buffer Controller)缓存控制器负责暂时存储接收或发送的数据,这些数据来自设备端的外部SDRAM或者主机。考虑到USB 2. 0 高速数据的传输要求,减小存储或读取数据

2019-04-12 07:00:12

设计的思想。项目实现了PC机上的上位机通过以太网UDP协议将图片数据传输给AC620 FPGA开发板,AC620接收图片数据后将图片缓存在片外的SDRAM中,最后将缓存的图片数据显示在4.3寸TFT屏上

2017-09-17 16:43:43

`一、硬件平台二、实验简介本实验基于ARM+FPGA超mini款iCore4T双核心板,核心板ARM挂有一片32MB SDRAM,可用于数据采集缓存,液晶显示缓存,代码执行等。该实验将带你一步一步

2020-04-06 22:08:43

管理模型,它能够根据应用优先级区分回收缓存资源以实现对各应用缓存分区容量的在线动态调节进而达成应用级缓存管理语义.实验数据表明PARP策略能够在实际系统中有效的支持区分应用优先级,这不仅可以用于实现存储系统

2010-04-24 09:43:47

使用Verilog实现基于FPGA的SDRAM控制器

2012-08-20 19:35:27

介绍了一种基于现场可编程门阵列(FPGA)和第二代双倍数据率同步动态随机存取记忆体(DDR2)的高速模数转换(ADC)采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA中如何实现高速同步

2010-04-26 16:12:39

基于FPGA的SDRAM设计与实现

2013-03-14 18:34:25

设计高温环境下(最高120°)基于FPGA的数据采集存储系统,就是通过传感器采集数据,通过FPGA来控制,把数据存储到存储芯片上,回头可以通过接口读取数据显示在计算机上,求大师给我指导,我急需整个系统的protel原理图,请各位帮忙,我将感激不尽。最好有附件画出整个原理图,谢谢!

2012-10-29 21:37:12

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

作者:吴连慧,周建江,夏伟杰摘要:为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器

2018-08-02 11:23:24

显示。FPGA的片内存储资源较少,对于缓存如此大量的数据,只能使用SDRAM或DDR3缓存数据。2、图片的预处理首先选取要显示的图片两张,使用 Window 系统自带的画图工具对图片进行处理,将图片

2023-01-06 17:06:04

SDRAM同步动态随机存储器,同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址

2016-10-07 09:43:43

吞吐量大、功耗低的需求,因此选择DDR3 SDRAM作为机载视频图形显示系统的外部存储器。本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。

2019-06-24 06:07:53

要求:该系统将图像采集、显示和存储功能集成到FPGA平台上,本设计采用NIOS II 设计软核系统,通过FPGA初始化图像传感器OV7670,OV7670再等待场同步,行同步,将采集的数据在TFT

2012-05-22 09:22:09

了解它,运用它,你会发现它将非常有趣。恭喜我们两名同学在快乐中制作出了新的作品,在老师的帮助下,两位同学合力完成了基于SDRAM的图像存储显示系统,跟大家分享一下学习过程吧!首先是设计思路,我们的想法

2019-08-19 10:57:37

的网络数据传输。3、 系统结构高速同步数据采集系统主要包括以下几个部分:ARM控制器、存储电路、FPGA逻辑控制电路、A/D转换电路、FIFO缓存、电源电路、接口电路等。系统具备多通道数据采集接口

2010-08-31 09:14:55

基于Xilinx FPGA的DDR2 SDRAM存储器接口

2012-08-20 18:55:15

FPGA怎么把数据写入SDRAM缓存啊?

2016-08-17 11:37:17

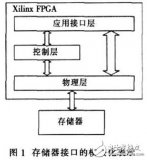

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

FPGA芯片上实现对时序与数据缓存系统的控制。最后针对Xiling公司的FPGA器件XQ2V3000对设计进行了配置及仿真,从而验证了该设计方案的可行性。

2021-06-08 06:35:41

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些

2019-08-09 07:42:01

表。4 结 语介绍了在嵌入式Windows CE系统平台上,使用大容量SDRAM作为动态存储设备的方案。详细介绍了sDRAM硬件连接方案以及软件接口的实现。该方案已经在工程设计中投入使用,其可以在同类的嵌入式高端产品中推广使用。

2020-08-12 00:00:00

` 帧差法FPGA实现原理作者:FPGA自习室微信公众号:FPGA自习室时间:2020/4/12邮箱:1964740514@qq.com根据帧差法的实现流程,设计的双端口SDRAM控制器,一侧读写

2020-04-12 23:29:14

,影响系统可靠性,要进一步提高系统实时性,必须研究开发高速嵌入式雷达信号采集系统。这里结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢFPGA实现的异步FIFO和锁相环(PLL)结构来实现

2019-08-21 06:56:32

请问怎么利用FPGA实现模式可变的卫星数据存储器纠错系统?

2021-04-13 06:10:54

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

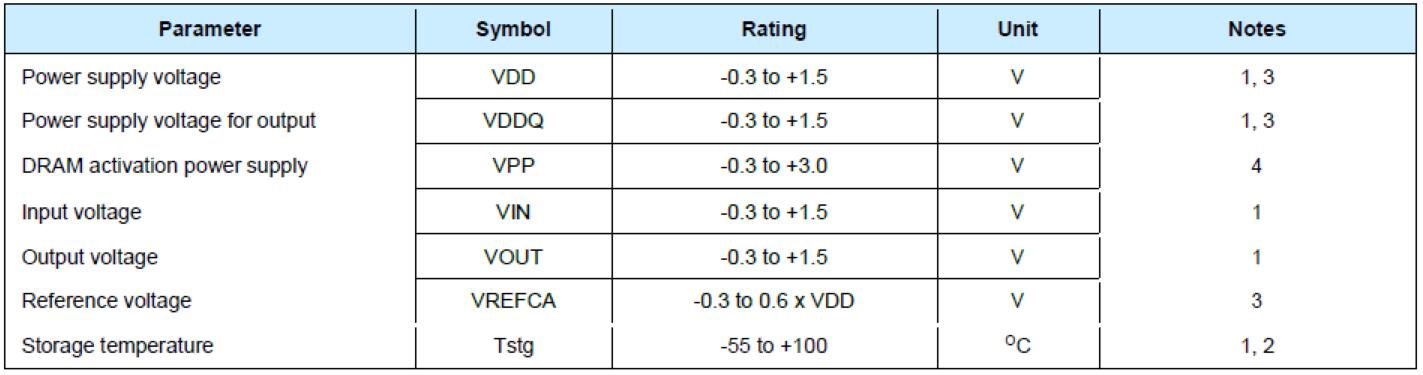

型号 UD408G5S1AF的一款8Gb 32位 DDR4 SDRAM,是一款支持使用在英特尔Arria 10 SoC FPGA以及Kintex Ultrascale FPGA中的存储器。32位 DDR4

2020-09-23 10:59:56

本帖最后由 upmcu 于 2012-7-28 15:07 编辑

截图:LED显示控制系统中SDRAM控制器的设计.pdf基于FPGA的DDR2+SDRAM数据存储研究.pdf基于FPGA

2012-07-28 14:40:53

XC2S200型FPGA器件实现。采用Spansion公司的NOR Flash存储器来存放配置文件,其型号为S29GL512N,容量为512 Mb。系统总体框图如图3所示。上位机软件包括Flash烧写

2019-05-30 05:00:05

。 3、海量缓存的设计实现 本系统使用了两片256k16bit容量的SRAM作为高速缓存,系统中的4个通道可同时存储每通道128k点采样数据。在25MHz的采样频率下,一次可采集存储5ms多的波形数据

2020-12-04 15:59:14

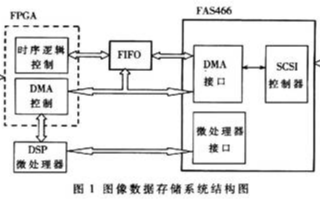

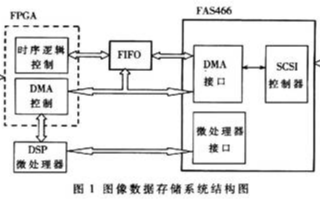

为了实现SCSI协议和硬盘存储,一般需要有微处理器、DMA控制器、SCSI协议控制器、数据缓存器等硬件支持和相应的软件控制模块。·微处理器用来控制设备中各部件的工作,实现设备本身的特定功能。该专用

2011-06-02 09:33:21

一种I2C总线型EEPROM 存储器,在数据记录系统中,用来保存当前时刻以前一段时间内的多组数据使用时设计成首尾地址相接的环型存储结构,实现数据文件的循环存储文章介绍循环

2009-04-15 10:36:20 33

33 探讨了高速数据采集系统中高速采样缓存的重要性和实现途径,阐述了基于ADSP-21065L的并行多通道数据采集板上高速采样缓存的设计与电路结构,给出了采用FPGA实现通道复用和采样数据

2009-04-23 17:08:09 23

23 介绍基于现场可编程门阵列(FPGA),利用VHDL 语言设计实现MMC2107 与SDRAM 接口电路。文中包括MMC2107 组成结构、SDRAM 存储接口结构和SDRAM 控制状态机的设计。

2009-05-15 14:47:29 24

24 提出了一种在HDTV SOC 系统中实现多模块共享存储单元的高效SDRAM 控制器。通过利用合理的请求仲裁、Full Page 读写、指令与数据分离、指令缓存和前后相关处理等机制,实现了高吞吐

2009-08-14 16:09:14 13

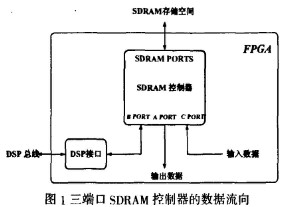

13 设计实现了一种基于FPGA 的,可用于多数据缓存的、能够高效利用带宽的多端口SDRAM 控制器。本文使用状态机的设计思想,采用Verilog 硬件描述语言设计了时序控制程序。得到的SDR

2009-08-27 09:43:33 22

22 本文设计了一种以 FPGA 为数据压缩和数据缓存单元的高速数据采集系统,其主要特点是对高速采集的数据进行实时压缩,再将压缩后的数据进行缓冲存储。该设计利用数据比较模

2009-11-30 15:32:36 20

20 摘要:一种I2C总线型EEPROM存储器,在数据记录系统中,用来保存当前时刻以前一段时间内的多组数据。使用时设计成首尾地址相接的环型存储结构,实现数据文件的

2006-03-24 13:01:38 1123

1123

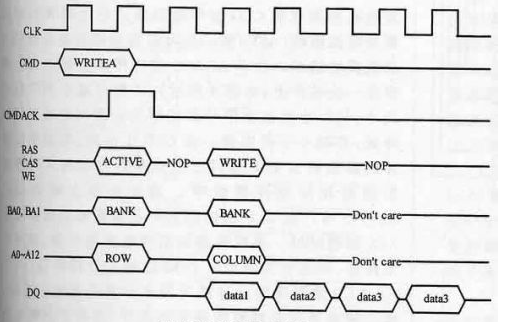

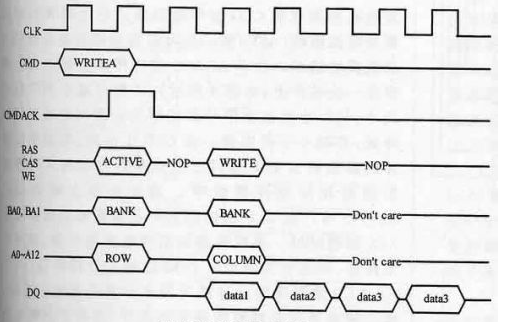

摘要: 介绍了SDRAM的存储体结构、主要控制时序和基本操作命令,并且结合实际系统,给出了一种用FPGA实现的通用SDRAM控制器的方案。

关键词:

2009-06-20 12:51:58 834

834

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键

2009-06-20 13:04:51 2075

2075 基于FPGA的高速SDRAM控制器的视频应用

0 引言 SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适

2009-11-04 09:56:20 847

847 FPGA芯片在高速数据采集缓存系统中的应用

概 述在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬

2010-03-30 10:51:15 881

881

O 引言

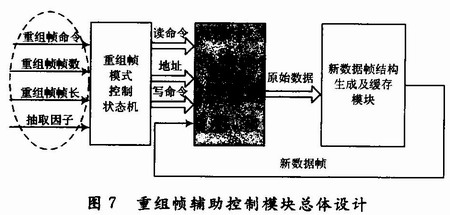

面对不同的应用场景,原始采样数据可能包含多种不同样式的信号,这给传统基于连续存储方式的数据缓存系统带来了挑战。除此之外,由于对不同信

2010-10-08 11:11:20 1179

1179

本内容提出了适于测控系统的文件存储结构研究,希望对大家学习上有所帮助

2011-05-26 16:20:03 9

9 本文利用“FPGA+单片机”作为存储控制器,采用基于LZW算法的数据压缩技术,以SDRAM作为周期存储和缓存,SD卡作为最终存储载体,实现车载CAN总线记录仪实现大容量存储系统。

2011-09-08 16:24:59 2172

2172

在高速实时或者非实时信号处理系统当中,使用大容量存储器实现数据缓存是一个必不可少的环节,也是系统实现中的重点和难点之一。详细阐读SDRAM数据文档的前提下,参考ALTERA公司的

2012-10-30 17:04:58 1770

1770

使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 高速图像存储系统中SDRAM控制器的实现

2016-08-29 15:02:03 10

10 华清远见FPGA代码-SDRAM读写控制的实现与Modelsim仿真

2016-10-27 18:07:54 26

26 中,并采用DMA传输技术将存储后的图像数据上传至计算机硬盘中作进一步处理;同时,利用SDRAM显存实时刷新数据,FPGA构造相应的VGA信号,最终实现100 MB/s图像数据的实时显示。 随着数据存储设备被广泛应用于航空航天系统、医疗卫生、工业自动化等各行各业,对于图像设备采集的控制及实

2017-10-11 18:33:17 6

6 在数字图像处理、航空航天等高速信号处理应用场合,需要有高速大容量存储空间的强力支持,来满足系统对海量数据吞吐的要求。通过使用大容量同步动态RAM(SDRAM)来扩展嵌入式DSP系统存储空间的方法

2017-10-23 10:48:11 1

1 的像素大小。在存储模块中,SDRAM的工作时钟和视频采集系统的时钟不同,为解决读写时钟不同步的问题,采用异步FIFO实现跨时钟域的同步化,同时采用了两片SDRAM实现乒乓缓存设计,对SDRAM控制器各个模块分别进行Modelsim仿真验证,得出正确结果,可以满足系统的整体要求。

2017-11-17 01:28:55 3704

3704

控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

2017-11-18 12:42:03 2054

2054

在高速信号处理系统中, 需要缓存高速、大量的数据, 存储器的选择与应用已成为系统实现的关键所在。DDR SDRAM是一种高速CMOS、动态随机访问存储器, 它采用双倍数据速率结构来完成高速操作

2018-07-20 18:38:00 12744

12744

为提高云存储的访问速率并降低费用,提出了一种面向费用优化的云存储缓存策略。利用几乎免费的局域网环境下的多台桌面计算机,在本地建立一个分布式文件系统,并将其作为远端云存储的缓存。进行文件读取时,首先

2018-01-24 14:45:35 0

0 针对Ceph文件系统元数据写操作响应时间较长的问题,提出一种对元数据缓存进行备份的方案。该方案采用多个元数据服务器之间互相备份写缓存数据的方法,保证元数据的可靠性,并设计基于元数据热度的多队列缓存

2018-02-08 15:38:24 0

0 SDRAM 具有存储容量大、速度快、成本低的特点,因此广泛应用于雷达信号处理等需 要海量高速存储的场合,但是SDRAM 的操作相对复杂,需要有专门的控制器配合处理器 工作完成数据的存取操作。随着FPGA 技术的快速发展及其应用的普及,用FPGA 实现 SDRAM 控制器是目前最流行的技术手段。

2019-04-26 08:06:00 2129

2129

,因此能够很好地满足上述场合对大量数据缓存的需求。但DDR SDRAM的接口不能直接与现今的微处理器和DSP的存储器接口相连,需要在其间插入控制器实现微处理器或DSP对存储器的控制。

2019-07-02 08:03:00 4051

4051

了SDRAM作为缓存器件。来自多个输入通道的数据在采集后需要暂时存储在SDRAM中,处理后的数据也需要存储在SDRAM中,再输出到输出通道中。在SDRAM与多个输入输出通道之间,采用多个双口RAM作为

2020-06-01 07:08:00 2577

2577

实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序

2019-08-14 08:00:00 3401

3401

,SDRAM的原理和时序,SDRAM控制器,动态随即存储器SDRAM模块功能简介,基于FPGA的SDRAM控制器的设计和实现,一种简易SDRAM控制器的设计方法

2018-12-25 08:00:00 56

56 在DSP应用系统中,需要大量外扩存储器的情况经常遇到。例如,在数码相机和摄像机中,为了将现场拍摄的诸多图片或图像暂存下来,需要将DSP处理后的数据转移到外存中以备后用。从目前的存储器市场看,SDRAM由于其性能价格比的优势,而被DSP开发者所青睐。DSP与SDRAM直接接口是不可能的。

2020-04-08 09:26:00 1268

1268

,SDRAM是非常流行的存储器。它们不像静态存储器那样容易控制,因此经常使用SDRAM控制器。 FPGA器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA的基本结构包括可编程输入输出单元,可配

2020-05-19 17:35:14 1833

1833

随着目前数字技术的发展,多通道数据的高速采集处理获得了广泛的应用,面对大的数据吞吐量,往往需要共享一块大的缓存空间(外挂的大容量存储SDRAM或是DDR)。而大多时候多通道之间的实时数据流量并不一定

2020-11-20 15:54:54 635

635 在 DSP 应用系统中,需要大量外扩存储器的情况经常遇到。例如,在数码相机和摄像机中,为了将现场拍摄的诸多图片或图像暂存下来,需要将 DSP 处理后的数据转移到外存中以备后用。从目前的存储器市场

2020-12-22 13:16:00 5

5 针对SDRAM 操作繁琐的问题,在对SDRAM 存储器和全页突发式操作进行研究的基础上,提出一种简易SDRAM 控制器的设计方法。该设计方法充分利用全页式高效率存取的优点,对SDRAM 进行配置、全页突发式读写时,操作方便。在实现sDRAM 的快速批量存储方面,具有良好的应用价值。

2020-12-18 16:13:18 6

6 SDRAM与 Flash不同,它不具有掉电保持数据的特性,但其存取速度大大高于 Flash存储器,且具有读/写的属性,因此 SDRAM在系统中主要用作程序的运行空间,数据及堆栈区。当系统

2020-12-18 16:13:16 12

12 本文档的主要内容详细介绍的是使用FPGA读写SDRAM存储器的实例工程文件和程序免费下载。

2020-12-18 16:13:13 10

10 的设计方法。结合实际系统,设计给出了使用FPGA实现 SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通过增加流水级数和将输出触发器布置在IO单元中,该控制器可达到185MHz的频率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越来越广泛。

2.SDRAM具有存储容量大,速率快的特点。

3.SDRAM对时序要求严格,需要不断刷新保持数据。

.FPGA在电子设计中的广泛应用,使用十分灵活利用FPGA来设计自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 实现SCSI协议和硬盘存储,通常需要有微处理器、DMA控制器、SCSI协议控制器、数据缓存器等硬件支持和相应的软件控制模块。而本系统。DMA控制通过对FPGA编程来实现。图像数据存储系统结构图如图l所示。

2021-03-16 14:52:10 2076

2076

基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的设计与实现简介(嵌入式开发工程师和基层公务员)-该文档为基于FPGA的SDRAM控制器的设计与实现简介文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当FIFO1中缓存有一行图像数据时,在下一行图像数据来临的时候,将FIFO1中缓存的图像数据读出,并传递给下一个FIFO

2022-05-10 09:59:29 3056

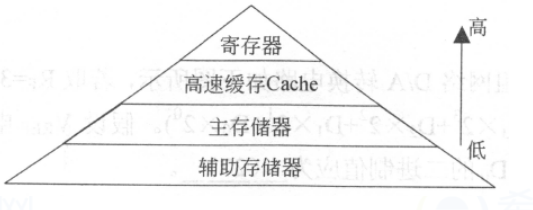

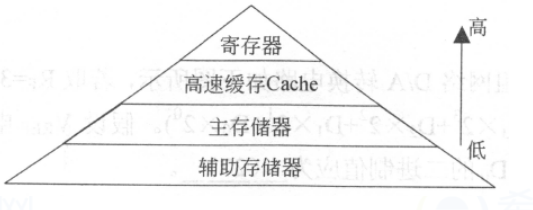

3056 存储系统的层次化结构可以分为5级:寄存器组、高速缓存Cache、主存、虚拟存储器和外部存储器。其中,寄存器组总是在CPU内部,程序员可通过寄存器名访问,无总线操作,访问速度最快;其余

2022-06-18 20:47:10 4738

4738

实时视频SDRAM控制器的FPGA设计与实现

2022-12-30 09:21:26 3

3

电子发烧友App

电子发烧友App

评论