powerlogic如何生成网表netlist

- powerlog(6190)

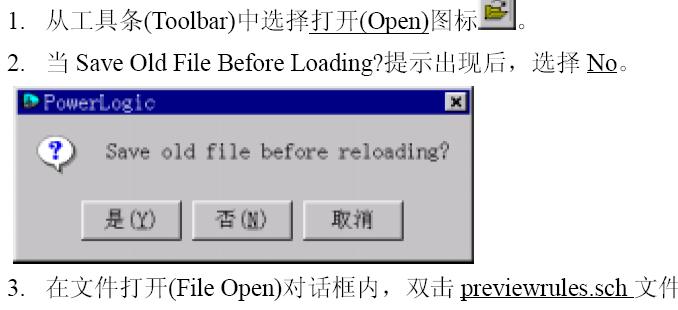

相关推荐

POWERLOGIC 自动重新编号的的解决方法

LOGIC下,从刚才打开的对话框里选Design 再选,Send netlist 将网络表导到PCB 里面,在PCB 里面按需要放好,元件后,再选Setup---》ECO Prefs 进到ECO模式下,这样

2008-07-21 17:37:54

生成网表时出错,请高人指点

在生成网表时报Error,【ALG0030】Unable to read design "d:\PCB\test\test.dsn"为什么呢,请高手说明,谢谢

2013-03-26 16:04:00

网表包含不起作用

您好,我有一个用于2端口无源组件的SPICE / Spectre子电路。我试图通过网表导入和Netlist include元素在ADS 2011.10中使用它。我已按照文档“Netlist

2019-07-04 08:06:30

AD14版的怎样生成网表,导入到pads中?

AD14版的原理图选项design->netlistfordocumnet中怎么没有pads选项?怎样生成.asc网表,导入到pads中?

2015-01-07 16:37:54

AD9在原理图如何生成网表

AD9在原理图绘制完之后如何生成网表文件?在PROTEL99SE里面我就可以看到相关选项 设计\GREATE NET,AD9就没有这个选项,另外AD9里面也没有电气规则检测选项。

2012-12-25 10:16:31

AD网表导入allgero问题

本帖最后由 菜鸟级别 于 2015-9-7 22:04 编辑

AD生成OrCad/PCB2网表,第一次导入allgero没问题,但是更新原理图(有添加元件)重新生成网表,再导入allegro,没有报错,allegro中的元件清单还是和之前的一样,没有变化,请高手帮忙解释下。

2015-09-07 21:31:40

Allegro 15.7下为何不能导出网表?求高人指点

在WIN7系统下安装了allegro,在从原理图导出网表时,不会报错,也不会生成网表文件,我按照附件的安装方式安装的,请各位大侠帮忙解答一下!

2013-03-25 19:32:45

EDIF网表实施错误

您好我有一个模块的EDIF网表(由Vivado 2017.4中的第3方生成)。我没有模块源verilog。我有加密模块的行为模型,我有一个行为模型的测试平台。行为模拟在Modelsim中运行。行为

2018-11-07 11:34:55

Orcad软件怎么生成导出allegro网表、ad网表、pads网表

1、 orcad软件怎么生成allegro网表、ad网表、pads网表?答:首先,通过orcad软件打开原理图,选中原理图的根目录,点击Tools-Creat Netlist,或者是点击菜单栏上N

2019-08-26 17:46:14

PCB设计经验之Altium网表及Protel网表的生成

8.2.1网表网表也称网络表,顾名思义,就是网络连接和联系的表示,其内容主要是电路图中各个元件类型、封装信息、连接流水序号等数据信息。在使用Altium]

2020-04-24 08:00:00

PCB设计软件蓝牙音箱实操│网表导出导入和封装路径设置

表格式,再导入到PCB工程中。二、原理图网表生成方法一(第一方):使用OrCADCapture打开原理图单击按钮或执行菜单命令Tools/create Netlist…,弹出对话框,选择PCB

2018-07-31 14:15:07

ad网表导入allegro

本帖最后由 糖果. 于 2016-12-19 15:22 编辑

Altium Designer13.3.4导出网表,allegro16.6通过other导入导入后出现error生成了device,setup中路径已添加,求问如何解决

2016-12-19 14:32:45

allegro 16.6 100讲中EXAMPLE2.DSN可以导出网表,Hi3519V101DMEB.DSN为什么不可以导出网表?

第一个可以生成网表,这是第二个不能生成网表。查了一下是器件属性Device 几个器件重复,但第一例子器件device重复就可以导出网表,不知道为什么?使用的均为orcad下PCB Editor 导出

2019-03-04 07:35:18

cadence16.6生成网表后原理图与PCB不能正常交互,为何?

cadence16.6生成网表后原理图与PCB不能交互,交互功能勾选了,原理图改网络重新生成网表PCB的网络也会相应改过,PCB选择器件高亮原理图相应的也会有关联,但是在原理图选择元器件PCB不会

2021-09-09 17:10:24

cadence:capture生成allegro网表的一个问题

be identicalon all sections of the part.生成网表的时候,这个问题如何解决?我的U3是分成三个部分的(A,B,C),我觉得主要问题估计是在Conflicting

2012-05-02 14:37:51

orcad 生成allergo网表时报错,Could not open file /pstxprt.dat

刚开始使用allergo,准备用orcad导出网表,DRC已经过了,pcb footprint也都填好了,allergo路径也设置了,但是导出的时候出现了#77 ERROR(SPCODD-77

2017-06-25 21:25:28

orcad生成网表出错DRC检测只有警告

求助!orcad生成网表的时候出现错误,DRC检测只有警告,网表文件能生成但导入不了查看错误信息是{ Using PSTWRITER 16.6.0 d001Aug-21-2018 at 17:28

2018-08-22 15:26:41

orcad软件怎么生成allegro网表、ad网表、pads网表?

1、ORCAD软件打开原理图,选中原理图的根目录,点击Tools-Creat Netlist,或者是点击菜单栏上N的图标,如下图所示,即可产生网标。2、Allegro第一方网表如上图操作以后。弹出

2018-11-05 15:04:04

win7下protel99生成网表

原理图和封装都画好了,层次原理图,ERC没有问题~~生成网表的时候,子层次图中,+3.3V节点没有了,如果将部分+3.3V节点换成+3.3V_P,则显示+3.3V_P节点(或+3.3V,显示数目比较

2011-12-30 15:20:26

【求助】OrCAD Capture原理图生成Netlist问题

Cadence16.6中OrCAD Capture原理图生成Netlist时候出现如下图问题,请大神告知原因以及如何解决。 错误信息为: #1 ERROR(ORCAP-36020): Unable

2017-12-23 15:54:39

不能生成网表

oracd capture cis 生成网表时,我确定所有路径都是没问题的,而且也没有非法字符,但是按了creat netlist的确定时,一直不出现这个窗口,也没有生成任何bat文件。后来查看

2016-06-25 13:02:03

使用synplify和生成器网表文件合成VIRTEX 7时报告严重警告

相匹配,应在源网表中更改SIM_DEVICE的值。未能正确设置SIM_DEVICE将阻止此设计生成比特流。严重警告[Netlist 29-335]'IDELAYE2'类型的实例'u_idelaye1'可能

2018-10-29 14:17:21

分享一个FEC RTLvs Netlist等价性比对的示例

中,只要你使用逻辑综合将RTL转换为门级网表,那么你必然需要使用FEC工具进行RTL和门级网表等价性比对。下图是一个FEC RTLvs Netlist等价性比对的示例。看起来不同,实际功能是一致

2022-07-22 14:56:37

利用AD9中CAMtastic 反向生成PCB 文件

\Gerbers\ 导入方法和导入NC Drill一样4、使用Tool/Netlist/Extract 提取导入的Gerber 的网络(将相连的Track 视为同一网络,网络名随机生成)。如果不导入网表将不

2012-09-10 16:04:56

制作一个简单的GPIO生成网表错误

我只是按照示例制作一个简单的GPIO。生成网表时,会产生如下错误。错误:EDK:4074- 实例:MYaxi_gpio_0,PORT:GPIO_IO,连接器:axi_gpio_0_GPIO_IO-

2019-02-20 10:45:45

可以将原理图网表导入PADS Maker吗

亲爱的先生现在我尝试使用PADS Maker工具。我是PCB布局的初学者。那么,是否可以将第三方工具生成的原理图网表导入PADS Maker?谢谢。以上来自于谷歌翻译以下为原文Dear sirNow

2018-10-23 11:39:03

在使用candence 编译生成网表时出现#1035 error :Cannot find a ppt part that mat

在使用candence 编译生成网表时出现#1035 error :Cannot find a ppt part that matches the instance properties应该怎么解决

2010-01-14 22:35:09

如何为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?

嗨,Vivado的新手问题;是否有可能为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?谢谢,埃里克

2019-11-11 07:33:05

如何使用网表精确定位ZYNQ上的确切区域

你好,我现在正在学习如何使用Vivado。现在我在Vivado中“实现”并点击“Open Implementation Design”后获得一个网表。这是我的网表图片。我可以知道ZYNQ芯片上的确

2018-10-19 14:38:09

如何创建我们自己的IP核或可重复使用的网表?

你好,我目前正在开发一些VHDL项目,我们生成可重用的网表似乎很有趣。遗憾的是,我没有找到从Xilinx ISE 10.1生成这些文件的信息。我需要创建* .ngc和* .xco文件,然后将它们重新

2018-10-08 11:11:22

如何导出网表

用OrCAD画好原理图后我们需要导出网表便于后续导入Allego画PCB(AD这点不同,可直接生成PCB文件)。Tools-Create Netlist,出现以下界面:点击确定即可生成第一方网表。选择Other项:

2022-02-15 07:33:39

将输入端口命名为AD_GPIO_in生成网表始终存在错误

我的EDK为9.1i,在为AD添加GPIO之后,尝试将输入端口命名为AD_GPIO_in,然后生成网表,但始终存在错误:错误:MDT-INST:AD端口:GPIO_in连接器

2018-09-28 16:56:06

快点PCB原创∣简述PCB设计中第三方网表的导入

一.第三方网表的导出 点击后(生成的netlist就是第三方网表,第三方网表的格式有.txt .tel等多种格式,但都能用记事本打开) 点击保存,得到netlist.txt文档,即第三方网表二

2016-09-14 10:32:32

怎么避免在Synplify中生成DSP48模块

有没有人知道在使用Synplify生成edif网表时如何将LUT用于多路复用器而不是DSP48模块?谢谢。以上来自于谷歌翻译以下为原文Does anybody know how can I use

2018-10-15 11:46:22

急!!!orcad生成网表时无法正常退出

各位大侠,我在用orcad生成网表时,软件无法正常退出,但其实网表文件已经生成了,这个怎么解决?谢谢本来一直没有理会这个问题,直接那生成的网表去布局布线,但现在需要back annonate,这个步骤只能在网表正常生成后做,所以需要急需解决这个问题。

2011-12-18 11:14:55

新手求助:生成网表文件时出现错误 ,谢谢

请问在生成网表文件时出现错误 Port has a type which is inconsistent with other ports on the net USART_RX SCHEMATIC1, STM3210E-MCU(2.60, 2.90)是怎么回事啊?我该怎样修改,谢谢!

2013-01-07 11:02:15

用PADS生成网表时出现的问题

用PADS生成网表时出现的问题,求高手解答,谢谢。PCB Net List Errors Report - FIRST.sch - Sat Feb 11 19:51:39

2012-02-11 20:08:33

简述PCB设计中第三方网表的导入

一.第三方网表的导出 点击后(生成的netlist就是第三方网表,第三方网表的格式有.txt .tel等多种格式,但都能用记事本打开) 点击保存,得到netlist.txt文档,即第三方网表二

2016-09-16 16:16:58

请问如何在allegro中导入orcad 生成的网表?

请问如何在allegro中导入orcad 生成的网表?谁知道详细的步骤,如何把DSN导成NETLIST的形式呢?请高手帮帮呀。。

2011-09-29 22:34:58

请问版主:POWERLOGIC如何从原理图更新PCB

请问版主:POWERLOGIC如何从原理图更新PCB?在画PCB过程中,发现原理图有的地方错了,如果重新导入网络表,那前期工作就白费了,又要重新做,能不能从原理图更新PCB呢?PROTEL99SE有这个功能啊,不知POWERPCB有无此功能?怎么做?

2008-11-04 22:19:19

APD不需重新Import Netlist 要如何直接修改Netname

APD不需重新Import Netlist,要如何直接修改Netname

1. 前言

一般APD设计檔的Netlist都是3rd-Party格式,而不是來自于schematic (OrCAD capture, ConceptHDL等)的输出netlist,因此若

2009-09-06 11:10:29 0

0

0

0PowerLogic 教程

欢迎使用 PowerLogic 教程。本教程描述了 PADS-PowerLogic 的各种功能和特点、以及使用方法。这些功能包括:· 如何在 PowerLogic 中使用工作区(Working Area)。· 如何在 PADS 的元件库

2010-08-12 17:37:36 0

0

0

0如何使用PowerLogic的OLE功能

如何使用PowerLogic的OLE功能

PowerLogic 现在使用先进的目标连接与嵌入(OLE) (Object Linking andEmbedding)技术,它可以在Windows 95和Windows NT 之类的

2008-03-12 12:42:44 1944

1944

1944

1944

PCB设计及Powerlogic入门基础

目录: 1、一步一步学用powerlogic/powerpcb(连载,建立元件) 2、SI 高速电路设计之第二章(传输线理论) 3、PCB 设计基础知识(trojan 提供) 4、本期特别文章一:PCB 设计指引 5、本期特

2011-04-11 10:20:16 0

0

0

0PCB设计流程你有没有了解

网表输入有两种方法,一种是使用PowerLogic的OLE PowerPCB Connection功能,选择Send Netlist,应用OLE功能,可以随时保持原理图和PCB图的一致,尽量减少出错的可能。

2019-12-13 17:34:22 1323

1323

1323

1323 电子发烧友App

电子发烧友App

评论