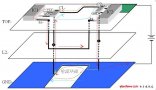

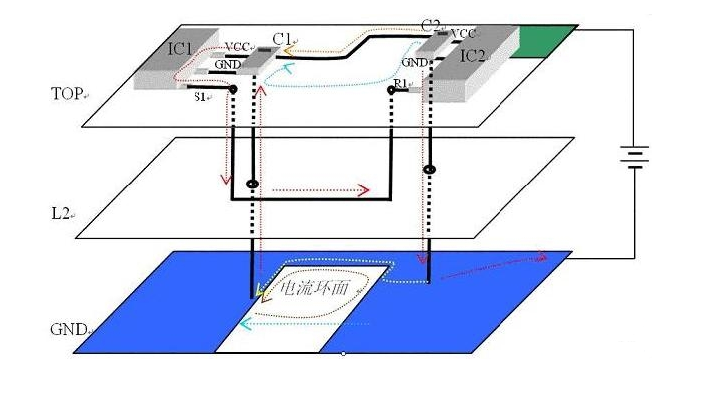

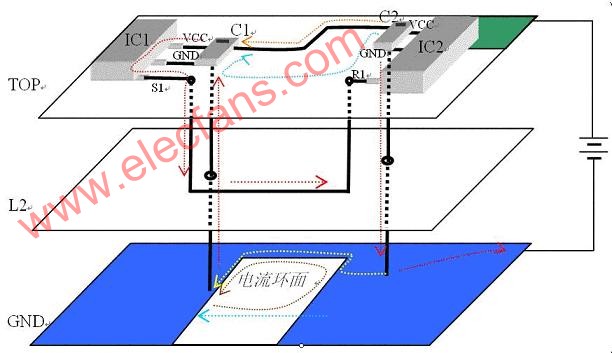

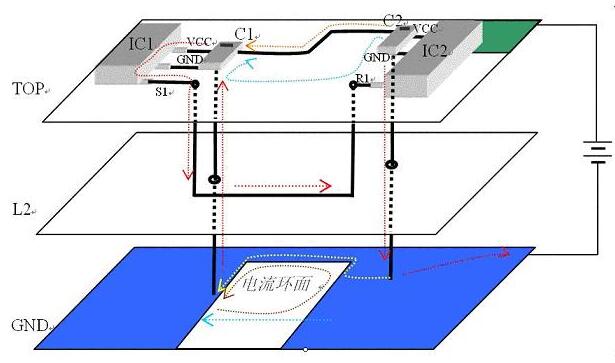

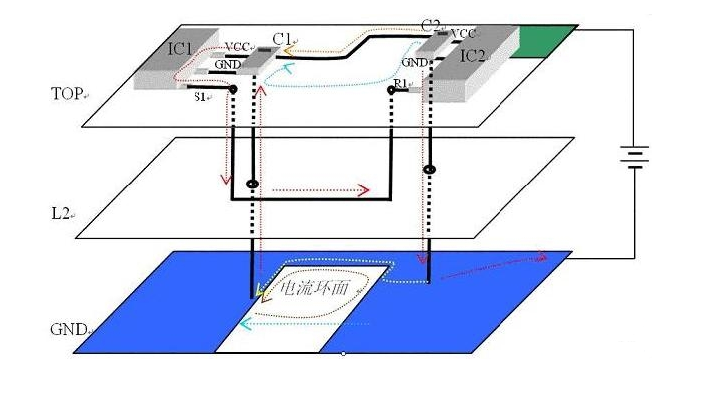

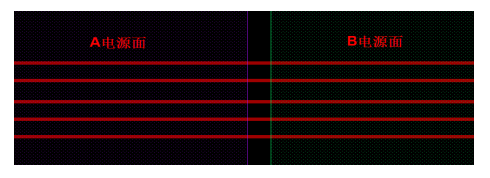

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。

2012-04-27 11:32:06 2376

2376

所有的高速信号必须有良好的回流路径,尽可能地保证时钟等高速信号的回流路径最小,否则会极大的增加辐射,并且辐射的大小和信号路径和回流路径所包围的面积成正比。

2019-04-03 09:30:51 6902

6902

当高速信号发生跨沟现象时,整个电流的环路面积将增加,通常系统的EMC辐射也将增加。同时传输线的特征阻抗也将发生变化(如下图2所示为信号线阻抗变化曲线),信号遇到传输线特征阻抗突变点时将发生发射、振铃等信号完整性问题。

2022-09-15 11:05:12 794

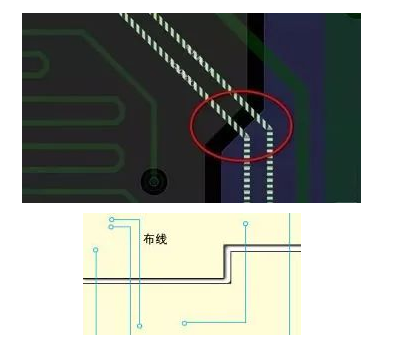

794 通常PCB上的打过孔换层会引起镜像平面的非连续性,这就会导致信号的最佳回流途径被破坏。

2023-01-10 10:19:31 1431

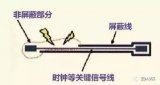

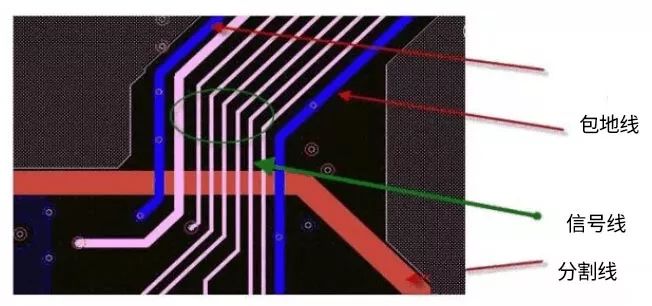

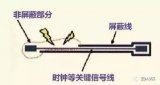

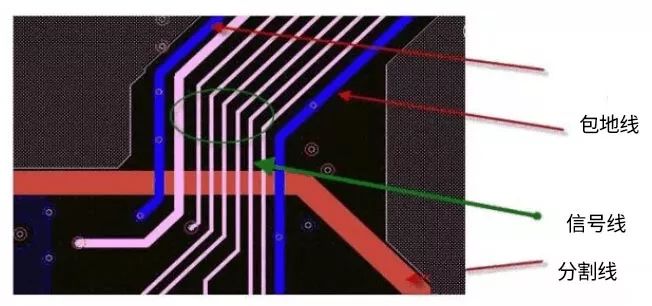

1431 规则一:高速信号走线屏蔽规则在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。图1 高速

2018-11-28 11:14:18

“长途跋涉”才能形成一个完整的回流通路,而这个通路也是相邻信号的回流通路,这个相同的回流通路和共地干扰的效果是一样的,等效为信号之间的串扰。对于一些无法避免的跨电源分割的情况,可以在跨分割的地方跨接

2020-10-23 11:30:00

轨线严禁跨分割走线,避免造成阻抗不连续,引起严重的信号完整性问题; 当 PCB 板上存在不相容电路时,应该进行分地的处理,但分地不应该造成高速信号线的跨分割走线,也尽量不要造成低速信号线的跨分割走线

2022-06-23 10:23:40

通过外接电缆产生共模辐射;加大与板上其它电路产生高频信号串扰的可能性(如下图)。三 PCB 设计对开槽的处理对开槽的处理应该遵循以下原则:需要严格的阻抗控制的高速信号线,其轨线严禁跨分割走线,避免造成

2020-12-17 09:49:40

在 PCB 设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考ᒣ面不连续,信号跨分割

2016-10-09 13:10:37

数字地、模拟地、信号地、交流地、直流地、屏蔽地、浮地基本概念及PCB地线分割的方法一、关于接地的知识普及:数字地、模拟地、信号地、交流地、直流地、屏蔽地、浮地转自:https

2022-01-26 08:05:09

平面分割对EMI的影响; *回流平面(路径)不分割。 2.5布线 *阻抗控制:高速信号线会呈现传输线的特性,需要进行阻抗控制,以避免信号的反射、过冲和振铃,降低EMI辐射。 *将信号进行分类,按照

2011-11-09 20:22:16

干扰源与敏感系统尽可能分离,减小耦合。●严格控制时钟信号(特别是高速时钟信号)的走线长度、过孔数、跨分割区、端接、布线层、回流路径等。●信号环路,即信号流出至信号流入形成的回路,是PCB设计中EMI

2019-04-27 06:30:00

PCB板的跨分割设计,不看肯定后悔

2021-04-23 06:17:14

PCB设计中跨分割的处理高速信号布线技巧

2021-02-19 06:27:15

/segments over voids,检查跨分割。2. 关键信号, JTAG信号的走线拓扑满足仿真报告中的要求,• JTAG信号 一般由5根测试信号,分别为:TCK、TDI、TDO,TMS

2017-11-03 09:41:25

轨线严禁跨分割走线,避免造成阻抗不连续,引起严重的信号完整性问题; 当 PCB 板上存在不相容电路时,应该进行分地的处理,但分地不应该造成高速信号线的跨分割走线,也尽量不要造成低速信号线的跨分割走线

2022-05-02 22:59:41

。尽管这种方法可行,但是存在很多潜在的问题,在复杂的大型系统中问题尤其突出。最关键的问题是不能跨越分割间隙布线,一旦跨越了分割间隙布线,电磁辐射和信号串扰都会急剧增加。在PCB设计中最常见的问题就是

2014-11-19 11:50:13

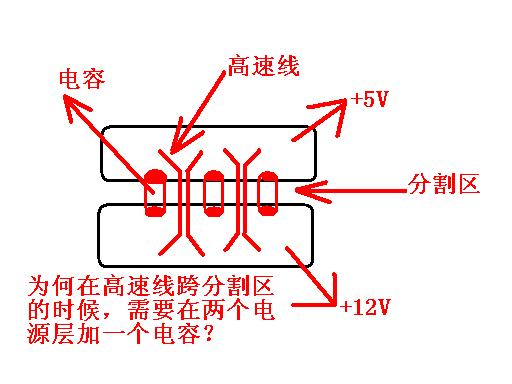

的跨电源分割的情况,可以在跨分割的地方跨接电容或RC串联构成的高通滤波器(如10欧电阻串680p电容,具体的值要依自己的信号类型而定,即要提供高频回流通路,又要隔离相互平面间的低频串扰)。这样可能会

2021-11-27 07:00:00

01 基本概念 (1)简单来说,传输线就是提供信号传输和回流的一组导体结构。常见的传输线有双绞线,同轴线,PCB走线中的微带线、带状线、共面波导,如图1所示结构示意图。 图1 常见传输线

2023-03-07 15:57:14

面的分割问题。 #混合信号PCB设计是一个复杂的过程,设计过程要注意以下几点:1.将PCB分区为独立的模拟部分和数字部分。 2.合适的元器件布局。 3.A/D转换器跨分区放置。 4.不要对地进行分割。在

2009-03-25 11:42:39

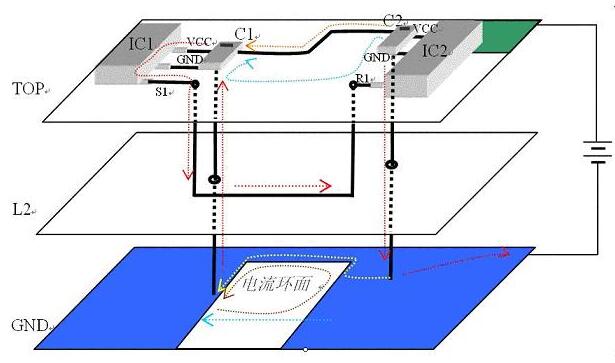

`高速PCB中的信号回流及跨分割这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。 IC1为信号输出端,IC2为信号输入端(为简化PCB模型

2013-10-24 11:12:40

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。 IC1为信号输出端,IC2为信号输入端(为简化PCB模型,假定接收端内含

2018-11-22 15:58:42

工欲善其事必先利其器,在学习PCB设计必须先了解各种要求,只有学习了才能画出设计需求的效果 废话不多说后续将陆续上传相关资料。后面我们在逐步学习 Altium Designer pads cadence等相关设计软件

2016-07-14 14:54:16

高速PCB中的地回流和电源回流以及跨分割问题分析

2021-04-25 07:47:31

设计,一些心得和大家交流、交流。规则一、高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线

2021-03-31 06:00:00

通过高速PCB来控制解决。做了4年的EMI设计,一些心得和大家交流、交流。规则一、高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只

2022-04-18 15:22:08

同,尤其是在高速系统中,信号的频率越高,与数字信号跳变相关的操作所产生的RF能量的频带也越宽,要防止工作频带不同的器件间的相互干扰,尤其是高带宽器件对其他设备的干扰。 解决上述问题的办法是采用

2018-11-27 15:21:34

解决高速PCB设计中的相互干扰问题。 我们知道,在多层PCB中高频信号的回流路径应该在该信号线层临近的参考地平面(电源层或者地层)上,这样的回流和阻抗最小,但是实际的地层或电源层中会有分割和镂空,从而

2018-09-10 16:37:21

行折中,精度相对较高的,需要的计算时间很长,而仿真速度快的工具,其精度又很低。因此用这些工具进行仿真,不能完全解决高速PCB设计中的相互干扰问题。 我们知道,在多层PCB中高频信号的回流路径应该在该

2013-10-28 14:39:24

高速设计已成为愈来愈多 PCB 设计人员关切的重点。在进行高速 PCB 设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性

2021-02-05 07:00:00

和互连工具可以帮助设计师解决部分难题,但高速PCB设计也更需要经验的不断积累及业界间的深入交流。 >>焊盘对高速信号的影响 在PCB中,从设计的角度来看,一个过孔主要由两部分组成:中间

2012-10-17 15:59:48

本期讲解PCB设计中高速信号关键信号的布线要求。一、时钟信号布线要求在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。时钟电路在数字电路中点有重要地位,同时又是产生

2017-10-19 14:25:36

抗干扰能力。35、关键信号走线一定不能跨分割区走线(包括过孔、焊盘导致的参考平面间隙)。原因:跨分割区走线会导致信号回路面积的增大。36、信号线跨其回流平面分割地情况不可避免时,建议在信号跨分割附近采用桥

2014-12-25 10:19:32

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地

2016-01-19 22:50:31

高速信号PCB布线中降低寄生电感的具体措施

2021-03-08 08:49:46

高速信号回流环路实际分析

2021-01-22 06:36:47

高速信号的电源完整性分析在电路设计中,设计好一个高质量的高速PCB板,应该从信号完整性(SI——Signal Integrity)和电源完整性 (PI——Power Integrity )两个方面来

2012-08-02 22:18:58

影响高速信号链设计性能的机制是什么?高速ADC设计中的PCB布局布线技巧有哪些?

2021-04-21 06:29:52

SerDes应用的PCB设计要点– reference2:差分信号的回流路径问题讨论– video如何应对未来高密SerDes设计的挑战高速PCB layout设计应考虑的点:PCB mate...

2021-11-12 06:46:26

电流总是在环路中流动,电路中任意的信号都以一个闭合回路的形式存在。对于高频信号传输,实际上是对传输线与直流层之间包夹的介质电容充电的过程。2.回流的影响数字电路通常借助于地和电源平面来完成回流。高频信号

2021-08-04 06:30:00

高速电路设计学习 一、PCB设计时高速信号和低速信号区分 在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高

2020-12-21 09:23:34

请问大家,所谓的“跨分割平面走线”,这个“分割平面”,是指“被分割的地平面”,还是“被分割的电源平面”,或是统指“被分割的地平面和电源平面”??谢谢

2010-07-06 13:26:39

®PCBDesigner 中 IDA(In-DesignAnalysis,设计同步分析)的 ReturnPath 分析功能,在 PCB 设计过程中进行回流路径分析,帮助工程师快速找出那些高速信号的回流路径

2020-12-07 09:24:05

电流总是在环路中流动,电路中任意的信号都以一个闭合回路的形式存在。对于高频信号传输,实际上是对传输线与直流层之间包夹的介质电容充电的过程。 2回流的影响 数字电路通常借助于地和电源平面来完成回流

2020-08-01 17:30:00

、时钟信号、I/O信号、总线、电源等)的EMI辐射强度及敏感程度,使干扰源与敏感系统尽可能分离,减小耦合。 *严格控制时钟信号(特别是高速时钟信号)的走线长度、过孔数、跨分割区、端接、布线层、回流路径等

2019-09-16 22:37:29

本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。误区一:GHz 速率以上的信号才算高速信号? 提到“高速信号”,就需要先明确什么是“高速”,MHz 速率级别的信号算高速

2022-04-28 16:21:41

互为回流路径,跨平面分割不会割断信号的回流,但是跨平面分割分的传输线会因为缺少参考平面而导致阻抗不连续。(8)接收端的匹配电阻要尽量靠近接收引脚,距离要尽量短,接线距离也要尽可能的短。(9)控制匹配

2017-07-18 10:57:28

:边缘间距大于或等于2倍的线宽Display/segments over voids,检查跨分割。2. 关键信号, JTAG信号的走线拓扑满足仿真报告中的要求,• JTAG信号 一般由5根测试信号,分别为

2017-11-01 17:06:26

络,PCB中主要表现为地线噪声和电源噪声.辐射干扰是指信号以电磁波的形式辐射出去,从而影响到另一个电网络.在高速PCB及系统设计中,高频信号线、芯片的引脚、接插件等都可能成为具有天线特性的辐射干扰源

2018-11-22 16:03:30

络,PCB中主要表现为地线噪声和电源噪声。辐射干扰是指信号以电磁波的形式辐射出去,从而影响到另一个电网络。在高速PCB及系统设计中,高频信号线、芯片的引脚、接插件等都可能成为具有天线特性的辐射干扰源

2018-09-12 15:16:15

解决高速PCB设计信号问题的全新方法

2021-04-25 07:56:35

电路系统的设计中,在布局模块化、布线局部化的基础上,数字电路模块和模拟电路模块公用一个完整的、不加分割的电压参考平面,不但不会增大数字电路对模拟电路的干扰,由于消除了信号线“跨沟”问题,能够大幅度降低信号

2020-04-13 08:00:00

,必须识别高速通道中的这些不连续,并提供减轻其影响的方法,以实现更好的信号传输。其中,元器件封装焊盘,连接器和信号打孔换层都会会造成阻抗不连续及回流路径的变化,这时需要为信号的过孔提供额外的接地过孔为其

2023-04-18 14:52:28

小于1/20波长。 3 、电容和接地过孔对回流的作用高速PCB设计中对于EMI的抑制是非常灵活的,设计者永远不可能很完美地解决所有的EMI问题,只有从小处着手,从对各个细节的把握来达到整体抑制的效果

2019-05-20 08:30:00

)的走线长度、过孔数、跨分割区、端接、布线层、回流路径等。 ●信号环路,即信号流出至信号流入形成的回路,是PCB设计中EMI控制的关键,在布线时必须加以控制。要了解每一关键信号的流向,对于关键信号要靠

2018-09-14 16:32:58

与敏感系统尽可能分离,减小耦合。* 严格控制时钟信号(特别是高速时钟信号)的走线长度、过孔数、跨分割区、端接、布线层、回流路径等。* 信号环路,即信号流出至信号流入形成的回路,是PCB 设计中EMI

2017-08-09 15:09:57

关于模拟数字地分割的问题,还是有些不太明白,想请高手们再指教下。以前我画板子,数字地和模拟地是分开的,然后通过电阻连接。但是这样又有人说不可取,因为两块地隔开后如果有跨分割的走线,那么这条线的回流

2019-04-23 00:42:05

对于高速信号,pcb的设计要求会更多,因为高速信号很容易收到其他外在因素的干扰,导致实际设计出来的东西和原本预期的效果相差很多。 所以在高速信号pcb设计中,需要提前考虑好整体的布局布线,良好

2023-04-12 14:22:25

最近要搞告诉信号的东西,但是从来没有布过高速信号的PCB,求大神指教

2013-08-30 14:10:03

将 PCB 分区为独立的仿真部分和数字部分。 合适的元器件布局。 A/D 转换器跨分区放置。 不要对地进行分割。在电路板的仿真部分和数字部分下面敷设统一地。 在电路板的所有层中,数字信号只能

2011-10-16 10:50:12

高速PCB设计过孔有哪些注意事项?如何降低数字信号和模拟信号间的相互干扰呢?分割地的方法还有用吗?

2021-04-25 06:12:22

问题。 #混合信号PCB设计是一个复杂的过程,设计过程要注意以下几点: 1.将PCB分区为独立的模拟部分和数字部分。 2.合适的元器件布局。 3.A/D转换器跨分区放置。 4.不要对地进行分割。在电路板

2018-08-31 11:53:54

︰ 将 PCB 分区为独立的仿真部分和数字部分。 合适的元器件布局。 A/D 转换器跨分区放置。 不要对地进行分割。在电路板的仿真部分和数字部分下面敷设统一地。 在电路板的所有层中

2012-10-17 15:49:38

成正比)。在设计中要尽可能避免这两种情况。 有人建议将混合信号电路板上的数字地和模拟地分割开,这样能实现数字地和模拟地之间的隔离。尽管这种方法可行,但是存在很多潜在的问题,在复杂的大型系统中问题尤其突出

2018-08-28 15:28:43

成正比)。在设计中要尽可能避免这两种情况。 有人建议将混合信号电路板上的数字地和模拟地分割开,这样能实现数字地和模拟地之间的隔离。尽管这种方法可行,但是存在很多潜在的问题,在复杂的大型系统中问题尤其突出

2015-01-14 14:27:34

,回流的路径必须是完整的,也就要求了信号不能跨分割,否则会引起很大的辐射和串扰。另外,回流平面也不一定总是地,和你的板子元件布局还有信号类型有关。 b)从抑制高频

2008-07-14 16:27:56

高速信号线 规则二:高速信号的走线闭环规则 由于板的密度越来越高,很多 LAYOUT工程师在走线的过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果

2018-09-20 10:38:01

的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。规则二:高速信号的走线闭环规则由于PCB板的密度越来越高

2017-11-02 12:11:12

如果信号线必须跨电源或地平面分割的话,则需要桥接电容。那么桥接电容的位置是否要靠近信号线,为什么?有没有理论根据?

2009-02-10 16:48:50

本文主要分析一下在高速 PCB 设计中,高速信号与高速 PCB 设计存在一些理解误区。误区一:GHz 速率以上的信号才算高速信号?提到“高速信号”,就需要先明确什么是“高速”,MHz 速率级别的信号

2020-11-30 09:51:58

高速信号号在电源层分割时的处理办法

2007-11-08 09:13:59 3681

3681

高速PCB中的信号回流及跨分割

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便

2009-11-17 08:56:03 1053

1053 在高速电路中经常会遇到跨分割设计,在2017年的时候也写过一篇跨分割设计的文章。

今天给大家分享一篇跨分割设计对信号的影响。

2018-01-23 15:49:53 7590

7590

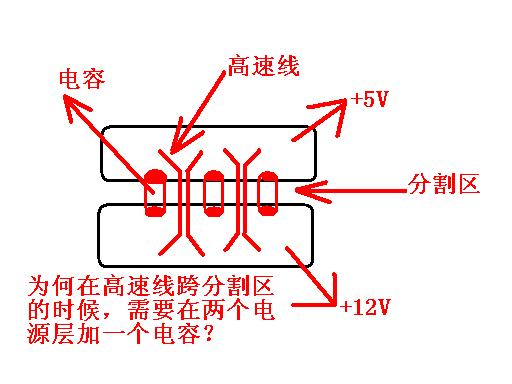

IC1为信号输出端,IC2为信号输入端(为简化PCB模型,假定接收端内含下接电阻)第三层为地层。IC1和IC2的地均来自于第三层地层面。顶层右上角为一块电源平面,接到电源正极。C1和C2分别为IC1、IC2的退耦电容。图上所示的芯片的电源和地脚均为发、收信号端的供电电源和地。

2019-06-14 15:25:06 4827

4827

数字电路通常借助于地和电源平面来完成回流。高频信号和低频信号的回流通路是不相同的,低频信号回流选择阻抗最低路径,高频信号回流选择感抗最低的路径。

2020-04-13 17:37:15 3709

3709

但在高频时,PCB所呈现的分布特性会对信号产生很大影响。

2020-03-28 11:06:57 1158

1158 本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。 误区一:GHz速率以上的信号才算高速信号? 提到高速信号,就需要先明确什么是高速,MHz速率级别的信号算高速、还是

2019-11-05 11:27:17 10310

10310

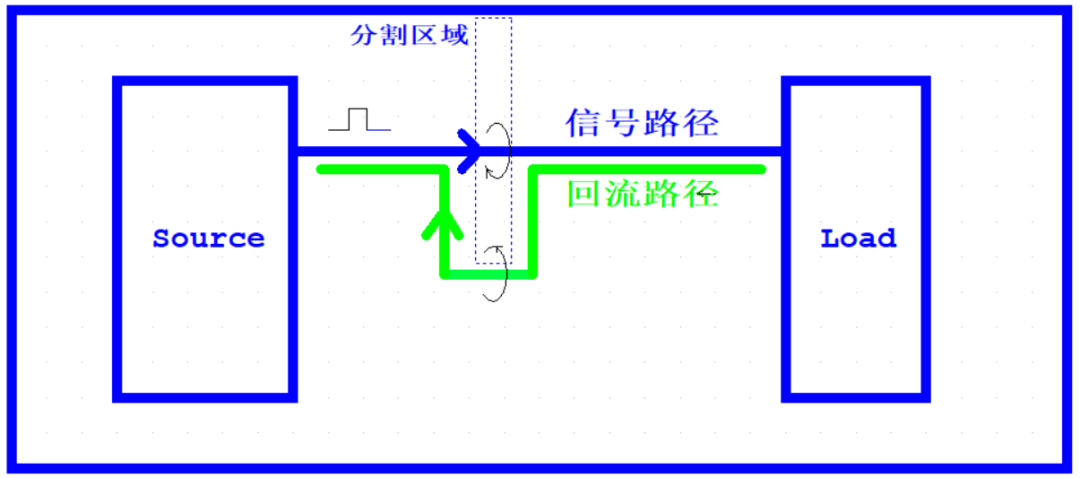

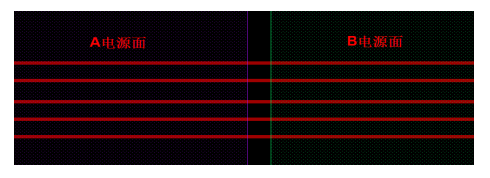

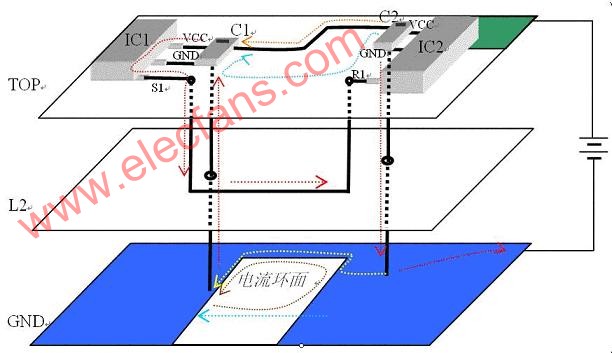

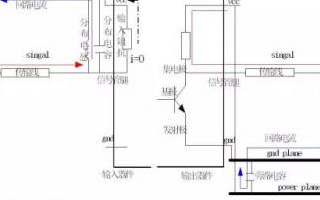

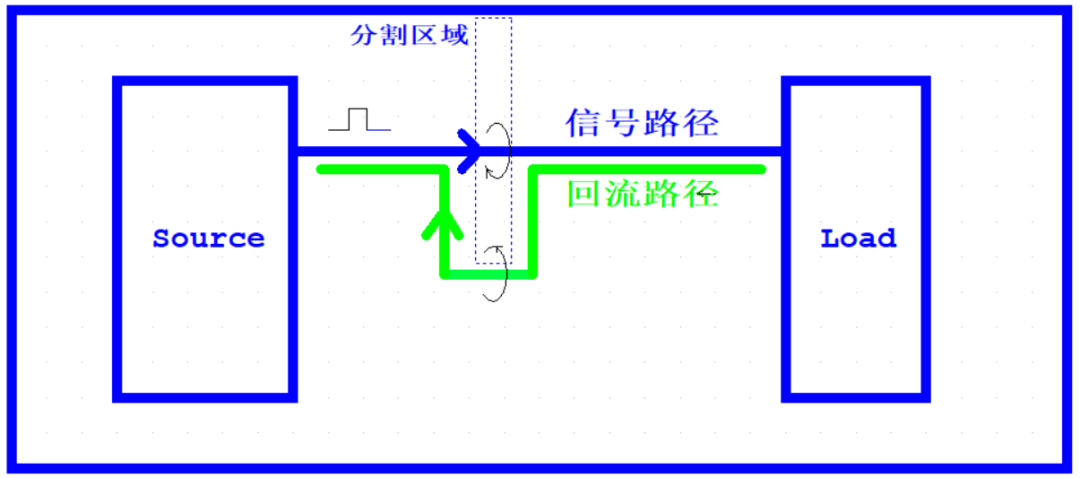

跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响。

2020-03-08 11:26:00 5162

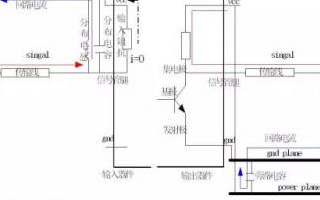

5162 在PCB设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考?面不连续,信号跨分割,这就会带来诸多的问题,如EMI、串扰等问题。

2020-03-11 15:00:24 1908

1908 在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。

2020-09-02 11:06:40 6745

6745

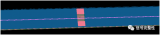

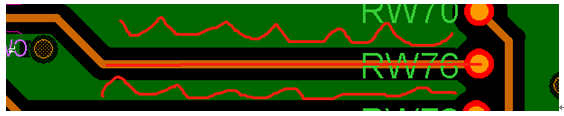

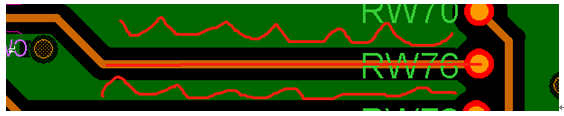

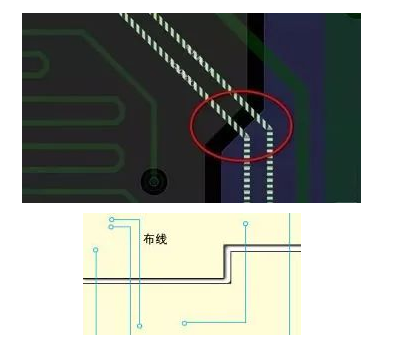

1、实际走线分析:

上面的走线橘色为信号走线,周围绿色(波浪标注)为周围包地,下方为第二层完整地平面。

从上图来看设计师的本意是好的,有参考地平面,周围也有包地,此时设计正确的话可以保证回流

2022-02-10 09:43:35 2338

2338

1、实际走线分析:

上面的走线橘色为信号走线,周围绿色(波浪标注)为周围包地,下方为第二层完整地平面。

从上图来看设计师的本意是好的,有参考地平面,周围也有包地,此时设计正确的话可以保证回流路径

2021-02-24 06:51:51 4

4 PCB工程师注意啦:通常pcb上的打过孔换层会引起镜像平面的非连续性,这就会导致信号的最佳回流途径被破坏。 我们都知道,信号打孔换层会改变信号的回流路径,如果信号换层,回流路径也跟着换层,但是在信号

2021-05-29 14:32:12 5967

5967

SerDes应用的PCB设计要点– reference2:差分信号的回流路径问题讨论– video如何应对未来高密SerDes设计的挑战高速PCB layout设计应考虑的点:PCB mate...

2021-11-07 10:21:00 47

47 通常PCB上的打过孔换层会引起镜像平面的非连续性,这就会导致信号的最佳回流途径被破坏。 我们都知道,信号打孔换层会改变信号的回流路径,如果信号换层,回流路径也跟着换层,但是在信号换层处过孔不能将信号回路连通起来,将引起信号回路面积增大,从而导致EMC问题。

2022-12-20 09:59:30 2864

2864 跨分割,对于低速信号可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。

2023-02-21 13:44:36 1168

1168 PCB高速信号在当今的一个pcb设计中显然已成为主流,一名优秀的PCB工程师,除了在实战项目慢慢积累设计PCB高速信号的经验外,还需通过不断学习来提升自己的知识储存和专业技能。本文捷多邦小编就给大家科普一下PCB高速信号的一些相关布线知识。

2023-09-15 10:19:18 720

720 高频下信号会镜像回流,但是由于有分割,导致信号不能镜像回流。信号回流绕过分割区域形成大的环路,环形天线效应使差模辐射增加。

2023-10-01 17:33:00 307

307

在低频时,如果S1端输出高电平,整个电流回路是电源经导线接到VCC电源平面,然后经橙色路径进入IC1,然后从S1端出来,沿第二层的导线经R1端进入IC2,然后进入GND层,经红色路径回到电源负极。

2023-10-16 15:18:36 298

298

可以很好的决定布线的走向和结构,电源与地之间的分割,以及电磁干扰和噪声的控制。 不过在理解高速PCB设计前,需要知道什么是高速信号。 一般如果符合以下几点,那它就可以被认为是高速信号(cadence公司做的定义): (1)频率大于

2023-11-06 10:04:04 340

340

,对正常的信号传输和系统性能产生不良影响。 信号回流路径是一个普遍存在的问题,尤其在高速电子设备中更为突出。信号的回流可能是因为传输线路或布线不良造成的,也可能是由于高频器件之间存在不良的反射或耦合引起的。它会

2023-11-24 14:44:50 615

615 ,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。 跨分割现象示意图 跨分割,对于低速信号可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时

2023-12-04 10:26:34 288

288

电源回流是PCB设计中的一个重要问题,特别是在高速电路设计中尤为重要。为了确保电源回流的良好表现,设计师需要采取一系列的方法和策略。本文将通过详尽、详实、细致的方式,介绍PCB电源回流的方法。 首先

2023-12-20 15:57:56 453

453 我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。

2024-01-03 15:12:19 272

272

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。

2024-01-10 15:28:13 222

222

电子发烧友App

电子发烧友App

评论