allegro多重规则套用方法(Multi-Group Ne

- PCB设计(82997)

- Neste(7764)

- 可制造性设计(15288)

- 华秋DFM(3866)

相关推荐

PROTEL转ALLEGRO的方法

PROTEL转ALLEGRO的方法

随着PCB设计的复杂程度和高速PCB设计需求的不断增加,越来越多的PCB设计者、设计团队选择Cadence的设计平台和工具。但是,由于没有P

2008-03-22 16:11:26 5010

5010

5010

5010Allegro布线规则的设置

PCB布线经常会要求对重要的信号线进行规则的设置。布线规则的设置通常包括线宽和线距两大部分。下面就以一主板Layout guide

2010-06-21 08:48:22 10808

10808

10808

10808

***中不规则敷铜方法

我用DXP中Solid Region 来进行不规则敷铜,其实是为了连接导线,因为这几个器件引脚在一块,用导线的话不方便。布线后的效果如下图所示。红色区域是用Solid Region来敷铜,红线是DXP中的导线。请问怎么将这两个区域连接在一起呢?一般不规则导线连接用什么方法呢?谢谢~

2014-03-02 22:17:39

ALLEGRO PCB SI GXL

ALLEGRO PCB SI GXLALLEGRO PCB SI GXLCadence Allegro PCB SI GXL provides a virtual prototyping

2008-10-16 09:32:28

ALLEGRO转PADS

以前一直用pads layout,allegro刚学,用的很不习惯。看到网上说allegro可以转成pads(allegro---cam350---pads)或者别的方法?一直转不成功,有没有详细点操作步骤,哪种方法转换最好呢?

2014-11-19 10:33:09

Allegro Out Of Date Shapes原因及解决方法

Allegro Out Of Date Shapes原因及解决方法使用Allegro设计PCB板时,查看Status,经常会遇到out of date shapes的警告信息,具体如下

2014-11-12 17:53:48

Allegro16.3与15.5相互切换的方法

给大家分享一个两个版本不能切换的方法,Win7&XP都适用!!!!1、win7下请右键-管理员身份运行2、路径为个人电脑路径,请修改为本机的路径!!!3、运行后会自动打开Allegro

2011-10-18 16:35:10

Allegro怎么放置后台元器件 PCB图文教程

Allegro怎么放置后台元器件 PCB图文教程答:导入网表成功以后,我们需要在Allegro软件中将后台的元器件放置出来,放置出来的方法有如下几种:Ø 快速放置法,点击

2019-08-26 14:27:57

Allegro技术如何助力EDA360目标的实现

手动方式进行布局与布线,但这种方式很容易出错,需要反复重来,也没有设计规则检查。Allegro技术可以通过约束驱动式方法,用一种更简单的方式对这些元件进行布局与布线。全新Allegro Power

2020-07-06 17:50:50

Allegro文件转成PADS文档的方法

需要将两种软件格式的PCB和原理图相互转换。下面是将Cadence Allegro的PCB文件转化为PADS的PCB文件的方法介绍如下:方法/步骤:1、将PADS 安装目录

2019-09-17 09:05:03

Allegro极坐标布局方法

allegro极坐标布局方法!记得多余时间来撩我!!!好了废话不多说了,开始!!!首先,将网标导入PCB中(封装记得都做对)然后,快速放入器件紧接着,画一个圆形,并选择一个要放在圆上器件放好(使用坐标法);又来

2019-12-31 00:01:06

allegro布线出现一截一截线段的解决办法?

有很多网友都问过:关于设计软件allegro出现一截一截的线段,出现小方框的这个问题,移动线非常不方便。 问题描述如图: 很多群友提出了自己的解决办法: 第一种方法删除重新走一遍,当然

2020-09-02 17:46:41

allegro转pads的方法(使用allegro 16.3和pads9.3.1)

:1、这个转换只支持到allegro 16.3版本,如果你的版本比较高,16.5或是16.6,貌似是有问题的,我没具体试过,可以考虑再安装个16.3版本的,或是使用虚拟机;2、以上方法是在mentor

2014-11-06 13:50:07

Altium“unplated multi-layer pad(s) detected”报错解决方法

(multi-pad ),并且这两个multi-pad 分别与管脚1(USB_IN)和5(GND)相连,而电气规则设置默认不允许无沉铜通孔。解决方法:1.如果这两个multi-pad是有网络连接的,应该都是金属化(镀铜) ,即应该对其勾选plated:(图文详解见附件)

2019-11-02 11:00:31

Altium的pcb文件转allegro的方法

AD的pcb设计文件并不能直接转换成allegro的pcb板,常用的方法是AD→PADS→Allegro;所以AD转allegro的步骤如下:一、将AD文件转为PADS文件;(PADS9.5以上版本

2019-09-03 17:02:30

CADENCE ALLEGRO内层平面切割方法

CADENCE ALLEGRO内层平面切割方法在4层或4层以上的PCB设计中,我们一般都会设置2层或2层以上的Plane,例如以一个4层板为例,最常见的叠层是TOP-GND-VCC-BOTTOM

2009-12-04 10:14:49

Cadence 17.4支持约束规则的双向设置及同步

的链接更加紧密,提高规则设计的效率,并督导工程师及时纠正这些设计错误和存在的问题,为电路的原理图设计打下坚实基础。接下来将重点讲述OrCAD Capture和Allegro的规则设置方法及同步技巧,一起

2020-07-06 15:00:43

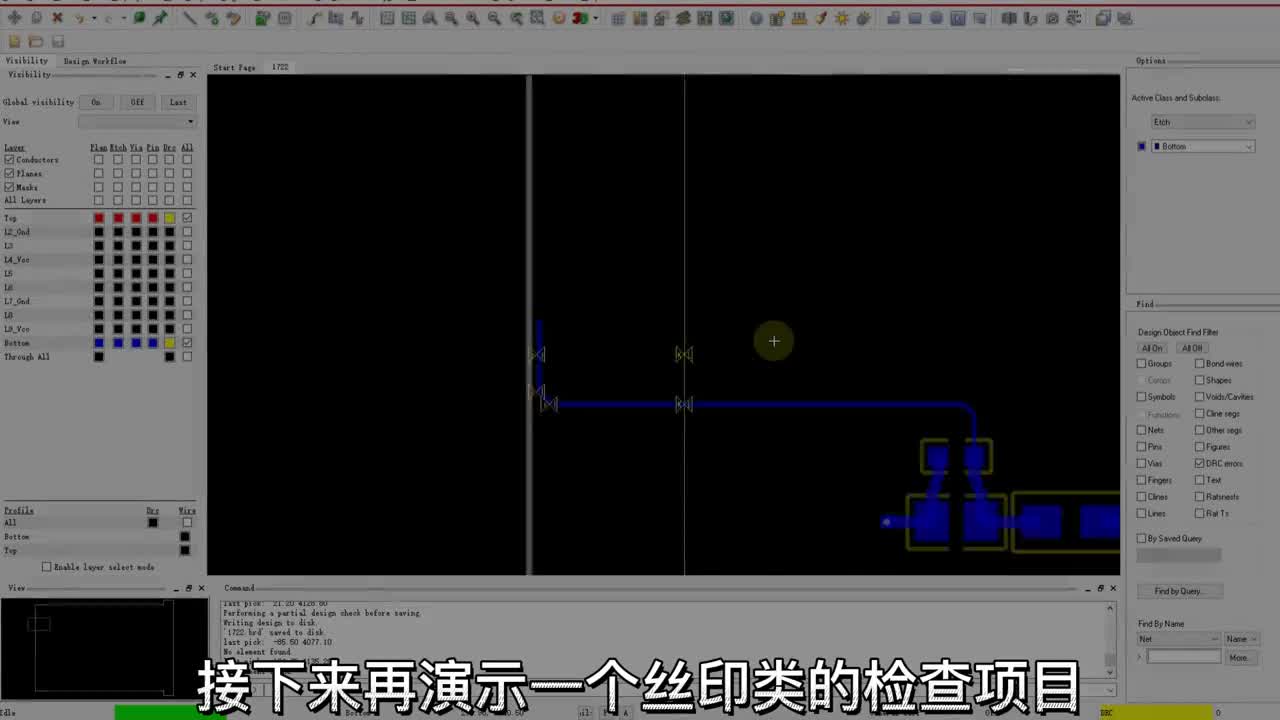

PCB设计软件allegro16.6演示区域规则的设置

的特殊线宽、线距要求在某些区域中又不适于使用,这就需要进行区域规则的设置。首先,同样需要打开allegro16.6菜单栏选择setup->constraints->constraint

2016-12-28 10:45:56

PCB设计软件操作之两种建立Match Group的方法

`上一期我们介绍了主流PCB设计软件allegro区域规则的设置不知道我们可爱的攻诚师们学会了木有如果没有学会没有关系板儿妹本期继续给大家介绍两种建立Match Group的方法方法一:如下图所示图

2016-12-30 11:20:27

PCB设计软件操作之两种建立Match Group的方法

建立Match Group的方法方法一:如下图所示图1-1创建Match Group然后输入Match Group组名图1-2Match Group命名方法二:是通过先建立电气规则,然后赋予给相关网络

2016-12-30 11:13:50

Pads文件转换Allegro PCB后封装如何按PAD大小规则的重命名

Pads文件转换Allegro PCB后封装如何按PAD大小规则的重命名,避免设计出错。 封装PAD名字规则重命名 1、导出整板PCB封装到一个新的lib文件路径 2、任意打开一个封装,可以看出PAD

2023-03-31 15:19:17

Protel到Allegro转化的方法

CCT的转换工具来完成这一工作。对于第二种情况,要做的工作相对复杂一些,下面将这种转化的方法作一简单的介绍。 Cadence信噪分析工具的分析对象是Cadence Allegro的brd文件,而

2014-12-03 15:23:18

Python多重继承使用方法

语法的含义是创建了一个subClass类,让它同时继承了Base1和Base2的相关特性,关于继承还有以下规则需要遵循:1. 继承只会继承父类的方法,不能继承父类的变量;2. 要想继承父类的变量,需要

2018-04-19 14:41:27

【设计技巧】allegro PCB设计使用技巧

后会发现Color and Visibility 视窗过长不好关掉其视窗,这时有两个方法可解决.1) 关掉 Allegro程式然后删掉pcbenv路径下的allegro.geo,再进 Allegro

2019-07-15 05:00:00

【转换】三种方法教你玩转 Allegro到Sigrity 的文件格式转换

本帖最后由 社区管家 于 2014-12-3 12:01 编辑

关于如何转换allegro/SIP的设计文件到Sgrity的spd文件,一般有以下三种方法:1.Brd/sip文件直接

2014-12-03 11:58:06

为什么在AD15中设置Room规则的方法有效在AD17中就无效了?

在AD15中设置Room规则的方法有效,为什么同样的方法在AD17 中规则就无效了呢,强哪位高手帮忙讲解一下在AD17 中Roomph规则该怎么设置

2019-07-31 03:00:54

使用NE556控制脉宽调制的方法

描述使用 NE556 控制脉宽调制使用这种类型的电路,您可以控制电机从 0 到 100%,保持转矩恒定。原则上在NE556电路的第一个非稳态信号400Hz 的频率适用于单稳态周期由电位器 R9 的值

2022-08-09 07:20:10

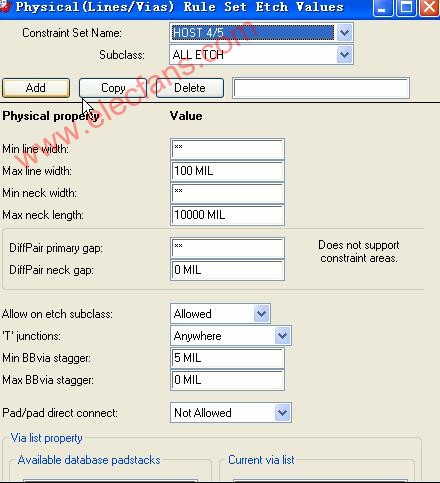

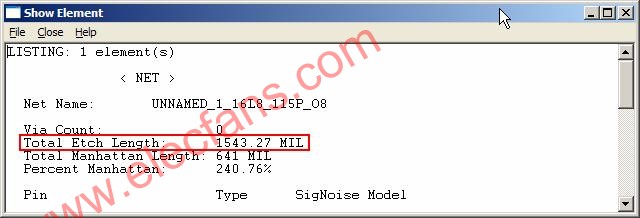

原创|高速PCB设计软件allegro中与网络有关的约束规则设置

在allegro pcb的设计过程中,设计约束规则包括时序规则、间距规则、信号完整性规则以及物理规则等,本期主要详细讲解与物理、间距与电气约束中的线宽、线间距物理规则的设置。一、线宽设置(1)设置

2016-12-23 17:08:25

在AT32微控制器上创建Multi MCU IAP应用程序的方法

对于大多数基于闪存的系统,一项重要要求是能够在最终产品中安装固件时进行更新。此功能称为应用程序内编程(IAP)。本应用笔记的目的是提供在AT32微控制器上创建Multi MCU IAP应用程序的方法

2023-10-24 06:48:06

实用技巧集锦:allegro 使用技巧(2)

dynamic shape)完成GND层覆铜7、相同的方法完成POWER层覆铜Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –>

2014-12-23 15:18:07

怎么把allegro的飞线设置成正常形式?

allegro的飞线是总线形式,怎么设置成正常的file:///C:\Users\Administrator\Documents\Tencent Files\1249658156\Image\Group\]~EPLL3DY)G9_@$K`{VU1VF.png

2019-09-06 05:35:46

没有与IODELAY GROUP关联的IDELAYCTRL

元素与IODELAY_GROUP'tri_mode_ethernet_mac_iodelay_grp'相关联,但没有与此IODELAY_GROUP关联的IDELAYCTRL。单独的示例设计运行良好但是

2018-10-25 15:26:50

高速PCB设计软件allegro16.6演示差分规则的设置

上一期我们介绍了高速PCB设计软件allegro16.6差分信号的设定在高速PCB布线前需要对差分信号的规则进行设置因此本期重点介绍在电气规则和物理规则下是如何建立差分信号的规则1、在电气规则下建立

2017-01-06 09:46:41

新西兰Group3高斯计

新西兰Group3 DTM-152高斯计产品特点:4量程操作(0.3T、0.6T、1.2T、3.0T)触摸屏界面网络通过局域网,可以使用LabView VI进行操作(提供)数据记录现场温度同步显示

2022-01-10 16:42:49

ALLEGRO PCB SI GXL

Cadence Allegro PCB SI GXL provides a virtual prototyping environment fordesigns with signals

2008-10-16 09:30:31 0

0

0

0ALLEGRO SYSTEM ARCHITECT GXL

ALLEGRO SYSTEM ARCHITECT GXLCadence Allegro System Architect GXL is the industry°Os first

2008-10-16 09:46:55 0

0

0

0一种防火墙规则配置异常分析方法

从集合角度描述防火墙过滤规则及规则之间存在的异常类型,给出规则间异常类型判定方法。指出直接使用判定方法分析防火墙规则集时所存在的问题,提出一种基于规则顺序敏感

2009-04-01 08:36:49 8

8

8

8基于改进PSO的规则提取方法

为解决飞行动作识别规则的自动提取问题,提出一种基于改进粒子群优化算法的飞行动作规则提取方法。在对关键飞行参数特征量进行符号化的基础上,利用基于改进的动态惯性权

2009-04-14 08:32:53 9

9

9

9PCB设计中20H规则的验证方法

PCB设计中20H规则的验证方法:随着电路工作频率的上升,PCB设计面临越来越多的电磁辐射问题。20H规则是减小电路板辐射的设计规则之一。

2009-09-26 08:30:43 0

0

0

0HDMI规则及方法

HDMI规则及方法

HDMI Licensing LLC目前授權兩家HDMI授權測試中心(ATC),其中一家位於日本大阪,由Matsushita Electric Industries經營,另一家則位於美國加州Sunnyvale,由晶

2010-03-06 10:40:42 27

27

27

27ALLEGRO生成钻孔文件的方法

ALLEGRO生成钻孔文件的方法

生成钻孔文件的步骤:ALLEGRO TO NC DRILL

1. Manufacture -> NC -> Drill Customization…

2008-03-22 15:45:26 8020

8020

8020

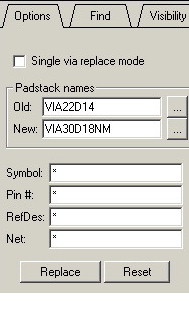

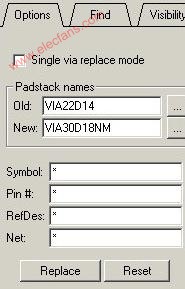

8020Allegro中如何修改VIA过孔的方法

Allegro中如何修改VIA过孔的方法

图 11.Tools => Padstack => Replace (

2008-03-22 16:21:31 13438

13438

13438

13438

Protel封装库转换到Allegro的方法及步骤

Protel封装库转换到Allegro的方法及步骤

长期使用 Protel作 PCB 设计,我们总会积累一个庞大的经过实践检验的 Protel 封装库,当设计平台转换时,如何

2009-04-15 00:14:19 5049

5049

5049

5049Protel到Allegro格式转换方法及步骤

Protel到Allegro格式转换方法及步骤

当今IT产业的发展日新月异,对硬件设备的要求也越来越高,硬件设计师们面临如何设计高速高

2009-04-15 00:35:47 775

775

775

775Cadence/allegro V16.0的安装方法

Cadence/allegro V16.0的安装方法

解压缩Cadence Spb 16.0 New Working Crack.rar这个eMule搜索一下有下的,不过里面的Nolic.Com我电脑NOD32报

2009-09-08 17:46:36 1140

1140

1140

1140Protel转换G到Allegro/CCT格式的转换方法

Protel转换G到Allegro/CCT格式的转换方法

由于接触和使用较早等原因,国内Prote用户为数众多,他们在选择Cadence

2009-11-01 16:45:36 717

717

717

717Protel转换至Allegro及CCT格式的简便方法

Protel转换至Allegro及CCT格式的简便方法

由于接触和使用较早等原因,国内Prote用户为数众多,他们在选择Cadence高速PCB解决方案

2009-11-18 08:36:27 763

763

763

763贴片电容的型号命名方法及规则简介

贴片电容的型号命名方法及规则简介

贴片电容命名规则及方法 贴片电容的命名:贴片电容的命名所包含的参数有贴片电容的尺寸、做这种贴片电容用的材质、

2009-11-26 08:58:27 8989

8989

8989

8989简易pcb软件allegro中手工封装技术

简易pcb软件allegro中手工封装技术

在电路改板设计中经常会遇到PCB软件allegro如何手工封装的问题,下面我们就来介绍PCB软件allegro中手工封装的简易方法:

2010-01-23 11:39:16 1452

1452

1452

1452Allegro同时旋转多个元器件的方法

Allegro同时旋转多个元器件的方法

下面的解决方案适用于,多个零件同时围绕一个点旋转,而不是围绕各自的一点旋转.

1.Edit->Move,在Options中Rotat

2010-03-21 18:07:43 8776

8776

8776

8776allegro pcb editor规则设置类别优先顺序

allegro pcb editor在规则设置之前,必须了解allegro pcb editor规则设置类别优先顺序,

2011-11-22 10:53:16 5429

5429

5429

5429

多重网格格子Boltzmann方法

针对复杂流动数值模拟中的格子Boltzmann方法存在计算网格量大、收敛速度慢的缺点,提出了基于三维几何边界的多重笛卡儿网格并行生成算法,并基于该网格生成方法提出了多重网格并行格子Boltzmann

2018-01-24 15:23:33 0

0

0

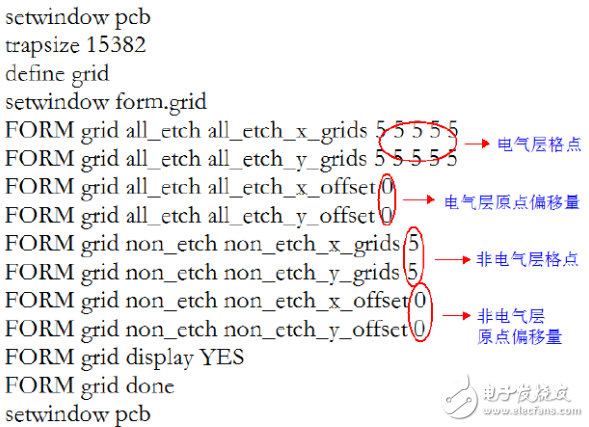

0allegro快速设置栅格点方法步骤介绍

约束驱动的Allegro流程包括高级功能用于设计捕捉、信号完整性和物理实现。由于它还得到Cadence Encounter与Virtuoso平台的支持,Allegro协同设计方法使得高效的设计链协同成为现实。

2018-02-07 14:35:31 27399

27399

27399

27399

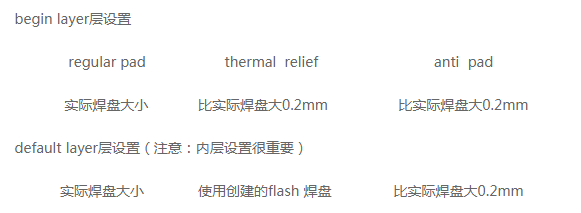

allegro建立焊盘的方法和操作步骤

是不是还在对allegro建立焊盘的一些方法和规则模糊不清,这里就对大家进行详细的介绍,希望能帮助到大家。 详细说明下,allegro软件中,制作通孔焊盘的方法步骤: 对pcb设计来说,通孔类的元件

2018-04-25 15:01:00 12990

12990

12990

12990

Allegro PCB设计时等长设置的一些方法与技巧解析

本文档的主要内容详细介绍的是Allegro PCB设计时等长设置的一些方法与技巧解析。以DDR3(4pcs,fly-by 结构)为例,讲述一下在allegro 中如何添加电气约束(时序等长)。

2018-11-27 16:02:57 0

0

0

0Allegro合并铜皮的方法

Allegro中如何合并铜皮,这又是一篇有关Allegro操作的简短文章,同样是近期很多读者搜索的。Allegro中简单快捷的绘制Shape的操作,是我非常喜欢Allegro的一个原因,使用者可以轻易地绘制出各种需要的Shape。

2019-06-08 14:32:00 8284

8284

8284

8284

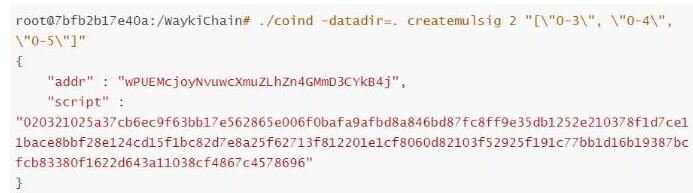

什么是维基链多重签名技术

多重签名(Multi Signature)指的是需要多个密钥来授权一个数字货币交易,它通常被用来界定对数字货币的所有权。传统的数字资产账户中,你的数字货币地址中,每一个地址都有一个对应的私钥,可以称为“单签名交易”。而多重签名地址,可以有多个相关联的私钥,你需要其中的多个才能完成一笔转账。

2019-06-05 10:14:22 790

790

790

790

将Allegro设计转换成POWER PCB的方法的教程免费下载

本文档的主要内容详细介绍的是将Allegro 设计转换成POWER PCB 的方法的教程免费下载。

2020-05-12 08:00:00 0

0

0

0你常用哪种方法去检查3W规则呢?

如何解决这个问题呢?可以利用Altium Designer的高级规则编辑功能、利用PADS的设计规则、利用Allegro、Mentor等对差分线进行过滤。

2020-06-05 14:47:05 2979

2979

2979

2979

protel转allegro的方法有哪些

电路设计软件的使用频率极高,采用电路设计软件,可提升工作者设计电路的效率。但在电路设计软件使用过程中,同样存在一些问题,如格式转换等。为帮助大家解决电路设计软件难点,本文将对protel电路设计软件中protel转allegro的方法予以介绍。如果你对本文内容具有兴趣,不妨继续往下阅读哦。

2020-08-23 09:16:42 2646

2646

2646

2646Group By高级用法Groupings Sets语句的功能和底层实现

SQL 中 Group By 语句大家都很熟悉,根据指定的规则对数据进行分组,常常和聚合函数一起使用。

2022-07-04 10:26:51 2657

2657

2657

2657芯片设计里的Multi-Bit FF方法讨论

在现代的芯片设计里边,工程师在优化功耗和面积上无所不有其极,这里讨论的multi-bit FF 就是其中的一种方法或者称之为一种流程。

2023-05-08 09:34:00 760

760

760

760

技术资讯 | Allegro软件中如何使用Temp Group功能

01什么是TempGroup?所谓的TempGroup,就相当于临时创建的Group组,用于很多元素的选择,用于一起执行某项命令,比如移动、复制等等。执行完命令之后呢,Group组就打散了,不存在

2022-02-07 14:17:51 566

566

566

566

Allegro小技巧 | 如何使用Allegro直接添加相对传输延迟的等长规则

Allegro的全称是CadenceAllegroPCBDesigner,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度

2022-05-13 09:28:25 1797

1797

1797

1797

电子发烧友App

电子发烧友App

评论