在Allegro 16.6中默认是2层板的,那怎样设置单层板呢?

2012-12-20 09:37:24

安装完Allegro后,Allegro可以正常使用,但capture无法打开,提示This application has quit unexpectedly,重装了好几次,都不行,求助大神

2016-03-09 15:21:21

Allegro中建立异形焊盘Allegro中可以建立异形焊盘.异形PAD是通过画Shape来实现的.在PADS中建立异形PAD,需要借助一个PAD和Shape相结合(Associate),即可建立

2019-01-19 11:24:13

Cadence、OrCAD、Capture的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。Allegro拥有完善的Constraint设定,用户只须按要求设定好布线规则,在

2019-04-28 17:24:42

也使用。采用花形,是因为金属化中工艺的要求。在allegro里又叫Flash Pad,是指过孔或元件引脚与铜箔的一种连接方式。其目的有几个,一是为了避免由于元件引脚与大面积铜箔直接相连,而使焊接

2011-11-24 16:35:22

小弟是PCB制版新手,刚开始自学 Cadence没有多久。我用的是Cadence 16.3. 用Orcad Capture CIS 制作原理图。练习时,从朋友那拷来了15.7版本的原理图,然后自己在

2010-06-17 03:43:50

allegro16_5中文教程

2014-07-06 15:07:59

allegro中analysis菜单下使用workflow manager,点击start analysis后显示implement analysis failed或者coupling analysis failed?

2022-03-07 22:02:42

pad、anti pad三种,那么当我导入网表之后(原理图中定义了该引脚和哪层相连),是不是由allegro自动决定,我的这个元件的引脚与地层相连还是与电源层相连,而相连的那层用的就是themal

2012-05-02 13:33:50

怎样在allegro16.5中查看没有定义的焊盘是否被添加了信号?如何避免?急急急!

2016-08-19 19:14:11

求助各位大神,capture原理图(dsn)怎么导入altuim 9中,在altuim 9中使用 File→import wizard,next→然后选择 orcad ,再选择**.DSN文件,再就报错啦{:4:}大家有没有高招,在线等.....{:13:}

2012-12-13 17:27:17

介绍在ALLEGRO中如何加入中文,这种方法也可以在ALLEGRO PSD中使用。<br/></p><p>&

2009-10-30 11:43:59

忽略掉这些,不用管这些错误,直接点击OK按钮即可; Xnet是什么含义,如何在Allegro软件中添加Xnet? 图5-113 SI Design Audit示意图 第三步,在PCB界面

2020-09-07 17:57:50

程序功能:在allegro中实现阴字体。 通常情况下,我们只能在allegro中添加阳字体文字。在某些特殊的场合,我们希望能够在板上的铜皮或者丝印中增加阴字体文字。在allegro本身没有提供该功能

2019-07-02 21:42:39

大家好。请教个问题呢。在allegro中怎么画 弹簧天线的封装

2015-01-28 11:50:39

对话框,如图1。图1在对话框中确定User Units选择Mils,阿Accuracy选择0,其他根据你的尺寸自行定义。设置完成选择OK按钮,使配置生效。◆设置动态铺铜参数。在Allegro中打开

2012-03-29 22:48:20

在allegro软件中插入公司LOGO的方法,有附件。

2015-07-13 17:51:55

在AD14中如何在重新定义板子形状时画出圆形的板子,求高手解答

2015-08-17 10:36:16

的摸索,找到一些实现的曲线实现方法。我用Altium Designer 6.6,下面以6.6为例讲讲如何将Allegro的brd板子导入Protel (DXP)中。

2019-07-23 07:00:19

如何在BIM中添加pin的驱动,因为ImgB没有OAD功能,希望在ImgB不能正常工作时,也能够在boot的时候通过引脚电平去选择从ImgA启动,但是我想加入PIN.h和CC26XXPIN.C的时候提示各种错误,我把其他工程中的路径包含和宏定义都加上也不行,请问是还缺少什么?

2016-03-31 16:52:33

请教个问题,在 CCG5代码中怎么实现DR_SWAP?我们配置了端口 0 作为源对外充电,但是我们希望 PORT0 做了 UFP。我们是这样写的代码:案例 APP_EVT_PD_合同谈判_完成

2024-02-26 06:27:15

教大家一个如何在头文件中定义全局变量的方法 通常情况下,都是在C文件中定义全局变量,在头文件中声明,但是,如果我们定义的全局变量需要被很多的C文件使用的话,那么将全局变量定义在头文件里面会方便

2018-07-04 08:34:47

教大家一个如何在头文件中定义全局变量的方法 通常情况下,都是在C文件中定义全局变量,在头文件中声明,但是,如果我们定义的全局变量需要被很多的C文件使用的话,那么将全局变量定义在头文件里面会方便

2018-07-09 09:25:50

allegro 16.2中文教程,英文图文说明,并附有中文注释,有allegro基础的都能看懂。点击下载

2019-04-28 16:13:25

步可以完成在Altium Designer中打开ALLEGRO的brd文件,也可以用来提取ALLEGRO的封装(不过AD画封装已经够容易了,估计不会有人需要这么做吧),通过手动元件恢复,可以重建

2014-12-03 15:05:29

OrACD capture cis 使用中问题:通过CIS网络抓取功能获得元器件老出错:如图所示,老提示 cannotplace part outside of Capture CISq求大神指教啊!!!

2014-05-04 16:03:28

。通过这一功能我们可以直接将Protel的原理图转化到Capture CIS中。 注意事项: 1) Protel DXP在输出Capture DSN文件的时候,没有输出封装信息,在Capture中

2018-09-17 17:14:49

PCB设计软件allegro蓝牙音箱案例实操讲解,以蓝牙音箱为案例将PCB设计基础知识融进实际案例中,通过操作过程讲解PCB设计软件功能及实用经验技巧,本文着重讲解结构性器件的定位的相关内容。本期

2018-08-15 10:10:36

开启这项功能而已.在Cadence 16.5中的capture开始交互式布局方法为在Capture中设置'option'-->'preferences'-->'miscellaneous

2012-04-19 22:11:11

问:Allegro中如何合并铜皮(Merge Shapes)答:在Allegro中,Shape不仅可以是走线,还可以是各种其他属性,例如Silkscreen,Place Bound,Solder

2014-11-12 17:49:12

一致的,本文以BeamRF中的开窗设计为例。其实在Allegro中设计开窗的方法非常简单,总的来说就是在Board Geometry下的Soldermask Top或者Soldermask Bottom

2019-08-07 04:00:00

`我需要的是直接在allegro中修改的方法,不要导出,因为没有CAD那些其他的软件。点击setup-outlines-board outline后弹出下面这个对话框求各位大大们帮忙一下,我是新手~谢谢了`

2017-11-13 14:46:11

ALLEGRO快速换层技巧-----博励pcb培训整理打开env文件在EVN文件里增加如下命令funckey 1 'pop bbdrill;pop swap;subclass top'funckey

2019-02-15 03:24:30

in drill legends,and there could be problems elsewhere as well.内容是Drill/Slot symbol需设定,而手工制作焊盘时不设定这个参数也不会报错。请教如何在LP中设置Drill/Slot symbol或不定义这个参数。万分感谢!

2014-07-17 11:29:28

V853开发板购买链接:https://www.hqchip.com/p/KFB-V853.htmlswap功能简介1、概念介绍swap:系统内存紧张时进行的内存回收操作。swap分区:在swap

2022-07-18 09:36:09

的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。本资料详细划分了allegro的每个功能对应的教程,看完必定会有所收获。

2019-01-15 14:01:00

PSpice菜单中,配置文件名称显示在PSpice配置文件中。 2.更加简洁的工作区 OrCAD Capture为您提供了大量易于使用的工具和功能,便于您的原理图设计。从17.4版本开始,工作区

2020-07-06 14:49:39

点查找了相关的帖子后找到解决方法,小结步骤如下: 1. 首先确认orcad中value值被设置 2. 在Allegro中建立元件库(Package symbol)时,需要添加Ref,其中最常用的2个

2011-06-23 15:08:09

怎么直接在allegro PCB环境下直接给一个无网络的pin赋予网络(不通过原理图)我已经在 PCBeditor已经创建了网络了,但是不知道怎么赋予这个pi 你们谁知道?

2019-06-25 22:49:36

1. 前言什麼是 SKILL?SKILL 是一種程式語言。是Cadence 開放給使用者可以藉由SKILL 取得Allegro中的資料並做一些客製化的程式

2011-01-11 10:36:56

allegro中这个怎么样添加模型?

2019-08-01 05:35:21

allegro中 要修改 丝印编号 比如从pcb01改成pcb02怎么修改呀还是只能再次重新添加

2019-09-09 05:35:31

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h”。但是,它不起作用。 另外,我想知道C代码中

2019-03-05 13:40:09

如何在IAR for ARM中定义常量或数组到flash而不是RAM中?const,__flash关键字都不行,网上说加一个编译开关,也没有,如何实现想请教,谢谢!已经得到解决,是我看错了地址区间,实际上const定义就行。

2022-12-09 16:17:13

如何在IAR中实现printf函数功能?

2021-12-01 06:29:17

如何在Keil ARM MDK中实现延迟功能,等待给定时间(以微秒为单位),可以重新编译为Keil项目设置中定义的任何合理时钟速度?所有这一切都没有使用计时器。

2018-08-22 10:29:23

我使用相同的示例代码来捕获句点。在调试模式下,我正在读取表达式 - 数据,我能够在那里看到十六进制值你能帮我理解吗,如何将这个十六进制值与输入引脚上的频率联系起来和如何在 PPG bean 中配置

2023-03-20 07:38:51

如何在PSOC4中覆盖PrtTf?重写RealTest.c中的PrtTf函数,但仍在“y-siNIT”ARM LIB函数调用中崩溃。如何在PSoC4编译中跳过(或重写)?目标是从PrtTF到RealTest.c中定义的FPTCCF函数。附上项目供参考。Cyrjj.CaseV02.Zip的设计176.4 K

2019-09-25 14:08:37

。我定义了两个屏幕:一,二。两个屏幕都包含容器“Selection1”这个过程工作正常。问题:如何在 ScreenOneView::setupScreen() 函数中设置容器中按钮的颜色?我已经尝试了一切,只是找不到解决方案。

2023-02-02 06:20:02

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。那么该如何在低端FPGA中实现DPA的功能呢?

2021-04-08 06:47:08

请问如何在函数中命名引脚,如[C] 纯文本查看 复制代码//两个函数在同一个程序中。以下为示例需求***it P1_1= P1^1; void test(){P1_1= P1^2;}void

2019-07-10 04:12:56

我如何在启动文件中调用定义为 uint32_t getValue(void) 的 C 函数(在 Reset_Handler 例程中)?需要什么语法?我尝试导入它并将其设置为 extern(其他标准

2022-12-09 07:27:54

使用BLE共享内存引导加载程序我试图定义用于在应用程序的配置数据bootloadable一块闪光。但这不应该由一个引导闪存操作的影响。所以我想块应在bootloader程序定义。我做了以下工作:在

2019-09-06 12:57:34

我在C中编写代码,但需要与包含文件通信。如何在源代码中包含包含文件的定义?我必须创建一个头文件,它反映了包含文件吗?如果是,有没有办法将头文件与包含文件合并?,或者可能从包含文件生成头文件?

2019-09-17 11:51:07

对于virtex7系列FPGA,如何在用户代码中定义“Startup”元素?我在哪里可以找到有关其用法的具体文档?谢谢!

2020-07-25 11:17:37

,如何实现linux中支持的swap功能的呢?1,嵌入式linux随产品发布时,运行的逻辑往往是在设计之初就确定了。因而在选择内存大小时,避免了可用内存的不足的问题。因而不会出现swap现象和需求...

2021-11-05 07:05:22

allegro中怎么制作Mark点,有没有教程文档之类的资料,在百度上找了,都没有找到制作教程

2019-08-27 05:30:54

在allegro中,请问怎么给一个过孔赋予网络?多谢解答!

2019-08-26 05:35:41

allegro中机械孔怎么制作的,有没有制作教程,新手不懂,求指教

2019-08-29 02:36:37

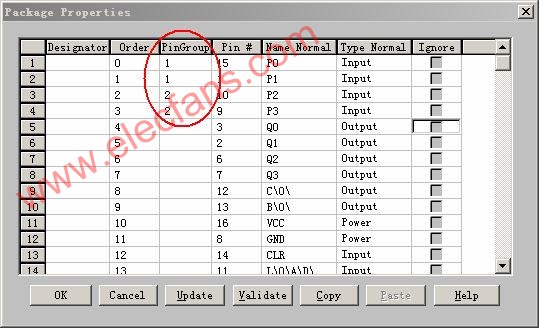

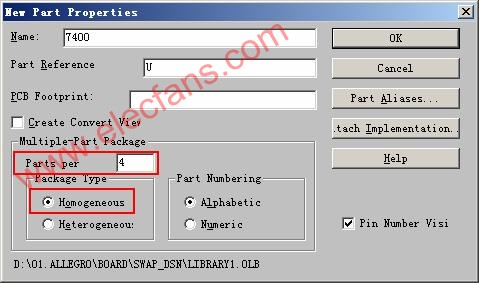

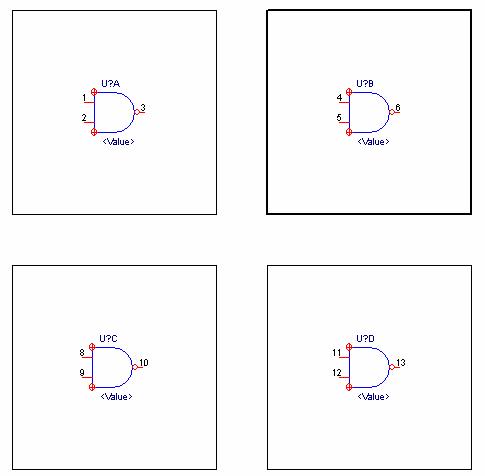

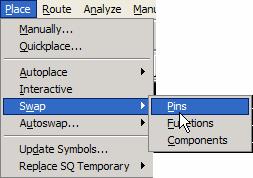

我在PCB editor中swap了pin,怎么成长orcad中back annotate时使用的.SWP文件?

2011-12-18 11:26:04

更换了一次计算机域,计算机名字,然后重新更新了allegro破解licence之后,在allegro中鼠标滚轮的缩放功能就没有了。鼠标没坏,在其他软件里面缩放功能都没问题。查看了env,对比同事的也没有问题。网上也没有解决方法,求大神指点。

2018-08-22 11:56:30

/Capture CIS(含有元件库管理之功能),原理图仿真工具PSpice(PSpiceAD、PSpiceAA),PCB Layout工具 OrCAD PCB Editor(Allegro L版本

2012-07-08 22:59:53

功能我们可以直接将Protel的原理图转化到Capture CIS中。 这里,我们仅提出几点通过实践总结出来的注意事项。 1) Protel DXP在输出Capture DSN文件的时候,没有输出

2018-11-22 15:47:00

Capture生成的Allegro格式的网表传递到Allegro BRD中,作为我们重现工作的起点; 2) 首先,我们要重现器件布局。在Protel中输出Place & Pick文件,这个文件

2014-12-03 15:20:51

在allegro中怎么把整个模块旋转

2019-04-26 07:35:24

想要使用data capture功能,但是下载下来的文件夹(见附件)中没有data_capture.bat这个文件。点击其他文件显示找不到系统路径。请问data capture功能怎么使用?附件DataCapture.zip40.3 KB

2018-10-23 09:29:28

大家好!请问如何在RT-Thread studio的debug和release模式中设置各自的宏定义,我在debug模式下设置了一个DEBUG的宏定义,发现它在release模式下也起作用。切换

2022-07-26 11:15:21

如何在Allegro增加零件及修改连线关系 步骤: 1. 设定环境变數: 使用这项功能前必先启动Logic_edit_enabled环境变數. 在Allegro选择下拉式菜单

2009-09-06 11:07:31 0

0 Allegro中网络表的导入以及回编到Capture中的一些注意事项:网络表(Netlist)是沟通电路原理图和Layout实际板子的桥梁网络表包含的内容有零件Pin的连接线关系以及零件的包装等基本

2009-09-20 18:08:08 0

0 What is the Capture to Allegro interface?Before the 9.2.1 release, Capture used the third party

2010-04-05 06:21:28 0

0 如何在Allegro中执行SKILL-由下拉菜单执行指令:如何在 Allegro 中執行SKILL(2)-由下拉選單執行指令1. 前言在之前我們已經介紹過如何載入以及執行 SKILL,接下

2010-04-25 10:06:53 0

0 Best practices for preparing a library for Capture-Allegro PCB Editorflow Limit part and pi

2006-04-16 20:47:17 665

665 PCB抄板之PROTEL到ALLEGRO的转换技术1

1. PROTEL 原理图到Cadence Design Systems, Inc. Capture CIS

在Protel原理图的转化上我们可以利用Protel DXP SP2的新功能来实现。通过

2010-02-02 10:42:53 1435

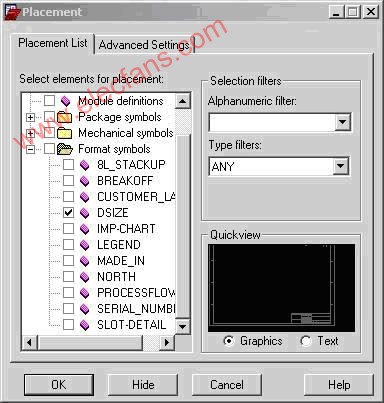

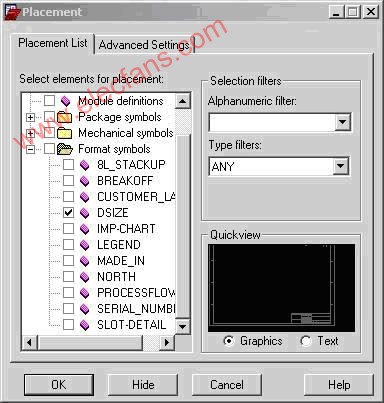

1435 一、创建图纸外框Allegro提供专门的创建图纸外框功能,并把它视为一种的Symbol,称为Format Symbol。 方法:在Fil

2010-06-24 10:29:05 2936

2936

本章的主要内容介绍Allegro 如何载入Netlist,进而认识新式转法和旧式转法有何不同及优缺点的分析,通过本章学习可以对Allegro 和Capture 之间的互动关係,同时也能体验出Allegro 和Captur

2011-11-24 11:37:21 0

0 allegro常用功能介绍

2022-01-10 11:53:15 0

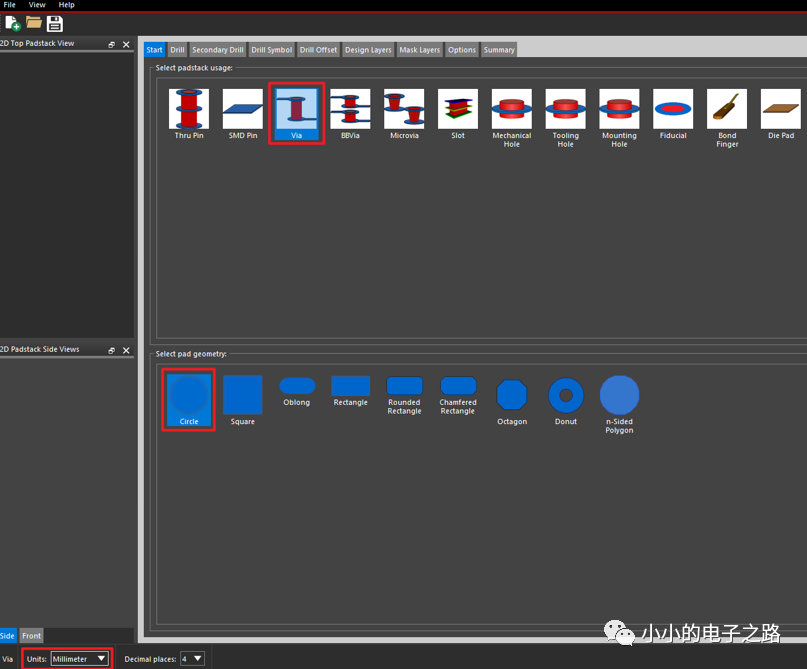

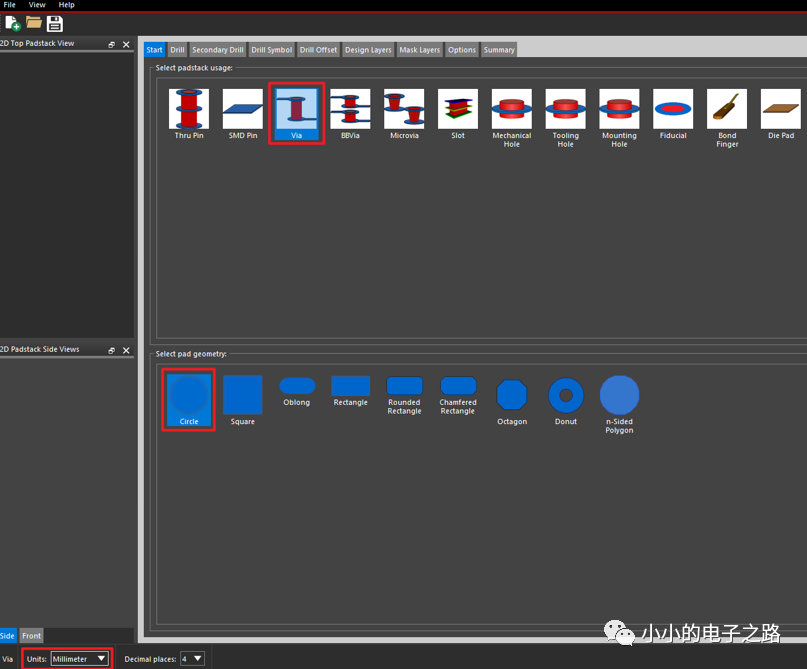

0 过孔也是PCB中最常见的孔之一,它用于连接双面板和多层板中各层之间的走线。下面就来简单介绍一下如何在Cadence Allegro软件中制作过孔。

2023-10-21 14:07:25 1287

1287

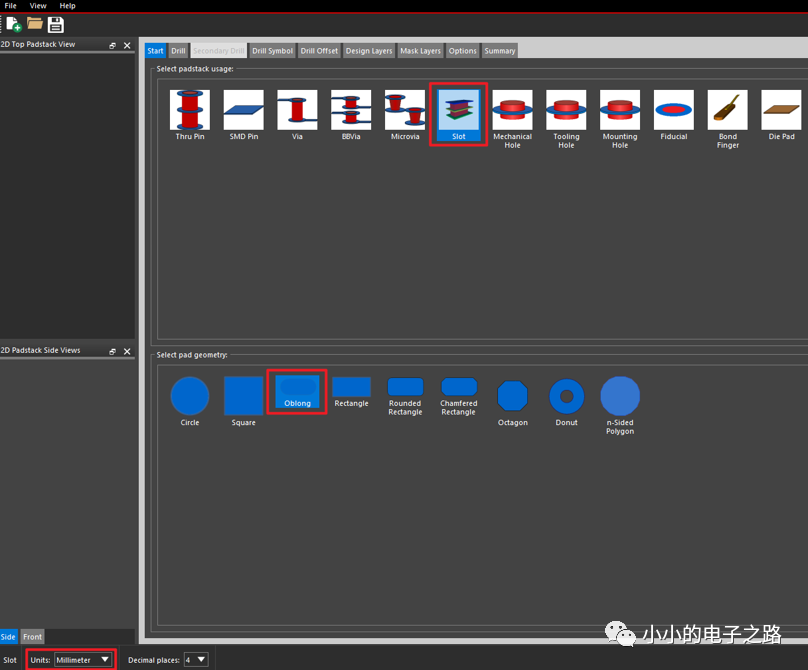

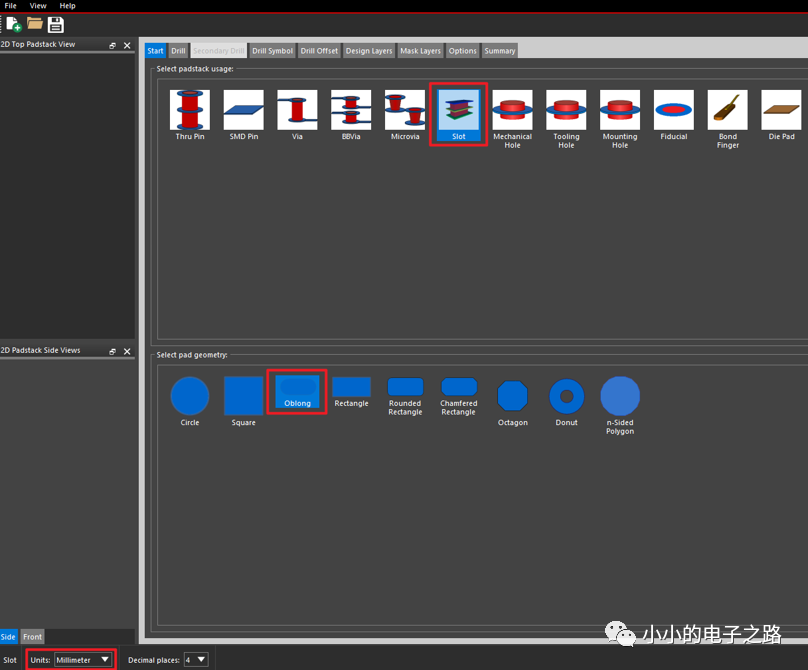

槽孔是指钻孔形状不是圆形的通孔,某些体积较大的开关的封装会采用槽孔。下面就来简单介绍一下如何在Cadence Allegro软件中制作槽孔焊盘。

2023-10-21 14:08:29 621

621

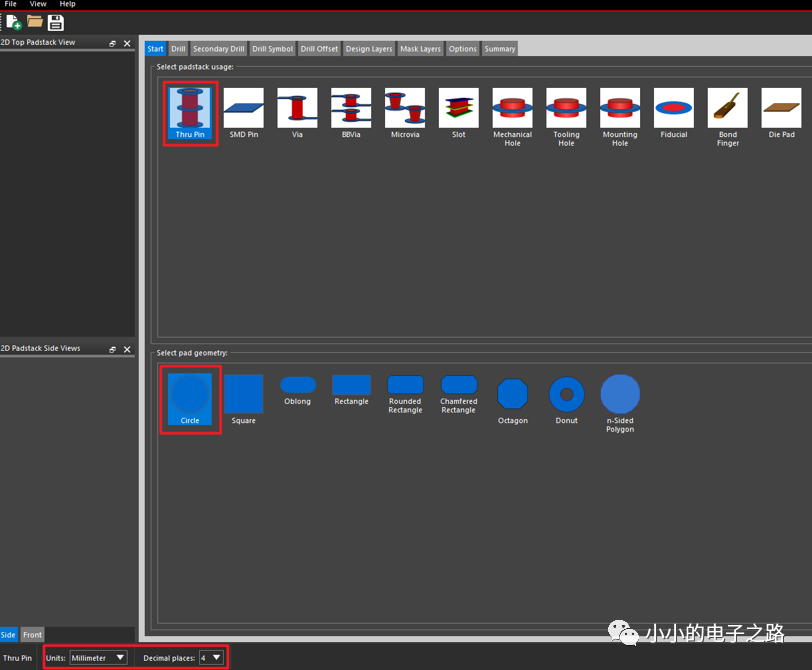

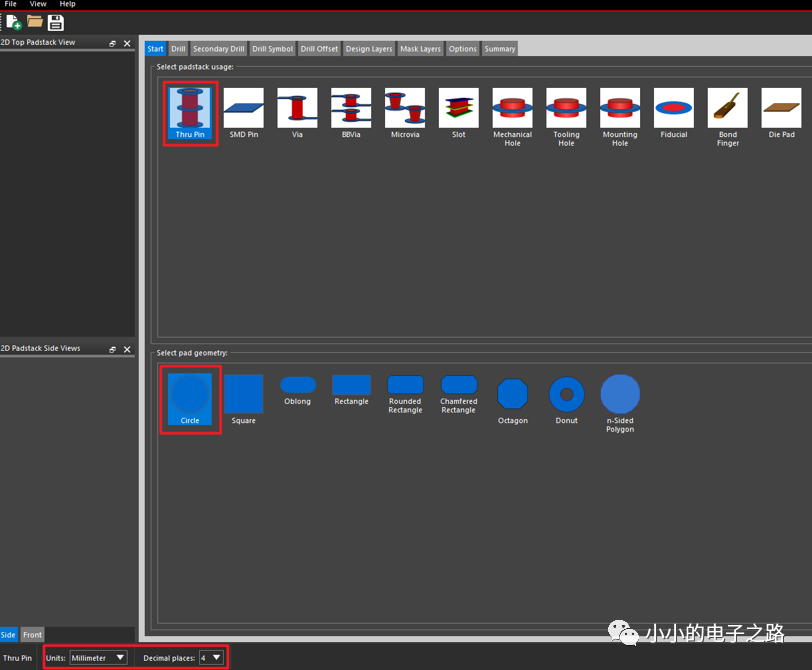

通孔焊盘可以说是PCB中最常见的焊盘之一了,对于插针等插件元器件的焊接,其采用的焊盘大都是通孔焊盘。下面就来简单介绍一下如何在Cadence Allegro软件中制作通孔焊盘。

2023-10-21 14:10:59 1189

1189

电子发烧友App

电子发烧友App

评论