本文为大家带来cadence allegro pcb layout详细教程 。

工程师的巨大福利,首款P_C_B分析软件,点击免费领取

一、用Design Entry CIS(Capture)设计原理图

1、创建工程

file--》new--》project ;输入工程名称,指定工程放置路径;

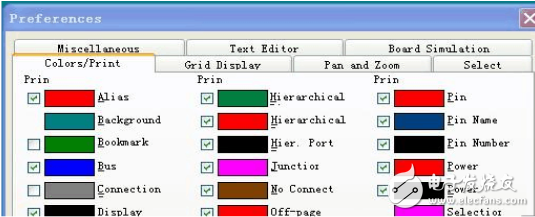

2、设置操作环境Options--》Preferencses:

颜色:colors/Print

格子:Grid Display

杂项:Miscellaneous

常取默认值

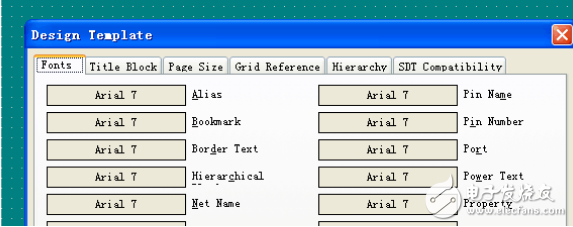

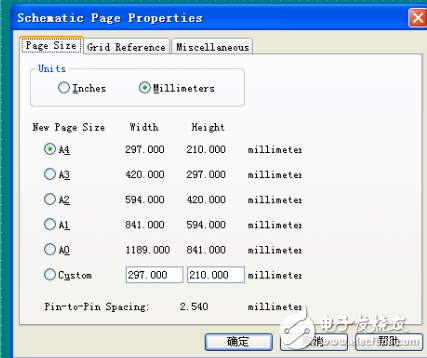

3、配置设计图纸:

设定模板:Options--》Design Template:(应用于新图)

设定当前图纸Options--》Schematic Page Properities

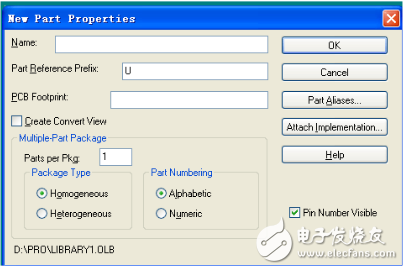

4、创建元件及元件库

File--》New Library --》选择要添加到的工程

Design --》New Part.(或者在Library处右击选择New Part)

(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default适用于标准逻辑)

(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)

一个封装下多个元件图,以View ext part(previous part)切换视图 元器件封装:

(1)place --》line画线,用来画封装外形;

(2)place--》pin放置管脚;放单个或多个;

不同类型的管脚选择的type不同;

5、绘制原理图

(1)放置电器

Place--》part ;可以从设计缓存中,活着元件库,软件自带元件库,中选择;选择Add Library增加元件库;

电源和地(power gnd)从右边工具栏中选择;

(2)连接线路 wire

bus:与wire之间必须以支线连接,并以网标(net alias)对应(wire:D0,D1.。。.D7;bus:D[0..7]) 数据总线和数据总线的引出线必须定义net alias

(3)Schematic new page (可以多张图:

单层次电路图间,以相同名称的“电路端口连接器”off-page connector连接

多层次式电路图:以方块图(层次块Hierarchical Block.。。)来代替实际电路的电路图,以相同名称Port的配对内层电路,内层电路之间可以多张,同单层连接

(4)PCB层预处理

编辑元件属性

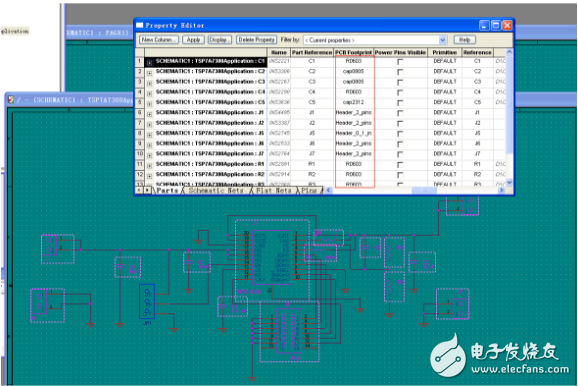

在导入PCB之前,必须正确填写元件的封装(PCB Footprint) 参数整体赋值(框住多个元件,然后Edit Properties),出现如图所示的property editer; 编辑pcb footPrint(与allegro pcb中的元器件的封装名称相一致);part Perference是网表导入allegro pcb后的元器件名称;还能进行其他属性编辑;还可添加其他需要的属性;

(6)分类属性编辑

Edit Properties--》New ColumnClass:IC(IC,IO,Discrete三类,在PCB中分类放置) 放置定义房间(Room) Edit Properties--》New ColumnRoom 添加文本和图像

添加文本、位图(Place.。。)

6、 原理图绘制的后续处理

(切换到项目管理器窗口,选中*.DSN文件,然后进行后处理————DRC检查、生成网表及元器件清单)

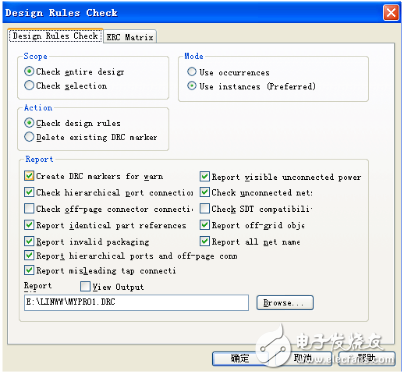

(1)设计规则检查(Tools--》Design Rules Check.。。)

Design Rules Check

scope(范围):entire(全部)/selection(所选)

Mode(模式):occurences(事件:在同一绘图页内同一实体出现多次的实体电路) instance(实体:绘图页内的元件符号) Action(动作):check design rules/delete DRC Report(报告):

Create DRC markers for warn(在错误之处放置警告标记) Check hierarchical port connection(层次式端口连接) Check off-page connector connection(平坦式端口连接) Report identical part referenves(检查重复的元件序号) Report invalid package (检查无效的封装)

Report hierarchical ports and off-page connector(列出port和off-page 连接) Check unconnected net Check SDT compatible Report all net names

(2)元件自动编号(Tools --》Annotate)

scope(范围):Update entire design/selection

Action:Incremental reference update 增长的自动编号

unconfitional reference update

reset part reference to “?” 将编号重置为“?”;

Add/delete Intersheet Reference(在分页图纸的端口的序号加上/删除图纸的编号) Reset reference numbers to begin at 1 each page原理图每个页重置编号从1开始

(3)自动更新器件或网络的属性(Tools--》Update Properties.。。)

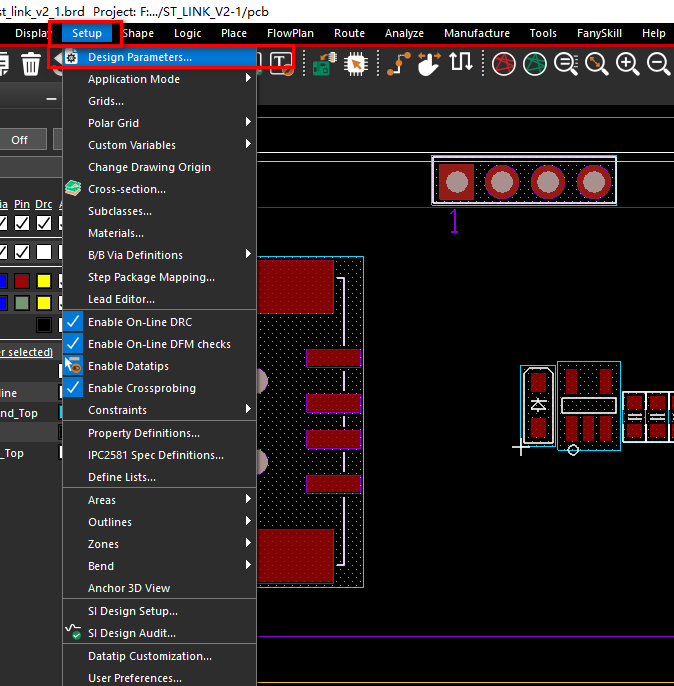

7、生成网表

在原理图检查无误后

Tools--》Create NetLists生成网表;

电子发烧友App

电子发烧友App

评论