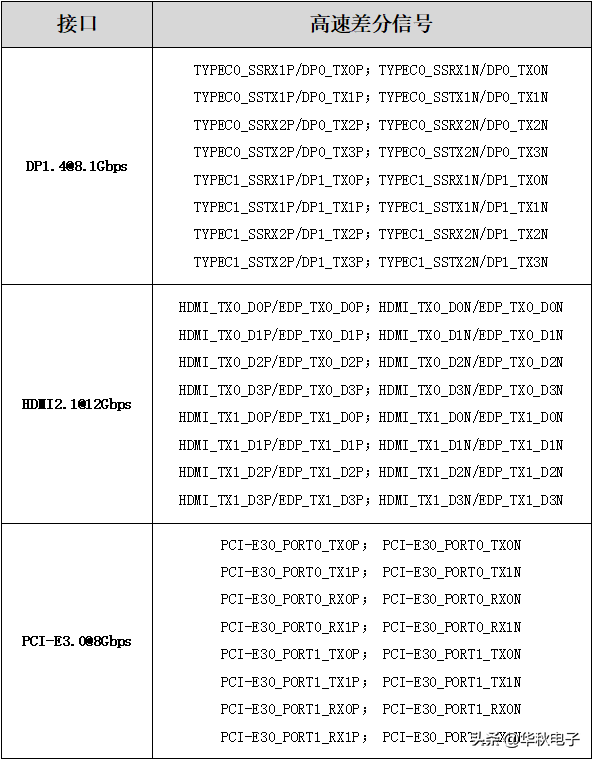

接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。 高速信号布线时尽量少打孔

2023-08-02 08:41:11 1432

1432

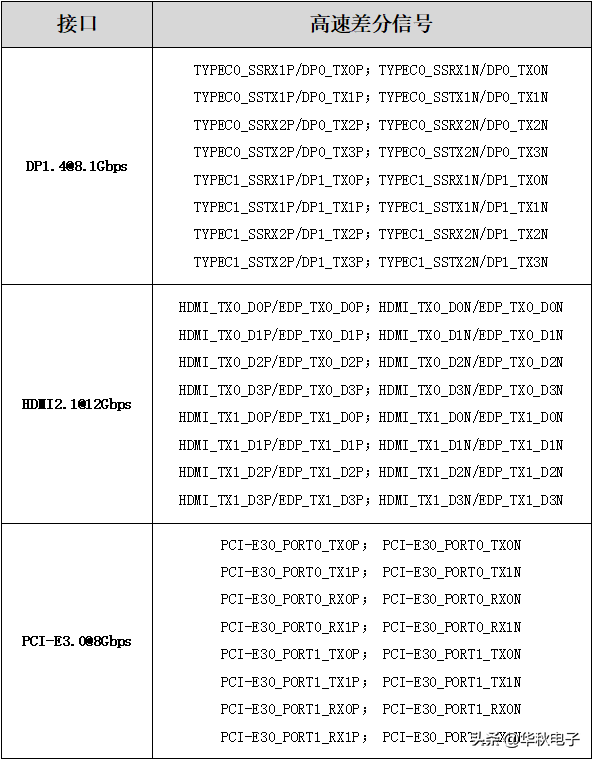

如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。 高速信号布线时尽量

2023-08-01 18:10:06 1263

1263

如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。 高速信号布线时尽量

2023-08-03 17:13:35 644

644

老师给了去年一个师姐画的板子的那个项目文件,10层的,就是所有工作都做完了,只等着加工那种。 让我们学习,我把他布的线全部给去了,然后自己试验布,不过咋样也布不完!请问高手:10层板是纯手工布,还是加杂自动布线, 我试了,没成功,求指点~~~~

2012-12-18 13:43:01

等等。参与直播观众将获得哪些知识点:• 1.多层板的设计原则• 2.叠层和阻抗的设计• 3.高速电路布局布线考量• 4.常用接口的PCB设计• 5.开关电源Buck的PCB lay板技巧• 6.BGA

2019-09-06 18:44:34

有个问题想请教一下,设计6层板的时候将2,5层设置成电源层,3,4层设置成内部布线层。这样两层之间难免有一些线会重叠部分,怎么确认会不会有严重的串扰?

2019-04-01 07:35:04

放线,特别是集成电路引脚之间和周围。3、不同层之间的线尽量不要平行,以免形成实际上的电容。4、布线尽量是直线,或45度折线,避免产生电磁辐射。5、地线、电源线至少10-15mil以上(对逻辑电路)。6

2013-12-05 17:46:56

4层板布线指南

2012-08-18 09:42:49

各位老师,一块已用过一段时间的4层板( 别人画的),现想用手动布线的方式做一些小的修改,但在布线时,有一些新放置的过孔和焊盘,不知如何使它从顶层连接的底层?或顶层连接到电源层?或连接到地线层?谢谢,请知道的老师告知详细步骤。

2016-09-24 21:04:29

,并且夹在两个内电层之间。这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。(4)避免两个信号层直接相邻。相邻的信号层之间容易引入串

2015-02-11 16:25:13

上设置的约束多,延时将增大。通常高速逻辑器件的信号上升时间大约为0.2ns。如果板上有GaAs芯片,则最大布线长度为7.62mm。 设Tr 为信号上升时间, Tpd 为信号线传播延时。如果Tr≥4

2012-09-19 17:08:44

高速板4层以上布线总结 (工作之余总结,谨供学习交流)1、 3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短,如下图(按前一种):2、 引脚之间尽量不要放线,特别是集成电路引脚之间和周围。3

2014-11-18 10:02:46

在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。最终的答案各不相同,但在所有情况下,设计工程师都应尽量消除最佳做法的误差,而不要

2018-10-17 15:14:27

高速PCB布线经验: 1、3点以上连线,尽量让线依次通过各点,便于测试,线尽量短 2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。 3、不同层之间的线尽量不要平行,以免形成实际上

2018-01-04 08:50:10

转帖高速PCB布线经验: 1、3点以上连线,尽量让线依次通过各点,便于测试,线尽量短 2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。 3、不同层之间的线尽量不要平行,以免形成

2018-01-10 10:24:05

(地)层上在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量,成本也相应增加了,为解决这个矛盾,可以考虑在电(地)层上进行布线。 首先应考虑用电源层

2012-07-20 19:11:26

布线所需要的最少布线层数。布线层的数量以及 层叠(stack-up)方式会直接影响到印制线的布线和阻抗。板的大小有助于确定层叠方式和印制线宽度,实现期望的设计效果。多年来,人们总是认为电路板层数越少

2021-03-31 06:00:00

这些器件布线所需要的最少布线层数。布线层的数量以及 层叠(stack-up)方式会直接影响到印制线的布线和阻抗。板的大小有助于确定层叠方式和印制线宽度,实现期望的设计效果。 多年来,人们总是认为电路板

2022-04-18 15:22:08

就是指4层及4层以上的板,对于元器件的密度要求不高的一般来讲4层就足够了。从过孔的角度可以分成通孔,盲孔,和埋孔。通孔就是一个孔是从顶层直接通到底层的;盲孔是从顶层或底层的孔穿到中间层,然后就不继续穿了

2018-11-28 11:41:21

15条高速PCB布线经验分享

2021-01-29 06:10:51

1、3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短。 2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。 3、不同层之间的线尽量不要平行,以免形成实际上的电容。 4、布线

2017-06-22 15:15:34

`高速PCB板的电源布线设计随着集成电路工艺和集成度的不断提高,集成电路的工作电压越来越低,速度越来越快。进入新世纪后,CPU和网络都迈入了GHZ的时代,这对于PCB板的设计提出了更高的要求。本文正是基于这种背景下,对高速PCB设计中最重要的环节之一——电源的合理布局布线进行分析和探讨。`

2009-12-09 13:58:28

高速PCB板的电源布线设计

2009-03-26 21:50:55

,也就是说设计同样的电路,如果4层电路板的使用面积能降低到双层板的1/2,那么成本就与双层电路板相同。虽然批量多寡会影响电路板的单位面积成本,不过尚不致有4倍的价差,如果发生4倍以上的价差时,只要能设法

2018-11-23 16:04:04

尽量短。如图所示,将第2层设置成分配给高速数字器件(如处理器)的电源;将第4层设置成高速数字地;而将去耦电源放置在PCB的顶层;这是一种比较合理的设计。此外,要尽量保证由同一个高速器件所驱动的信号走线

2018-11-27 15:14:59

在高速PCB电路板的设计和制造过程中,工程师需要从布线、元件设置等方面入手,以确保这一PCB板具有良好的信号传输完整性。在今天的文章中,我们将会为各位新人工程师们介绍PCB信号完整性设计中常

2018-11-27 09:57:50

PCB(印制电路板)布线在高速电路中具有关键作用,那么高速PCB的布线需要考虑哪些事项呢? 这个问题大家考虑过吗?

2019-08-02 06:46:56

本帖最后由 eehome 于 2013-1-5 10:01 编辑

高速PCB板信号接地设计中存在接地噪声及电磁辐射等问题,提出了高速PCB接地模型,并从PCB设计中布线策略的分析和去耦电容的使用等几个方面讨论了解决高速PCB板的接地噪声和电磁辐射问题的方法。

2012-03-31 14:31:52

设计要求使用高密度球栅数组(BGA)组件,就必须考虑这些器件布线所需要的最少布线层数。布线层的数量以及层叠(stack-up)方式会直接影响到印制线的布线和阻抗。板的大小有助于确定层叠方式和印制线宽度,实现

2015-09-24 14:39:21

高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗控制(12)建议所有布线需倒角,倒角角度推荐45度(13)建议防止信号线在相邻层

2017-02-16 15:06:01

` 本帖最后由 飞翔的乌龟005 于 2017-2-10 10:43 编辑

高速PCB设计中常规PCB布线,有以下基本要求:(1)QFP、SOP等封装的矩形焊盘出线,应从PIN中心引出(一般采用

2017-02-10 10:42:11

量短,且不能引得到处都是。时钟振荡电路下面、特殊高速逻辑电路部分要加大地的面积,而不应该走其它信号线,以使周围电场趋近于零。4、尽可能采用45°的折线布线,不可使用90°折线,以减小高频信号的辐射

2016-12-21 10:12:15

作为地线用。或是做成多层板,电源,地线各占用一层。2 数字电路与模拟电路的共地处理 现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑它们

2012-08-13 16:30:47

1、pcb时钟频率超过5MHZ或信号上升时间小于5ns,一般需要使用多层板设计。原因:采用多层板设计信号回路面积能够得到很好的控制。2、对于多层板,关键布线层(时钟线、总线、接口信号线、射频线、复位

2014-12-25 10:19:32

在未布板之前,先将高速USB主控制器和一些相关的主要器件摆放好。尽可能缩短走线长度,优先考虑对高速时钟信号和高速USB差分线的布线,尽可能的避免高速时钟信号与高速USB差分线和任何的接插件靠近走线

2019-05-30 07:36:38

实践探讨高速电路布线问题

2021-03-02 08:29:40

和地吗?如果电源不止一个的时候怎么弄(是不是这样分配:信号层 - 地 - 电源层(分割电源层)- 信号层)? (3)什么情况下才考虑做成4层板?4层板能不能达到一定的屏蔽效果?该怎样设计?(我主要是想得到一定的屏蔽效果,才做的4层板。) 以上问题还请各位帮我解答一下,非常感谢!!!

2019-01-23 06:36:48

约束设置都是至关重要的,它是PCB布局布线质量的主要保证,一个好的规则约束需要花费掉整个PCB设计至少一半以上的时间和精力(尤其是对高速板更是如此)。关于布局布线规则约束的设置,有些经验值可以

2012-12-04 23:14:03

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

一、BGA焊盘区域挖

2023-08-01 18:02:03

PCB布线设计原理在当今激烈竞争的电池供电市场中,由于成本指标限制,设计人员常常使用双面板。尽管多层板(4层、6层及8层)方案在尺寸、噪声和性能方面具有明显优势,成本压力却促使工程师们重新考虑其布线

2009-11-24 10:58:51

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。 6层板:L2和L5为地线层和电源层,其它为信号层。

2019-05-21 10:19:01

之间和周围。3、不同层之间的线尽量不要平行,以免形成实际上的电容。4、布线尽量是直线,或45度折线,避免产生电磁辐射。5、地线、电源线至少10-15mil以上(对逻辑电路)。6、尽量让铺地多义线

2012-09-16 20:11:29

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层

2018-09-17 17:41:10

转自赛盛技术分享在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后

2016-08-24 17:28:39

PCB四层板的电源和地的内层到底怎么布线?

2023-05-06 10:19:18

问题: 目前的,PCB,实际的布线层,最多可以达到多少层?!层与层之间应该没有加压任何元器件,特殊情况除外。 PCB板上的走线, 最细的线径,表面板和之间的夹层板的走线,是1/3毫米,== mm

2018-11-05 10:07:44

地相连接作为地线用。或是做成多层板,电源,地线各占用一层。2 数字电路与模拟电路的共地处理现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑

2018-12-07 09:44:39

可以适当加粗。 3. 限定布线区域,尽量在模拟区域内完成布线,远离数字信号。高速信号布线要求 1. 多层布线 高速信号布线电路往往集成度较高,布线密度大,采用线路板多层板既是布线所必须的,也是降低

2022-11-07 20:44:08

总数BGA区域所有除外4层的管脚布线都需要占用第5层环形区域的布线通道,根据此区域的布线通道数和总的布线连接数确定最少内层布线层数。(4)根据布线瓶颈区确定PCB板布线层数,瓶颈区域PCB板最少布线层数

2017-09-07 14:36:02

PCB设计中 禁止布线层、丝印层、机械层这三个层好像概念挺模糊的,比如画板子的外围标识的时候,使用禁止布线层,同时也可以使用丝印层,那这两个层有啥区别啊?另外这个机械层好像并没有什么作用,大家在什么情况下会使用这个机械层?

2019-08-16 04:36:00

的可靠性设计-去耦电容配置 ◎ 高速板4层以上布线总结 ◎ &

2009-04-14 23:48:45

实例之四:信号线布线.5-10 4层PCB设计实例之五:内电层定义及分割5-11 4层PCB设计实例之六:补泪滴和覆铜6-1 高速PCB布局的基本原则16-2 高速PCB布局的基本原则26-3 高速

2016-10-21 13:40:00

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

01

BGA焊盘区域挖

2023-08-03 18:18:07

四层板的层叠方案层叠建议:优选方案一(见图1)。方案一为常见四层PCB的主选层设置方案。方案二适用于主要元器件在BOTTOM布局或关键信号底层布线的情况;一般情况限制使用。方案三适用于元器件以插件

2016-08-05 19:44:17

,阐述多层板布线时所应该注意的事项,以供电子设计者参考。 1、 3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短。 2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。 3、不同层之间

2016-08-13 20:50:53

4x7628pp,滑片2mm板厚极限14层,1.6mm一般最多12层,做14层阻抗不易控制高速要求:信号层与地层尽量近电源与地尽量近,并有一处相邻保证地平面足够大,并完整保证相邻的两个信号层尽量远,布线走线为交叉走线,尽量满足3W规则,不行则相互错开信号层如果以VCC为参考平

2022-03-02 06:09:06

近一段在学4 层板的画法 在图书馆借了很多书 上边讲4层板的画法很浅去往上找视频都是讲99sede 不够通过以上2过程对4层板有了一定了解问老师 老师 说 你去百度一下“内电层分割” 下一届给你仔细

2012-04-28 11:45:24

高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗控制(12)建议所有布线需倒角,倒角角度推荐45度(13)建议防止信号线在相邻层

2017-01-23 16:04:35

高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗控制(12)建议所有布线需倒角,倒角角度推荐45度(13)建议防止信号线在相邻层

2017-01-23 09:36:13

板的布线层层数;(3)信号质量控制:对于高速信号比较集中的PCB设计,如果重点关注信号质量,那么就要求减少相邻层布线以降低信号间串扰,这时布线层层数与参考层层数(Ground层或Power层)的比例

2017-03-01 15:29:58

本文分享了四层以上的高速板布线的技巧与方法。

2021-04-26 06:22:05

PCB板分为很多层,那其中四层以上PCB高速板布线有哪些技巧呢?下面就为大家介绍介绍,希望对大家有一定的帮助。 1、3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短。 2、引脚之间尽量

2019-05-06 11:32:44

这几个网络线 3.设置层颜色 4.设置走线层对:从top到bottom 5.布线:电源线走在第三层F3走线 换层(左键点击 F4)再L+n,就在第n层布线 六层板:第一层:top第二层:GND第三层

2015-06-18 15:50:34

。这样做虽然可以使布线工作变得容易,但是同时也增加了PCB 设计的成本。因此是否选取此技术,要根据实际的电路复杂程度及经济能力来决定。在设计四层板的过程中根据成本并不一定采用此技术。如果觉得贯通孔数

2015-01-23 10:34:30

高速化,具体地说,层间绝缘膜要用介电常数比低于3的材料,通过这样低介电常数膜与铜布线相结合进一步降低布线延迟。之后与0.1mm、0.07mm的细微化相适应,还要继续降低层间绝缘膜的介电常数比。 在

2018-08-29 10:53:04

多层板中,内相邻布线层布线有何原则?

2015-01-06 15:28:31

想问下多层板怎么布线层

2016-04-20 01:22:03

。 地的层数设置则需要注意以下几点:主要器件面对应的第二层要有比较完整的地平面;高速、高频、时钟等重要信号要参考地平面;主要电源和地平面紧耦合,降低电源平面阻抗等等。 二、信号层数规划 布线通道

2018-09-20 10:56:31

怎样将RK3568系统的6层板改为4层板设计呢?

2022-03-02 09:32:59

求大神介绍一下关于高速板4层以上的设计流程

2021-04-23 06:29:05

链接深入浅出谈多层面板布线技巧(1)——双面板深入浅出谈多层面板布线技巧(2)——双层板深入浅出谈多层面板布线技巧(3)——四层板深入浅出谈多层面板布线技巧(4)——四层板

2015-01-15 11:11:57

的每一个改变都需要rebuild,使得软件运行速度很慢。乱七八糟的说了这么多,总结起来就一句话,多层板的电源层和地层用plane,信号层用layer。 选用四层板不仅是电源和地的问题,高速数字电路对走线

2015-01-15 11:39:12

我们都已经很清楚了,PCB板分为很多层,其中四层以上布线比普通的单层和双层要复杂一些,这就要求我们掌握一些技巧,那么具体有哪些技巧呢,下面就为大家介绍介绍,希望对大家有一定的帮助。3点以上连线,尽量

2019-03-11 11:04:46

成本时总是要求设计者在设计中使用双层电路板。虽然多层板(四层、六层以及八层)的解决方式无论在尺寸、噪声,以及性能上都可以做得更好,但成本压力迫使工程师必须尽量使用双层板。在本文中将讨论使用或不用自动布线

2016-04-28 11:45:56

4层板板厚多少有要求吗?

2019-09-17 22:20:23

4层板加GND VCC链接到网络后,请问顶层那些vcc和gnd的网络还需要布线吗?还有这些vcc和gnd的网络点只有焊盘穿过到底层,是怎样连接到中间层的gnd和vcc,是要打过孔吗?

2018-08-06 14:22:40

,请问一下,4层板铜厚一般是怎么设置的?外层多厚?内层多厚?是不是越厚越好?高速信号线的铜厚一般是多少?

2019-08-26 00:29:13

请问POWER PCB能布4层板吗?我在BlazeRouter的布线规则里只看到有TOP 和BOT两层,它能布4层板吗?如何设置呢?请高手回答,谢谢!

2008-09-23 20:48:43

需要传输高速信号,那么设计原则 3(电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间)就必须得到满足。 10层板 PCB典型10层板设计 一般通用的布线顺序是TOP--GND---

2016-08-23 10:02:30

,是L2-3一张芯板(core),L4-5(core)一张芯板,其它的用PP加铜箔,最后压合在一起而成的。如图一所示。图一 但是六层板板厚在1.6mm及以上时,如果要进行常规阻抗控制(单线50欧姆,差分100

2019-05-30 07:20:55

,是L2-3一张芯板(core),L4-5(core)一张芯板,其它的用PP加铜箔,最后压合在一起而成的。如图一所示。图一 但是六层板板厚在1.6mm及以上时,如果要进行常规阻抗控制(单线50欧姆,差分100

2022-03-07 16:04:23

,是L2-3一张芯板(core),L4-5(core)一张芯板,其它的用PP加铜箔,最后压合在一起而成的。如图一所示。 图一但是六层板板厚在1.6mm及以上时,如果要进行常规阻抗控制(单线50欧姆,差分100

2019-05-29 07:26:53

PCB布线经验技巧总结,好东西,喜欢的朋友可以下载来学习。

2016-01-20 15:20:25 0

0 。

4、布线尽量是直线,或45度折线,避免产生电磁辐射。

5、地线、电源线至少10-15mil以上(对逻辑电路)。

2019-05-09 14:31:16 1749

1749 让你布线少走弯道的15条高速PCB布线经验分享

2022-02-12 10:44:53 5486

5486 8Gbps及以上高速信号PCB布线建议 —来源:瑞星微RK3588 PCB设计白皮书 如表1-1所示,RK3588芯片以下接口的信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求

2023-08-02 07:35:01 423

423

如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。高速信号布线时尽量少打孔

2023-08-03 17:31:07 662

662

高速信号布线时尽量少打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

2023-08-04 16:12:44 316

316

1432

1432

1263

1263

644

644

423

423

662

662

316

316

电子发烧友App

电子发烧友App

评论