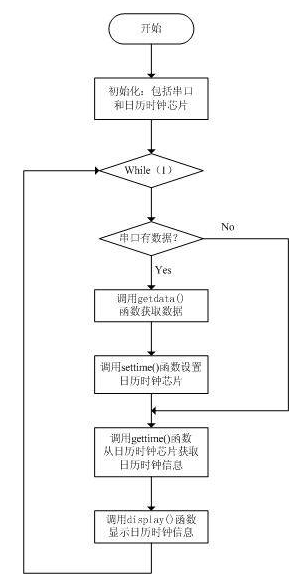

| 关键词:Verilog HDL 系统仿真 逻辑综合 数字电子系统 日历时钟芯片应用非常广泛,例如在IC卡电子门锁中,可利用日历时钟芯片的定时时钟计数功能,在IC卡内输入客人住房时的时间段,只有当时间段所包含的时间与日历时钟所记录的时间一致时,方可开门,否则IC卡为无效卡。 利用Synopsys公司提供的集成电路设计工具VCS和DC,设计了一个带有48字节RAM的日历时钟芯片,包括该芯片RTL级代码的编写、功能仿真和综合,达到了预期的目标。该芯片的具体性能指标是:工作电源电压为2.5~6V;日历时钟工作电源和RAM数据保持电源电压为1~6V;工作电流最大为50μA;四年日历时钟,24或12小时格式,32.768kHz时基;48字节RAM,自动字节地址增量;具有可编程的闹钟、定时和中断功能。 1 ASIC设计概述 随着深亚微米技术的发展,数字集成电路的规模已经发展到上百万门。未来的二十多年里,一块ASIC芯片中将会达到上千万门的规模。这样的电路规模,仿真和综合优化在开发过程中发函来发函重要。较复杂的数字电子系统设计往往采用自顶向下(Top-Down)的方法,设计流程可以分为以下几个主要的部分:系统级设计、设计实现、设计验证和流片封装。深亚微米工艺下的ASIC设计流程如图1所示。

图1

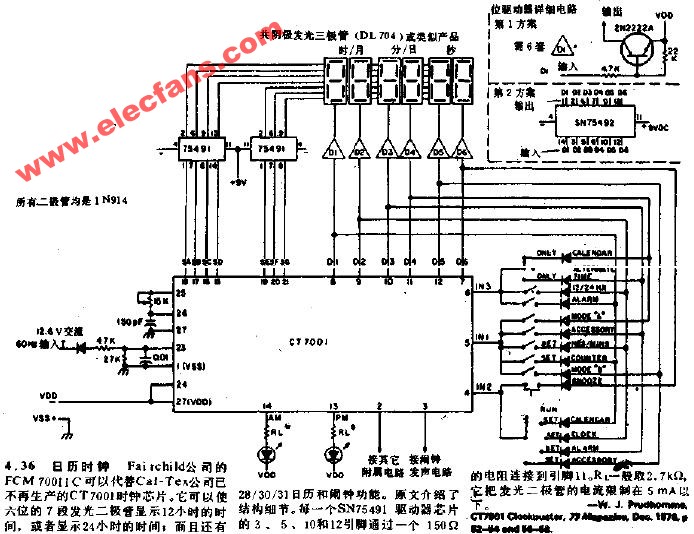

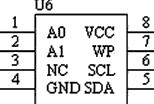

本文主要介绍芯片的系统级设计和所有逻辑设计,生成可供物理设计的经过验证的门级网表文件。 2 芯片的系统级设计 系统级设计是芯片设计的第一步,也是关键的一步。首先根据设计要求提出设计构想,然后再对这一构想进行细化。本设计把整个系统分成几大模块,即产生32.768kHz的振荡器(这个模块不用设计)、256分频器、48字节RAM和地址寄存器。设计构想如图2所示。 RAM中的00~0FH单元是一些带有特殊功能的寄存器,00H单元是控制芯片所有功能和操作的状态寄存器,通过设置状态寄存器,可以选择32.768kHz时钟模式或计数模式。在日历时钟模式中,1/128秒、秒、分、小时、年/日期、星期/月都是以BCD码分别存放在01H~06H单元的寄存器中;而在事件计数模式中,则对输入到振荡器输入端(OSCI)的脉冲计数,事件计数器为6位BCD码。07H单元是能存储最大数为99天的定时器。08H是控制定闹、定时和中断输出功能的闹钟控制寄存器。09H~0FH单元用于储存用户信息。 对于这样的设计,传统的方法是使用中小规模集成电路来构成,本文则用Verilog HDL描述来实现。整个芯片采用模块化设计方式和Top-Down设计方法,根据寄存器的不同划分成模块,然后用测试程序TestBench对顶层模块进行仿真;仿真通过后利用厂家提供的工艺库及时序约束脚本文件对其进行综合;综合通过后生成门级网表文件,然后再用厂家提供的仿真库对门级网表进行综合后仿真。本文设计用到的工艺库是***旺宏公司(Macronix,MXIC)提供的基本单元库(slow.db和fast.db)、基本符号单元库(slow.sdb)和用于综合后仿真的库文件仿真库(models.v)。

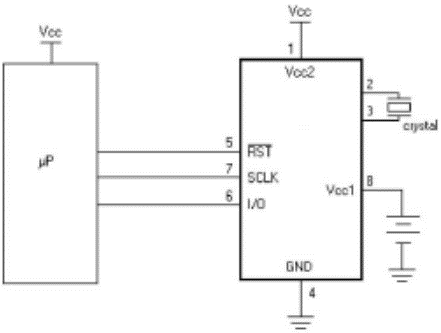

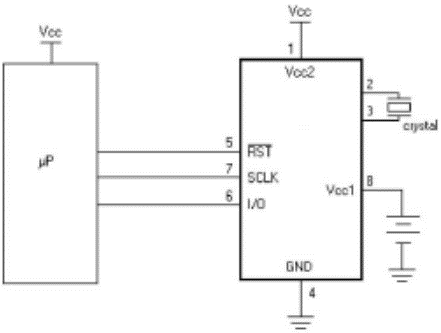

这是一个同步时序电路的设计,所以保证正确的时序是设计的关键,本设计中有四个时钟: (1)系统时钟clksys,是外部微控制器提供的时钟信号,用作寄存器读、写时钟信号; (2)测试时钟clktest,是整个芯片的测试时钟信号,一般限于厂家使用。 (3)时基时钟clk32,定时方式时,外部石英晶振提供的32.768kHz振荡信号经过256分频后得到时钟信号(evt128),作为RAM前16字节特殊寄存器的同步时钟信号。 (4)计数时钟clkevt,计数模式时的外部计数脉冲信号。 图3是日历时钟顶层模块端口示意图,读选通信号w、写选通信号r、片选信号csn和RAM地址控制信号addr[5:0]是由外部微处理器提供的。当写信号w为真时,将输入数据datin[7:0]写入存储器被选中的地址;当读信号r为真时,将从存储器被选中的地址中输出数据datu[7:0]。当满足下面两个条件之一时,中断请求信号intz输出低电平:①00H单元中的第0位为1,并且08H单元的第3位为1。 由于篇幅有限,在这里只写出顶层模块rtc的部分设计程序,具体如下: ‵timescale 10ns/10ps //模拟时间定标; module rtc (clktest,clksys,clk32,clkevt,csn,rstz,w,r, addr,datin, datu, intz); input clktest,clkysy,clk32,clkevt,csn,rstz,w,r; //输入输出端口说话 input[7:0] datin; input[5:0] addr; output[7:0] datu; output intz; reg[7:0] datu; //设定变量的数据结构; ctl_status c0 ( clksys,evt128,rstz,w,cs00,……); //调用00H单元子模块; sec128 c1 (clksys, clktest, evt128, rstz,……); //调用01H单元子模块; sec c2 (clksys, evt128, clktest,rstz,……); //调用02H单元子模块; …… int c20 ( timer_flag,alarm_flag,……); //调用产生中断模块; always @ ( addr or stop_soft or ) begin if(cs & r) begin //根据控制地址信号而输出RAM中各寄存器的数据; case (addr) 0:datu={stop_soft,hold_flag,func_mode,mask_flag,alarm_en,alarm_flag,time_flag}; 1:datu=data_latch[15:8]; …… 47:datu=data_ram[255:248]; default:datu=8‵h00; endcase end else datu=8‵h00; end endmodule 在顶层模块中调用了根据不同功能而编写的20个子模块,如ctl_status.v、sec.v和ram.v等。其中RAM存储器的1F~2FH单元是模拟电路,要用全定制的方法生成。而在数字集成电路设计中,仿真时经常要用到存储器的行为模型,这里给出的行为模型ram.v用于仿真。

3 利用EDA工具进行系统仿真 设计人员利用先进的EDA工具作为测试平台,以验证数字电子系统设计模块的逻辑功能和时序功能。虽然不同的EDA工具提供的平台不同,但都可以对被测试对象加载激励信号,并通过波形输出、文件记录输出等方式观察和比较仿真结果。加载激励信号需要设计人员设计测试程序(TestBench),对于较大规模的系统设计,测试程序的设计有时比本身的程序设计还要复杂。 在本文的设计中,首先对每一个子模块设计一个测试程序,单独进行逻辑仿真,然后再设计一个测试程序对整个设计进行逻辑仿真。由于篇幅有限,在这里仅写出sec.v的部分测试程序,具体如下: ‵timescale 10ns/10ps module sec_test; reg clksys,evt128,clktest,carry_sec128,rstz,datin,datoout,w; reg[7:0]datin,datout; reg[1:0]func_mode; sec c2 (clksys,evt128,clktest,carry_sec128,rstz,datin, datout,func_mode,w,); always #10 clksys = ~ clksys; always #30 evt128 = ~ evt128; always #50 clktest = ~ clktest; always #80 carry_sec128 = ~ carry_sec128; //产生输入激励; initial begin rstz = 0; #90 rstz = 1; end //产生复位信号 initial begin w = 0; #100 w = 1; #5 w = 0; #1100 w = 1; #5 w = 0; end //产生写信号 initial begin func_mode= 0 ; #1000 func_mode = 1; end //功能模式的选择; initial begin datin= 0 ; #20 datin = 00100101h; #1000 datin = 00010010; end //输入数据; always @ (func_mode or datin of datout) ﹩ display ("At time %t,func_mode=%b,datin is %b% b,datout is %b",﹩time,func_mode,datin,datout); //输出模拟结果。 利用Synopsys公司的仿真工具VCS进行仿真,无论在功能上还是在时序上,都完全符合要求。 4 利用EDA工具进行综合和优化 综合是利用芯片制造商提供的基于电路单元(综合库)实现用硬件描述语言描述的电路功能。现在许多优秀的综合工具都能借助现有的综合库将Verilog HDL源代码进行综合,转化成门级电路图,并且可以根据设计者施加的约束条件对电路进行优化,产生面积或者速度达到最优的结构,并生成相应的逻辑网表以供后端设计使用。 综合时要进行延时计算和设计规则检查,需要设置的相关内容主要包括:操作环境、导线负载模型、设计约束、设计规则约束。通常情况,设计者要先编辑一个包括这些设置的脚本文件(例如本文编辑的脚本文件rtc.tcl),启动逻辑综合工具DC后就可,执行文件中的各条指令了。综合的过程如图4所示。下面利用日历时钟实例简单介绍这一过程。 (1)建立设计环境 ***旺宏公司的0.35μm CMOS标准单元综合库slow.db和fast.db包含了与非、或非、非门等基本逻辑单元,还有选择器、与或非、或与非等较复杂的组合逻辑以及DFF(D触发器)等时序逻辑单元。利用该库可以这样来建立环境: set target_library {slow.db fast.db} set link_library {*slow.db fast.db} set search_path "/home/tools/synopsys/library" (2)读入HDL描述 如果读入多个模块,首先应该读入的是顶层模块。要将当前的设计设置为顶层模块,可以这样来设置: read_verilog "home/design/rtl/rtc.v" read_verilog "home/design/rtl/see.v" current_design rtc (3)定义环境变量 环境变量输出网表和输出报告等路径设置可以这样来定义: netlist_path = "home/design/netlist" report_path = "home/design/report" (4)定义性能约束、时序约束和面积约束 性能约束主要包括创建时钟、输入延迟和输出延迟等;综合的目标是得到最小的面积。可以这样来设置: creat_clock-period 70-name my_clock [get_ports clksys] set ex_clk[remove_from_collection[all_inputs][get_ports clksys] set_input_delay 4 -clock my_clock ﹩ex_clk set_output_delay 3 -clock my_clock [all_outputs] set_max_area 1 (5)编译 用compile命令进行编译即可。

(6)写门级网表 综合后的门级网表可以用edif文件形式保存,也可以用.V文件形式存放,采用如下命令: write-format verilog-hierarchy-output $netlist_path/rtc.vg 此外,还需要保存延时信息,以便综合后仿真,延时信息一般放在.sdf文件中,采用如下命令: write_sdf ﹩netlist_path/rtc.sdf-version 1.4 (7)给出报告 可以报告综合出的面积、时序信息、违反约束路径以及单元的个数等,并存放到定义的目录文件中,下面举几个例子: report_area >$report_path/area.rpt report_timing >$report_path/timing.rpt report_constraint-verbose-all_violators $report_path/constrain.rpt 利用Synopsys公司的逻辑综合工具DC[4]进行综合和优化非常成功。 本文设计主要描述带有48字节RAM的日历时钟芯片的逻辑设计过程,并对其成功地进行了代码编写、仿真和综合,版图设计等。当然,本逻辑设计不是一蹴而就的。在此过程中,对各种异常情况都需要认真分析和反复调试。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

相关推荐

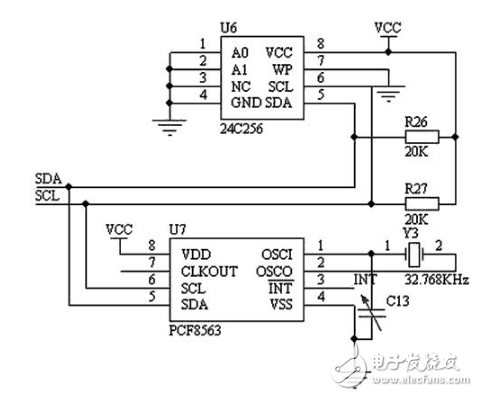

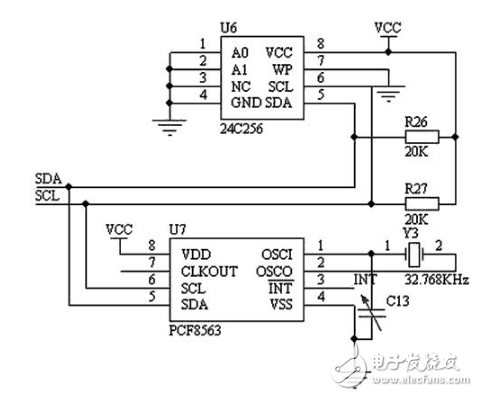

日历时钟和存储电路

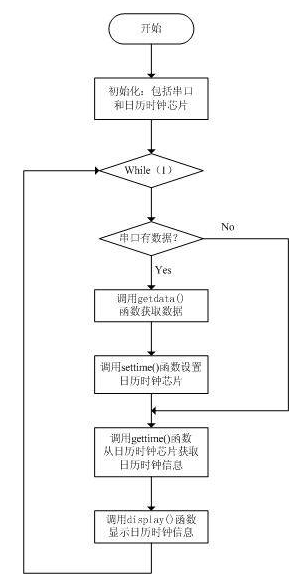

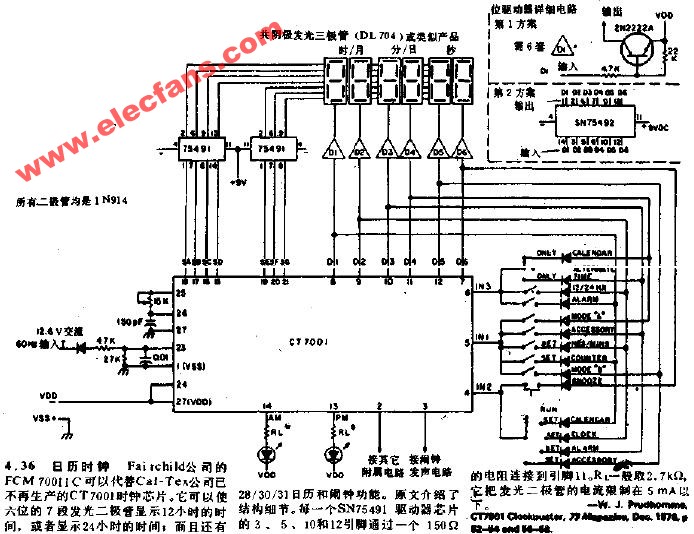

如图5所示,由EEPROM24C256和日历时钟芯片PCF8563组成。24C256是一款低电压、串行接口,容量为256K的存储器,用于存储测量的血压值。PCF8563是PHILIP 2010-01-27 09:47:49 6047 6047  fn(){ u8 buf[512]; ……}main(){ u8 buf[1024]; fn(); // 执行到fn内部被中断入栈1536字节 …… // 入栈1024字节}问:1024字节的局部数组在任意时候都会占据1024字节的栈区吗? 2020-07-31 07:07:46 ,发送第三字节……设备只时钟输出7位!从范围上可以看到,对于最后一个字节,只有7个时钟脉冲,然后代码进入一个永无止境的循环,等待BF设置,当然不会发生这种情况,因为传输没有完成(由于相同的原因,IF也没有触发)。可能,更不用说什么可能引起它。有什么建议吗?问候,DK 2019-09-19 07:35:20 芯片的DPTR有两组,所以多2字节)寄存器和2字节PC,算起来最多是:8*2(普通子程序)+7(反汇编中断的直接PUSH和POP指令,状态寄存器)+2(中断现场)+2(中断中的子程序)=27字节 2016-11-22 16:47:02 指示,有夏令时功能。(5)Motorola和Intel总线时序选择。(6)有128个字节RAM单元与软件接口,其中14个字节作为时钟和控制寄存器,114字节为通用RAM,所有RAM单元数据都具有掉电 2008-10-08 11:18:25 BLE现在在一个连接事件中只能发送小于20字节的数据,如果有更多的数据,能否在单次事件中将其发送完? 2016-04-01 10:36:46 CH341缓冲区长度32字节,I2C消息最长只有26字节,怎样收发大于26字节的消息? 2022-07-12 07:10:16 1、对于单发送或者接收的端点,端点数据长度为32字节,是否可配置DMA缓存长度为32字节;2、手册上有这样一句话:“注:接收数据的缓冲区的长度 >= min(可能接收到的最大数据包长度 + 2 字节,64 字节)”这个“2字节”是个什么意思? 2022-06-23 08:32:43 亲们,今天在设计中看见了一个关于DS12C887日历时钟芯片的电路设计,有完整的程序和电路图,我根据电路图(jpg格式)画好以后,在proteus里面仿真,虽然程序是对的,但数码管显示不显示,这是为什么呢,本人初学单片机,求大神帮助,附件里面有电路图和程序,求大神帮助改正,万分感谢 2014-04-06 22:56:17 DS1302是一款高性能、低功耗的实时时钟芯片,附加31字节静态RAM,采用SPI三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号和RAM数据。它可以与HT1380互换。 2021-04-27 06:55:02 存储实时时钟/日历的 31 字节的静态 RAM,可通过简单的串行接口与微处理器通讯,将当前的是时钟存于RAM。DS1302芯片对于少于 31 天的月份月末会自动调整,并会自动对闰年进行校正。由于有一个... 2022-01-17 07:37:39 有效期至2100年31 x 8支持电池的通用RAM2.0V至5.5V都可运行在2.0V时使用小于300nA电流单字节或多字节(突发模式)用于时钟或计算机读- 写的数据传输内存数据简单的3线接口详细描述DS1302芯片包含一个实时时钟/日历和31字节的静态RAM。它通过一个简单的串行接口与 2022-01-24 06:55:36 DS1302电子时钟DS1302如上图所示,它是由美国DALLAS公司推出的具有涓细电流充电能力的低功耗实时时钟芯片, DS1302是一种高性能、低功耗的实时时钟芯片,附加31字节静态RAM,采用 2022-01-17 06:44:35 一、芯片介绍DS1302是一种串行接口的实时时钟,高性能、低功耗,内部有可编程的日历时钟和31个字节的静态RAM,可以自动进行闰年补偿工作电压范围宽(2.5V~5.5V),还有对备用电池进行涓流充电 2022-02-25 06:05:15 DS1302涓流充电时钟保持芯片的原理与应用DS1302 是DALLAS 公司推出的涓流充电时钟芯片内含有一个实时时钟/日历和31 字节静态RAM 通过简单的串行接口与单片机进行通信实时时钟/日历 2009-12-12 16:36:36 (数据线), and SCLK (串行时钟). 数据输出输入时钟/RAM 一次1字节或者在脉冲串中多管脚定义DS1302涓流充电计时芯片达 31 字节. DS1302 被设计工作在非常低的电能下,在低于 2023-09-28 07:52:51 前天我用时钟芯片PCF8563与89C51搭了个系统!现在分享下PCF8563R日历时钟芯片原理及应用设计 2013-08-26 11:32:03 本帖最后由 964378200@qq.co 于 2016-2-17 12:35 编辑

RC522怎么读取7字节的UID?网上都是4字节的,有谁弄过的麻烦指导下呀 2016-02-17 10:19:01 SH79F642B是一颗低功耗高性能单相电能计量SOC芯片,片内集成单相电能计量、LCD驱动、日历时钟和加强8051核等功能。 SH79F642B内嵌电能计量模块,计量有功、无功,以及电压电流有效值 2022-10-20 06:16:57 具有运行更快速的优越特性。保留了标准8051芯片的大部分特性。这些特性包括内置256字节RAM和2个16位定时器/计数器,3个UART,外部中断NT1.此外,SH79F6431还集成了外部2816字节 2022-10-20 08:01:11 传统的8051芯片它具有运行更快速的优越特性。保留了标准8051芯片的大部分特性。这些特性包括内置256字节RAM和2个可编程计数器阵列,3个16位定时器/计数器,3个EUART,3个SPI。此外 2022-10-19 08:09:03 传统的8051芯片它具有运行更快速的优越特性。保留了标准8051芯片的大部分特性。这些特性包括内置256字节RAM和1个可编程计数器阵列,3个16位定时器/计数器,2个EUART,2个SPI。此外 2022-10-19 07:06:28 SH88F48是一种高速高效率8051兼容单片机。在同样振荡频率下,较之传统的8051芯片具有运行更快速,性能更优越的特性。 SH88F48保留了标准8051芯片的大部分特性,包括内置256字节 2022-10-19 07:24:42 通过SPI方式实现一字节的收发,主要是为了适配以下接口: 2023-02-16 08:18:45 您好: 我现在使用CC2530F256芯片,用TI专门的烧写工具可以对flash加解锁16字节进行加解锁操作。但是现在我想通过调用HalFlashWrite()函数软件控制BANK7的page127 2020-08-10 08:14:37 大家好,在zynq 7000系列中,UART FIFO的深度为128字节,这是不是意味着直到所有128字节的数据都在FIFO中传输它才会传输?如果有人知道,请告诉我...谢谢 2020-03-31 09:29:05 我知道数据储存的起始地址%对齐字节(N)=0才行,但是我不明白有两点问题1:UCOSIII的系统中的浮点数打印任务的堆栈大小要8字节对齐,float无论在32位机还是64位机中都是4字节大小, 可为 2020-04-23 00:21:44 刚刚发现 ARP 请求消息用 18 个字节的尾随零字节填充,使它们的长度为 60 个字节而不是 42 个字节。第三方设备不喜欢这样,无法响应 ARP 请求消息。我正在使用 STM32F476 设备生成 ARP 请求。有人能解决这个问题吗? 2023-01-04 08:31:36 但是提交给UDP就只有前256字节了,是pbuf没连接起来吗 2019-10-31 23:51:09 是4B的一级描述符,图上写错了,抱歉这个是韦老师MMU实验的C语言源码,可以正常使用,但是问题来了,4B的描述符地址的[1:0]位应该是00啊,也就是4字节对齐啊,可是这里明显不是4字节对齐,而是1 2019-08-05 03:26:44 我想把某个扇区全写上0x01,但只能将前256字节写上,后256字节全都是0xff,这是为什么呢还有,扇区不能读,读扇区函数已经检查了好多遍了,除了程序问题还可能有其他问题吗芯片是STC89C52 2019-08-01 04:35:24 数据线SDA和时钟线SCL与外界进行数据交换,从其时序关系可看出,DS3231有两种操作方式:(1) 写操作:把SDA数据线上的数据按RAM指定的首地址(Word Address)依次写入N个字节数据。主 2019-04-12 07:00:08 基于DS1302与AT89C51的实时日历时钟的LCD 2012-08-14 19:31:02 HiI目前正在使用带有EBI模块的DMA将64字节的数据传输到一个显示器,该显示器每接收一个字节就需要一个时钟。EBI选通的写使能(/WE)管脚使用PBCLK8除法器将发送的数据精细地设置为3 2020-05-11 12:37:20 我在EnCORE 2中的USB组件控制端点大小只有8字节。在我的应用程序中,我需要传输64字节。如何做到这一点?控制端点是一个双向端点,它使用相同的缓冲器(UBSI接口 2019-08-13 09:38:49 功能是什么?其次,我想使用TouthTigGPFiver探路者和写Flash的扇区,如何使用GPIF读取和写入512字节?第三,ChaneSeTeDMAChank是如何进行数据传输的?期待你的回复。 2019-10-31 11:22:15 31字节静态ROM 实时时钟SPI:一种传输方式静态ROM:只要有电,数据就不会丢失采用SPI三线接口与MCU同步通信,可采用突发方式一次传送多个字节的时钟参数和RAM数据附加31字节的静态RAM0两个存储器:日历时钟寄存器+静态RAM存储器寄存器:● 在任何对时钟或 2021-12-13 06:55:47 在TM4C123中申请一个1000*4字节的空间用来存储AD转换的结果,请问要怎么办?急求 2019-09-09 10:29:03 万年历一、实验目的二、实验内容三、实验步骤四、C代码如下五、实验结果六、实验体会一、实验目的为巩固所学的单片机知识,把所学理论运用到实践中,用LCD1602与AT89C51设计可调式电子日历时钟。二 2022-02-23 07:37:11 使用的按钮。这是在pic32mz ef)/.ony 1.07.1上运行的。如果进行这些更改,test=5,向生成器[4][0]=添加另一行,并将字节数更改为1000,则将结束一个永无休止的循环。缓冲区中的最大字节数是多少?如何编写比800字节更多的字节? 2019-08-12 08:45:41 利用Synopsys公司提供的集成电路设计工具VCS和DC,设计了一个带有48字节RAM的日历时钟芯片,包括该芯片RTL级代码的编写、功能仿真和综合,达到了预期的目标。 2021-04-27 06:17:33 我使用具有256字节EEPROM的PIC16F18325。我使用eeprom_read()和eeprom_write()函数来访问它。用于指示地址的变量被定义为无符号字符。然而,编译器说“警告:(752)转换为更短的数据类型”,并且当地址超过127时,奇怪的行为是我如何访问所有的256字节? 2020-04-21 10:09:55 我已经用F407的MAC层接收了小于60字节的帧,至于为什么会小于60字节我也不知道,因为我是从千兆网转换成百兆的,所以不知道是不是因为千兆网不会填充剩下的字节。我在描述符底层已经接收到ARP地址 2019-09-17 23:37:01 DS1302时钟芯片的使用带你写一个小时钟DS1302地址字节控制字节逻辑有效位必须是逻辑1,若为0,则数据就写不进去1302中。位6如果是0,则表示存取日历时钟数据位6如果是0,则表示存取RAM数据。一到五位则为操作地址,最低为为0表示写操作,1表示读操作。注意控制字节总是从最低位开始输出... 2022-01-17 07:43:57 串行日历时钟一、实验目的二、实验内容三、实验步骤四、C代码如下五、实验结果六、实验体会一、实验目的掌握串行日历时钟芯片DS1302的结构特点、工作原理和使用方法。2.掌握串行日历时钟驱动程序的开发 2021-12-08 08:30:21 数码显示日历时钟电路本文所应用到的相关器件资料: CD4017 LM8364   2008-08-18 22:03:02 封装很适合,且有256字节的内存。STM8小体积的居然都是小于等于128内存。

言归正传,说的就是和RAM相关的知识点,有没有想过keil 再使用默认配置SMALL模式,如果定义unsigned 2016-02-17 15:20:52 嗨,我们正在使用CR95HF,我们正在尝试使用CR95HFDll_SendReceive读取78字节的帧,但我们得到一个带有CRC和错误代码CCCCCC的64字节帧。 当使用USB作为CR95HF 2019-07-23 15:45:22 电子日历时钟(可设置两个闹钟)含protues图 2016-09-07 15:39:01 萌新求助,电脑串口发送9字节,其中包含1字节包头0x5a,和8字节的数 据,将8字节数据从小到大排序,单片机串口发送回电脑排序后结果。如何实现? 2019-11-01 13:44:56 字节的静态随机存取存储器。它通过简单的串行接口与微处理器通信。实时时钟/日历提供秒、分、小时、日、月、星期和年的信息。对于少于31天的月份,月末日期会自动调整,包括闰年的更正。时钟以24小时制或12小时制运行,带有上午/下午指示器。3.地址命令字节MSB(位7)必须是逻辑1。如果为0,对DS130 2022-01-17 08:30:02 AT45DB321D如何吧每页528字节改成512字节,用什么指令?手册上怎么没写啊? 2019-06-05 04:35:02 BLE5.0能支持广播数据达256字节,但是SDK里面最多只能广播31字节的数据,是不是只要修改B_MAX_ADV_LEN就可以了?如果设备广播数据超过31字节,仅支持BLE4.2的手机能否搜索到设备? 2019-10-31 09:38:43 设备描述符里面的第8个字节.bMaxPacketSize0,看了很多Demo都是设置为8字节。CH554.h头文件里面定义的DEFAULT_ENDP0_SIZE也是8。是否可以设置为64呢?如果设置 2022-05-30 07:36:36 大家好,C2000成员TMS320F28335在CCS3.3下是2字节对齐的,能不能改为1字节对齐?怎么改呢?再者,有没有在F28335下成功移植了ucos+lwip的呢? 2018-08-20 06:41:43 本帖最后由 一只耳朵怪 于 2018-6-6 15:26 编辑

如题,求问大家,IAR如何设置按1字节对齐? 2018-06-06 02:22:30 SUBS3014,SuxBB3014;你的简历是512字节吗?一、一、二、二、二、二、二、二、二、二、三、二、二、三、二、二、三、二、三、二、二、三、二、二、三、二、三、二、三、二、三、二、二、三、二、三、四、五、四、六、四、六、四、六、四、六、四、六、四、六、四、五、四、五、五、五、五、五、五 2019-10-31 10:06:55 看新塘的技术手册关于发送数据缓存与接收数据缓存,有15字节的FIFO,那么是不是说一次最多只能发送/接收15字节的数据呢?DrvUART_Write(UART_PORT1,string,24 2023-08-25 06:10:17 MCU包括8K和128字节的Flash,这8K的Flash和128字节的有不同吗?为什么我可以对128字节的读写。8K部分的读出的不是写进去的内容呢?型号是8051f206. 2019-06-25 02:16:04 M48T86是意法半导体公司生产的一种实时时钟,日历芯片.它具有精确计时、定时报警输出等功能,由于其内置128字节的非易失性RAM,因而具有功能强、使用方便等特点.文中详细介绍了M4 2009-04-24 16:22:36 36 36 PCF8583是 PHIL IPS 公司制造的带有 256×8bit RAM 的 8引脚日历/ 时钟芯片,采用 I2C两线串行总线接口,内含完整的振荡、分频、上电复位电路,并具备计时、日历、定时、闹钟和中断输出功 2009-04-25 13:48:47 56 56 DP8573A 是美国国家半导体公司生产的计算机用日历时钟芯片, 当主电源出现故障时自动转到备用电源并记录故障出现时间,有三种中断类型,并能记录晶振停振时间,故更适用于要求严格 2009-04-27 17:14:15 20 20 和114字节的电池备份静态RAM (DS12C887和DS12C887A包含113字节RAM)。DS12887在24引脚模块DIP封装内集成了晶体和锂电池。DS1 2023-07-21 17:15:17 和114字节的电池备份静态RAM (DS12C887和DS12C887A包含113字节RAM)。DS12887在24引脚模块DIP封装内集成了晶体和锂电池。DS1 2023-07-21 17:23:41 )、可编程方波输出和114字节的电池备份静态RAM (DS12C887和DS12C887A包含113字节RAM)。DS12887在24引脚模块DIP封装内集成了晶体和锂 2023-07-21 17:25:09 介绍了一种带有48字节RAM的日历时钟芯片的设计,该芯片具有振荡、分频、可编程的计时计数、定时闹响和中断输出等功能。该芯片基于Verilog HDL描述,采用模块化设计,可扩展性好 2010-07-05 16:10:08 23 23

日历时钟电路图 2009-01-13 20:25:22 2314 2314  日历时钟DS12887或146818的C语言源程序

#define uchar unsigned char#define uint unsigned int#i nclude <reg52.h>#i nclude <stdio.h>#i nclude & 2009-01-16 11:50:27 955 955 文中是以Versa 8051系列MCU的典型器件VRS51L3074和时钟日历芯片DSl2887为核心制作的可多定点电子日历时钟。该系统功能齐 2010-12-24 10:03:24 2043 2043  介绍了用自带的接口来实现对时钟日历芯片进行读取的方法。本设计所使用的时钟日历芯片是公司的。这是一款低功耗的实时时钟日历芯片, 它的所有地址和数据都通过总线接口串行传 2011-09-07 16:05:01 94 94 DS1302 是DALLAS 公司推出的涓流充电时钟芯片,内含有一个实

时时钟/日历和 31 字节静态 RAM ,通过简单的串行接口与单片机进

行通信。实时时钟/日历电路提供秒、分、时、日、周、月、年的信

息,每月的天数和闰年的天数可自动调整。 2015-11-24 17:02:10 8 8 带温度显示日历时钟及温度显示的电子万年历,带电路图+PCB+源程序 2015-12-07 14:35:52 86 86 PCF8563日历时钟芯片原理及应用设计,很好的学习资料。 2016-06-03 15:31:43 78 78 新型电子日历时钟芯片接口电路及程序设计 2017-01-24 16:54:24 30 30 PCF8563 I2C 实时时钟/日历芯片 2017-09-22 10:31:47 29 29 如下图所示,由EEPROM24C256和日历时钟芯片PCF8563组成。24C256是一款低电压、串行接口,容量为256K的存储器,用于存储测量的血压值。PCF8563是PHILIPS公司推出的一款 2018-01-17 14:08:01 4289 4289  在银行或者其他的公共场合中,经常会看到显示实时信息的显示屏,其中包括年、月、日、星期、时间等,本例子的功能是在51单片机系统中设置、获取、记录实时的日历时钟信息并通过数码管显示,选用日历时钟芯片 2019-08-19 14:16:23 4619 4619  本文档的主要内容详细介绍的是单片机C语言程序设计实例之带日历时钟及温度显示的电子万年历程序和工程文件免费下载。 2021-02-01 16:45:58 17 17 DS1302 ckle流充电计时芯片包含一个实时时钟/日历和31个字节的静态RAM。 它通过简单的串口与微处理器通信界面。 实时时钟/日历提供秒,分钟,小时,日期,日期,月份和年份信息。 月底日期 2021-04-07 09:33:22 9 9 通信产品中。 时钟芯片的原理 DS1302 的控制字符表示。控制字节的最高有效位(位7)必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据; 位5至位1指示操作单元的地址;最低 2021-07-13 14:48:27 9249 9249 串行日历时钟一、实验目的二、实验内容三、实验步骤四、C代码如下五、实验结果六、实验体会一、实验目的掌握串行日历时钟芯片DS1302的结构特点、工作原理和使用方法。 2.掌握串行日历时钟驱动程序的开发 2021-11-25 17:06:03 3 3 存储实时时钟/日历的 31 字节的静态 RAM,可通过简单的串行接口与微处理器通讯,将当前的是时钟存于RAM。DS1302芯片对于少于 31 天的月份月末会自动调整,并会自动对闰年进行校正。由于有一个... 2022-01-17 13:03:59 27 27 DS1302时钟芯片的使用带你写一个小时钟DS1302地址字节控制字节逻辑有效位必须是逻辑1,若为0,则数据就写不进去1302中。位6如果是0,则表示存取日历时钟数据位6如果是0,则表示存取RAM 2022-01-18 09:01:00 3 3 DS1302是DALLAS公司推出的涓流充电时钟芯片,内含有一个实时时钟/日历和31字节静态RAM,通过简单的串行接口与单片机进行通信。实时时钟/日历电路提供秒、分、时、日、日期、月、年的信息,每月 2022-04-22 14:27:33 3 3 TK1302带静态RAM的串行实时时钟包含一个RTC/日历和31字节的静态RAM。它通过一个简单的串行接口与微处理器通信。RTC/日历提供秒、分、时、日、日、月和年信息。月末日期自动调整为少于31天的月份,包括闰年的更正。时钟以24小时制或12小时制运行,带有AM/PM指示器。 2022-12-05 10:42:37 782 782  电子发烧友网站提供《带有月相LED矩阵的微型日历和时钟.zip》资料免费下载 2022-12-15 09:58:10 0 0 电子发烧友网站提供《使用1307 RTC、I2C LCD和Arduino Uno的数字日历时钟.zip》资料免费下载 2022-12-15 11:12:19 1 1

已全部加载完成

|  6047

6047

36

36 56

56 20

20 23

23 955

955 2043

2043

94

94 8

8 4289

4289

4619

4619

17

17 9

9 9249

9249 3

3 27

27 3

3 3

3 782

782

1

1 电子发烧友App

电子发烧友App

评论